# MIPS® Architecture for Programmers Volume IV-d:The SmartMIPS® Application-Specific Extension to the MIPS32® Architecture

Document Number: MD00101 Revision 3.01 December 16, 2012

MIPS Technologies, Inc. 955 East Arques Avenue Sunnyvale, CA 94085-4521

Copyright © 2004-2005, 2008, 2010,2012 MIPS Technologies Inc. All rights reserved.

Copyright © 2004-2005, 2008, 2010,2012 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS73, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS-VERIFIED, Aptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004Kc, 1004Kf, 1074Kc, 1074Kc, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries. All other trademarks referred to herein are the property of their respective owners.

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.02, Built with tags: 2B ARCH MIPS32

| MIPS® Architecture for Programmers Volume IV-d:The SmartMIPS® Application-Specific Extension to the MIPS32® Architecture, Revision 3.01 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

# **Table of Contents**

| Chapter 1: About This Book                                                           | 11 |

|--------------------------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                                       | 11 |

| 1.1.1: Italic Text                                                                   | 12 |

| 1.1.2: Bold Text                                                                     | 12 |

| 1.1.3: Courier Text                                                                  | 12 |

| 1.2: UNPREDICTABLE and UNDEFINED                                                     | 12 |

| 1.2.1: UNPREDICTABLE                                                                 | 12 |

| 1.2.2: UNDEFINED                                                                     | 13 |

| 1.2.3: UNSTABLE                                                                      | 13 |

| 1.3: Special Symbols in Pseudocode Notation                                          | 13 |

| 1.4: For More Information                                                            | 16 |

| Chapter 2: Guide to the Instruction Set                                              | 17 |

| 2.1: Understanding the Instruction Fields                                            | 17 |

| 2.1.1: Instruction Fields                                                            | 19 |

| 2.1.2: Instruction Descriptive Name and Mnemonic                                     | 19 |

| 2.1.3: Format Field                                                                  | 19 |

| 2.1.4: Purpose Field                                                                 | 20 |

| 2.1.5: Description Field                                                             | 20 |

| 2.1.6: Restrictions Field                                                            | 20 |

| 2.1.7: Operation Field                                                               | 21 |

| 2.1.8: Exceptions Field                                                              |    |

| 2.1.9: Programming Notes and Implementation Notes Fields                             |    |

| 2.2: Operation Section Notation and Functions                                        |    |

| 2.2.1: Instruction Execution Ordering                                                |    |

| 2.2.2: Pseudocode Functions                                                          |    |

| 2.3: Op and Function Subfield Notation                                               |    |

| 2.4: FPU Instructions                                                                | 31 |

| Chapter 3: The SmartMIPS® Application-Specific Extension to the MIPS32® Architecture |    |

| 3.1: Base Architecture Requirements                                                  |    |

| 3.2: Software Detection of the ASE                                                   |    |

| 3.3: Compliance and Subsetting                                                       |    |

| 3.4: Overview of the SmartMIPS ASE                                                   |    |

| 3.4.1: Support for Cryptographic Algorithms in the SmartMIPS ASE                     |    |

| 3.4.2: Code Density Optimization                                                     |    |

| 3.4.3: Other ISA Enhancements                                                        |    |

| 3.4.4: Privileged Resource Architecture Enhancements                                 |    |

| 3.5: Instruction Bit Encoding                                                        | 37 |

| Chapter 4: The SmartMIPS® Cryptographic Feature Set                                  |    |

| 4.1: The Special Register ACX                                                        |    |

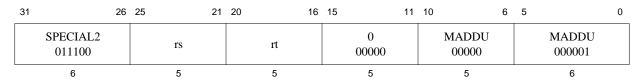

| 4.2: Change to MADDU Semantics                                                       |    |

| 4.3: Change to MULTU Semantics                                                       |    |

| 4.5: New Instructions                                                                | 42 |

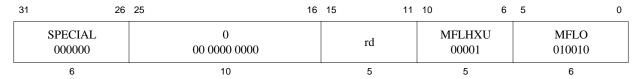

| 4.5.1: MFLHXU                                                                       | 42 |

|-------------------------------------------------------------------------------------|----|

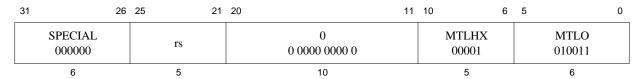

| 4.5.2: MTLHX                                                                        |    |

| 4.5.3: MADDP                                                                        |    |

| 4.5.4: MULTP                                                                        |    |

| 4.5.5: PPERM                                                                        |    |

| 4.5.6: ROTR                                                                         |    |

| 4.5.7: ROTRV                                                                        |    |

| 4.5.7. NOTKV                                                                        | 45 |

| Chantar F. Other ISA Flaments of the SmartMIDS® ASE                                 | 45 |

| Chapter 5: Other ISA Elements of the SmartMIPS® ASE                                 |    |

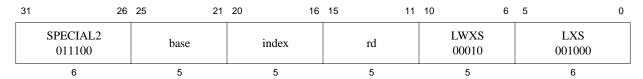

| 5.1: LWXS Instruction                                                               | 45 |

| OL                                                                                  |    |

| Chapter 6: The SmartMIPS® Release 3 Privileged Resource Architecture                | 5/ |

| 6.1: Introduction                                                                   |    |

| 6.2: Overview                                                                       |    |

| 6.3: Compliance                                                                     | 57 |

| 6.4: Interaction between the SmartMIPS ASE and Release 2 of the MIPS32 Architecture |    |

| 6.5: The SmartMIPS System Coprocessor                                               |    |

| 6.5.1: CP0 Register Summary                                                         |    |

| 6.6: Virtual Memory                                                                 |    |

| 6.6.1: TLB-Based Virtual Address Translation                                        |    |

| 6.6.2: General Exception Processing                                                 | 61 |

| 6.6.3: TLB Refill Exception                                                         | 61 |

| 6.6.4: TLB Invalid Exception                                                        | 61 |

| 6.6.5: TLB Modified Exception                                                       |    |

| 6.7: CP0 Registers                                                                  |    |

| 6.7.1: PageMask Register (CP0 Register 5, Select 0)                                 |    |

| 6.7.2: PageGrain Register (CP0 Register 5, Select 1)                                |    |

| 6.7.3: EntryHi Register (CP0 Register 10, Select 0                                  |    |

| 6.7.4: Configuration Register 3 (CP0 Register 16, Select 3)                         |    |

|                                                                                     |    |

| Appendix A: The SmartMIPS® Release 2 Privileged Resource Architecture               | 67 |

| A.1: Introduction                                                                   |    |

| A.2: Overview                                                                       |    |

| A.3: Compliance                                                                     |    |

| A.4: Interaction between the SmartMIPS ASE and Release 2 of the MIPS32 Architecture |    |

| A.5: The SmartMIPS System Coprocessor                                               |    |

|                                                                                     |    |

| A.5.1: CP0 Register Summary                                                         |    |

| A.6: Virtual Memory                                                                 |    |

| A.6.1: TLB-Based Virtual Address Translation                                        |    |

| A.6.2: General Exception Processing                                                 |    |

| A.6.3: TLB Refill Exception                                                         |    |

| A.6.4: TLB Invalid Exception                                                        |    |

| A.6.5: TLB Modified Exception                                                       |    |

| A.7: CP0 Registers                                                                  |    |

| A.7.1: EntryLo0, EntryLo1 (CP0 Registers 2 and 3, Select 0)                         |    |

| A.7.2: Context Register (CP0 Register 4, Select 0)                                  |    |

| A.7.3: ContextConfig Register (CP0 Register 4, Select 1)                            |    |

| A.7.4: PageMask Register (CP0 Register 5, Select 0)                                 |    |

| A.7.5: PageGrain Register (CP0 Register 5, Select 1)                                | 79 |

| A.7.6: EntryHi Register (CP0 Register 10, Select 0                                  |    |

| A.7.7: Configuration Register 3 (CP0 Register 16, Select 3)                         | 81 |

# **List of Figures**

| Figure 2.1: Example of Instruction Description                      | 18 |

|---------------------------------------------------------------------|----|

| Figure 2.2: Example of Instruction Fields                           | 19 |

| Figure 2.3: Example of Instruction Descriptive Name and Mnemonic    | 19 |

| Figure 2.4: Example of Instruction Format                           | 19 |

| Figure 2.5: Example of Instruction Purpose                          | 20 |

| Figure 2.6: Example of Instruction Description                      | 20 |

| Figure 2.7: Example of Instruction Restrictions                     | 21 |

| Figure 2.8: Example of Instruction Operation                        |    |

| Figure 2.9: Example of Instruction Exception                        |    |

| Figure 2.10: Example of Instruction Programming Notes               |    |

| Figure 2.11: COP_LW Pseudocode Function                             |    |

| Figure 2.12: COP_LD Pseudocode Function                             |    |

| Figure 2.13: COP_SW Pseudocode Function                             | 23 |

| Figure 2.14: COP_SD Pseudocode Function                             |    |

| Figure 2.15: CoprocessorOperation Pseudocode Function               |    |

| Figure 2.16: AddressTranslation Pseudocode Function                 |    |

| Figure 2.17: LoadMemory Pseudocode Function                         |    |

| Figure 2.18: StoreMemory Pseudocode Function                        |    |

| Figure 2.19: Prefetch Pseudocode Function                           |    |

| Figure 2.20: SyncOperation Pseudocode Function                      |    |

| Figure 2.21: ValueFPR Pseudocode Function                           |    |

| Figure 2.22: StoreFPR Pseudocode Function                           |    |

| Figure 2.23: CheckFPException Pseudocode Function                   | 29 |

| Figure 2.24: FPConditionCode Pseudocode Function                    | 29 |

| Figure 2.25: SetFPConditionCode Pseudocode Function                 |    |

| Figure 2.26: SignalException Pseudocode Function                    |    |

| Figure 2.27: SignalDebugBreakpointException Pseudocode Function     |    |

| Figure 2.28: SignalDebugModeBreakpointException Pseudocode Function |    |

| Figure 2.29: NullifyCurrentInstruction PseudoCode Function          |    |

| Figure 2.30: JumpDelaySlot Pseudocode Function                      |    |

| Figure 2.31: PolyMult Pseudocode Function                           |    |

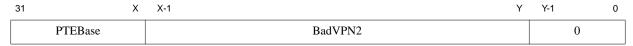

| Figure 6.1: SmartMIPS PageMask Register Format                      | 62 |

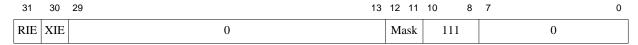

| Figure 6.2: SmartMIPS PageGrain Register Format                     |    |

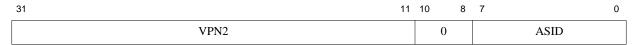

| Figure 6.3: SmartMIPS EntryHi Register Format                       |    |

| Figure A.1: Contents of a TLB Entry                                 |    |

| Figure A.2: SmartMIPS EntryLo0, EntryLo1 Register Format            |    |

| Figure A.3: SmartMIPS Context Register Format                       |    |

| Figure A.4: SmartMIPS ContextConfig Register Format                 |    |

| Figure A.5: SmartMIPS PageMask Register Format                      |    |

| Figure A.6: SmartMIPS PageGrain Register Format                     |    |

| Figure A.7: SmartMIPS EntryHi Register Format                       | 81 |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                     | 13 |

|---------------------------------------------------------------------------------|----|

| Table 2.1: AccessLength Specifications for Loads/Stores                         | 26 |

| Table 3.1: Symbols Used in the Instruction Encoding Tables                      | 37 |

| Table 3.2: SmartMIPS ASE Encoding of the Opcode Field                           |    |

| Table 3.3: SmartMIPS ASE SPECIAL Opcode Encoding of Function Field              | 38 |

| Table 3.4: SmartMIPS ASE SPECIAL2 Encoding of Function Field                    | 38 |

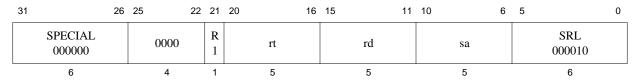

| Table 3.5: SmartMIPS ASE SRL Encoding of Shift/Rotate                           |    |

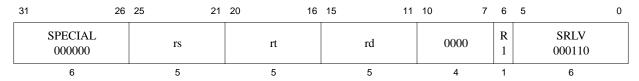

| Table 3.6: SmartMIPS ASE SRLV Encoding of Shift/Rotate                          | 38 |

| Table 3.7: SmartMIPS ASE MFLO Encoding of MFLO/MFLHXU                           |    |

| Table 3.8: SmartMIPS ASE MTLO Encoding of MTLO/MTLHX                            |    |

| Table 3.9: SmartMIPS ASE MULTU Encoding of MULTU/MULTP                          | 39 |

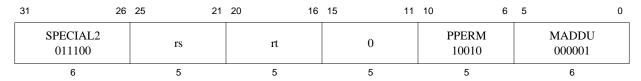

| Table 3.10: SmartMIPS ASE MADDU Encoding of MADDU/MADDP/PPERM                   |    |

| Table 3.11: SmartMIPS ASE LXS Encoding of LWXS                                  | 39 |

| Table 6.1: SmartMIPS Changes to Coprocessor 0 Registers in Numerical Order      |    |

| Table 6.2: Physical Address Generation                                          |    |

| Table 6.3: TLB Refill Exception State Saved in Addition to the Cause Register   |    |

| Table 6.4: TLB Invalid Exception State Saved in Addition to the Cause Register  |    |

| Table 6.5: TLB Modified Exception State Saved in Addition to the Cause Register |    |

| Table 6.7: Values for the Mask Field of the PageMask Register                   |    |

| Table 6.6: PageMask Register Field Descriptions                                 |    |

| Table 6.8: SmartMIPS PageGrain Register Field Descriptions                      |    |

| Table 6.9: PageGrain Implementation Subset Behavior                             |    |

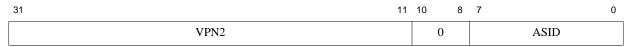

| Table 6.10: EntryHi Register Field Descriptions                                 | 66 |

| Table A.1: SmartMIPS Changes to Coprocessor 0 Registers in Numerical Order      |    |

| Table A.2: Physical Address Generation                                          |    |

| Table A.3: TLB Refill Exception State Saved in Addition to the Cause Register   |    |

| Table A.4: TLB Invalid Exception State Saved in Addition to the Cause Register  |    |

| Table A.5: TLB Modified Exception State Saved in Addition to the Cause Register |    |

| Table A.6: SmartMIPS EntryLo0, EntryLo1 Register Field Descriptions             |    |

| Table A.7: SmartMIPS Context Register Field Descriptions                        |    |

| Table A.8: SmartMIPS ContextConfig Register Field Descriptions                  |    |

| Table A.9: Recommended ContextConfig Values for SmartMIPS                       |    |

| Table A.10: PageMask Register Field Descriptions                                |    |

| Table A.11: Values for the Mask Field of the PageMask Register                  |    |

| Table A.12: SmartMIPS PageGrain Register Field Descriptions                     |    |

| Table A.13: PageGrain Implementation Subset Behavior                            |    |

| Table A.14: EntryHi Register Field Descriptions                                 | 81 |

# **About This Book**

The MIPS® Architecture for Programmers Volume IV-d:The SmartMIPS® Application-Specific Extension to the MIPS32® Architecture comes as part of a multi-volume set.

- Volume I-A describes conventions used throughout the document set, and provides an introduction to the MIPS32® Architecture

- Volume I-B describes conventions used throughout the document set, and provides an introduction to the microMIPS32<sup>TM</sup> Architecture

- Volume II-A provides detailed descriptions of each instruction in the MIPS32® instruction set

- Volume II-B provides detailed descriptions of each instruction in the microMIPS32<sup>TM</sup> instruction set

- Volume III describes the MIPS32® and microMIPS32<sup>TM</sup> Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS® processor implementation

- Volume IV-a describes the MIPS16e<sup>TM</sup> Application-Specific Extension to the MIPS32® Architecture. Beginning with Release 3 of the Architecture, microMIPS is the preferred solution for smaller code size.

- Volume IV-b describes the MDMX<sup>TM</sup> Application-Specific Extension to the MIPS64® Architecture and microMIPS64<sup>TM</sup>. It is not applicable to the MIPS32® document set nor the microMIPS32<sup>TM</sup> document set. With Release 5 of the Architecture, MDMX is deprecated. MDMX and MSA can not be implemented at the same time.

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and the microMIPS32<sup>TM</sup> Architecture.

- Volume IV-e describes the MIPS® DSP Module to the MIPS® Architecture

- Volume IV-f describes the MIPS® MT Module to the MIPS® Architecture

- Volume IV-h describes the MIPS® MCU Application-Specific Extension to the MIPS® Architecture

- Volume IV-i describes the MIPS® Virtualization Module to the MIPS® Architecture

- Volume IV-j describes the MIPS® SIMD Architecture Module to the MIPS® Architecture

# 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

#### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CPO usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

UNPREDICTABLE operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

**Table 1.1 Symbols Used in Instruction Operation Statements**

| Symbol          | Meaning                                                                                                                                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ←               | Assignment                                                                                                                                                                                                                                                        |

| =, ≠            | Tests for equality and inequality                                                                                                                                                                                                                                 |

|                 | Bit string concatenation                                                                                                                                                                                                                                          |

| x <sup>y</sup>  | A y-bit string formed by y copies of the single-bit value x                                                                                                                                                                                                       |

| b#n             | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| 0bn             | A constant value $n$ in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                                   |

| 0xn             | A constant value $n$ in base $16$ . For instance $0x100$ represents the hexadecimal value $100$ (decimal $256$ ).                                                                                                                                                 |

| x <sub>yz</sub> | Selection of bits $y$ through $z$ of bit string $x$ . Little-endian bit notation (rightmost bit is 0) is used. If $y$ is less than $z$ , this expression is an empty (zero length) bit string.                                                                    |

| +, -            | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol        | Meaning                                                                                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *,×           | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                                                         |

| div           | 2's complement integer division                                                                                                                                                                                                                                                                                |

| mod           | 2's complement modulo                                                                                                                                                                                                                                                                                          |

| /             | Floating point division                                                                                                                                                                                                                                                                                        |

| <             | 2's complement less-than comparison                                                                                                                                                                                                                                                                            |

| >             | 2's complement greater-than comparison                                                                                                                                                                                                                                                                         |

| ≤             | 2's complement less-than or equal comparison                                                                                                                                                                                                                                                                   |

| ≥             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                                                                |

| nor           | Bitwise logical NOR                                                                                                                                                                                                                                                                                            |

| xor           | Bitwise logical XOR                                                                                                                                                                                                                                                                                            |

| and           | Bitwise logical AND                                                                                                                                                                                                                                                                                            |

| or            | Bitwise logical OR                                                                                                                                                                                                                                                                                             |

| not           | Bitwise inversion                                                                                                                                                                                                                                                                                              |

| &&            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                                                                      |

| <<            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                                                                         |

| >>            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                                                                         |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                             |

| GPR[x]        | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                                   |

| SGPR[s,x]     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose registers may be implemented. SGPR[s,x] refers to GPR set s, register x.                                                                                                                                  |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                                              |

| FCC[CC]       | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                                         |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                                                                 |

| CPR[z,x,s]    | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                               |

| CP2CPR[x]     | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                  |

| CCR[z,x]      | Coprocessor unit z, control register x                                                                                                                                                                                                                                                                         |

| CP2CCR[x]     | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                  |

| COC[z]        | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                            |

| Xlat[x]       | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                               |

| BigEndianMem  | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the enanness of Kernel and Supervisor mode execution.                             |

| BigEndianCPU  | The endianness for load and store instructions ( $0 \rightarrow \text{Little-Endian}$ , $1 \rightarrow \text{Big-Endian}$ ). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian). |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as (SR <sub>RE</sub> and User mode).                                           |

<sup>14</sup> MIPS® Architecture for Programmers Volume IV-d:The SmartMIPS® Application-Specific Extension to the MIPS32® Architecture, Revision 3.01

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Meaning                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> .  The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| PC                   | tion word. The address of ing a value to <i>PC</i> during pseudocode statement, it tion) or 4 before the next instruction time of the ins In the MIPS Architecture restart address into a GPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f the instruct is auton instruct struction e, the PC on a justice. | ring the instruction time of an instruction, this is the add ruction that occurs during the next instruction time is de action time. If no value is assigned to <i>PC</i> during an instruction time. A taken branch assigns the target address to the in the branch delay slot.  I value is only visible indirectly, such as when the proce mp-and-link or branch-and-link instruction, or into a Contains a full 32-bit address all of which are significant d | etermined by assign-<br>ruction time by any<br>MIPS 16e instruc-<br>ne PC during the<br>ssor stores the<br>processor 0 register |

| ISA Mode             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | MIPS16e Application Specific Extension or the microNoit register that determines in which mode the processor                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                 |

|                      | Enc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | oding                                                              | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                  | The processor is executing 32-bit MIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                  | The processor is executing MIIPS16e or microMIPS instructions                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                 |

|                      | combined value of the up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | per bits                                                           | A Mode value is only visible indirectly, such as when the of PC and the ISA Mode into a GPR on a jump-and-link of register on an exception.                                                                                                                                                                                                                                                                                                                      |                                                                                                                                 |

| PABITS               | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{PABITS} = 2^{36}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP32RegistersMode                    | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). In MIPS32 Release 1, the FPU has 32 32-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs. In MIPS64, (and optionally in MIPS32 Release2 and MIPSr3) the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                                                                                                                                    |

|                                      | In MIPS32 Release 1 implementations, <b>FP32RegistersMode</b> is always a 0. MIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs. The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register. |

| InstructionInBranchDe-<br>laySlot    | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                                                                                                                            |

| SignalException(exception, argument) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function—the exception is signaled at the point of the call.                                                                                                                                                                                                                                                                                        |

# 1.4 For More Information

Various MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL: http://www.mips.com

For comments or questions on the MIPS32® Architecture or this document, send Email to support@mips.com.

# **Guide to the Instruction Set**

This chapter provides a detailed guide to understanding the instruction descriptions, which are listed in alphabetical order in the tables at the beginning of the next chapter.

# 2.1 Understanding the Instruction Fields

Figure 2.1 shows an example instruction. Following the figure are descriptions of the fields listed below:

- "Instruction Fields" on page 19

- "Instruction Descriptive Name and Mnemonic" on page 19

- "Format Field" on page 19

- "Purpose Field" on page 20

- "Description Field" on page 20

- "Restrictions Field" on page 20

- "Operation Field" on page 21

- "Exceptions Field" on page 21

- "Programming Notes and Implementation Notes Fields" on page 22

Instruction Mnemonic and **EXAMPLE Example Instruction Name** Descriptive Name **EXAMPLE** 31 26 25 21 20 16 15 11 10 6 5 0 Instruction encoding constant and variable field **SPECIAL** 0 **EXAMPLE** 0 names and values rt rd 000000 00000 000000 6 5 5 5 5 6 Architecture level at which instruction was defined/redefined Format: MIPS32 EXAMPLE fd, rs, rt Assembler format(s) for each definition **Purpose:** Example Instruction Name Short description -To execute an EXAMPLE op. Symbolic description . **Description:**  $GPR[rd] \leftarrow GPR[r]s$  example op GPR[rt]This section describes the operation of the instruction in text, tables, and illustrations. It Full description of . includes information that would be difficult to encode in the Operation section. instruction operation Restrictions: Restrictions on instruction and operands This section lists any restrictions for the instruction. This can include values of the instruction encoding fields such as register specifiers, operand values, operand formats, address alignment, instruction scheduling hazards, and type of memory access for addressed locations. High-level language Operation: description of instruction operation /\* This section describes the operation of an instruction in \*/ /\* a high-level pseudo-language. It is precise in ways that /\* the Description section is not, but is also missing \* / information that is hard to express in pseudocode. \* / ← GPR[rs] exampleop GPR[rt] temp  $GPR[rd] \leftarrow temp$ Exceptions that -**Exceptions:** instruction can cause A list of exceptions taken by the instruction Notes for programmers \_ → Programming Notes: Information useful to programmers, but not necessary to describe the operation of the instruction Implementation Notes: Notes for implementors -

Figure 2.1 Example of Instruction Description

Like *Programming Notes*, except for processor implementors

#### 2.1.1 Instruction Fields

Fields encoding the instruction word are shown in register form at the top of the instruction description. The following rules are followed:

- The values of constant fields and the *opcode* names are listed in uppercase (SPECIAL and ADD in Figure 2.2). Constant values in a field are shown in binary below the symbolic or hexadecimal value.

- All variable fields are listed with the lowercase names used in the instruction description (*rs*, *rt*, and *rd* in Figure 2.2).

- Fields that contain zeros but are not named are unused fields that are required to be zero (bits 10:6 in Figure 2.2). If such fields are set to non-zero values, the operation of the processor is **UNPREDICTABLE**.

26 25 31 21 20 16 15 11 10 6 5 0 **SPECIAL** 0 ADD rt rd rs 000000 00000 100000 6 5

Figure 2.2 Example of Instruction Fields

#### 2.1.2 Instruction Descriptive Name and Mnemonic

The instruction descriptive name and mnemonic are printed as page headings for each instruction, as shown in Figure 2.3.

Figure 2.3 Example of Instruction Descriptive Name and Mnemonic

Add Word ADD

#### 2.1.3 Format Field

The assembler formats for the instruction and the architecture level at which the instruction was originally defined are given in the *Format* field. If the instruction definition was later extended, the architecture levels at which it was extended and the assembler formats for the extended definition are shown in their order of extension (for an example, see C.cond.fmt). The MIPS architecture levels are inclusive; higher architecture levels include all instructions in previous levels. Extensions to instructions are backwards compatible. The original assembler formats are valid for the extended architecture.

Figure 2.4 Example of Instruction Format

Format: ADD fd,rs,rt MIPS32

The assembler format is shown with literal parts of the assembler instruction printed in uppercase characters. The variable parts, the operands, are shown as the lowercase names of the appropriate fields. The architectural level at which the instruction was first defined, for example "MIPS32" is shown at the right side of the page.

There can be more than one assembler format for each architecture level. Floating point operations on formatted data show an assembly format with the actual assembler mnemonic for each valid value of the *fmt* field. For example, the ADD.fmt instruction lists both ADD.S and ADD.D.

The assembler format lines sometimes include parenthetical comments to help explain variations in the formats (once again, see C.cond.fmt). These comments are not a part of the assembler format.

#### 2.1.4 Purpose Field

The *Purpose* field gives a short description of the use of the instruction.

#### Figure 2.5 Example of Instruction Purpose

Purpose: Add Word

To add 32-bit integers. If an overflow occurs, then trap.

# 2.1.5 Description Field

If a one-line symbolic description of the instruction is feasible, it appears immediately to the right of the *Description* heading. The main purpose is to show how fields in the instruction are used in the arithmetic or logical operation.

#### Figure 2.6 Example of Instruction Description

**Description:** GPR[rd] ← GPR[rs] + GPR[rt]

The 32-bit word value in GPR *rt* is added to the 32-bit value in GPR *rs* to produce a 32-bit result.

- If the addition results in 32-bit 2's complement arithmetic overflow, the destination register is not modified and an Integer Overflow exception occurs.

- If the addition does not overflow, the 32-bit result is placed into GPR rd.

The body of the section is a description of the operation of the instruction in text, tables, and figures. This description complements the high-level language description in the *Operation* section.

This section uses acronyms for register descriptions. "GPR rt" is CPU general-purpose register specified by the instruction field rt. "FPR fs" is the floating point operand register specified by the instruction field fs. "CP1 register fd" is the coprocessor 1 general register specified by the instruction field fd. "FCSR" is the floating point Control /Status register.

#### 2.1.6 Restrictions Field

The *Restrictions* field documents any possible restrictions that may affect the instruction. Most restrictions fall into one of the following six categories:

- Valid values for instruction fields (for example, see floating point ADD.fmt)

- ALIGNMENT requirements for memory addresses (for example, see LW)

- Valid values of operands (for example, see ALNV.PS)

- Valid operand formats (for example, see floating point ADD.fmt)

- Order of instructions necessary to guarantee correct execution. These ordering constraints avoid pipeline hazards for which some processors do not have hardware interlocks (for example, see MUL).

- Valid memory access types (for example, see LL/SC)

#### Figure 2.7 Example of Instruction Restrictions

#### **Restrictions:**

None

#### 2.1.7 Operation Field

The *Operation* field describes the operation of the instruction as pseudocode in a high-level language notation resembling Pascal. This formal description complements the *Description* section; it is not complete in itself because many of the restrictions are either difficult to include in the pseudocode or are omitted for legibility.

Figure 2.8 Example of Instruction Operation

```

Operation:  \begin{split} & \text{temp} \leftarrow (\text{GPR}[\text{rs}]_{31} | | \text{GPR}[\text{rs}]_{31...0}) + (\text{GPR}[\text{rt}]_{31} | | \text{GPR}[\text{rt}]_{31...0}) \\ & \text{if } \text{temp}_{32} \neq \text{temp}_{31} \text{ then} \\ & \text{SignalException}(\text{IntegerOverflow}) \\ & \text{else} \\ & \text{GPR}[\text{rd}] \leftarrow \text{temp} \end{split}

```

See 2.2 "Operation Section Notation and Functions" on page 22 for more information on the formal notation used here.

# 2.1.8 Exceptions Field

The *Exceptions* field lists the exceptions that can be caused by *Operation* of the instruction. It omits exceptions that can be caused by the instruction fetch, for instance, TLB Refill, and also omits exceptions that can be caused by asynchronous external events such as an Interrupt. Although a Bus Error exception may be caused by the operation of a load or store instruction, this section does not list Bus Error for load and store instructions because the relationship between load and store instructions and external error indications, like Bus Error, are dependent upon the implementation.

Figure 2.9 Example of Instruction Exception

#### **Exceptions:**

endif

Integer Overflow