# Section 55. Charge Time Measurement Unit (CTMU)

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 55.1  | Introduction                                |       |

|-------|---------------------------------------------|-------|

| 55.2  | Registers                                   |       |

| 55.3  | CTMU Operation                              |       |

| 55.4  | CTMU Module Initialization                  |       |

| 55.5  | Calibrating the CTMU Module                 | 55-10 |

| 55.6  | Measuring Capacitance with the CTMU         | 55-15 |

| 55.7  | Measuring Time with the CTMU Module         | 55-17 |

| 55.8  | Creating a Delay with the CTMU Module       | 55-18 |

| 55.9  | Measuring On-chip Temperature With the CTMU | 55-19 |

| 55.10 | Operation During Sleep or Idle Mode         | 55-20 |

| 55.11 | Effects of a Reset on CTMU                  | 55-20 |

| 55.12 | Pregister Maps                              | 55-21 |

| 55.13 | Related Application Notes                   | 55-22 |

| 55.14 | Revision History                            | 55-23 |

55

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33F/PIC24H devices.

Please consult the note at the beginning of the "Charge Time Measurement Unit (CTMU)" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

## 55.1 INTRODUCTION

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources and asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can be used to precisely measure time, capacitance, relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- Up to 16 channels available for capacitive or time measurement input

- On-chip precision current source

- · Four-edge input trigger sources

- Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

The CTMU works in conjunction with the A/D Converter to provide up to 16 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs, Timer1 or Output Compare Module 1. For device-specific information on available input sources, refer to the appropriate dsPIC33F/PIC24H data sheet.

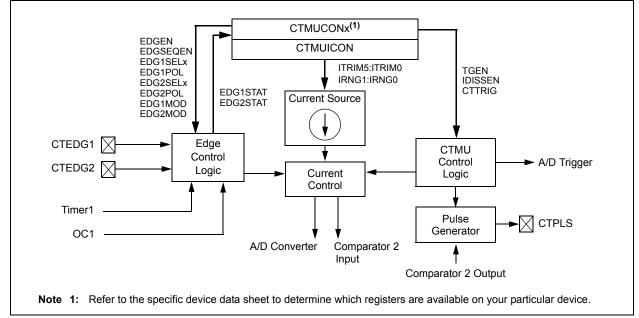

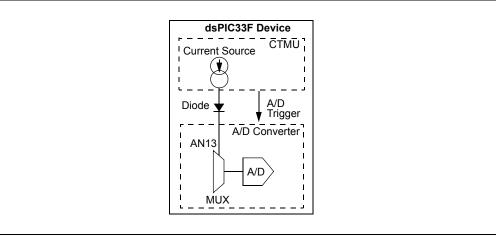

A block diagram of the CTMU is illustrated in Figure 55-1.

#### Figure 55-1: CTMU Block Diagram

# 55.2 REGISTERS

Depending on the device variant there are up to three control registers available for the CTMU: CMTUCON1, CTMUCON2, and CTMUICON.

The CTMUCON1 and CTMUCON2 registers (Register 55-1 and Register 55-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 55-3) has bits for selecting the current source range and current source trim.

| Register 55-1: | CTMUCON1: CTMU Control Register 1 <sup>(1)</sup> |

|----------------|--------------------------------------------------|

|----------------|--------------------------------------------------|

| R/W-0  | U-0        | R/W-0 | R/W-0      | R/W-0 | R/W-0    | R/W-0   | R/W-0  |  |

|--------|------------|-------|------------|-------|----------|---------|--------|--|

| CTMUEN | - CTMUSIDL |       | TGEN EDGEN |       | EDGSEQEN | IDISSEN | CTTRIG |  |

| bit 15 |            |       |            |       |          |         |        |  |

|        |            |       |            |       |          |         |        |  |

| U-0    | U-0        | U-0   | U-0        | U-0   | U-0      | U-0     | U-0    |  |

| _      |            |       | _          | _     | —        | _       |        |  |

bit 7

| Legend:    |                                  |                                                                |                                    |                    |  |  |  |  |  |  |

|------------|----------------------------------|----------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | able bit                         | W = Writable bit                                               | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |  |

| -n = Value | at POR                           | '1' = Bit is set                                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |  |

| bit 15     | CTMUEN                           | I: CTMU Enable bit                                             |                                    |                    |  |  |  |  |  |  |

|            |                                  | ule is enabled<br>ule is disabled                              |                                    |                    |  |  |  |  |  |  |

| bit 14     | Unimple                          | mented: Read as '0'                                            |                                    |                    |  |  |  |  |  |  |

| bit 13     | CTMUSI                           | DL: Stop in Idle Mode bit                                      |                                    |                    |  |  |  |  |  |  |

|            |                                  | ontinue module operation whi                                   |                                    |                    |  |  |  |  |  |  |

| bit 12     | TGEN: Time Generation Enable bit |                                                                |                                    |                    |  |  |  |  |  |  |

|            |                                  | bles edge delay generation<br>bles edge delay generation       |                                    |                    |  |  |  |  |  |  |

| bit 10     | EDGEN:                           | Edge Enable bit                                                |                                    |                    |  |  |  |  |  |  |

|            | •                                | es are not blocked<br>es are blocked                           |                                    |                    |  |  |  |  |  |  |

| bit 10     | EDGSEC                           | EN: Edge Sequence Enable                                       | e bit                              |                    |  |  |  |  |  |  |

|            | •                                | e 1 event must occur before l<br>dge sequence is needed        | Edge 2 event can occur             |                    |  |  |  |  |  |  |

| bit 9      | IDISSEN                          | : Analog Current Source Cor                                    | ntrol bit                          |                    |  |  |  |  |  |  |

|            |                                  | og current source output is g<br>og current source output is n |                                    |                    |  |  |  |  |  |  |

| bit 8      | CTTRIG:                          | Trigger Control bit                                            |                                    |                    |  |  |  |  |  |  |

|            | •••                              | ger output is enabled<br>ger output is disabled                |                                    |                    |  |  |  |  |  |  |

| bit 7-0    | Unimple                          | mented: Read as '0'                                            |                                    |                    |  |  |  |  |  |  |

|            |                                  |                                                                |                                    |                    |  |  |  |  |  |  |

**Note 1:** Refer to the specific device data sheet to determine whether this register is available on your particular device.

bit 0

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                      | R/W-0                                                                                                                                            | R/W-0                  | R/W-0           | R/W-0           | U-0      |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----------------|----------|--|--|

| EDG1MOD       | EDG1POL                                                                                                                                                           |                                                                                                                                                                                                                                            | EDG1S                                                                                                                                            | EL<3:0> <sup>(1)</sup> |                 | EDG2STAT        | EDG1STAT |  |  |

| bit 15        |                                                                                                                                                                   |                                                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 | bit 8    |  |  |

|               |                                                                                                                                                                   |                                                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 |          |  |  |

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                      | R/W-0                                                                                                                                            | R/W-0                  | R/W-0           | U-0             | U-0      |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                                           |                                                                                                                                                                                                                                            | EDG2S                                                                                                                                            | EL<3:0> <sup>(1)</sup> |                 | —               |          |  |  |

| bit 7         |                                                                                                                                                                   |                                                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 | bit      |  |  |

| Legend:       |                                                                                                                                                                   |                                                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 |          |  |  |

| R = Readable  | e bit                                                                                                                                                             | W = Writable I                                                                                                                                                                                                                             | oit                                                                                                                                              | U = Unimplem           | nented bit, rea | d as '0'        |          |  |  |

| -n = Value at | POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                           |                                                                                                                                                  | '0' = Bit is clea      | ared            | x = Bit is unkn | iown     |  |  |

| bit 15        | <b>EDG1MOD:</b> In 1 = Input is ed<br>0 = Input is le                                                                                                             | •                                                                                                                                                                                                                                          | ction bit                                                                                                                                        |                        |                 |                 |          |  |  |

| bit 14        | 1 = Edge 1 p                                                                                                                                                      | dge 1 Polarity S<br>rogrammed for                                                                                                                                                                                                          | a positive lev                                                                                                                                   |                        |                 |                 |          |  |  |

| bit 13-10     | • .                                                                                                                                                               | rogrammed for<br><b>0&gt;:</b> Edge 1 So                                                                                                                                                                                                   | •                                                                                                                                                | •                      |                 |                 |          |  |  |

|               | 1100 = Edge<br>1011 = Edge<br>1001 = Edge<br>1000 = Edge<br>0111 = Edge<br>0110 = Edge<br>0101 = Edge<br>0100 = Edge<br>0011 = Edge<br>0001 = Edge<br>0000 = Edge | 1 Source 13 set<br>1 Source 12 set<br>1 Source 11 set<br>1 Source 10 set<br>1 Source 9 set<br>1 Source 9 set<br>1 Source 7 set<br>1 Source 6 set<br>1 Source 5 set<br>1 Source 4 set<br>1 Source 2 set<br>1 Source 2 set<br>1 Source 0 set | elected<br>elected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected<br>ected |                        |                 |                 |          |  |  |

| bit 9         | EDG2STAT: Edge 2 Status bit<br>1 = Edge 2 event has occurred<br>0 = Edge 2 event has not occurred                                                                 |                                                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 |          |  |  |

| bit 8         | 1 = Edge 1 e                                                                                                                                                      | Edge 1 Status b<br>vent has occurr<br>vent has not oc                                                                                                                                                                                      | red                                                                                                                                              |                        |                 |                 |          |  |  |

| bit 7         | -                                                                                                                                                                 | nput Mode Sele<br>Ige-sensitive                                                                                                                                                                                                            |                                                                                                                                                  |                        |                 |                 |          |  |  |

| bit 6         | EDG2POL: E                                                                                                                                                        | dge 2 Polarity S                                                                                                                                                                                                                           | a positive lev                                                                                                                                   |                        |                 |                 |          |  |  |

# Register 55-2: CTMUCON2: CTMU Control Register 2

**Note 1:** Refer to the particular device data sheet for specific edge source types and assignments.

Register 55-2: CTMUCON2: CTMU Control Register (Continued)2

- bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits<sup>(1)</sup> 11 = Edge 2 Source 3 selected 10 = Edge 2 Source 2 selected 01 = Edge 2 Source 1 selected 00 = Edge 2 Source 0 selected bit 1-0 Unimplemented: Read as '0'

- Note 1: Refer to the particular device data sheet for specific edge source types and assignments.

**G** Charge Time Measurement Unit (CTMU)

| R/W-0        | R/W-0                                                                                                            | R/W-0              | R/W-0 R/W-0 |                            | R/W-0           | R/W-0              | R/W-0 |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------|--------------------|-------------|----------------------------|-----------------|--------------------|-------|--|--|--|--|--|

|              |                                                                                                                  | ITRIM              | <5:0>       | IRNG<1:0>                  |                 |                    |       |  |  |  |  |  |

| bit 15       |                                                                                                                  |                    |             |                            |                 | 1                  | bit 8 |  |  |  |  |  |

|              |                                                                                                                  |                    |             |                            |                 |                    |       |  |  |  |  |  |

| U-0          | U-0                                                                                                              | U-0                | U-0         | U-0                        | U-0             | U-0                | U-0   |  |  |  |  |  |

|              |                                                                                                                  |                    |             |                            |                 |                    | —     |  |  |  |  |  |

| bit 7        |                                                                                                                  |                    |             |                            |                 |                    | bit ( |  |  |  |  |  |

| Legend:      |                                                                                                                  |                    |             |                            |                 |                    |       |  |  |  |  |  |

| R = Readat   | ole hit                                                                                                          | W = Writable I     | hit         | II = I Inimplen            | nented bit, rea | d as 'O'           |       |  |  |  |  |  |

| -n = Value a |                                                                                                                  | '1' = Bit is set   | on          | '0' = Bit is clea          |                 | x = Bit is unknown |       |  |  |  |  |  |

|              |                                                                                                                  | 1 - Dit 13 301     |             |                            | arcu            |                    | 00011 |  |  |  |  |  |

|              | • 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG1:IRNG0 |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | <ul> <li>111111 = Minimum negative change from nominal current</li> <li>•</li> </ul>                             |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | •                                                                                                                |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | •                                                                                                                |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | 100010<br>100001 = Maximum negative change from nominal current                                                  |                    |             |                            |                 |                    |       |  |  |  |  |  |

| bit 9-8      | IRNG<1:0>: Current Source Range Select bits<br>11 = 100 × base current                                           |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | $11 = 100 \times c$<br>$10 = 10 \times ba$                                                                       |                    |             |                            |                 |                    |       |  |  |  |  |  |

|              | 01 <b>= Base c</b>                                                                                               | urrent level (0.55 |             | .(1)                       |                 |                    |       |  |  |  |  |  |

| h: 1 7 0     |                                                                                                                  | t source disabled  |             | ase current <sup>(1)</sup> |                 |                    |       |  |  |  |  |  |

| bit 7-0      | Unimpieme                                                                                                        | nted: Read as '0   | )           |                            |                 |                    |       |  |  |  |  |  |

## Register 55-3: CTMUICON: CTMU Current Control Register

Note 1: Refer to the specific device data sheet to determine which setting is available on your particular device.

# 55.3 CTMU OPERATION

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement is made. In the case of charge measurement, the current and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D is then a measurement of the capacitance of the circuit. In the case of time measurement, the current and the capacitance of the circuit is fixed. In this case, the voltage read by the A/D is then representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is used as a time delay, both capacitance and current source are fixed, and the voltage supplied to the comparator circuit also fixed. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

## 55.3.1 Theory of Operation

The operation of the CTMU is based on the equation for charge, as shown in Equation 1.

### Equation 55-1:

$I = C \cdot \frac{dV}{dT}$

The amount of charge measured in coulombs in a circuit is defined as current in amperes (I) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V), as shown in Equation.

### Equation 55-2:

$$I \cdot t \; = \; C \cdot V$$

The CTMU module provides a constant current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). Equation 55-2 can be used to calculate capacitance or time either using the known fixed capacitance of the circuit as shown in Equation 55-3 or using a fixed time that the current source is applied to the circuit as shown in Equation 55-4.

### Equation 55-3:

$t = \frac{(C \cdot V)}{I}$

Equation 55-4:

## 55.3.2 Current Source

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges or a total of two orders of magnitude, with the ability to trim the output in  $\pm 2\%$  increments (nominal). The current range is selected by the IRNG1:IRNG0 bits (CTMUICON<9:8>), with a value of '00' representing the lowest range.

Current trim is provided by the ITRIM5:ITRIM0 bits (CTMUICON<15:10>). These six bits allow trimming of the current source in steps of approximately 2% per step. The half of the range adjusts the current source positively and another half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100000' is the maximum negative adjustment (approximately -62%), and '011111' is the maximum positive adjustment (approximately +62%).

## 55.3.3 Edge Selection and Control

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTEDG1 and CTEDG2), Timer1 or Output Compare Module 1. The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCON2<5:2> and <13:9>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCON2<14:6>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCON1<10>).

## 55.3.4 Edge Status

The CTMUCON register also contains two status bits, EDG2STAT and EDG1STAT (CTMUCON2<9:8>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the status bits become set immediately if the channel's configuration is changed and the input channels remain at their current state.

The module uses the edge status bits to control the current source output to external analog modules like A/D Converter. Current is supplied to external modules only when one (but not both) of the status bits is set, and shuts current off when both the bits are either set or cleared. This allows the CTMU to measure current only during the interval between edges. After both status bits are set, it is necessary to clear them before another measurement is taken. If possible, both the bits should be cleared simultaneously to avoid re-enabling the CTMU current source.

In addition to being set by the CTMU hardware, the edge status bits can also be set by software. This is also the user's application to manually enable or disable the current source. Setting either one (but not both) of the bits enables the current source. Setting or clearing both bits at once disables the source.

## 55.3.5 Interrupts

The CTMU sets its interrupt flag (IFS4<13>) whenever the current source is enabled and disabled. An interrupt is generated only if the corresponding interrupt enable bit (IEC4<13>) is also set. If edge sequencing is not enabled (that is Edge 1 must occur before Edge 2), it is necessary to monitor the edge status bits and determine which edge occurred last and caused the interrupt.

# 55.4 CTMU MODULE INITIALIZATION

The following sequence is a general guideline used to initialize the CTMU module:

- 1. Select the current source range using the IRNG bits (CTMUICON<9:8>).

- 2. Adjust the current source trim using the ITRIM bits (CTMUICON<15:10>).

- 3. Configure the edge input sources for Edge 1 and Edge 2 by setting the EDG1SEL and EDG2SEL bits (CTMUCON2<13:10> and <5:2>).

- 4. Configure the input polarities for the edge inputs using the EDG1POL and EDG2POL bits (CTMUCON2<14:6>). The default configuration is for negative edge polarity (high-to-low transitions).

- 5. Enable edge sequencing using the EDGSEQEN bit (CTMUCON1<10>). By default, edge sequencing is disabled.

- 6. Select the operating mode (Measurement or Time Delay) with the TGEN bit. The default mode is Time/Capacitance Measurement.

- Configure the module to automatically trigger an A/D conversion when the second edge event has occurred using the CTTRIG bit (CTMUCON1<8>). The conversion trigger is disabled by default.

- 8. Discharge the connected circuit by setting the IDISSEN bit (CTMUCON1<9>); after waiting a sufficient time for the circuit to discharge, clear IDISSEN.

- 9. Disable the module by clearing the CTMUEN bit (CTMUCON1<15>).

- 10. Clear the Edge Status bits, EDG2STAT and EDG1STAT (CTMUCON2<9:8>).

- 11. Enable both edge inputs by setting the EDGEN bit (CTMUCON1<11>).

- 12. Enable the module by setting the CTMUEN bit.

Depending on the type of measurement or pulse generation being performed, one or more additional modules may also need to be initialized and configured with the CTMU module:

- Edge Source Generation: In addition to the external edge input pins, both Timer1 and the Output Compare/PWM1 module can be used as edge sources for the CTMU.

- Capacitance or Time Measurement: The CTMU module uses the A/D Converter to measure the voltage across a capacitor that is connected to one of the analog input channels.

- Pulse Generation: When generating system clock independent output pulses, the CTMU module uses Comparator 2 and the associated comparator voltage reference.

For specific information on initializing these modules, refer to the applicable dsPIC33F/PIC24H Family Reference chapter for the appropriate module.

# 55.5 CALIBRATING THE CTMU MODULE

The CTMU requires calibration for precise measurements of capacitance and time, and also for accurate time delay. If the application only requires measurement of a relative change in capacitance or time, calibration is usually not necessary. An example of this type of application would include a capacitive touch switch, in which the touch circuit has a baseline capacitance, and the added capacitance of the human body changes the overall capacitance of a circuit.

If actual capacitance or time measurement is required, two hardware calibrations must take place: the current source needs calibration to set it to a precise current, and the circuit being measured needs calibration to measure and/or nullify all other capacitance other than that to be measured.

## 55.5.1 Current Source Calibration

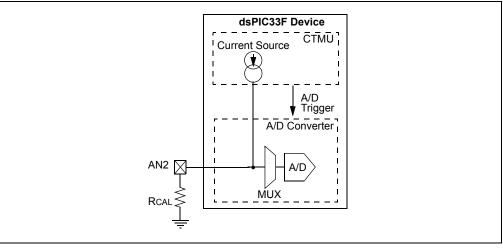

The current source onboard the CTMU module has a range of  $\pm 62\%$  nominal for each of three current ranges. Therefore, for precise measurements, it is possible to measure and adjust this current source by placing a high precision resistor, RCAL, on the analog channel AN2. An example circuit is illustrated in Figure 55-2. The current source measurement is performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU by configure the module for Pulse Generation mode (TGEN = 1).

- 3. Enable the current source by setting EDG1STAT (CTMUCON1<8>).

- 4. Issue settling time delay.

- 5. Perform A/D conversion.

- 6. Calculate the current source current using I = V/RCAL, where RCAL is a high precision resistance and V is measured by performing an A/D conversion.

The CTMU current source may be trimmed with the trim bits in CTMUICON using an iterative process to get an exact desired current. Alternatively, the nominal value without adjustment may be used and it may be stored by the software for use in all subsequent capacitive or time measurements.

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON1<12>), the internal current source is connected to one of the inputs of Comparator 2. Figure 55-2 illustrates the external connections for current source calibration and the relationship of the different analog modules required.

To calculate the value for *RCAL*, the nominal current must be chosen, and then the resistance can be calculated. For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale, or 2.31V as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as *RCAL* = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, *RCAL* will be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

### Figure 55-2: CTMU Current Source Calibration Circuit

A value of 70% full-scale voltage is chosen to ensure that the A/D Converter was in a range that is well above the noise floor. If an exact current is chosen that is to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL may be adjusted to allow for available resistor values. RCAL should be of the highest precision available, the amount of precision required for the circuit that the CTMU will be used to measure. A recommended minimum precision will be 0.1% tolerance.

The following examples show a typical method for performing a CTMU current calibration. Example 55-1 shows how to initialize the A/D Converter and the CTMU; this routine is typical for the applications using both the modules. Example 55-2 shows one method for the actual calibration routine. This method manually triggers the A/D Converter and it is performed to demonstrate the entire stepwise process. It is also possible to automatically trigger the conversion by setting the CTTRIG bit (CTMUCON1<8>).

# Example 55-1: Setup for CTMU Calibration Routines for Devices with CTMUCON1 and CTMUCON2 Registers

```

#include "p33Fxxxx.h"

*****

void setup(void)

{ //CTMUCON - CTMU Control register

CTMUCON1 = 0x1000; //make sure CTMU is disabled

CTMUCON2 = 0 \times C0C0;

// CTMU continues to run when emulator is stopped, CTMU continues

// to run in idle mode, Time Generation mode enabled, Edges are

// blocked. No edge sequence order, Analog current source not

// grounded, trigger output disabled, Edge2 polarity = positive level,

// Edge2 source = source 0, Edge1 polarity = positive level,

// Edge1 source = source 0, Set Edge status bits to zero

//CTMUICON - CTMU Current Control Register

CTMUICON = 0x0100; // 0.55uA, Nominal - No Adjustment

TRISB = 0x0001; // Set channel 2 as an input

AD1PCFG = 0x0001; //

AD1CHS = 0x002; // Select the analog channel(2)

AD1CSSL = 0x0000; //

AD1CON1 = 0x8000; // Turn On A/D Converter, continue in Idle mode,

// Unsigned fractional format, Clear SAMP bit to

// start conversion, Sample when SAMP bit is set,

// sampling on hold

AD1CON2 = 0x0000; // VR+ = AVDD, V- = AVSS, Don't scan,

// always use MUX A inputs

AD1CON3 = 0x0000; // A/D uses system clock, conversion clock = 1xTcy

```

```

#include "p33Fxxxx.h"

#define

COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define RCAL .027 //R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

#define ADSCALE 1023 //for unsigned conversion 10 sig bits

#define ADREF 3.3 //Vdd connected to A/D Vr+

int main (void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

double VTot = 0;

float Vavg=0, Vcal=0, CTMUISrc = 0; //float values stored for calcs

//assume CTMU and A/D have been setup correctly

//see Example 11-1 for CTMU & A/D setup

setup();

CTMUCON1bits.CTMUEN = 1;

//Enable the CTMU

for(j=0;j<10;j++)</pre>

{

AD1CON1bits.SAMP = 1;

//Manual sampling start

CTMUCON1bits.IDISSEN = 1;

//drain charge on the circuit

DELAY:

//wait 125us

CTMUCON1bits.IDISSEN = 0;

//end drain of circuit

CTMUCON2bits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

//wait for 125 us

DELAY;

IFSObits.AD1IF = 0;

//make sure A/D Int not set

AD1CON1bits.SAMP = 0;

//and begin A/D conv.

while(!IFSObits.AD1IF);

//Wait for A/D convert complete

AD1CON1bits.DONE = 0;

CTMUCON2bits.EDG1STAT = 0;

//Stop charging circuit

Vread = ADC1BUF0;

//Get the value from the A/D

//Clear A/D Interrupt Flag

IFSObits.AD1IF = 0;

VTot += Vread;

//Add the reading to the total

}

Vavg = (float) (VTot/10.000);

//Average of 10 readings

Vcal = (float) (Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

```

# Example 55-2: Current Calibration Routine for Devices With CTMUCON1 and CTMUCON2 Registers

## 55.5.2 Capacitance Calibration

A small amount of capacitance from the internal A/D Converter sample capacitor and stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken to ensure the desired capacitance to be measured is removed. The measurement is then performed using the following steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time *t*.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances using Equation 55-5.

Equation 55-5:

$$C_{OFFSET} = C_{STRAY} + C_{AD} = \frac{(I \cdot t)}{V}$$

where *I* is known from the current source measurement step, t is a fixed delay and *V* is measured by performing an A/D conversion.

This measured value is then stored and used for calculations of time measurement, or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known. CAD is approximately 4 pF.

An iterative process must be used to adjust the time *t*, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of *t* may be determined by setting *C*OFFSET to a theoretical value, then solving for *t*. For example, if *C*STRAY is theoretically calculated to be 11 pF, and *V* is expected to be 70% of VDD, or 2.31V, *t* would be equal to Equation 55-6 or 63  $\mu$ s.

Equation 55-6: :

$$(4 \ pF + 11 \ pF) \bullet \frac{2.31 V}{0.55 \mu A}$$

A typical routine for CTMU capacitance calibration is shown in Example 55-3.

55

# Example 55-3: Capacitance Calibration Routine for Devices With CTMUCON1 and CTMUCON2 Registers

```

#include "p33Fxxxx.h"

#define COUNT 25 //@ 8MHz INTFRC = 62.5 us.

#define ETIME COUNT*2.5 //time in us

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define ADSCALE 1023 //for unsigned conversion 10 sig bits

//Vdd connected to A/D Vr+

#define ADREF 3.3

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

float CTMUISrc, CTMUCap, Vavg, VTot, Vcal;

//assume CTMU and A/D have been setup correctly

//see Example 11-1 for CTMU & A/D setup

setup();

CTMUCON1bits.CTMUEN = 1;//Enable the CTMU

for(j=0;j<10;j++)</pre>

{

AD1CON1bits.SAMP = 1;

//Manual sampling start

//drain any charge on the circuit

CTMUCON1bits.IDISSEN= 1;

//wait 62.5 us

DELAY:

CTMUCON1bits.IDISSEN = 0;

//end drain of circuit

CTMUCON2bits.EDG1STAT = 1;

//Begin charging the circuit

//using the CTMU current source

DELAY:

//wait for 62.5 us for circuit

//to charge

CTMUCON2bits.EDG1STAT = 0;

//Stop charging circuit and begin

//A/D conversion

AD1CON1bits.SAMP = 0;

while(!IFSObits.AD1IF); //Wait for A/D conversion to complete

Vread = ADC1BUF0; //Get the value from the A/D converter

//Clear AD1IF

IFSObits.AD1IF = 0;

VTot += Vread;

//Add the reading to the total

}

Vavg = (VTot/10); //Average of 10 readings

Vcal = (Vavg/ADSCALE*ADREF);

CTMUCap = (CTMUISrc*ETIME/Vcal)/100;

//CTMUISrc is in 1/100ths of uA,

//calculated in Example 1-2

//time is in us

//CTMUCap is in pF

```

# 55.6 MEASURING CAPACITANCE WITH THE CTMU

The two methods of measuring capacitance with the CTMU are:

- Absolute Capacitance Measurement: The actual capacitance value is required

- Relative Charge Measurement: The actual capacitance value is not required instead an indication of change in capacitance is required.

## 55.6.1 Absolute Capacitance Measurement

For absolute capacitance measurements, both the current and capacitance calibration steps found in **55.5** "**Calibrating the CTMU Module**" should be followed. Capacitance measurements are then performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- 3. Set EDG1STAT.

- 4. Wait for a fixed delay, *T*.

- 5. Clear EDG1STAT.

- 6. Perform an A/D conversion.

- 7. Calculate the total capacitance, CTOTAL = (I \* T)/V, where *I* is known from the current source measurement step (**55.5.1 "Current Source Calibration"**), *T* is a fixed delay and *V* is measured by performing an A/D conversion

- 8. Subtract the stray and A/D capacitance (*COFFSET* from **55.5.2** "Capacitance Calibration") from *CTOTAL* to determine the measured capacitance.

## 55.6.2 Relative Charge Measurement

An application may not require precise capacitance measurements. For example, when detecting a valid press of a capacitance-based switch, detecting a relative change of capacitance is of interest. In this application, when the switch is open (or not touched), the total capacitance is the capacitance of the combination of the board traces, the A/D Converter, etc. A larger voltage will be measured by the A/D Converter. When the switch is closed (or is touched), the total capacitance is larger due to the addition of the capacitance of the human body to the above listed capacitances, and a smaller voltage will be measured by the A/D Converter.

Detecting capacitance changes can be done with the CTMU using these steps:

- 1. Initialize the A/D Converter and the CTMU

- 2. Set EDG1STAT

- 3. Wait for a fixed delay

- 4. Clear EDG1STAT

- 5. Perform an A/D conversion

The voltage measured by performing the A/D conversion is an indication of the relative capacitance. In this case, no calibration of the current source or circuit capacitance measurement is required. A sample software routine for a capacitive touch switch is shown in Example 55-4.

#### #include "p33Fxxxx.h" //@ 8MHz = 125uS. #define COUNT 500 #define DELAY for(i=0;i<COUNT;i++)</pre> #define OPENSW 1000 //Unpressed switch value #define TRIP 300 //Difference between pressed //and unpressed switch //amount to change #define HYST 65 //from pressed to unpressed #define PRESSED 1 #define UNPRESSED0 int main(void) { unsigned int Vread; //storage for reading unsigned int switchState; int i; //assume CTMU and A/D have been setup correctly //see Example 11-1 for CTMU & A/D setup setup(); CTMUCON1bits.CTMUEN = 1; //Enable the CTMU AD1CON1bits.SAMP = 1; //Manual sampling start CTMUCON1bits.IDISSEN = 1; //drain charge on the circuit //wait 125us DELAY: CTMUCON1bits.IDISSEN = 0; //end drain of circuit CTMUCON2bits.EDG1STAT = 1; //Begin charging the circuit //using CTMU current source //wait for 125us DELAY: CTMUCON2bits.EDG1STAT = 0;//Stop charging circuit IFSObits.AD1IF = 0; //make sure A/D Int not set AD1CON1bits.SAMP = 0; //and begin A/D conv. while(!IFSObits.AD1IF); //Wait for A/D convert complete AD1CON1bits.DONE = 0; Vread = ADC1BUF0; //Get the value from the A/D if(Vread < OPENSW - TRIP) { switchState = PRESSED; } else if(Vread > OPENSW - TRIP + HYST) { switchState = UNPRESSED; }

# Example 55-4: Routine for Capacitive Touch Switch for Devices With CTMUCON1 and CTMUCON2 Registers

# 55.7 MEASURING TIME WITH THE CTMU MODULE

Time can be precisely measured after the ratio (C/I) is measured from the current and capacitance calibration step by following these steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Set EDG2STAT.

- 4. Perform an A/D conversion.

- 5. Calculate the time between edges as T = (C/I) \* V, where *I* is calculated in the current calibration step (55.5.1 "Current Source Calibration"), *C* is calculated in the capacitance calibration step (55.5.2 "Capacitance Calibration") and *V* is measured by performing the A/D conversion.

It is assumed that the time measured is small enough that the capacitance *C*OFFSET provides a valid voltage to the A/D Converter. For the smallest time measurement, set the A/D Channel Select register (AD1CHS) to an unused A/D channel; the corresponding pin for which is not connected to any circuit board trace. This minimizes added stray capacitance by keeping the total circuit capacitance close to the A/D Converter (4-5 pF). To measure longer time intervals, an external capacitor may be connected to an A/D channel, and this channel is selected when making a time measurement.

**5** Charge Time Measurement Uni (CTMU)

# 55.8 CREATING A DELAY WITH THE CTMU MODULE

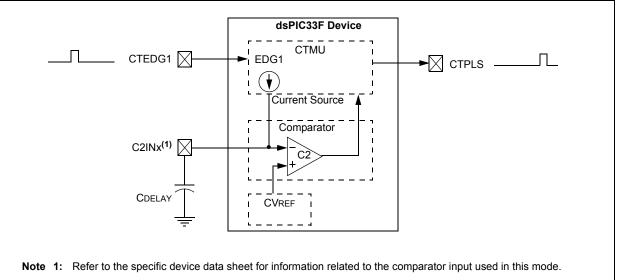

A unique feature of the CTMU module is to generate system clock independent output pulses based on an external capacitor value. This is accomplished using the internal comparator voltage reference module, Comparator 2 input pin and an external capacitor. The pulse is output onto the CTPLS pin. To enable this mode, you need to set the TGEN bit.

An example circuit is illustrated in Figure 55-3. CPULSE is chosen by the user to determine the output pulse width on CTPLS. The pulse width is calculated by T = (CPULSE/I) \* V, where I is known from the current source measurement step (**55.5.1 "Current Source Calibration**") and V is the internal reference voltage (CVREF).

An example use of this feature is for interfacing with variable capacitive-based sensors like a humidity sensor. As the humidity varies, the pulse-width output on CTPLS will vary. The CTPLS output pin can be connected to an input capture pin and the varying pulse width is measured to determine the humidity in the application.

Follow these steps to use this feature:

- 1. Initialize Comparator 2.

- 2. Initialize the comparator voltage reference.

- 3. Initialize the CTMU and enable time delay generation by setting the TGEN bit.

- 4. Set EDG1STAT.

- 5. When *CPULSE* charges to the value of the voltage reference trip point, an output pulse is generated on CTPLS.

# 55.9 MEASURING ON-CHIP TEMPERATURE WITH THE CTMU

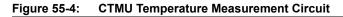

The CTMU module can be used to measure the internal temperature of the device through an internal diode that is available for such purposes. When EDGE1 is not equal to EDGE2 and TGEN = 0, the current is steered into the temperature sensing diode. The voltage across the diode is available as an input to the ADC module (AN13).

Figure 55-4 illustrates how this module can be used for temperature measurement. As the temperature rises, the voltage across the diode will drop by about 300 mV over a 150°C range. Selecting a higher current drive strength will raise the voltage value by a few 100 mV.

At 25°C, the forward voltage of the temperature diode is 0.83V. The rate of change between the forward voltage of the diode and its temperature is 1.87 mV per degree Celsius. The formula shown in Equation 55-7 can be used to calculate the forward voltage.

Equation 55-7: Voltage versus Temperature

$$Vf(\text{in mV}) = 783.24mV + 1.87mV \cdot T$$

Where:

*Vf* = Forward voltage of temperature diode

T = Temperature in degrees Celsius

## 55.10 OPERATION DURING SLEEP OR IDLE MODE

## 55.10.1 Sleep Mode and Deep Sleep Modes

When the device enters any Sleep mode, the CTMU module current source is always disabled. If the CTMU is performing an operation that depends on the current source when Sleep mode is invoked, the operation may not terminate correctly. Capacitance and time measurements may return erroneous values.

## 55.10.2 Idle Mode

The behavior of the CTMU in Idle mode is determined by the CTMUSIDL bit (CTMUCON1<13>). If CTMUSIDL is cleared, the module will continue to operate in Idle mode. If CTMUSIDL is set, the CTMU module's current source is disabled when the device enters Idle mode. If the CTMU module is performing an operation when Idle mode is invoked, the results will be similar to those with Sleep mode.

# 55.11 EFFECTS OF A RESET ON CTMU

Upon Reset, all registers of the CTMU are cleared. This leaves the CTMU module disabled, its current source is turned off and all configuration options return to their default settings. The module needs to be re-initialized following any Reset.

If the CTMU is in the process of taking a measurement at the time of Reset, the measurement will be lost. A partial charge may exist on the circuit that was being measured, and should be properly discharged before the CTMU makes subsequent attempts to make a measurement. The circuit is discharged by setting and then clearing the IDISSEN bit (CTMUCON1<9>) while the A/D Converter is connected to the appropriate channel.

# 55.12 REGISTER MAPS

A summary of the registers associated with the dsPIC33F/PIC24H CTMU is given in Table 55-1.

## Table 55-1: CTMU Register Map

| File Name               | Bit 15  | Bit 14     | Bit 13   | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|---------|------------|----------|--------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------------|

| CTMUCON1 <sup>(1)</sup> | CTMUEN  | _          | CTMUSIDL | TGEN   | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _     | _       | _     | —     | _     | 0000          |

| CTMUCON2 <sup>(1)</sup> | EDG1MOD | EDG1POL    |          | EDG18  | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | EL<3:0> |       | _     | _     | 0000          |

| CTMUICON                |         | ITRIM<5:0> |          |        |          | IRNG     | <1:0>    | _        | _       |         | -     |       | -       | —     |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Refer to the specific device data sheet to determine whether this register is available on your particular device.

© 2010 Microchip Technology Inc.

# 55.13 RELATED APPLICATION NOTES

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the dsPIC33F/PIC24H device family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to the CTMU module are:

## Title

### Application Note #

No related application notes are available.

N/A

**Note:** Visit the Microchip web site (www.microchip.com) for additional application notes and code examples for the dsPIC33F/PIC24H family of devices.

# 55.14 REVISION HISTORY

# Revision A (June 2010)

This is the initial release of this document.

**5** Charge Tin Measurement (CTMU)

Ð

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION. INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-60932-253-3

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

## ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10