# **Section 25. Device Configuration**

## HIGHLIGHTS

This section of the manual contains the following topics:

| 25.1 | Introduction                         | . 25-2 |

|------|--------------------------------------|--------|

| 25.2 | Device Configuration                 | . 25-2 |

| 25.3 | Device Identification                | . 25-5 |

| 25.4 | Unit Identification                  | . 25-6 |

| 25.5 | In-Circuit Programming and Debugging | . 25-6 |

| 25.6 | Related Application Notes            | . 25-7 |

| 25.7 | Revision History                     | .25-8  |

|      |                                      |        |

25

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33F/PIC24H devices.

Please consult the note at the beginning of the "**Special Features**" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

### 25.1 INTRODUCTION

At their highest level of functionality, dsPIC33F/PIC24H devices integrate several features that affect the entire device as a whole. They add convenience and flexibility of design for the user, and allow the devices to be incorporated into a wider range of designs. These include:

- Flexible Configuration Options Allowing users to select a wide range of basic microcontroller operating options and changing them if needed during run time.

- Device Identification Allowing electronic confirmation of a device part number and revision level in the target application.

## 25.2 DEVICE CONFIGURATION

The basic behavior and operation of dsPIC33F/PIC24H devices are set by the device Configuration bits. These bits allow the user to select a wide range of options and optimize the microcontroller's operation to the application's requirements.

In all dsPIC33F/PIC24H family devices, device Configuration bits are mapped to the device's program memory space, starting at location 0xF80000.

The method by which the Configuration bits are programmed differs between major device families. The details are discussed in **25.2.1 "Volatile Memory Implementation**" and **25.2.2 "Nonvolatile Memory Implementation**". See the specific device data sheet for information on which method is implemented for your particular device.

Table 25-1 provides a list of the most common Configuration bit options. Note that this is not a comprehensive list; certain device families will have unique configuration options that are specific to its peripheral set. Each Configuration bit and its operation is described in the relevant section of the "dsPIC33F/PIC24H Family Reference Manual". For more information on Configuration bit mapping of a particular device, refer to the specific device data sheet.

**Note:** All of the bits that are described in Table 25-1 are not present on all the devices. Refer to the specific device data sheet for availability.

#### Table 25-1: Common dsPIC33F/PIC24H Device Configuration Bits

| Configuration Bit | Function                                                                                 |

|-------------------|------------------------------------------------------------------------------------------|

| BSS               | Enables boot segment and sets security level (3 bits, up to 8 configuration options).    |

| BWRP              | Enables boot segment write protection                                                    |

| FNOSC             | Selects the initial (default) device oscillator (3 bits, up to 8 configuration options). |

| FWDTEN            | Enables the Watchdog Timer.                                                              |

| GWRP              | Enables write/erase protection for program memory.                                       |

| IESO              | Enables Two-Speed Start-up.                                                              |

| IOL1WAY           | Selects one-time or unrestricted run-time changes to peripheral mapping.                 |

| JTAGEN            | Enables dedicated JTAG port and disables corresponding I/O ports on designated pins.     |

| OSCIOFCN          | Selects function of OSC2 pin (I/O port or CLKO) in certain external oscillator modes.    |

| POSCMD            | Selects primary (external) oscillator configuration (2 bits, 4 configurations).          |

| WINDIS            | Selects Windowed Operation mode for the Watchdog Timer.                                  |

#### 25.2.1 Volatile Memory Implementation

In Volatile Memory Implementation for dsPIC33F/PIC24H devices, the Configuration bits are implemented as volatile memory; that is, the configuration data must be loaded each time the device is powered up. The actual configuration data is stored in the last several words at the end of the on-chip program memory space, known as the Configuration Words (abbreviated as CW). During all types of device Resets, the configuration data is automatically loaded from the Configuration Words to the proper Configuration registers.

The CWs are 16-bit, packed representations of the actual device Configuration bits; the actual locations of which are distributed among several locations in configuration space. The number of CWs implemented for a particular device family depends on the device's feature set and configuration options. Refer to the specific device data sheet for part-specific implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various configuration options. To prevent inadvertent configuration changes during code execution, all programmable device Configuration bits are write-once. After a bit is initially written during a power cycle or any Reset, it cannot be written to again. Any change of a Configuration bit (not a change to a Flash Configuration Word) causes a Configuration Mismatch (CM) Reset, which then forces a reload of the original values.

#### 25.2.1.1 CONSIDERATIONS WHEN USING FLASH CONFIGURATION WORDS

The upper byte of all the Flash Configuration Words in the program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since the Configuration bits are not implemented in the corresponding locations, writing '1' to these locations has no effect on device operation.

As mentioned previously, changes to the actual device Configuration bits during run time would cause a Configuration Mismatch Reset. This does not prevent changes to Flash Configuration Words during normal operation. This also makes it possible for an application to change its hardware configuration by writing new data to these Flash Configuration Words, and then executing a RESET command, which results in reloading the new values.

#### 25.2.2 Nonvolatile Memory Implementation

With nonvolatile memory implementation, the Configuration bits are implemented as a physically separate block of nonvolatile memory. Once programmed, configuration data is maintained indefinitely. Although they act like fuses, the Configuration bits are freely reprogrammable. Since they lie inside the configuration memory space, the Configuration bits are not directly accessible; they can only be written and read using table read and table write instructions.

Unlike volatile memory implementation devices, the Configuration bits with nonvolatile memory implementation devices are organized into 8-bit registers, always the Least Significant Byte (LSB) of a program memory address. These Configuration registers are symbolically named according to their primary function (i.e., General Segment protection, Oscillator Selection, and so on). Table 25-2 lists the typical names and address of Configuration registers. Note that not all Configuration registers are implemented on all devices and certain devices with extended feature sets may have additional registers. In addition, there may be variations in naming or location of registers in certain devices. Refer to the specific device data sheet for specific information.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various configuration options.

The implementation of the Configuration bits in devices using nonvolatile memory implementation makes a Configuration Mismatch (CM) error and Reset during full-speed operation virtually impossible. However, a severe device disturbance (such as an ESD event) during Sleep may disrupt the configuration safety check, resulting in a CM Reset.

| Register Name | Primary Function         | Address  |  |  |

|---------------|--------------------------|----------|--|--|

| FBS           | Boot Segment Protect     | 0xF80000 |  |  |

| FGS           | General Segment Protect  | 0xF80004 |  |  |

| FOSCEL        | Oscillator Select        | 0xF80006 |  |  |

| FOSC          | Oscillator Configure     | 0xF80008 |  |  |

| FWDT          | Watchdog Timer Configure | 0xF8000A |  |  |

| FPOR          | Reset Configure          | 0xF8000C |  |  |

| FICD          | Debug Configure          | 0xF8000E |  |  |

Table 25-2: Typical Configuration Registers

## 25.3 DEVICE IDENTIFICATION

dsPIC33F/PIC24H devices have two read-only registers that provide device-specific identification information. These are located near the end of the program memory space, starting at 0xFF0000. Like the Flash Configuration Words, the Device ID registers are 24 bits wide and the upper 8 bits are unimplemented. Both registers can be read using table read instructions.

The DEVID register at 0xFF0000 (Register 25-1) identifies the Microchip microcontroller architectural family and the specific part number. The DEVREV register at 0xFF0002 (Register 25-2) identifies the particular silicon revision for that device in terms of major and minor revision levels ("letter and dot revision" format).

For any given family of dsPIC33F/PIC24H devices, the corresponding Family Silicon Errata and Data Sheet Clarification document provides a list of values for DEVID and the corresponding part numbers for that family. The association of the value of DEVREV to a silicon revision level is different for each part number. The translation of a DEVREV value to a revision level can be found in the associated Family Silicon Errata and Data Sheet Clarification document.

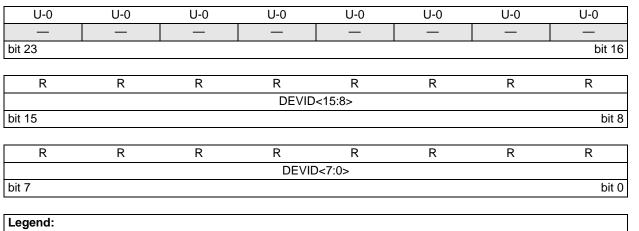

Register 25-1: DEVID: Device ID Register

R = Readable bit U = Unimplemented bit, read as '0'

bit 23-16 Unimplemented: Read as '0'

bit 15-0 DEVID<15:0>: Device ID Value bits

#### Register 25-2: DEVREV: Device Revision Register

|                                        |           | DEVICE REVISION REgister |                                    |         |                 |        |        |  |  |

|----------------------------------------|-----------|--------------------------|------------------------------------|---------|-----------------|--------|--------|--|--|

| U-0                                    | U-0       | U-0                      | U-0                                | U-0     | U-0             | U-0    | U-0    |  |  |

| -                                      | —         | —                        | —                                  |         | —               | —      | —      |  |  |

| bit 23                                 |           |                          |                                    |         |                 |        | bit 16 |  |  |

| R                                      | R         | R                        | R                                  | R       | R               | R      | R      |  |  |

|                                        |           |                          | DEVRE                              | √<15:8> |                 |        |        |  |  |

| bit 15                                 |           |                          |                                    |         |                 |        | bit 8  |  |  |

| R                                      | R         | R                        | R                                  | R       | R               | R      | R      |  |  |

|                                        |           |                          | DEVRE                              | V<7:0>  |                 |        |        |  |  |

| bit 7                                  |           |                          |                                    |         |                 |        | bit C  |  |  |

| Legend:                                |           |                          |                                    |         |                 |        |        |  |  |

| R = Readable bit                       | t         |                          | U = Unimplemented bit, read as '0' |         |                 |        |        |  |  |

| R = Readable bit<br>bit 23-16 <b>U</b> | nimplemen | nted: Read as '0'        | 3                                  | ·       | ented bit, read | as '0' |        |  |  |

25

© 2010 Microchip Technology Inc.

## 25.4 UNIT IDENTIFICATION

Some devices may feature programmable Unit ID registers (FUIDx), which can be programmed by the user with unique device information. Refer to the specific device data sheet for FUIDx availability and memory locations.

## 25.5 IN-CIRCUIT PROGRAMMING AND DEBUGGING

#### 25.5.1 In-Circuit Serial Programming™ (ICSP™)

The ICSP<sup>™</sup> capability is Microchip's proprietary process for microcontroller programming in the target application. The ICSP interface uses two pins as its core. The programming data pin (PGEDx) functions as both an input and an output, allowing programming data to be read in and device information to be read out on command. The programming clock pin (PGECx) clocks in data and controls the overall process.

Serial programming allows customers to manufacture boards with unprogrammed devices and then to program the digital signal controller just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. For more details on ICSP, refer to the "*dsPIC33F/PIC24H Flash Programming Specification*" (DS70152).

Any of the following three pairs of programming clock/data pins can be used:

- PGEC1/PGED1

- PGEC2/PGED2

- PGEC3/PGED3

During programming, each pin pair is recognized as a valid programming connection. Therefore, no special selection is to be performed by the user to specify which pin pair will be used for programming.

#### 25.5.2 In-Circuit Debugger

When the MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> in-circuit emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging when used with MPLAB IDE. The debugging functionality is controlled through the PGECx (emulation/debug clock) and PGEDx (emulation/debug data) pin functions.

Any of the following three pairs of debugging clock/data pins can be used:

- PGEC1/PGED1

- PGEC2/PGED2

- PGEC3/PGED3

The debugging clock and data pins must be selected by programming the ICD Communication Channel Select Enable bits (ICS<1:0>) in the In-Circuit Debugger Configuration register (FICD<1:0>). To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss, and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

## 25.6 RELATED APPLICATION NOTES

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the dsPIC33F/PIC24H product family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to Device Configuration include the following:

#### Title

#### Application Note #

No related application notes at this time.

N/A

**Note:** Please visit the Microchip web site (www.microchip.com) for additional Application Notes and code examples for the dsPIC33F/PIC24H family of devices.

Configuration

## 25.7 REVISION HISTORY

#### **Revision A (February 2007)**

This is the initial release of this section.

#### **Revision B (February 2007)**

Minor edits throughout document.

## Revision C (January 2008)

This revision includes the following corrections and updates:

- Sections:

- Added 25.3.6 "JTAG Interface"

- Added 25.3.7 "In-Circuit Serial Programming™ (ICSP™)"

- Added 25.4.2 "In-Circuit Debugger"

- Registers:

- Updated FOSCSEL: Oscillator Source Selection register (see Register 25-4)

- Updated FPOR: POR Configuration register (see Register 25-7)

- Added FICD: In-Circuit Debugger Configuration register (see Register 25-8)

- Tables:

- Updated register map table (see Table 25-1)

#### Revision D (January 2009)

This revision includes the following corrections and updates:

- Registers:

- Added the PLLKEN bit to the Watchdog Timer Configuration (FWDT) register (see Register 25-6).

- Removed the BKBUG and COE bits from the In-Circuit Debugger Configuration (FICD) register (see Register 25-8).

- Updated 25.3.2 "Oscillator Configuration Bits" to include a reference to the PLLKEN bit

- Additional minor corrections such as language and formatting updates have been incorporated throughout the document.

### Revision E (August 2009)

This revision includes the following corrections and updates:

- Note:

- Added a note in Register 25-7.

- Registers:

- Updated unimplemented bits to read as '0' in all the registers:

- U = Unimplemented bit, read as '1' is updated as U = Unimplemented bit, read as '0'.

- Added new bit name and bit descriptions for bit 5 and bit 6 in Register 25-7.

- Updated the bit name as "r" for bit 6 and bit 7 in Register 25-8.

- Updated the Legend "r = Reserved" in Register 25-8.

- Added the FCMP: Comparator Configuration Register (see Register 25-9).

- Sections:

- Updated the **25.3.7** "In-Circuit Serial Programming™ (ICSP™)" section for selection of programming pins.

- Changed all instances of PGCx/EMUCx and PGDx/EMUDx (where x = 1, 2, or 3) to PGECx and PGEDx

- Removed the Register Map section (Section 25.5).

- Additional minor corrections such as language and format updates have been incorporated throughout the document.

## Revision F (June 2010)

This revision includes the following changes:

- Updated the entire document for the purpose of maintaining consistency with other Microchip family reference manual sections.

- Changed the document name from dsPIC33F Family Reference Manual to dsPIC33F/PIC24H Family Reference Manual.

- All references to dsPIC33F in the document are updated to dsPIC33F/PIC24H.

- Notes:

- Added a shaded note at the beginning of the section, which provides information on complimentary documentation.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-60932-272-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820