# Section 25. USB On-The-Go (OTG)

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 25.1 | Introduction                              |  |

|------|-------------------------------------------|--|

| 25.2 | Control Registers                         |  |

| 25.3 | Operation                                 |  |

| 25.4 | Host Mode Operation                       |  |

| 25.5 | Interrupts                                |  |

| 25.6 | Operation in Debug and Power-Saving Modes |  |

| 25.7 | Effects of a Reset                        |  |

| 25.8 | Related Application Notes                 |  |

| 25.9 | Revision History                          |  |

25 USB On-1

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33E/PIC24E devices.

Please consult the note at the beginning of the "**USB On-The-Go (OTG)**" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

# 25.1 INTRODUCTION

The dsPIC33E/PIC24E Universal Serial Bus (USB) On-The-Go (OTG) module includes the following features:

- USB Full-Speed Support for Host and Device

- · Low-Speed Host Support

- USB On-The-Go (OTG) Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- · Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated Bus Master to Access System RAM

- Does not require the dsPIC33E/PIC24E DMA module for its operation

- Supports external USB transceiver and external VBUS comparator

The USB module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

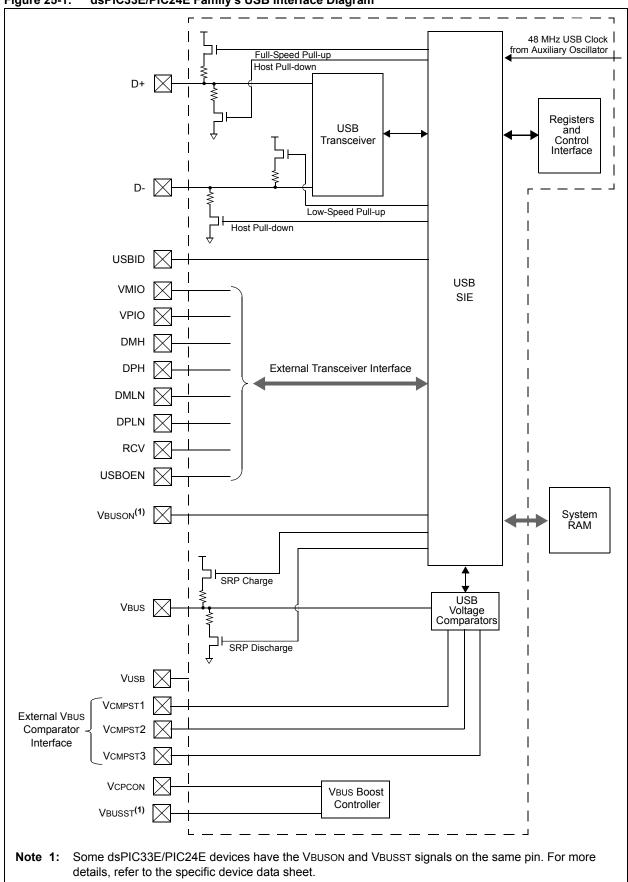

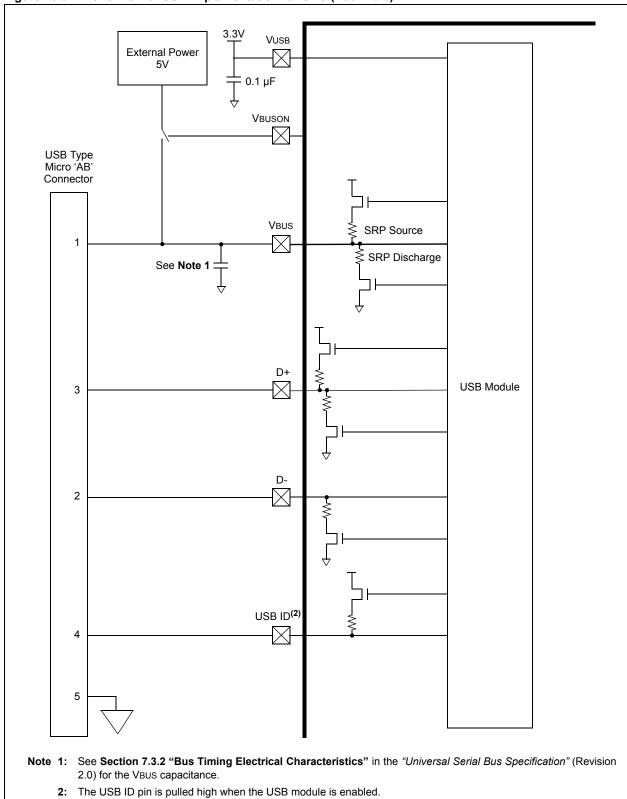

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB Bus Master, pull-up and pull-down resistors and the register interface. A block diagram of the dsPIC33E/PIC24E USB OTG module is illustrated in Figure 25-1.

The USB module requires a 48 MHz clock for USB full-speed and low-speed communication, which is supplied via a device auxiliary oscillator. The module requires an external supply of +3.3V to be connected to the VUSB pin. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The application can disable the internal VBUS voltage comparators and use an external VBUS voltage comparator. A flexible, external digital VBUS comparator interface is available for this purpose. The transceiver provides the analog translation between the USB bus and the digital logic. An external USB transceiver interface is available. In applications, where an external transceiver is preferred, the internal transceiver of the USB module can be disabled.

The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB Bus Master transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

**Note:** The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# 25.2 CONTROL REGISTERS

The USB module includes the following control and status registers:

UxOTGSTAT: USB OTG Status Register

This register provides access to the status of the V ${\sf B}{\sf U}{\sf S}$  voltage comparators and the debounced status of the ID pin.

UxOTGCON: USB On-The-Go Control Register

This register controls the operation of the VBUS pin and the pull-up and pull-down resistors.

UxPWRC: USB Power Control Register

This register controls the power-saving modes.

UxSTAT: USB Status Register

This register is a 16-deep FIFO. It is read-only by the CPU and read/write by the USB module. It is only valid when the TRNIF bit (UxIR<3>) is set.

• UxCON: USB Control Register (Device mode) and UxCON: USB Control Register (Host mode)

This register provides various control information for the module.

### UxADDR: USB Address Register

This register is read/write from the CPU side and read-only from the USB module side. Although the register values affect the settings of the USB module, the content of the registers does not change during access.

In Device mode, this address defines the USB device address as assigned by the host during the SETUP phase. The firmware writes the address in response to the SETUP request. The address is automatically reset when a USB bus Reset is detected.

In Host mode, the module transmits the address provided in this register with the corresponding token packet. This allows the USB module to uniquely address the connected device.

### • UxTOK: USB Token Register (Host mode only)

This read/write register is required when the module operates as a host. It is used to specify the token type, PID<3:0>, and the endpoint, EP<3:0>, being addressed by the host processor. Writing to this register triggers a host transaction.

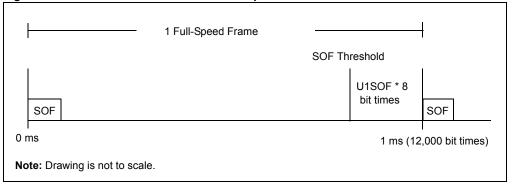

• UxSOF: USB OTG Start-of-Token Threshold Register (Host mode only)

This read/write register contains the count bits of the Start of Frame (SOF) Threshold Value used in Host mode only.

To prevent collision between a packet data with the Start of Frame token, which is sent every 1 ms, the USB module will not send any new transactions within the last UxSOF byte times. The USB module completes the transactions that are in progress. The SOF interrupt occurs when this threshold is reached, not when the SOF occurs. Transactions started within the SOF threshold are held by the USB module until the SOF token is sent.

### • UxCNFG1: USB Configuration Register 1

This read/write register controls the debug and idle behavior of the module. The register must be preprogrammed prior to enabling the module.

• UxCNFG2: USB Configuration Register 2

This read/write register configures the interface signals.

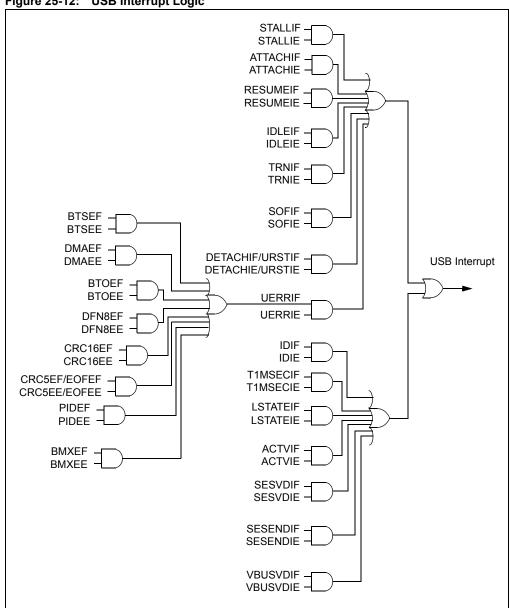

UxOTGIR: USB OTG Interrupt Status Register (Host mode only)

This register records the changes of the ID and VBUS pins to enable software to determine the event causing an interrupt. The interrupt bits are cleared by writing a '1' to the respective interrupt.

### UxOTGIE: USB OTG Interrupt Enable Register (Host mode only)

This register enables the corresponding interrupt status bits defined in the UxOTGIR register.

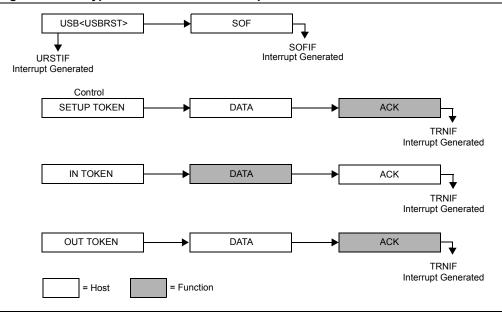

• UxIR: USB Interrupt Status Register (Device mode only) and UxIR: USB Interrupt Status Register (Host mode only)

This register contains information on pending interrupts. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

• UxIE: USB Interrupt Enable Register (Device mode) and UxIE: USB Interrupt Enable Register (Host mode)

This register's values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the respective interrupt source in the UxIR register.

UxEIR: USB Error Interrupt Status Register (Device mode) and UxEIR: USB Error Interrupt Status Register (Host mode)

This register contains information on pending error interrupt values. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

• UxEIE: USB Error Interrupt Enable Register (Device mode) and UxEIE: USB Error Interrupt Enable Register (Host mode)

This register's values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the respective interrupt source in the UxEIR register.

• UxEPn: USB Endpoint n Control Registers (n = 0 to 15)

These registers control the behavior of the corresponding endpoint.

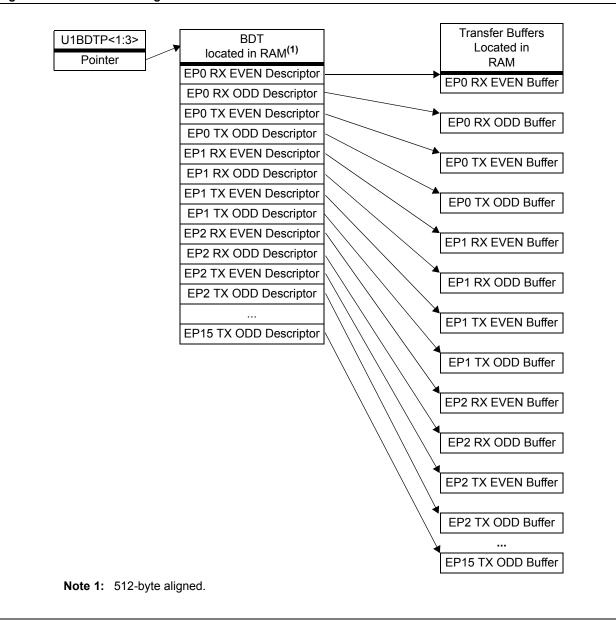

• UxBDTPx: USB Buffer Description Table Registers (Register 25-23, Register 25-24 and Register 25-25)

These read/write registers define the bits (31-9) of the 32-bit base address of the endpoint Buffer Descriptor Table (BDT) in the system memory.

UxPWMCON: USB VBUS PWM Generator Control Register

This register provides various bits for controlling the VBUS Boost Regulator PWM module.

• UxPWMRRS: Duty Cycle and PWM Period Register

This register specifies the duty cycle and PWM period for the VBUS Boost Regulator PWM module.

UxFRMH: USB Frame Number High Register and UxFRML: USB Frame Number Low Register

These registers are read-only registers. The frame number is formed by concatenating the two 8-bit registers. The high-order byte is in the UxFRMH register and the low-order byte is in the UxFRML register.

# 25.2.1 Clearing USB OTG Interrupts

Unlike device level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware set-only bits. Additionally, these bits can only be cleared in software by writing a '1' to their locations. Writing a '0' to a flag bit has no effect.

# 25.2.2 Registers Description

# Register 25-1: UxOTGSTAT: USB OTG Status Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       |     | LSTATE   | —   | SESVD    | SESEND   |     | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | U = Unimplemented bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | HSC = Hardware Settal              | ble/Clearable bit  |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                            |

|          | <ul> <li>1 = No cable is attached or a Type B plug has been plugged into the USB receptacle</li> <li>0 = Type A plug is plugged into the USB receptacle</li> </ul>                        |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                   |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has NOT been stable for the previous 1 ms</li> </ul> |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                        |

|          | <ul> <li>1 = VBUS voltage is above session valid on the A or B device</li> <li>0 = VBUS voltage is below session valid on the A or B device</li> </ul>                                    |

| bit 2    | SESEND: B-Session End Indicator bit                                                                                                                                                       |

|          | <ul> <li>1 = VBUS voltage is below session valid on the B device</li> <li>0 = VBUS voltage is above session valid on the B device</li> </ul>                                              |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 0    | VBUSVD: A-VBUS Valid Indicator bit                                                                                                                                                        |

|          | <ul> <li>1 = VBUS voltage is above session valid on the A device</li> <li>0 = VBUS voltage is below session valid on the A device</li> </ul>                                              |

| U-0          | U-0                                                                                                                     | U-0                                | U-0                        | U-0                   | U-0                  | U-0                    | U-0                    |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|-----------------------|----------------------|------------------------|------------------------|--|--|--|

| _            | _                                                                                                                       | —                                  | —                          | —                     | _                    | —                      | _                      |  |  |  |

| bit 15       |                                                                                                                         | ·                                  |                            | •                     |                      |                        | bit 8                  |  |  |  |

|              |                                                                                                                         |                                    |                            |                       |                      |                        |                        |  |  |  |

| R/W-0        | R/W-0                                                                                                                   | R/W-0                              | R/W-0                      | R/W-0                 | R/W-0                | R/W-0                  | R/W-0                  |  |  |  |

| DPPULUP      | DMPULUP                                                                                                                 | DPPULDWN <sup>(1)</sup>            | DMPULDWN <sup>(1)</sup>    | VBUSON <sup>(1)</sup> | OTGEN <sup>(1)</sup> | VBUSCHG <sup>(1)</sup> | VBUSDIS <sup>(1)</sup> |  |  |  |

| bit 7        |                                                                                                                         |                                    |                            |                       |                      |                        | bit C                  |  |  |  |

|              |                                                                                                                         |                                    |                            |                       |                      |                        |                        |  |  |  |

| Legend:      |                                                                                                                         |                                    |                            |                       |                      |                        |                        |  |  |  |

| R = Readab   | ole bit                                                                                                                 | W = Writable bi                    | t                          | U = Unimplen          | nented bit, rea      | ad as '0'              |                        |  |  |  |

| -n = Value a | at POR                                                                                                                  | '1' = Bit is set                   |                            | '0' = Bit is clea     | ared                 | x = Bit is unkr        | nown                   |  |  |  |

|              |                                                                                                                         |                                    |                            |                       |                      |                        |                        |  |  |  |

| bit 15-8     | Unimpleme                                                                                                               | nted: Read as '0'                  |                            |                       |                      |                        |                        |  |  |  |

| bit 7        |                                                                                                                         | D+ Pull-Up Enabl                   |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | a line pull-up resis               |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | a line pull-up resis               |                            |                       |                      |                        |                        |  |  |  |

| bit 6        | DMPULUP: D- Pull-Up Enable bit                                                                                          |                                    |                            |                       |                      |                        |                        |  |  |  |

|              | <ul> <li>1 = D- data line pull-up resistor is enabled</li> <li>0 = D- data line pull-up resistor is disabled</li> </ul> |                                    |                            |                       |                      |                        |                        |  |  |  |

| bit 5        |                                                                                                                         | I: D+ Pull-Down E                  |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | a line pull-down re                |                            | I                     |                      |                        |                        |  |  |  |

|              |                                                                                                                         | a line pull-down re                |                            |                       |                      |                        |                        |  |  |  |

| bit 4        | DMPULDW                                                                                                                 | N: D- Pull-Down E                  | Enable bit <sup>(1)</sup>  |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | i line pull-down re                |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | i line pull-down re                |                            |                       |                      |                        |                        |  |  |  |

| bit 3        |                                                                                                                         | BUS Power-on bit                   | (1)                        |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | ne is powered<br>ne is not powered | 4                          |                       |                      |                        |                        |  |  |  |

| bit 2        |                                                                                                                         | G Features Enab                    |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | TG is enabled; al                  |                            | and null-downs        | hits are enab        | led                    |                        |  |  |  |

|              |                                                                                                                         | TG is disabled; D                  |                            |                       |                      |                        | he settings o          |  |  |  |

|              |                                                                                                                         | STEN and USBE                      |                            |                       |                      |                        | Ū                      |  |  |  |

| bit 1        | VBUSCHG:                                                                                                                | VBUS Charge Sel                    | lection bit <sup>(1)</sup> |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | ne is set to charg                 |                            |                       |                      |                        |                        |  |  |  |

|              |                                                                                                                         | ne is set to charg                 |                            |                       |                      |                        |                        |  |  |  |

| bit 0        |                                                                                                                         | BUS Discharge E                    |                            |                       |                      |                        |                        |  |  |  |

|              | 1 = VBUS li                                                                                                             | ne is discharged                   | through a resisto          | ſ                     |                      |                        |                        |  |  |  |

|              |                                                                                                                         | ne is not discharg                 | -                          |                       |                      |                        |                        |  |  |  |

# Register 25-2: UxOTGCON: USB On-The-Go Control Register

**Note 1:** These bits are only used in Host mode; do not use in Device mode.

2 USB On-The-Go (OTG)

| U-0                         | U-0   | U-0              | U-0            | U-0                                | U-0 | U-0                | U-0                   |

|-----------------------------|-------|------------------|----------------|------------------------------------|-----|--------------------|-----------------------|

| —                           | _     | —                | —              | —                                  | —   | —                  | —                     |

| bit 15                      |       |                  |                |                                    |     |                    | bit 8                 |

|                             |       |                  |                |                                    |     |                    |                       |

| HS, HC-x                    | U-0   | U-0              | R/W            | U-0                                | U-0 | R/W-0, HC          | R/W-0                 |

| UACTPND                     | —     | —                | USLPGRD        | —                                  | —   | USUSPND            | USBPWR <sup>(1)</sup> |

| bit 7                       |       |                  |                |                                    |     |                    | bit 0                 |

|                             |       |                  |                |                                    |     |                    |                       |

| Legend: HS = Hardware Setta |       |                  | e Settable bit | HC = Hardware Clearable bit        |     |                    |                       |

| R = Readable                | e bit | W = Writable b   | bit            | U = Unimplemented bit, read as '0' |     |                    |                       |

| -n = Value at               | POR   | '1' = Bit is set |                | '0' = Bit is cleared x             |     | x = Bit is unknown |                       |

| Register 25-3: | UxPWRC: USB Power Control Register |

|----------------|------------------------------------|

|----------------|------------------------------------|

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | UACTPND: USB Activity Pending bit                                                                                                                              |

|          | <ul> <li>1 = Module should not be suspended at the moment (requires the USLPGRD bit to be set)</li> <li>0 = Module can be suspended or powered down</li> </ul> |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                     |

| bit 4    | USLPGRD: Sleep Guard bit                                                                                                                                       |

|          | <ul> <li>1 = Indicates to the USB module that it is about to be suspended or powered down</li> <li>0 = No suspend</li> </ul>                                   |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1    | USUSPND: USB Suspend Mode Enable bit                                                                                                                           |

|          | 1 = USB OTG module is in Suspend mode                                                                                                                          |

|          | 0 = Normal USB OTG operation                                                                                                                                   |

| bit 0    | USBPWR: USB Operation Enable bit <sup>(1)</sup>                                                                                                                |

|          | 1 = USB OTG module is enabled                                                                                                                                  |

|          | 0 = USB OTG module is disabled                                                                                                                                 |

**Note 1:** Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (UxCON<3,0> and UxOTGCON<2>) are cleared.

| U-0           | U-0                                      | U-0                            | U-0              | U-0                                | U-0            | U-0             | U-0                           |  |  |

|---------------|------------------------------------------|--------------------------------|------------------|------------------------------------|----------------|-----------------|-------------------------------|--|--|

|               | _                                        | _                              | _                | _                                  | —              |                 | _                             |  |  |

| bit 15        |                                          |                                |                  |                                    | •              |                 | bit 8                         |  |  |

|               |                                          |                                |                  |                                    |                |                 |                               |  |  |

| R-0, HSC      | R-0, HSC                                 | R-0, HSC                       | R-0, HSC         | R-0, HSC                           | R-0, HSC       | U-0             | U-0                           |  |  |

|               | ENDP                                     | T<3:0> <sup>(1)</sup>          |                  | DIR                                | PPBI           | —               | —                             |  |  |

| bit 7         |                                          |                                |                  |                                    |                |                 | bit 0                         |  |  |

|               |                                          |                                |                  |                                    |                |                 |                               |  |  |

| Legend:       |                                          | HSC = Hardwa                   | are Settable/Cle | earable bit                        |                |                 |                               |  |  |

| R = Readabl   | le bit                                   | W = Writable b                 | bit              | U = Unimplemented bit, read as '0' |                |                 |                               |  |  |

| -n = Value at | t POR                                    | '1' = Bit is set               |                  | '0' = Bit is clea                  | ared           | x = Bit is unkr | <pre>c = Bit is unknown</pre> |  |  |

| bit 15-8      | Unimplemer                               | nted: Read as '                | ٦,               |                                    |                |                 |                               |  |  |

| bit 7-4       | ENDPT<3:0>                               | >: Number of the last USB tran | e Last Endpoin   | t Activity bits (re                | presents the n | umber of the e  | ndpoint BDT                   |  |  |

|               | 1111 <b>= Endp</b><br>1110 <b>= Endp</b> |                                |                  |                                    |                |                 |                               |  |  |

|               | •                                        |                                |                  |                                    |                |                 |                               |  |  |

|               | •                                        |                                |                  |                                    |                |                 |                               |  |  |

|               | •                                        |                                |                  |                                    |                |                 |                               |  |  |

|               | 0001 = Endp<br>0000 = Endp               |                                |                  |                                    |                |                 |                               |  |  |

| bit 3         | DIR: Last Bu                             | ffer Descriptor [              | Direction Indica | tor bit                            |                |                 |                               |  |  |

|               |                                          |                                |                  |                                    |                |                 |                               |  |  |

# Register 25-4: UxSTAT: USB Status Register

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD buffer descriptor bank

- 0 = The last transaction was to the EVEN buffer descriptor bank

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** In Host mode, all transactions are processed through Endpoint 0 and the Endpoint 0 BDTs. Therefore, ENDPT<3:0> will always read as '0000'.

| U-0          | U-0                                                                                                                                                  | U-0                                 | U-0                | U-0                   | U-0              | U-0                   | U-0           |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|-----------------------|------------------|-----------------------|---------------|--|--|--|

| _            | —                                                                                                                                                    | —                                   | _                  | —                     | _                | —                     | _             |  |  |  |

| bit 15       |                                                                                                                                                      |                                     |                    |                       |                  |                       | bit 8         |  |  |  |

| U-0          | R-x HSC                                                                                                                                              | R/W-0                               | U-0                | R/W-0                 | R/W-0            | R/W-0                 | R/W-0         |  |  |  |

| _            | SE0                                                                                                                                                  | PKTDIS                              |                    | HOSTEN <sup>(1)</sup> | RESUME           | PPBRST <sup>(2)</sup> | USBEN         |  |  |  |

| bit 7        |                                                                                                                                                      |                                     |                    |                       |                  |                       | bit           |  |  |  |

| Legend:      |                                                                                                                                                      | U = Unimpleme                       | antod bit road     | ac '0'                |                  |                       |               |  |  |  |

| R = Readat   | alo hit                                                                                                                                              | W = Writable b                      |                    | HSC = Hardwa          | ara Sattabla/C   | lographo bit          |               |  |  |  |

| -n = Value a |                                                                                                                                                      | '1' = Bit is set                    | п                  | '0' = Bit is clea     |                  | x = Bit is unkno      |               |  |  |  |

|              |                                                                                                                                                      | I - DILIS SEL                       |                    |                       | areu             |                       |               |  |  |  |

| bit 15-7     | Unimpleme                                                                                                                                            | nted: Read as '0                    | ,                  |                       |                  |                       |               |  |  |  |

| bit 6        | SE0: Live Single-Ended Zero Flag bit <sup>(3)</sup>                                                                                                  |                                     |                    |                       |                  |                       |               |  |  |  |

|              | 1 = Single-ended zero active on the USB bus                                                                                                          |                                     |                    |                       |                  |                       |               |  |  |  |

|              | 0 = No single-ended zero detected                                                                                                                    |                                     |                    |                       |                  |                       |               |  |  |  |

| oit 5        | PKTDIS: Packet Transfer Disable bit                                                                                                                  |                                     |                    |                       |                  |                       |               |  |  |  |

|              |                                                                                                                                                      | en and packet pr<br>en and packet p |                    |                       | atically set whe | en a SETUP toke       | en is receive |  |  |  |

| bit 4        | Unimpleme                                                                                                                                            | nted: Read as '0                    | 3                  |                       |                  |                       |               |  |  |  |

| bit 3        | HOSTEN: Host Mode Enable bit <sup>(1)</sup>                                                                                                          |                                     |                    |                       |                  |                       |               |  |  |  |

|              | 1 = USB host capability is enabled; pull-downs on D+ and D- are activated in hardware                                                                |                                     |                    |                       |                  |                       |               |  |  |  |

|              |                                                                                                                                                      | ost capability is d                 |                    |                       |                  |                       |               |  |  |  |

| bit 2        | RESUME: Resume Signaling Enable bit                                                                                                                  |                                     |                    |                       |                  |                       |               |  |  |  |

|              | 1 = Resume signaling is activated                                                                                                                    |                                     |                    |                       |                  |                       |               |  |  |  |

| L:1 4        | 0 = Resume signaling is disabled                                                                                                                     |                                     |                    |                       |                  |                       |               |  |  |  |

| bit 1        | PPBRST: Ping-Pong Buffers Reset bit <sup>(2)</sup>                                                                                                   |                                     |                    |                       |                  |                       |               |  |  |  |

|              | <ul> <li>1 = Reset all Ping-Pong Buffer Pointers to the EVEN buffer descriptor banks</li> <li>0 = Ping-Pong Buffer Pointers are not reset</li> </ul> |                                     |                    |                       |                  |                       |               |  |  |  |

| bit 0        | 0                                                                                                                                                    | B Module Enable                     |                    |                       |                  |                       |               |  |  |  |

|              |                                                                                                                                                      | odule and supp                      |                    | are enabled (d        | levice attache   | d); D+ pull-up is     | activated i   |  |  |  |

|              |                                                                                                                                                      | odule and suppo                     | orting circuitry a | are disabled (de      | vice detached    | )                     |               |  |  |  |

| Note 1:      | This bit should b                                                                                                                                    | e '0' in Device n                   | nodo               |                       |                  |                       |               |  |  |  |

| Note 1:      |                                                                                                                                                      |                                     | USB module f       |                       |                  |                       |               |  |  |  |

# Register 25-5: UxCON: USB Control Register (Device mode)

- 2: Keeping this bit set will force the USB module to always use the EVEN buffer descriptors. The ping-pong feature gets disabled.

- **3:** While this bit indicates the single-ended zero condition on the bus, it is recommended that the application uses the URSTIF bit (UxIR<0>) to detect a RESET condition.

| U-0           | U-0                                                           | U-0                                                                                                                                            | U-0                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0              | U-0                          | U-0          |  |  |  |  |

|---------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|--------------|--|--|--|--|

|               |                                                               |                                                                                                                                                | _                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | _                            | —            |  |  |  |  |

| bit 15        |                                                               |                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                              | bit 8        |  |  |  |  |

|               |                                                               |                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                              |              |  |  |  |  |

| R-x, HSC      | R-x, HSC                                                      | R/W-0                                                                                                                                          | R/W-0                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            | R/W-0                        | R/W-0        |  |  |  |  |

| JSTATE        | SE0                                                           | TOKBUSY                                                                                                                                        | USBRST                     | HOSTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RESUME           | PPBRST <sup>(1)</sup>        | SOFEN        |  |  |  |  |

| bit 7         |                                                               | <u> </u>                                                                                                                                       |                            | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |                              | bit 0        |  |  |  |  |

|               |                                                               |                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                              |              |  |  |  |  |

| Legend:       |                                                               | U = Unimplem                                                                                                                                   | ented bit, read            | as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                              |              |  |  |  |  |

| R = Readable  | le bit                                                        | W = Writable b                                                                                                                                 | bit                        | HSC = Hardw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vare Settable/Cl | learable bit                 |              |  |  |  |  |

| -n = Value at | t POR                                                         | '1' = Bit is set                                                                                                                               |                            | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ared             | x = Bit is unkn              | iown         |  |  |  |  |

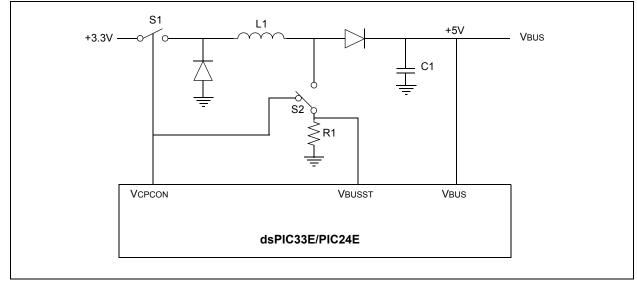

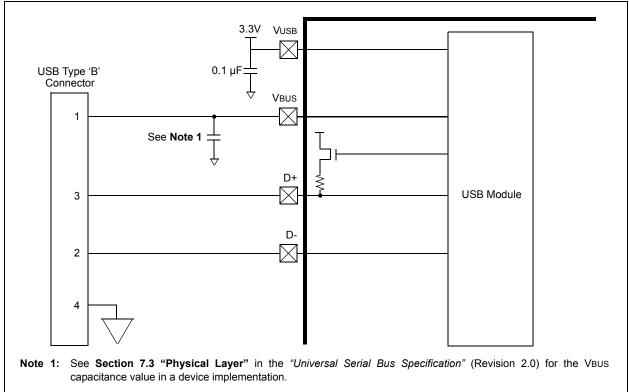

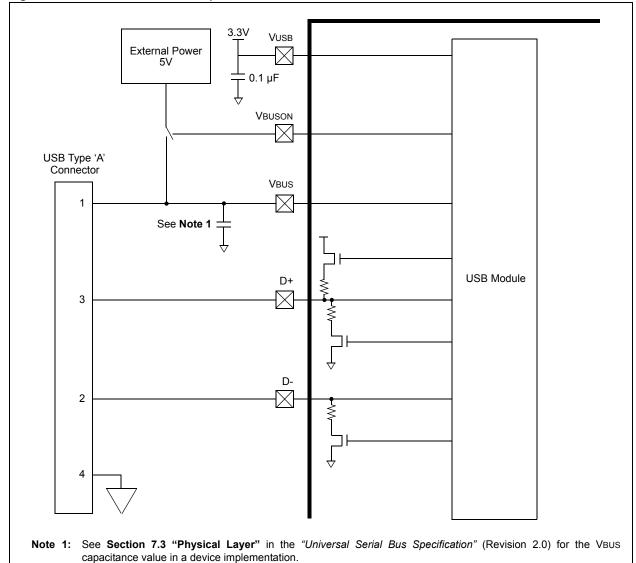

|               |                                                               |                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                              |              |  |  |  |  |