# Section 35. Ethernet Controller

## HIGHLIGHTS

This section of the manual contains the following topics:

| 35.1  | Introduction                              |      |

|-------|-------------------------------------------|------|

| 35.2  | Ethernet Controller Overview              | 35-3 |

| 35.3  | Status and Control Registers              | 35-4 |

| 35.4  | Operation                                 |      |

| 35.5  | Ethernet Interrupts                       |      |

| 35.6  | Operation in Power-Saving and Debug Modes |      |

| 35.7  | Effects of Various Resets                 |      |

| 35.8  | I/O Pin Control                           |      |

| 35.9  | Related Application Notes                 |      |

| 35.10 | Revision History                          |      |

Ethernet Controller

Note: This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the "Ethernet Controller" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

### 35.1 INTRODUCTION

The Ethernet Controller is a bus master module that interfaces with an off-chip PHY in order to implement a complete Ethernet node in a system.

Following are some of the key features of this module:

- Supports 10/100 Mbps data transfer rates

- · Supports Full-Duplex and Half-Duplex operation

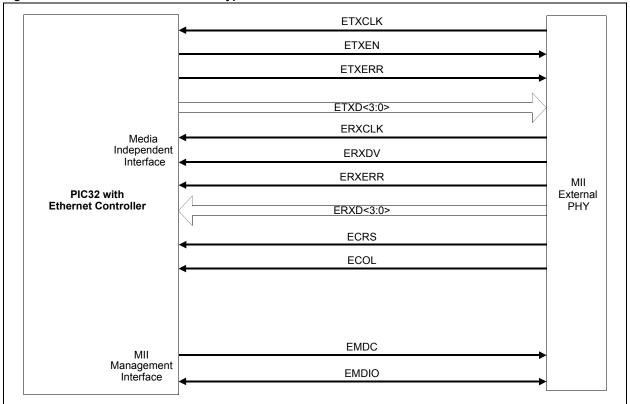

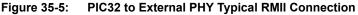

- Supports Reduced Media Independent Interface (RMII) and Media Independent Interface (MII) PHY interface

- Supports MII Management (MIIM) PHY Management interface

- · Supports both manual and automatic flow control

- · Supports Auto-MDIX and enabled PHYs

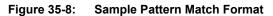

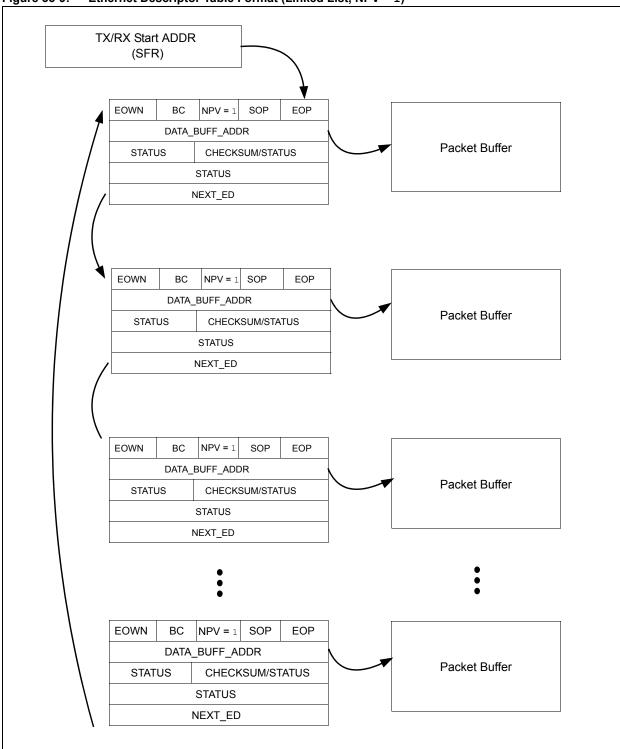

- RAM descriptor based DMA operation for both receive and transmit path

- Fully configurable interrupts

- Configurable receive packet filtering

- CRC Check

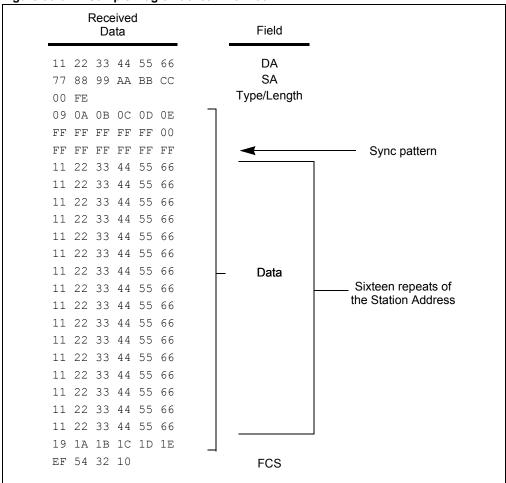

- 64-byte Pattern Match

- Broadcast, Multicast and Unicast packets

- Magic Packet<sup>™</sup>

- 64-bit Hash Table

- Runt Packet

- Supports Packet Payload Checksum calculation

- Supports various hardware statistics counters

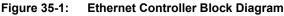

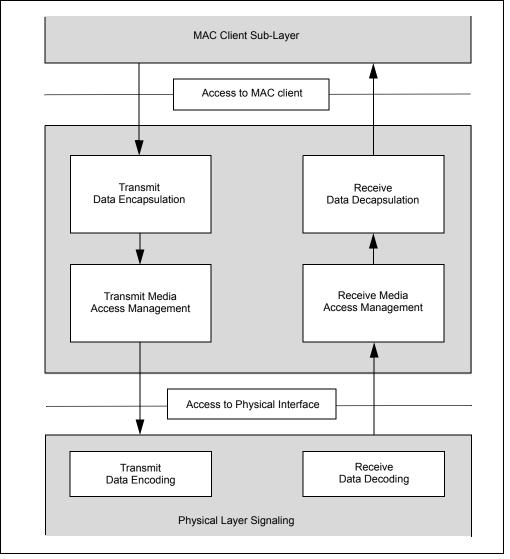

## 35.2 ETHERNET CONTROLLER OVERVIEW

The Ethernet Controller provides the modules needed to implement a 10/100 Mbps Ethernet node using an external PHY chip. In order to off-load the CPU from moving packet data to and from the module, internal descriptor-based DMA engines are included in the controller.

The Ethernet Controller consists of the following modules:

- Media Access Control (MAC) block: Responsible for implementing the MAC functions of the Ethernet IEEE 802.3 Specification

- Flow Control (FC) block: Responsible for control of the transmission of PAUSE frames. Reception of PAUSE frames is handled within the MAC.

- RX Filter (RXF) block: This module performs filtering on every receive packet to determine whether each packet should be accepted or rejected

- TX DMA/TX BM Engine: The TX DMA and TX Buffer Management engines perform data transfers from the memory (using descriptor tables) to the MAC Transmit Interface

- RX DMA/RX BM Engine: The RX DMA and RX Buffer Management engines transfer receive packets from the MAC to the memory (using descriptor tables)

Figure 35-1 shows a block diagram of the Ethernet Controller.

Note: For detailed explanations of Ethernet operation, refer to AN1120 "*Ethernet Theory* of Operation" (DS01120), which is available from the Microchip web site (www.microchip.com), and the IEEE 802.3 Specification (www.ieee.org).

**5** Ethernet Controller

### 35.3 STATUS AND CONTROL REGISTERS

The Ethernet Controller module consists of the following Special Function Registers (SFRs):

#### Controller and DMA Engine Configuration/Status Registers:

- ETHCON1: Ethernet Controller Control 1 Register

- ETHCON2: Ethernet Controller Control 2 Register<sup>(1,2)</sup>

- ETHTXST: Ethernet Controller TX Packet Descriptor Start Address Register<sup>(1,2)</sup>

- ETHRXST: Ethernet Controller RX Packet Descriptor Start Address Register<sup>(1,2)</sup>

- ETHIEN: Ethernet Controller Interrupt Enable Register

- ETHIRQ: Ethernet Controller Interrupt Request Register

- ETHSTAT: Ethernet Controller Status Register

#### **RX Filtering Configuration Registers:**

- ETHRXFC: Ethernet Controller Receive Filter Configuration Register<sup>(1,2)</sup>

- ETHHT0: Ethernet Controller Hash Table 0 Register<sup>(1,2)</sup>

- ETHHT1: Ethernet Controller Hash Table 1 Register<sup>(1,2)</sup>

- ETHPMM0: Ethernet Controller Pattern Match Mask 0 Register<sup>(1,2)</sup>

- ETHPMM1: Ethernet Controller Pattern Match Mask 1 Register<sup>(1,2)</sup>

- ETHPMCS: Ethernet Controller Pattern Match Checksum Register<sup>(1,2)</sup>

- ETHPMO: Ethernet Controller Pattern Match Offset Register<sup>(1,2)</sup>

#### Flow Control Configuring Register:

• ETHRXWM: Ethernet Controller Receive Watermarks Register<sup>(1)</sup>

#### **Ethernet Statistics Registers:**

- ETHRXOVFLOW: Ethernet Controller Receive Overflow Statistics Register<sup>(1,2)</sup>

- ETHFRMTXOK: Ethernet Controller Frames Transmitted OK Statistics Register<sup>(1,2)</sup>

- ETHSCOLFRM: Ethernet Controller Single Collision Frames Statistics Register<sup>(1,2)</sup>

- ETHMCOLFRM: Ethernet Controller Multiple Collision Frames Statistics Register<sup>(1,2)</sup>

- ETHFRMRXOK: Ethernet Controller Frames Received OK Statistics Register<sup>(1,2)</sup>

- ETHFCSERR: Ethernet Controller Frame Check Sequence Error Statistics Register<sup>(1,2)</sup>

- ETHALGNERR: Ethernet Controller Alignment Errors Statistics Register<sup>(1,2)</sup>

#### MAC Configuration Registers:

- EMAC1CFG1: Ethernet Controller MAC Configuration 1 Register<sup>(1)</sup>

- EMAC1CFG2: Ethernet Controller MAC Configuration 2 Register<sup>(1)</sup>

- EMAC1IPGT: Ethernet Controller MAC Back-to-Back Interpacket Gap Register<sup>(1)</sup>

- EMAC1IPGR: Ethernet Controller MAC Non-Back-to-Back Interpacket Gap Register<sup>(1)</sup>

- EMAC1CLRT: Ethernet Controller MAC Collision Window/Retry Limit Register<sup>(1)</sup>

- EMAC1MAXF: Ethernet Controller MAC Maximum Frame Length Register<sup>(1,2)</sup>

- EMAC1SUPP: Ethernet Controller MAC PHY Support Register<sup>(1,2)</sup>

- EMAC1TEST: Ethernet Controller MAC Test Register<sup>(1,2)</sup>

- EMAC1SA0: Ethernet Controller MAC Station Address 0 Register<sup>(1,2)</sup>

- EMAC1SA1: Ethernet Controller MAC Station Address 1 Register<sup>(1,2)</sup>

- EMAC1SA2: Ethernet Controller MAC Station Address 2 Register<sup>(1,2)</sup>

#### MII Management Registers:

- EMAC1MCFG: Ethernet Controller MAC MII Management Configuration Register<sup>(1,2)</sup>

- EMAC1MCMD: Ethernet Controller MAC MII Management Command Register<sup>(1)</sup>

- EMAC1MADR: Ethernet Controller MAC MII Management Address Register<sup>(1)</sup>

- EMAC1MWTD: Ethernet Controller MAC MII Management Write Data Register<sup>(1)</sup>

- EMAC1MRDD: Ethernet Controller MAC MII Management Read Data Register<sup>(1)</sup>

- EMAC1MIND: Ethernet Controller MAC MII Management Indicators Register<sup>(1)</sup>

Table 35-1 provides a brief summary of the Ethernet Controller registers. Corresponding registers appear after the summary, followed by a detailed description of each register.

| Table 35-1: Ethernet Controller Register Summary |              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------------------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Name                                             | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| ETHCON1 <sup>(1,2,3)</sup>                       | 31:24        |                   |                   |                   | PTV <             | 15:8>             |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        |                   |                   |                   | PTV               | <7:0>             |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         | ON                | —                 | SIDL              | _                 | —                 | _                 | TXRTS            | RXEN             |  |  |  |  |

|                                                  | 7:0          | AUTOFC            | —                 | —                 | MANFC             | —                 | —                 | _                | BUFCDEC          |  |  |  |  |

| ETHCON2 <sup>(1,2,3)</sup>                       | 31:24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |  |

|                                                  | 23:16        | _                 | —                 | —                 | —                 | _                 | _                 |                  |                  |  |  |  |  |

|                                                  | 15:8         | _                 | _                 | _                 | _                 | _                 | l                 | RXBUFSZ<6:4      | >                |  |  |  |  |

|                                                  | 7:0          |                   | RXBUF             | SZ<3:0>           |                   | _                 |                   | _                | _                |  |  |  |  |

| ETHTXST <sup>(1,2,3)</sup>                       | 31:24        |                   |                   |                   | TXSTADD           | R<31:24>          |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        |                   |                   |                   | TXSTADD           | R<23:16>          |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         |                   |                   |                   | TXSTAD            | )R<15:8>          |                   | 1                |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   | _                 | —                 |                   |                   |                  |                  |  |  |  |  |

| ETHRXST <sup>(1,2,3)</sup>                       | 31:24        |                   |                   |                   | RXSTADD           | R<31:24>          |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        | RXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         |                   |                   |                   | RXSTAD            | DR<15:8>          |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   | RXSTAD            | DR<7:2>           |                   |                   |                  | _                |  |  |  |  |

| ETHHT0 <sup>(1,2,3)</sup>                        | 31:24        |                   |                   |                   | HT<3              | 1:24>             |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   |                   | HT<               | 7:0>              |                   |                  |                  |  |  |  |  |

| ETHHT1 <sup>(1,2,3)</sup>                        | 31:24        | HT<63:56>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   | HT<39:32>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

| ETHPMM0 <sup>(1,2,3)</sup>                       | 31:24        |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        |                   |                   |                   | PMM<              | 23:16>            |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         |                   |                   |                   | PMM<              | :15:8>            |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |  |  |  |  |

| ETHPMM1 <sup>(1,2,3)</sup>                       | 31:24        |                   |                   |                   | PMM<              | 63:56>            |                   |                  |                  |  |  |  |  |

|                                                  | 23:16        |                   |                   |                   | PMM<              | 55:48>            |                   |                  |                  |  |  |  |  |

|                                                  | 15:8         |                   |                   |                   | PMM<              | 47:40>            |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   |                   | PMM<              | 39:32>            |                   |                  |                  |  |  |  |  |

| ETHPMCS <sup>(1,2,3)</sup>                       | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

|                                                  | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

|                                                  | 15:8         |                   |                   |                   | PMCS              | <15:8>            |                   |                  |                  |  |  |  |  |

|                                                  | 7:0          |                   |                   |                   | PMCS              | 6<7:0>            |                   |                  |                  |  |  |  |  |

Table 35-1: Ethernet Controller Register Summary

**Legend:** — = unimplemented, read as '0'.

Note 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ETHCON1CLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g.,ETHCON1SET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ETHCON1INV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

Ethernet Controller

| Table 35-1: Et                 | herne        | t Controlle       | r Register S      | Summary (C        | ontinued)         | r                 | r                 | r                | T                |  |  |

|--------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Name                           | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| ETHPMO <sup>(1,2,3)</sup>      | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | —                 | _                 | —                | _                |  |  |

|                                | 15:8         |                   |                   |                   | PMO<              | :15:8>            |                   |                  |                  |  |  |

|                                | 7:0          |                   |                   |                   | PMO               | <7:0>             |                   |                  |                  |  |  |

| ETHRXFC <sup>(1,2,3)</sup>     | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

|                                | 15:8         | HTEN              | MPEN              | _                 | NOTPM             |                   | PMMOE             | DE<3:0>          |                  |  |  |

|                                | 7:0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |  |  |

| ETHRXWM <sup>(1,2,3)</sup>     | 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

|                                | 23:16        |                   |                   |                   | RXFWI             | M<7:0>            |                   |                  |                  |  |  |

|                                | 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | -                |  |  |

|                                | 7:0          |                   |                   |                   | RXEW              | M<7:0>            |                   |                  |                  |  |  |

| ETHIEN <sup>(1,2,3)</sup>      | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

|                                | 15:8         | _                 | TXBUSEIE          | RXBUSEIE          | _                 | —                 | _                 | EWMARKIE         | FWMARKIE         |  |  |

|                                | 7:0          | RXDONEIE          | PKTPENDIE         | RXACTIE           | _                 | TXDONEIE          | TXABORTIE         | RXBUFNAIE        | RXOVFLWIE        |  |  |

| ETHIRQ <sup>(1,2,3)</sup>      | 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 15:8         | _                 | TXBUSE            | RXBUSE            | _                 | —                 | —                 | EWMARK           | FWMARK           |  |  |

|                                | 7:0          | RXDONE            | PKTPEND           | RXACT             | _                 | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |  |  |

| ETHSTAT                        | 31:24        | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

|                                | 23:16        | BUFCNT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

|                                | 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 7:0          | ETHBUSY           | TXBUSY            | RXBUSY            | _                 | —                 | _                 | —                | —                |  |  |

| ETHRXOVFLOW <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 15:8         |                   |                   |                   | RXOVFLW           | CNT<15:8>         |                   |                  |                  |  |  |

|                                | 7:0          |                   |                   |                   | RXOVFLW           | 'CNT<7:0>         |                   |                  |                  |  |  |

| ETHFRMTXOK <sup>(1,2,3)</sup>  | 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 15:8         |                   |                   |                   | FRMTXOK           | CNT<15:8>         |                   |                  |                  |  |  |

|                                | 7:0          |                   |                   |                   | FRMTXOK           | CNT<7:0>          |                   |                  |                  |  |  |

| ETHSCOLFRM <sup>(1,2,3)</sup>  | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|                                | 15:8         |                   |                   |                   | SCOLFRM           | CNT<15:8>         |                   |                  |                  |  |  |

|                                | 7:0          |                   |                   |                   | SCOLFRM           | CNT<7:0>          |                   |                  |                  |  |  |

#### Table 35-1: Ethernet Controller Register Summary (Continued)

Legend: — = unimplemented, read as '0'.

Note 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ETHCON1CLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g.,ETHCON1SET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ETHCON1INV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

| Table 35-1: Ef                | inerne       | t Controlle       | r Register a      | Summary (C        | ontinuea)         | 1                 |                   | 1                |                  |  |  |  |

|-------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Name                          | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| ETHMCOLFRM <sup>(1,2,3)</sup> | 31:24        | _                 | —                 | —                 | _                 | —                 | _                 | —                | —                |  |  |  |

|                               | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                               | 15:8         |                   |                   |                   | MCOLFRM           | CNT<15:8>         |                   |                  |                  |  |  |  |

|                               | 7:0          |                   |                   |                   | MCOLFRM           | ICNT<7:0>         |                   |                  |                  |  |  |  |

| ETHFRMRXOK <sup>(1,2,3)</sup> | 31:24        | _                 | —                 | —                 | _                 | —                 | _                 | —                | —                |  |  |  |

|                               | 23:16        | _                 | —                 | —                 |                   | _                 |                   | —                | _                |  |  |  |

|                               | 15:8         | FRMRXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                               | 7:0          |                   |                   |                   | FRMRXOK           | CNT<7:0>          |                   |                  |                  |  |  |  |

| ETHFCSERR <sup>(1,2,3)</sup>  | 31:24        | _                 | —                 | —                 |                   | _                 |                   | —                | _                |  |  |  |

|                               | 23:16        | _                 | —                 | _                 | _                 | _                 | _                 | —                | _                |  |  |  |

|                               | 15:8         |                   |                   |                   | FCSERRC           | NT<15:8>          |                   |                  |                  |  |  |  |

|                               | 7:0          | FCSERRCNT<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| ETHALGNERR <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | —                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                               | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                               | 15:8         |                   | ALGNERRCNT<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |

|                               | 7:0          |                   |                   |                   | ALGNERR           | CNT<7:0>          |                   |                  |                  |  |  |  |

| EMAC1CFG1 <sup>(1,2,3)</sup>  | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                               | 23:16        | _                 | —                 | _                 | _                 | _                 | _                 | —                | _                |  |  |  |

|                               | 15:8         | SOFTRESET         | SIMRESET          | —                 | _                 | RESETRMCS         | RESETRFUN         | RESETTMCS        | RESETTFUN        |  |  |  |

|                               | 7:0          | _                 | —                 | —                 | LOOPBACK          | TXPAUSE           | RXPAUSE           | PASSALL          | RXENABLE         |  |  |  |

| EMAC1CFG2 <sup>(1,2,3)</sup>  | 31:24        | _                 | _                 | _                 |                   | _                 |                   | _                | _                |  |  |  |

|                               | 23:16        | _                 | —                 | —                 | _                 | —                 | _                 | —                | _                |  |  |  |

|                               | 15:8         | _                 | EXCESSDFR         | BPNOBKOFF         | NOBKOFF           | _                 |                   | LONGPRE          | PUREPRE          |  |  |  |

|                               | 7:0          | AUTOPAD           | VLANPAD           | PADENABLE         | CRCENABLE         | DELAYCRC          | HUGEFRM           | LENGTHCK         | FULLDPLX         |  |  |  |

| EMAC1IPGT <sup>(1,2,3)</sup>  | 31:24        | _                 | —                 | —                 | _                 | —                 | _                 | —                | _                |  |  |  |

|                               | 23:16        | _                 | _                 | _                 |                   | _                 |                   | _                | _                |  |  |  |

|                               | 15:8         | _                 | _                 | _                 |                   | _                 |                   | _                | _                |  |  |  |

|                               | 7:0          | _                 |                   |                   | В                 | 2BIPKTGP<6:0      | >                 |                  |                  |  |  |  |

| EMAC1IPGR <sup>(1,2,3)</sup>  | 31:24        | _                 | —                 | _                 |                   | _                 |                   | _                | _                |  |  |  |

|                               | 23:16        | _                 | —                 | _                 |                   | _                 |                   | _                | _                |  |  |  |

|                               | 15:8         | _                 |                   |                   | NB                | 2BIPKTGP1<6       | :0>               |                  |                  |  |  |  |

|                               | 7:0          | _                 |                   |                   | NB                | 2BIPKTGP2<6       | :0>               |                  |                  |  |  |  |

| EMAC1CLRT <sup>(1,2,3)</sup>  | 31:24        | _                 | —                 | —                 | _                 | —                 | _                 |                  | —                |  |  |  |

|                               | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 |                  | —                |  |  |  |

|                               | 15:8         | _                 | _                 |                   |                   | CWINDC            | )W<5:0>           |                  |                  |  |  |  |

|                               | 7:0          | _                 | _                 | _                 | _                 |                   | RETX              | <3:0>            |                  |  |  |  |

Table 35-1:

Ethernet Controller Register Summary (Continued)

**Legend:** — = unimplemented, read as '0'.

Note

1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ETHCON1CLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g.,ETHCON1SET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ETHCON1INV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

| Table 35-1: E                | therne       | t Controller      | r Register S      | Summary (C        | continued)        |                   |                   |                  |                  |

|------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Name                         | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| EMAC1MAXF <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | —                 | —                 | _                | —                |

|                              | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 15:8         |                   |                   |                   | MACMAX            | (F<15:8>          |                   |                  |                  |

|                              | 7:0          |                   |                   |                   | MACMA             | XF<7:0>           |                   |                  |                  |

| EMAC1SUPP <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 23:16        | -                 | _                 | —                 | _                 | —                 | —                 | —                | —                |

|                              | 15:8         | _                 | _                 | _                 | _                 | RESETRMII         | —                 | _                | SPEEDRMII        |

|                              | 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| EMAC1TEST <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 7:0          | _                 | _                 | _                 | _                 | _                 | TESTBP            | TESTPAUSE        | SHRTQNTA         |

| EMAC1MCFG <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | —                 | —                 | —                | —                |

|                              | 23:16        | -                 | _                 | —                 | _                 | —                 | —                 | —                | —                |

|                              | 15:8         | RESETMGMT         | _                 | —                 | _                 | —                 | —                 | —                | —                |

|                              | 7:0          | _                 | _                 |                   | CLKSE             | EL<3:0>           |                   | NOPRE            | SCANINC          |

| EMAC1MCMD <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

|                              | 23:16        | -                 | _                 | —                 | _                 | —                 | —                 | —                | —                |

|                              | 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

|                              | 7:0          | _                 |                   | _                 |                   | _                 | _                 | SCAN             | READ             |

| EMAC1MADR <sup>(1,2,3)</sup> | 31:24        | _                 |                   | —                 |                   | —                 | _                 | —                | _                |

|                              | 23:16        | _                 |                   | _                 |                   | —                 | _                 | _                | _                |

|                              | 15:8         | _                 |                   | —                 |                   | F                 | PHYADDR<4:0       | >                |                  |

|                              | 7:0          | _                 |                   | _                 |                   | F                 | REGADDR<4:0       | >                |                  |

| EMAC1MWTD <sup>(1,2,3)</sup> | 31:24        | _                 |                   | _                 |                   | _                 | _                 | —                | _                |

|                              | 23:16        | _                 |                   | —                 |                   | —                 | _                 | —                | _                |

|                              | 15:8         |                   |                   |                   | MWTD              | <15:8>            |                   |                  |                  |

|                              | 7:0          |                   |                   |                   | MWTE              | )<7:0>            |                   |                  |                  |

| EMAC1MRDD <sup>(1,2,3)</sup> | 31:24        | -                 | _                 | —                 | _                 | —                 | —                 | —                | —                |

|                              | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 15:8         |                   |                   |                   | MRDD              | <15:8>            |                   |                  |                  |

|                              | 7:0          |                   |                   |                   | MRDD              | )<7:0>            |                   |                  |                  |

| EMAC1MIND <sup>(1,2,3)</sup> | 31:24        | _                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

|                              | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                              | 7:0          | _                 | _                 | —                 | _                 | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

Legend: - = unimplemented, read as '0'. Note

This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ETHCON1CLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated 1: register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g., ETHCON1SET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ETHCON1INV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated 3: register. Reads from the Invert register should be ignored.

| Table 35-1. E               |              | L CONTROLLER       | itogiotoi c       |                   | , on an a car     |                   |                   |                  |                  |  |

|-----------------------------|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Name                        | Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| EMAC1SA0 <sup>(1,2,3)</sup> | 31:24        | _                  | —                 | _                 | —                 | _                 | —                 | -                | —                |  |

|                             | 23:16        | _                  | _                 |                   | _                 |                   | _                 |                  | _                |  |

|                             | 15:8         | 15:8 STNADDR6<7:0> |                   |                   |                   |                   |                   |                  |                  |  |

|                             | 7:0          | STNADDR5<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |

| EMAC1SA1 <sup>(1,2,3)</sup> | 31:24        | _                  | —                 | _                 | —                 | _                 | —                 | _                | -                |  |

|                             | 23:16        | _                  | _                 |                   | _                 |                   | _                 |                  | _                |  |

|                             | 15:8         |                    |                   |                   | STNADD            | R4<7:0>           |                   |                  |                  |  |

|                             | 7:0          |                    |                   |                   | STNADD            | R3<7:0>           |                   |                  |                  |  |

| EMAC1SA2 <sup>(1,2,3)</sup> | 31:24        | _                  | _                 |                   | _                 |                   | _                 |                  | _                |  |

|                             | 23:16        | _                  | —                 | _                 | _                 | _                 | _                 | _                |                  |  |

|                             | 15:8         |                    |                   |                   | STNADD            | R2<7:0>           |                   |                  |                  |  |

|                             | 7:0          |                    |                   |                   | STNADD            | R1<7:0>           |                   |                  |                  |  |

Table 35-1: Ethernet Controller Register Summary (Continued)

Legend: — = unimplemented, read as '0'.

Note 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ETHCON1CLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g.,ETHCON1SET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ETHCON1INV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |

| 31.24     |                   |                   |                   | PTV<              | 15:8>             |                   |                  |                     |

| 22:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |

| 23:16     |                   |                   |                   | PTV<              | :7:0>             |                   |                  |                     |

| 15.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |

| 15:8      | ON                | _                 | SIDL              | —                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |

| 7.0       | AUTOFC            | _                 | _                 | MANFC             | _                 | _                 | —                | BUFCDEC             |

#### Register 35-1: ETHCON1: Ethernet Controller Control 1 Register

#### Legend:

| R = Readable bit      | W = Writable bit         | P = Programmable bit   | r = Reserved bit |

|-----------------------|--------------------------|------------------------|------------------|

| U = Unimplemented bit | -n = Bit Value at POR: ( | '0', '1', x = Unknown) |                  |

bit 31-16 **PTV<15:0>:** PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set.

These bits are used for Flow Control operations only.

- bit 15 ON: Ethernet ON bit

- 1 = Ethernet module is enabled

- 0 = Ethernet module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Ethernet Stop in Idle Mode bit

- 1 = Ethernet module transfers are frozen during Idle

- 0 = Ethernet module transfers continue during Idle

- bit 12-10 Unimplemented: Read as '0'

- bit 9 **TXRTS:** Transmit Request to Send bit

- 1 = Activate the transmit logic and send the packet(s) defined in the TX EDT

0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit affects TX operations only.

- bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit affects RX operations only.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

#### Register 35-1: ETHCON1: Ethernet Controller Control 1 Register (Continued)

- bit 7 AUTOFC: Automatic Flow Control bit

- 1 = Automatic flow control enabled

- 0 = Automatic flow control disabled

Setting this bit will enable automatic flow control. If set, the full and empty watermarks are used to automatically enable and disable the flow control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, flow control is automatically enabled. When the BUFCNT falls to the empty watermark, flow control is automatically disabled.

This bit is used for flow control operations only and affects both TX and RX operations.

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control enabled

- 0 = Manual Flow Control disabled

Setting this bit will enable manual flow control. If set, the flow control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

Note that for 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable flow control.

This bit is used for flow control operations only and affects both TX and RX operations.

- bit 3-1 Unimplemented: Read as '0'

- bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads out '0'. When written with '1', BUFCNT, the Descriptor Buffer Counter, will decrement by one. If the BUFCNT counter is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing '0' will have no effect.

This bit is used for RX operations only.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | —                 | —                 | —                 | -                 | -                 | _                 | _                | —                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | —                 | —                 | —                 | -                 | -                 | _                 | _                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | _                 | —                 | _                 | —                 | _                 | RXBUFSZ<6:4>      |                  | 4>               |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 7.0       |                   | RXBUFSZ<3:0>      |                   |                   |                   | _                 |                  |                  |

### Register 35-2: ETHCON2: Ethernet Controller Control 2 Register<sup>(1,2)</sup>

#### Legend:

| R = Readable bit      | W = Writable bit          | P = Programmable bit   | r = Reserved bit |

|-----------------------|---------------------------|------------------------|------------------|

| U = Unimplemented bit | -n = Bit Value at POR: (' | '0', '1', x = Unknown) |                  |

#### bit 31-11 Unimplemented: Read as '0'

- Note 1: This register is used for RX operations only.

- 2: These bits may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 51.24     |                   |                   |                   | TXSTADD           | R<31:24>          |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     |                   |                   |                   | TXSTADD           | R<23:16>          |                   |                  |                  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8      | TXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |

| 7.0       |                   |                   |                   | _                 |                   |                   |                  |                  |  |

### Register 35-3: ETHTXST: Ethernet Controller TX Packet Descriptor Start Address Register<sup>(1,2)</sup>

### Legend:

| Logena.               |                       |                      |                  |  |

|-----------------------|-----------------------|----------------------|------------------|--|

| R = Readable bit      | W = Writable bit      | P = Programmable bit | r = Reserved bit |  |

| U = Unimplemented bit | -n = Bit Value at POR |                      |                  |  |

## bit 31-2 **TXSTADDR<31:2>:** Starting Address of First Transmit Descriptor bits This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (i.e., bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

#### **Note 1:** This register is used for TX operations only.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     |                   |                   |                   | RXSTADE           | R<31:24>          |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | RXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | RXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 7.0       | RXSTADDR<7:2>     |                   |                   |                   |                   |                   |                  | _                |

### Register 35-4: ETHRXST: Ethernet Controller RX Packet Descriptor Start Address Register<sup>(1,2)</sup>

| Legend:               |                          |                      |                  |

|-----------------------|--------------------------|----------------------|------------------|

| R = Readable bit      | W = Writable bit         | P = Programmable bit | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: ( |                      |                  |

bit 31-2 **RXSTADDR<31:2>:** Starting Address of First Receive Descriptor bits This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (i.e., bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

E

**Note 1:** This register is used for RX operations only.

**2:** This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | HT<31:24>         |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | HT<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |

Register 35-5: ETHHT0: Ethernet Controller Hash Table 0 Register<sup>(1,2)</sup>

| Legend:               |                        |                         |                  |

|-----------------------|------------------------|-------------------------|------------------|

| R = Readable bit      | W = Writable bit       | P = Programmable bit    | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: | ('0', '1', x = Unknown) |                  |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

- Note 1: This register is used for RX operations only.

- 2: These bits may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |

| 02:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | HT<3              | 9:32>             |                   |                  |                  |

## Register 35-6: ETHHT1: Ethernet Controller Hash Table 1 Register<sup>(1,2)</sup>

### Legend:

| Logona.               |                            |                       |                  |

|-----------------------|----------------------------|-----------------------|------------------|

| R = Readable bit      | W = Writable bit           | P = Programmable bit  | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: ('0 | )', '1', x = Unknown) |                  |

bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

**Note 1:** This register is used for RX operations only.

| -         |                   |                   |                   |                   |                   |                   |                  |                  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |  |

| 22:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16     | PMM<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8      | PMM<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |  |

Register 35-7: ETHPMM0: Ethernet Controller Pattern Match Mask 0 Register<sup>(1,2)</sup>

#### Legend:

| =ogonan               |                           |                        |                  |

|-----------------------|---------------------------|------------------------|------------------|

| R = Readable bit      | W = Writable bit          | P = Programmable bit   | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: (' | 0', '1',  x = Unknown) |                  |

bit 31-24 PMM<31:24>: Pattern Match Mask 3 bits

bit 23-16 **PMM<23:16>:** Pattern Match Mask 2 bits

bit 15-8 **PMM<15:8>:** Pattern Match Mask 1 bits

bit 7-0 **PMM<7:0>:** Pattern Match Mask 0 bits

Note 1: This register is used for RX operations only.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 51.24     | PMM<63:56>        |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     | PMM<55:48>        |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      | PMM<47:40>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       | PMM<39:32>        |                   |                   |                   |                   |                   |                  |                  |  |

### Register 35-8: ETHPMM1: Ethernet Controller Pattern Match Mask 1 Register<sup>(1,2)</sup>

#### Legend:

| 6                     |                           |                        |                  |

|-----------------------|---------------------------|------------------------|------------------|

| R = Readable bit      | W = Writable bit          | P = Programmable bit   | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: (' | 0', '1',  x = Unknown) |                  |

bit 31-24 PMM<63:56>: Pattern Match Mask 7 bits

bit 23-16 PMM<55:48>: Pattern Match Mask 6 bits

bit 15-8 **PMM<47:40>:** Pattern Match Mask 5 bits

bit 7-0 **PMM<39:32>:** Pattern Match Mask 4 bits

Note 1: This register is used for RX operations only.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | —                 | _                 | —                 | _                 | _                 | _                | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | —                 | —                 | _                 | —                 | _                 | -                 | _                | _                |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | PMCS<15:8>        |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | PMCS              | 6<7:0>            |                   |                  |                  |

Register 35-9: ETHPMCS: Ethernet Controller Pattern Match Checksum Register<sup>(1,2)</sup>

#### Legend:

| 0                     |                           |                        |                  |

|-----------------------|---------------------------|------------------------|------------------|

| R = Readable bit      | W = Writable bit          | P = Programmable bit   | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: (' | 0', '1',  x = Unknown) |                  |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

Note 1: This register is used for RX operations only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | —                 | _                 | _                 | —                 | —                 | —                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

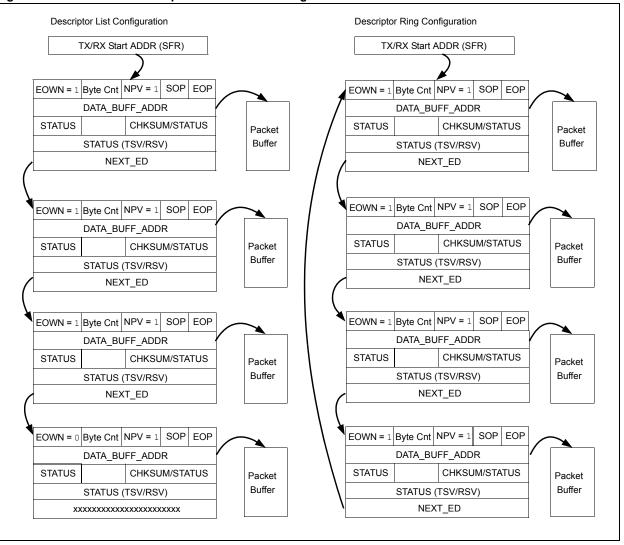

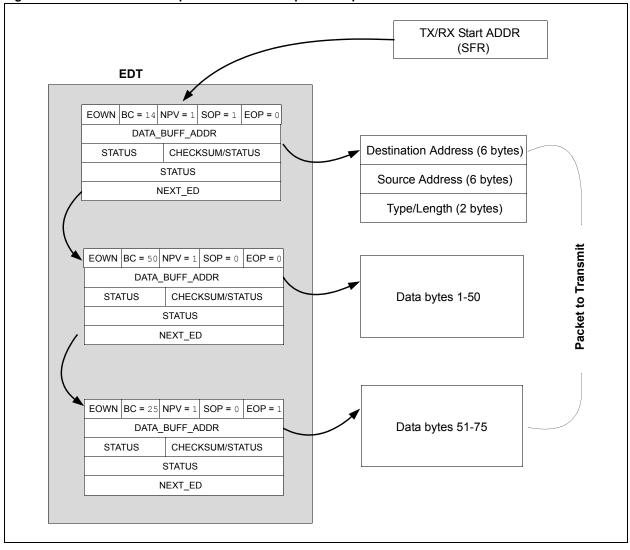

| 23.10        | —                 | _                 | _                 | _                 | _                 | —                 | —                | _                |  |  |