# **Section 23. CAN Module**

## **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 23.1  | Introduction                         | 23-2  |

|-------|--------------------------------------|-------|

| 23.2  | Control Registers for the CAN Module | 23-2  |

| 23.3  | Register Maps                        | 23-22 |

| 23.4  | CAN Module Features                  | 23-28 |

| 23.5  | CAN Module Implementation            | 23-29 |

| 23.6  | CAN Module Operation Modes           | 23-36 |

| 23.7  | Message Reception                    | 23-39 |

| 23.8  | Transmission                         | 23-49 |

| 23.9  | Error Detection                      | 23-58 |

| 23.10 | CAN Baud Rate                        | 23-60 |

| 23.11 | Interrupts                           | 23-64 |

| 23.12 | CAN Capture                          | 23-65 |

| 23.13 | CAN Module I/O                       | 23-65 |

| 23.14 | Operation in CPU Power Saving Modes  | 23-66 |

| 23.15 | CAN Protocol Overview                | 23-68 |

| 23.16 | Related Application Notes            | 23-72 |

| 23.17 | Revision History                     | 23-73 |

|       |                                      |       |

#### 23.1 Introduction

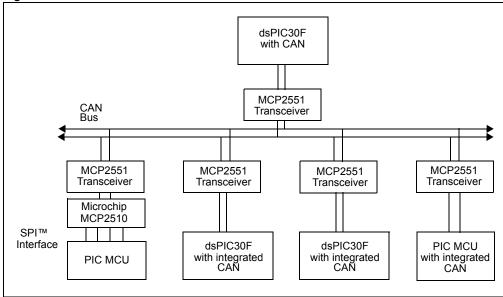

The Controller Area Network (CAN) module is a serial interface useful for communicating with other peripherals or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. Figure 23-1 shows an example CAN bus network.

Figure 23-1: CAN Bus Network

## 23.2 Control Registers for the CAN Module

There are many registers associated with the CAN module. Descriptions of these registers are grouped into the following sections:

- · Control and Status Registers

- · Transmit Buffer Registers

- Receive Buffer Registers

- · Baud Rate Control Registers

- · Interrupt Status and Control Registers

- Note 1: 'i' in the register identifier denotes the specific CAN module (CAN1 or CAN2).

- 2: 'n' in the register identifier denotes the buffer, filter or mask number.

- **3:** 'm' in the register identifier denotes the word number within a particular CAN data field.

## 23.2.1 CAN Control and Status Registers

#### Register 23-1: CiCTRL: CAN Module Control and Status Register

| Upper Byte: |     |       |       |        |       |           |       |  |  |  |

|-------------|-----|-------|-------|--------|-------|-----------|-------|--|--|--|

| R/W-x       | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-1 | R/W-0     | R/W-0 |  |  |  |

| CANCAP      | _   | CSIDL | ABAT  | CANCKS |       | REQOP<2:0 | )>    |  |  |  |

| bit 15      |     |       |       |        |       |           | bit 8 |  |  |  |

| Lower Byte: |             |     |     |     |            |     |       |  |  |  |  |

|-------------|-------------|-----|-----|-----|------------|-----|-------|--|--|--|--|

| R-1         | R-0         | R-0 | U-0 | R-0 | R-0        | R-0 | U-0   |  |  |  |  |

|             | OPMODE<2:0> |     |     |     | ICODE<2:0> |     |       |  |  |  |  |

| bit 7       |             |     |     |     |            |     | bit 0 |  |  |  |  |

- bit 15 CANCAP: CAN Message Receive Capture Enable bit

- 1 = Enable CAN capture

- 0 = Disable CAN capture

**Note:** CANCAP is always writable, regardless of CAN module Operating mode.

- bit 14 Unimplemented: Read as '0'

- bit 13 CSIDL: Stop in Idle Mode bit

- 1 = Discontinue CAN module operation when device enters Idle mode

- 0 = Continue CAN module operation in Idle mode

- bit 12 ABAT: Abort All Pending Transmissions bit

- 1 = Abort pending transmissions in all Transmit Buffers

- 0 = No effect

**Note:** Module will clear this bit when all transmissions aborted.

- bit 11 CANCKS: CAN Master Clock Select bit

- 1 = FCAN clock is FCY

- 0 = FCAN clock is 4 FCY

- bit 10-8 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

- bit 7-5 **OPMODE<2:0>:** Operation Mode bits

**Note:** These bits indicate the current Operating mode of the CAN module. See description for REQOP bits (CiCTRL<10:8>).

bit 4 Unimplemented: Read as '0'

## Register 23-1: CiCTRL: CAN Module Control and Status Register (Continued)

bit 3-1 ICODE<2:0>: Interrupt Flag Code bits

111 = Wake-up interrupt

110 = RXB0 interrupt

101 = RXB1 interrupt

100 = TXB0 interrupt

011 = TXB1 interrupt

010 = TXB2 interrupt

001 = Error interrupt

000 = No interrupt

bit 0 **Unimplemented:** Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## 23.2.2 CAN Transmit Buffer Registers

This subsection describes the CAN Transmit Buffer Register and the associated Transmit Buffer Control Registers.

#### Register 23-2: CiTXnCON: Transmit Buffer Status and Control Register

| Upper Byte: |     |     |     |     |     |     |       |  |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |  |  |  |

| _           | _   | _   | _   | _   | _   | _   | _     |  |  |  |

| bit 15      |     |     |     |     |     |     | bit 8 |  |  |  |

| Lower Byte | •     |        |       |       |     |            |       |  |

|------------|-------|--------|-------|-------|-----|------------|-------|--|

| U-0        | R-0   | R-0    | R-0   | R/W-0 | U-0 | R/W-0      | R/W-0 |  |

| _          | TXABT | TXLARB | TXERR | TXREQ | _   | TXPRI<1:0> |       |  |

| bit 7      |       |        |       |       |     |            | bit 0 |  |

bit 15-7 Unimplemented: Read as '0'

bit 6 **TXABT**: Message Aborted bit

1 = Message was aborted

0 = Message has not been aborted

Note: This bit is cleared when TXREQ is set.

bit 5 TXLARB: Message Lost Arbitration bit

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sentNote: This bit is cleared when TXREQ is set.

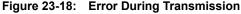

bit 4 TXERR: Error Detected During Transmission bit

1 = A bus error occurred while the message was being sent

0 = A bus error did not occur while the message was being sent

**Note:** This bit is cleared when TXREQ is set.

bit 3 TXREQ: Message Send Request bit

1 = Request message transmission

0 = Abort message transmission if TXREQ already set, otherwise no effect

Note: The bit will automatically clear when the message is successfully sent.

bit 2 Unimplemented: Read as '0'

bit 1-0 TXPRI<1:0>: Message Transmission Priority bits

11 = Highest message priority

10 = High intermediate message priority

01 = Low intermediate message Priority

00 = Lowest message priority

## Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## Register 23-3: CiTXnSID: Transmit Buffer n Standard Identifier

| Upper Byte: |       |       |       |       |     |     |       |

|-------------|-------|-------|-------|-------|-----|-----|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | U-0 | U-0   |

|             |       | _     | _     | _     |     |     |       |

| bit 15      |       |       |       |       |     |     | bit 8 |

| Lower Byte: |       |       |       |       |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|             | SRR   | TXIDE |       |       |       |       |       |

| bit 7       |       |       |       |       | •     | •     | bit 0 |

bit 15-11 SID<10:6>: Standard Identifier bits

bit 10-8 Unimplemented: Read as '0'

bit 7-2 SID<6:0>: Standard Identifier bits

bit 1 SRR: Substitute Remote Request bit

When TXIDE = 0

1 = Message will request a remote transmission

0 = Normal message

When TXIDE = 1, the SRR bit must be set to '1'.

bit 0 **TXIDE**: Extended Identifier bit

1 = Message will transmit extended identifier

0 = Message will transmit standard identifier

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### Register 23-4: CiTXnEID: Transmit Buffer n Extended Identifier

| Upper Byte: |       |        |       |     |     |     |       |

|-------------|-------|--------|-------|-----|-----|-----|-------|

| R/W-x       | R/W-x | R/W-x  | R/W-x | U-0 | U-0 | U-0 | U-0   |

|             | EID<  | 17:14> | _     | _   | _   | _   |       |

| bit 15      |       |        |       |     |     |     | bit 8 |

| Lower Byte: |           |       |       |       |       |       |       |  |  |  |

|-------------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|

| R/W-x       | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |

|             | EID<13:6> |       |       |       |       |       |       |  |  |  |

| bit 7       |           |       |       |       |       |       | bit 0 |  |  |  |

bit 15-12 EID<17:14>: Extended Identifier bits 17-14

bit 11-8 Unimplemented: Read as '0'

bit 7-0 EID<13:6>: Extended Identifier bits 13-6

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## Register 23-5: CiTXnDLC: Transmit Buffer n Data Length Control

| Upper Byte: |       |       |       |       |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|             | TXRTR | TXRB1 |       |       |       |       |       |

| bit 15      |       |       |       |       |       |       | bit 8 |

| Lower Byte: |       |       |       |       |     |     |       |  |  |  |

|-------------|-------|-------|-------|-------|-----|-----|-------|--|--|--|

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | U-0 | U-0   |  |  |  |

| TXRB0       |       | DLC<  | 3:0>  | _     | _   | _   |       |  |  |  |

| bit 7       |       |       |       |       |     |     | bit 0 |  |  |  |

bit 15-10 EID<5:0>: Extended Identifier bits 5-0

bit 9 TXRTR: Remote Transmission Request bit

When TXIDE = 1,

1 = Message will request a remote transmission

0 = Normal message

When TXIDE = 0, the TXRTR bit is ignored.

bit 8-7 TXRB<1:0>: Reserved Bits

**Note:** User must set these bits to '0' according to CAN protocol.

bit 6-3 **DLC<3:0>:** Data Length Code bits bit 2-0 **Unimplemented:** Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = bit is cleared x = Bit is unknown

## Register 23-6: CiTXnBm: Transmit Buffer n Data Field Word m

| 1109.010. =0 | • • • • • • • • • • • • • • • • • • • • |       |       |       |       |       |       |  |  |  |  |

|--------------|-----------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Upper Byte:  | •                                       |       |       |       |       |       |       |  |  |  |  |

| R/W-x        | R/W-x                                   | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |  |

|              | CTXB<15:8>                              |       |       |       |       |       |       |  |  |  |  |

| bit 15       |                                         |       |       |       |       |       | bit 8 |  |  |  |  |

| Lower Byte: |       |       |        |       |       |       |       |

|-------------|-------|-------|--------|-------|-------|-------|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x |

|             |       |       | CTXB<7 | 7:0>  |       |       |       |

| bit 7       |       |       |        |       |       |       | bit 0 |

## bit 15-0 CTXB<15:0>: Data Field Buffer Word bits (2 bytes)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = bit is cleared | x = Bit is unknown |

## 23.2.3 CAN Receive Buffer Registers

This subsection shows the Receive buffer registers with their associated control registers.

Register 23-7: CiRX0CON: Receive Buffer 0 Status and Control Register

| Upper Byte | :   |     |     |     |     |     |       |

|------------|-----|-----|-----|-----|-----|-----|-------|

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _          | _   | _   | _   | _   | _   | _   | _     |

| bit 15     |     |     |     |     |     |     | bit 8 |

| Lower Byte | :   |     |     |         |       |       |         |

|------------|-----|-----|-----|---------|-------|-------|---------|

| R/C-0      | U-0 | U-0 | U-0 | R-0     | R/W-0 | R/W-0 | R-0     |

| RXFUL      | _   | _   | _   | RXRTRRO | DBEN  | JTOFF | FILHIT0 |

| bit 7      |     |     |     |         |       |       | bit 0   |

#### bit 15-8 Unimplemented: Read as '0'

bit 7 RXFUL: Receive Full Status bit

- 1 = Receive buffer contains a valid received message

- 0 = Receive buffer is open to receive a new message

Note: This bit is set by the CAN module and should be cleared by software after the buffer is read.

- bit 6-4 Unimplemented: Read as '0'

- bit 3 RXRTRRO: Received Remote Transfer Request bit (read only)

- 1 = Remote Transfer Request was received

- 0 = Remote Transfer Request not received

Note: This bit reflects the status of the last message loaded into Receive Buffer 0.

- bit 2 DBEN: Receive Buffer 0 Double Buffer Enable bit

- 1 = Receive Buffer 0 overflow will write to Receive Buffer 1

- 0 = No Receive Buffer 0 overflow to Receive Buffer 1

- bit 1 JTOFF: Jump Table Offset bit (read only copy of DBEN)

- 1 = Allows Jump Table offset between 6 and 7

- 0 = Allows Jump Table offset between 0 and 1

- bit 0 FILHIT0: Indicates Which Acceptance Filter Enabled the Message Reception bit

- 1 = Acceptance Filter 1 (RXF1)

- 0 = Acceptance Filter 0 (RXF0)

**Note:** This bit reflects the status of the last message loaded into Receive Buffer 0.

#### Legend:

R = Readable bit W = Writable bit C = Bit can be cleared U = Unimplemented bit, read as '0'

Register 23-8: CiRX1CON: Receive Buffer 1 Status and Control Register

| •          |     |     |     |     | U   |     |       |

|------------|-----|-----|-----|-----|-----|-----|-------|

| Upper Byte | e:  |     |     |     | •   |     |       |

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _          | _   | _   | _   | _   | _   | _   | _     |

| bit 15     |     |     |     |     |     |     | bit 8 |

| Lower Byte | :   |     |     |         |     |             |       |

|------------|-----|-----|-----|---------|-----|-------------|-------|

| R/C-0      | U-0 | U-0 | U-0 | R-0     | R-0 | R-0         | R-0   |

| RXFUL      | _   | _   | _   | RXRTRRO |     | FILHIT<2:0> |       |

| bit 7      |     |     |     |         |     |             | bit 0 |

- bit 15-8 Unimplemented: Read as '0'

- bit 7 RXFUL: Receive Full Status bit

- 1 = Receive buffer contains a valid received message

- 0 = Receive buffer is open to receive a new message

Note: This bit is set by the CAN module and should be cleared by software after the buffer is read.

- bit 6-4 Unimplemented: Read as '0'

- bit 3 **RXRTRRO:** Received Remote Transfer Request bit (read only)

- 1 = Remote transfer request was received

- 0 = Remote transfer request not received

Note: This bit reflects the status of the last message loaded into Receive Buffer 1.

- bit 2-0 FILHIT<2:0>: Indicates Which Acceptance Filter Enabled the Message Reception bits

- 101 = Acceptance filter 5 (RXF5)

- 100 = Acceptance filter 4 (RXF4)

- 011 = Acceptance filter 3 (RXF3)

- 010 = Acceptance filter 2 (RXF2)

- 001 = Acceptance filter 1 (RXF1) (Only possible when DBEN bit is set)

- 000 = Acceptance filter 0 (RXF0) (Only possible when DBEN bit is set)

## Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## Register 23-9: CiRXnSID: Receive Buffer n Standard Identifier

| Upper Byte | :   |     |       |       |           |       |       |

|------------|-----|-----|-------|-------|-----------|-------|-------|

| U-0        | U-0 | U-0 | R/W-x | R/W-x | R/W-x     | R/W-x | R/W-x |

| _          | _   | _   |       |       | SID<10:6> |       |       |

| bit 15     |     |     |       |       |           |       | bit 8 |

| Lower Byte: |          |       |       |       |       |       |       |

|-------------|----------|-------|-------|-------|-------|-------|-------|

| R/W-x       | R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|             | SID<5:0> |       |       |       |       |       |       |

| bit 7       |          |       |       |       |       |       | bit 0 |

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier bits

bit 1 SRR: Substitute Remote Request bit (Only when RXIDE = 1)

When RXIDE = 0,

1 = Remote transfer request occured

0 = No remote transfer request occured

When RXIDE = 1, the SRR bit can be ignored.

bit 0 **RXIDE:** Extended Identifier Flag bit

1 = Received message is an extended data frame, SID<10:0> are EID<28:18>

0 = Received message is a standard data frame

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## Register 23-10: CiRXnEID: Receive Buffer n Extended Identifier

| Upper Byte | :   |     |     |            |       |       |       |  |

|------------|-----|-----|-----|------------|-------|-------|-------|--|

| U-0        | U-0 | U-0 | U-0 | R/W-x      | R/W-x | R/W-x | R/W-x |  |

| _          | _   | _   | _   | EID<17:14> |       |       |       |  |

| bit 15     |     |     |     |            |       |       | bit 8 |  |

| Lower Byte: |       |       |        |       |       |       |       |

|-------------|-------|-------|--------|-------|-------|-------|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x |

|             |       |       | EID<13 | :6>   |       |       |       |

| bit 7       |       |       |        |       |       |       | bit 0 |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits 17-6

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## Register 23-11: CiRXnBm: Receive Buffer n Data Field Word m

| Upper Byte: |            |       |       |       |       |       |       |  |  |  |

|-------------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

| R/W-x       | R/W-x      | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |

|             | CRXB<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15      |            |       |       |       |       |       | bit 8 |  |  |  |

| Lower Byte: |           |       |       |       |       |       |       |  |  |

|-------------|-----------|-------|-------|-------|-------|-------|-------|--|--|

| R/W-x       | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|             | CRXB<7:0> |       |       |       |       |       |       |  |  |

| bit 7       |           |       |       |       |       |       | bit 0 |  |  |

## bit 15-0 CRXB<15:0>: Data Field Buffer Word bits (2 bytes)

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## Register 23-12: CiRXnDLC: Receive Buffer n Data Length Control

| Upper Byte: |       |       |       |       |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID<5:0>    |       |       |       |       |       |       | RB1   |

| bit 15      |       |       |       |       |       |       | bit 8 |

| Lower Byte | :   |     |       |       |       |       |       |

|------------|-----|-----|-------|-------|-------|-------|-------|

| U-0        | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| _          | _   | _   | RB0   |       | DLC   | <3:0> |       |

| bit 7      |     |     |       |       |       |       | bit 0 |

#### bit 15-10 EID<5:0>: Extended Identifier bits

bit 9 RXRTR: Receive Remote Transmission Request Control bit

When RXIDE = 1,

1 = Remote transfer request

0 = No remote transfer request

When RXIDE = 0, the RXRTR bit can be ignored

**Note:** This bit reflects the status of the RTR bit in the last received message.

bit 8 RB1: Reserved bit 1

Reserved by CAN Spec and read as '0'

bit 4 RB0: Reserved bit 0

Reserved by CAN Spec and read as '0'

bit 3-0 DLC<3:0>: Data Length Code bits (Contents of Receive Buffer)

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

## 23.2.4 Message Acceptance Filters

This subsection describes the Message Acceptance filters.

#### Register 23-13: CiRXFnSID: Acceptance Filter n Standard Identifier

| Upper Byte | 1   |     |       |       |           |       |       |

|------------|-----|-----|-------|-------|-----------|-------|-------|

| U-0        | U-0 | U-0 | R/W-x | R/W-x | R/W-x     | R/W-x | R/W-x |

| _          | _   | _   |       |       | SID<10:6> |       |       |

| bit 15     |     |     |       |       |           |       | bit 8 |

| Lower Byte: |          |       |       |       |       |     |       |

|-------------|----------|-------|-------|-------|-------|-----|-------|

| R/W-x       | R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | R/W-x |

|             | SID<5:0> |       |       |       |       |     |       |

| bit 7       |          |       |       |       |       |     | bit 0 |

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier bits

bit 1 Unimplemented: Read as '0'

bit 0 **EXIDE:** Extended Identifier Enable bits

If MIDE = 1, then

1 = Enable filter for extended identifier 0 = Enable filter for standard identifier If MIDE = 0, then EXIDE is don't care

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## Register 23-14: CiRXFnEIDH: Acceptance Filter n Extended Identifier High

| Upper Byte | :   |     |     |            |       |       |       |

|------------|-----|-----|-----|------------|-------|-------|-------|

| U-0        | U-0 | U-0 | U-0 | R/W-x      | R/W-x | R/W-x | R/W-x |

| _          | _   | _   | _   | EID<17:14> |       |       |       |

| bit 15     |     |     |     |            |       |       | bit 8 |

| Lower Byte: |           |       |       |       |       |       |       |  |  |  |

|-------------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|

| R/W-x       | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |

|             | EID<13:6> |       |       |       |       |       |       |  |  |  |

| bit 7       |           |       |       |       |       |       | bit 0 |  |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits 17-6

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## Register 23-15: CiRXFnEIDL: Acceptance Filter n Extended Identifier Low

| Upper Byte: |          |       |       |       |       |     |       |

|-------------|----------|-------|-------|-------|-------|-----|-------|

| R/W-x       | R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | U-0   |

|             | EID<5:0> |       |       |       |       |     | _     |

| bit 15      |          |       |       |       |       |     | bit 8 |

| Lower Byte | :   |     |     |     |     |     |       |

|------------|-----|-----|-----|-----|-----|-----|-------|

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _          | _   | _   | _   | _   | _   | _   |       |

| bit 7      |     |     |     |     |     |     | bit 0 |

bit 15-10 **EID<5:0>:** Extended Identifier bits bit 9-0 **Unimplemented:** Read as '0'

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## 23.2.5 Acceptance Filter Mask Registers

#### Register 23-16: CiRXMnSID: Acceptance Filter Mask n Standard Identifier

| Upper Byte | :   |     |       |       |           |       |       |

|------------|-----|-----|-------|-------|-----------|-------|-------|

| U-0        | U-0 | U-0 | R/W-x | R/W-x | R/W-x     | R/W-x | R/W-x |

| _          | _   | _   |       |       | SID<10:6> |       |       |

| bit 15     |     |     |       |       |           |       | bit 8 |

| Lower Byte: |          |       |       |       |       |     |       |

|-------------|----------|-------|-------|-------|-------|-----|-------|

| R/W-x       | R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | R/W-x |

|             | SID<5:0> |       |       |       |       |     |       |

| bit 7       |          |       |       |       |       |     | bit 0 |

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier Mask bits

1 = Include bit in the filter comparison

0 = Don't include bit in the filter comparison

bit 1 **Unimplemented:** Read as '0'

bit 0 MIDE: Identifier Mode Selection bit

1 = Match only message types (standard or extended address) as determined by EXIDE bit in filter

0 = Match either standard or extended address message if the filters match

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### Register 23-17: CiRXMnEIDH: Acceptance Filter Mask n Extended Identifier High

| 3          |     |     |     |       |       |        |       |

|------------|-----|-----|-----|-------|-------|--------|-------|

| Upper Byte | :   |     |     |       | •     |        |       |

| U-0        | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x  | R/W-x |

| _          | _   | _   | _   |       | EID<  | 17:14> |       |

| bit 15     |     |     |     |       |       |        | bit 8 |

| Lower Byte: |           |       |       |       |       |       |       |  |  |

|-------------|-----------|-------|-------|-------|-------|-------|-------|--|--|

| R/W-x       | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|             | EID<13:6> |       |       |       |       |       |       |  |  |

| bit 7       |           |       |       |       |       |       | bit 0 |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier Mask bits 17-6

1 = Include bit in the filter comparison

0 = Don't include bit in the filter comparison

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

Register 23-18: CiRXMnEIDL: Acceptance Filter Mask n Extended Identifier Low

| U           |          |       |       |       |       |     |       |

|-------------|----------|-------|-------|-------|-------|-----|-------|

| Upper Byte: |          |       |       |       | •     | •   |       |

| R/W-x       | R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | U-0 | U-0   |

|             | EID<5:0> |       |       |       |       |     | _     |

| bit 15      |          |       |       |       |       |     | bit 8 |

| Lower Byte | :   |     |     |     |     |     |       |

|------------|-----|-----|-----|-----|-----|-----|-------|

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _          | _   | _   | _   | _   | _   | _   | _     |

| bit 7      |     |     |     |     |     |     | bit 0 |

bit 15-10 **EID<5:0>:** Extended Identifier bits bit 9-0 **Unimplemented:** Read as '0'

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## 23.2.6 CAN Baud Rate Registers

This subsection describes the CAN baud rate registers.

## Register 23-19: CiCFG1: Baud Rate Configuration Register 1

| Upper Byte: |     |     |     |     |     |     |       |  |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |  |  |  |

| _           | _   | _   | _   | _   | _   | _   | _     |  |  |  |

| bit 15      |     |     |     |     |     |     | bit 8 |  |  |  |

| Lower Byte: |       |       |       |       |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| SJW<1:0>    |       |       | BRP<  | 5:0>  |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

```

bit 15-8 Unimplemented: Read as '0'

```

```

bit 7-6

SJW<1:0>: Synchronized Jump Width bits

11 = Synchronized jump width time is 4 x TQ

10 = Synchronized jump width time is 3 x TQ

01 = Synchronized jump width time is 2 x TQ

00 = Synchronized jump width time is 1 x TQ

bit 5-0

BRP<5:0>: Baud Rate Prescaler bits

11 1111 = TQ = 2 x (BRP + 1)/FCAN = 128/FCAN

```

```

11 1111 = TQ = 2 x (BRP + 1)/Fcan = 128/Fcan

11 1110 = TQ = 2 x (BRP + 1)/Fcan = 126/Fcan

.

.

00 0001 = TQ = 2 x (BRP + 1)/Fcan = 4/Fcan

00 0000 = TQ = 2 x (BRP + 1)/Fcan = 2/Fcan

```

Note: FCAN is FCY or 4 FCY, depending on the CANCKS bit setting.

```

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

```

## Register 23-20: CiCFG2: Baud Rate Configuration Register 2

| Upper Byte | :      |     |     |     |             |       |       |

|------------|--------|-----|-----|-----|-------------|-------|-------|

| U-0        | R/W-x  | U-0 | U-0 | U-0 | R/W-x       | R/W-x | R/W-x |

| _          | WAKFIL | _   | _   | _   | SEG2PH<2:0> |       |       |

| bit 15     |        |     |     |     |             |       | bit 8 |

| Lower Byte:  |       |       |           |       |       |           |              |

|--------------|-------|-------|-----------|-------|-------|-----------|--------------|

| R/W-x        | R/W-x | R/W-x | R/W-x     | R/W-x | R/W-x | R/W-x     | R/W-x        |

| SEG2PHT<br>S | SAM   | S     | EG1PH<2:0 | >     |       | PRSEG<2:0 | <b> &gt;</b> |

| bit 7        |       |       |           |       |       |           | bit 0        |

bit 15 Unimplemented: Read as '0'

bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit

1 = Use CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 Unimplemented: Read as '0'

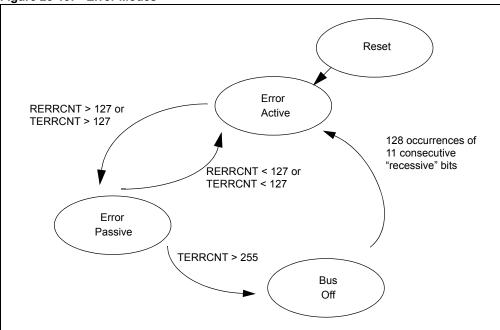

bit 10-8 **SEG2PH<2:0>:** Phase Buffer Segment 2 bits

111 = length is 8 x TQ

.

000 = length is 1 x TQ

bit 7 **SEG2PHTS:** Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PH or information processing time (3 TQ's), whichever is greater

bit 6 SAM: Sample of the CAN bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Buffer Segment 1 bits

111 = length is 8 x TQ

•

000 = length is  $1 \times TQ$

bit 2-0 **PRSEG<2:0>:** Propagation Time Segment bits

111 = length is 8 x TQ

.

000 = length is 1 x TQ

## Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

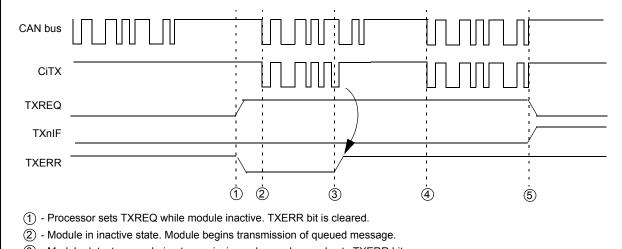

## 23.2.7 CAN Module Error Count Register

This subsection describes the CAN Module Transmission/Reception Error Count register. The various error status flags are present in the CAN Interrupt Flag Register.

## Register 23-21: CiEC: Transmit/Receive Error Count

| Upper Byte: | :            |     |     |     |     |     |       |  |  |

|-------------|--------------|-----|-----|-----|-----|-----|-------|--|--|

| R-0         | R-0          | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |

|             | TERRCNT<7:0> |     |     |     |     |     |       |  |  |

| bit 15      |              |     |     |     |     |     | bit 8 |  |  |

| Lower Byte: |              |     |     |     |     |     |       |  |  |

|-------------|--------------|-----|-----|-----|-----|-----|-------|--|--|

| R-0         | R-0          | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |

|             | RERRCNT<7:0> |     |     |     |     |     |       |  |  |

| bit 7       |              |     |     |     |     |     | bit 0 |  |  |

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

| Legend:           |                  |                                           |

|-------------------|------------------|-------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared $x = Bit$ is unknown |

## 23.2.8 CAN Interrupt Registers

This subsection describes the CAN Registers which are associated with interrupts.

#### Register 23-22: CilNTE: Interrupt Enable Register

| Upper Byte | <b>:</b> : |     |     |     |     |     |       |

|------------|------------|-----|-----|-----|-----|-----|-------|

| U-0        | U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _          | _          | _   | _   | _   | _   | _   | _     |

| bit 15     |            |     |     |     |     |     | bit 8 |

| Lower Byte | •     |       |       |       |       |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IVRIE      | WAKIE | ERRIE | TX2IE | TX1IE | TX0IE | RX1IE | RX0IE |

| bit 7      |       |       |       |       |       |       | bit 0 |

## bit 15-8 Unimplemented: Read as '0'

bit 7 IVRIE: Invalid Message Received Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 WAKIE: Bus Wake Up Activity Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 5 **ERRIE:** Error Interrupt Enable bit

1 = Enabled0 = Disabled

bit 4 **TX2IE:** Transmit Buffer 2 Interrupt Enable bit

1 = Enabled0 = Disabled

bit 3 **TX1IE:** Transmit Buffer 1 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 **TX0IE:** Transmit Buffer 0 Interrupt Enable bit

1 = Enabled0 = Disabled

bit 1 RX1IE: Receive Buffer 1 Interrupt Enable bit

1 = Enabled 0 = Disabled

bit 0 **RX0IE:** Receive Buffer 0 Interrupt Enable bit

1 = Enabled0 = Disabled

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

## Register 23-23: CilNTF: Interrupt Flag Register

| Upper Byte | •      |      |      |      |       |       |       |

|------------|--------|------|------|------|-------|-------|-------|

| R/C-0      | R/C-0  | R-0  | R-0  | R-0  | R-0   | R-0   | R-0   |

| RX00VR     | RX10VR | TXBO | TXEP | RXEP | TXWAR | RXWAR | EWARN |

| bit 15     |        |      |      |      |       |       | bit 8 |

| Lower Byte | :     |       |       |       |       |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IVRIF      | WAKIF | ERRIF | TX2IF | TX1IF | TX0IF | RX1IF | RX0IF |

| bit 7      |       |       |       |       |       |       | bit 0 |

- bit 15 RX0OVR: Receive Buffer 0 Overflowed bit

- 1 = Receive buffer 0 overflowed

- 0 = Receive buffer 0 not overflowed

- bit 14 RX10VR: Receive Buffer 1 Overflowed bit

- 1 = Receive buffer 1 overflowed

- 0 = Receive buffer 1 not overflowed

- bit 13 **TXBO:** Transmitter in Error State, Bus Off bit

- 1 = Transmitter in error state, bus off

- 0 = Transmitter not in error state, bus off

- bit 12 **TXEP:** Transmitter in Error State, Bus Passive bit

- 1 = Transmitter in error state, bus passive

- 0 = Transmitter not in error state, bus passive

- bit 11 RXEP: Receiver in Error State, Bus Passive bit

- 1 = Receiver in error state, bus passive

- 0 = Receiver not in error state, bus passive

- bit 10 TXWAR: Transmitter in Error State, Warning bit

- 1 = Transmitter in error state, warning

- 0 = Transmitter not in error state, warning

- bit 9 **RXWAR:** Receiver in Error State, Warning bit

- 1 = Receiver in error state, warning

- 0 = Receiver not in error state, warning

- bit 8 **EWARN:** Transmitter or Receiver is in Error State, Warning bit

- 1 = Transmitter or receiver is in error state, warning

- 0 = Transmitter and receiver are not in error state

- bit 7 IVRIF: Invalid Message Received Interrupt Flag bit

- 1 = Some type of error occurred during reception of the last message

- 0 = Receive error has not occurred

- bit 6 WAKIF: bus Wake-up Activity Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 5 **ERRIF:** Error Interrupt Flag bit (multiple sources in CilNTF<15:8> register)

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 4 TX2IF: Transmit Buffer 2 Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 3 **TX1IF:** Transmit Buffer 1 Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## Register 23-23: CilNTF: Interrupt Flag Register (Continued)

bit 2 **TX0IF:** Transmit Buffer 0 Interrupt Flag bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 1 RX1IF: Receive Buffer 1 Interrupt Flag bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 0 **RX0IF:** Receive Buffer 0 Interrupt Flag bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

## Legend:

R = Readable bit W = Writable bit C = Bit can be cleared U = Unimplemented bit, read as '0'

DS70070D-page 23-22

## 23.3 Register Maps

Table 23-1: CAN1 Register Map

| File Name  | ADR | Bit 15 | Bit 14 | Bit 13 | Bit 12         | Bit 11       | Bit 10   | Bit 9  | Bit 8 | Bit 7           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset |

|------------|-----|--------|--------|--------|----------------|--------------|----------|--------|-------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| C1RXF0SID  | 300 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<5 | 5:0>  |       |       | _     | EXIDE | xxxx  |

| C1RXF0EIDH | 302 | _      | _      | _      | _              |              | EID<     | 17:14> |       | EID<13:6>       |       |       |       |       |       |       |       | xxxx  |

| C1RXF0EIDL | 304 |        |        | EID<   | 5:0>           |              |          | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| unused     | 306 | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| C1RXF1SID  | 308 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<  | 5:0>  |       | •     | _     | EXIDE | xxxx  |

| C1RXF1EIDH | 30A | _      | _      | _      | _              | — EID<17:14> |          |        |       |                 |       |       | EID<1 | 3:6>  |       |       |       | xxxx  |

| C1RXF1EIDL | 30C |        |        | EID<   | :5:0>          |              |          | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| Unused     | 30E | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| C1RXF2SID  | 310 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<  | 5:0>  |       |       | _     | EXIDE | xxxx  |

| C1RXF2EIDH | 312 | _      | _      | _      | -              |              | EID<     | 17:14> |       |                 |       |       | EID<1 | 3:6>  |       |       |       | xxxx  |

| C1RXF2EIDL | 314 |        |        | EID<   | :5:0>          |              |          | _      | -     | _               | _     | _     | _     | _     | _     | _     | _     | XXXX  |

| Unused     | 316 | _      | _      | _      | 1              | _            | _        | _      | 1     | _               | _     | _     | _     | _     | _     | _     | _     | XXXX  |

| C1RXF3SID  | 318 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<5 | 5:0>  |       |       | _     | EXIDE | XXXX  |

| C1RXF3EIDH | 31A | _      | _      | _      | 1              | — EID<17:14> |          |        |       |                 |       |       | EID<1 | 3:6>  |       |       |       | XXXX  |

| C1RXF3EIDL | 31C |        |        | EID<   | :5:0>          |              |          | _      | -     | _               | _     | _     | _     | _     | _     | _     | _     | XXXX  |

| Unused     | 31E | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | XXXX  |

| C1RXF4SID  | 320 | _      | _      | _      |                |              | SID<10:6 | >      |       | SID<5:0>        |       |       |       |       |       |       | EXIDE | xxxx  |

| C1RXF4EIDH | 322 | _      | _      | _      | _              |              | EID<     | 17:14> |       | EID<13:6>       |       |       |       |       |       |       |       | xxxx  |

| C1RXF4EIDL | 324 |        |        | EID<   | 5:0>           |              |          | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| Unused     | 326 | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| C1RXF5SID  | 328 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<  | 5:0>  |       |       | _     | EXIDE | xxxx  |

| C1RXF5EIDH | 32A | _      | _      | _      | _              |              | EID<     | 17:14> |       | EID<13:6>       |       |       |       |       |       |       |       | xxxx  |

| C1RXF5EIDL | 32C |        |        | EID<   | 5:0>           |              |          | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| Unused     | 32E | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| C1RXM0SID  | 330 | _      | _      | _      |                |              | SID<10:6 | >      |       |                 |       | SID<  | 5:0>  |       |       | _     | MIDE  | xxxx  |

| C1RXM0EIDH | 332 | _      | _      | _      | _              |              | EID<     | 17:14> |       | EID<13:6>       |       |       |       |       |       |       | xxxx  |       |

| C1RXM0EIDL | 334 |        |        | EID<   | 5:0>           |              |          | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| Unused     | 336 | _      | _      | _      | _              | _            | _        | _      | _     | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| C1RXM1SID  | 338 | _      | _      | _      | SID<10:6>      |              |          |        |       | SID<5:0> — MIDE |       |       |       |       |       |       |       | xxxx  |

| C1RXM1EIDH | 33A | _      | _      | _      | — EID<17:14>   |              |          |        |       |                 |       |       | EID<1 | 3:6>  |       |       |       | XXXX  |

| C1RXM1EIDL | 33C |        |        | EID<   | EID<5:0> — — — |              |          |        |       | _               | _     | _     | _     | _     | _     | _     | _     | xxxx  |

| Unused     | 33E | _      | _      |        |                | _            | _        | _      | _     | _               | _     | _     | _     |       | _     | _     | _     | xxxx  |

Table 23-1: CAN1 Register Map (Continued)

| File Name | ADR | Bit 15                   | Bit 14 | Bit 13    | Bit 12     | Bit 11       | Bit 10 | Bit 9     | Bit 8     | Bit 7                    | Bit 6     | Bit 5      | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0     | Reset |  |

|-----------|-----|--------------------------|--------|-----------|------------|--------------|--------|-----------|-----------|--------------------------|-----------|------------|-------------|-------------|-------|-------|-----------|-------|--|

| C1TX2SID  | 340 |                          |        | SID<10:6> |            |              | _      | _         | _         |                          |           | SID<       | 5:0>        |             |       | SRR   | TX<br>IDE | xxxx  |  |

| C1TX2EID  | 342 |                          | EID<   | 17:14>    |            | _            | _      | _         | _         |                          |           |            | EID<1       | 3:6>        |       |       |           | xxxx  |  |

| C1TX2DLC  | 342 |                          |        | EID<      | :5:0>      |              |        | TX<br>RTR | TX<br>RB1 | TX<br>RB0                |           |            |             |             |       |       | _         | xxxx  |  |

| C1TX2B1   | 346 |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 1    |           |           |                          |           | Tra        | ansmit Buff | er 0 Byte 0 | )     |       |           | xxxx  |  |

| C1TX2B2   | 348 |                          |        | T         | ransmit Bı | uffer 0 Byte | e 3    |           |           |                          |           | Tra        | ansmit Buff | er 0 Byte 2 | 2     |       |           | xxxx  |  |

| C1TX2B3   | 34A |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 5    |           |           |                          |           | Tra        | ansmit Buff | er 0 Byte 4 | ļ     |       |           | xxxx  |  |

| C1TX2B4   | 34C | Transmit Buffer 0 Byte 7 |        |           |            |              |        |           |           |                          |           | Tra        | ansmit Buff | er 0 Byte 6 | 6     |       |           | xxxx  |  |

| C1TX2CON  | 34E | _                        | -      | _         | 1          | _            | _      | _         | _         | _                        | TX<br>ABT | TX<br>LARB | TX<br>ERR   | TX<br>REQ   | _     | TXPR  | l<1:0>    | 0000  |  |

| C1TX1SID  | 350 |                          |        | SID<10:6> | ,          |              | _      | _         | _         |                          |           | SID<       | 5:0>        |             |       | SRR   | TX<br>IDE | xxxx  |  |

| C1TX1EID  | 352 |                          | EID<   | 17:14>    |            | _            | _      | _         | _         | EID<13:6>                |           |            |             |             |       |       |           | xxxx  |  |

| C1TX1DLC  | 352 |                          |        | EID<      | :5:0>      |              |        | TX<br>RTR | TX<br>RB1 | TX<br>RB0                |           | DLC<       | 3:0>        |             | _     | _     | _         | xxxx  |  |

| C1TX1B1   | 356 |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 1    | •         |           |                          |           | Tra        | ansmit Buff | er 0 Byte 0 | )     |       |           | xxxx  |  |

| C1TX1B2   | 358 |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 3    |           |           | Transmit Buffer 0 Byte 2 |           |            |             |             |       |       |           |       |  |

| C1TX1B3   | 35A |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 5    |           |           | Transmit Buffer 0 Byte 4 |           |            |             |             |       |       |           |       |  |

| C1TX1B4   | 35C |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 7    |           |           | Transmit Buffer 0 Byte 6 |           |            |             |             |       |       |           |       |  |

| C1TX1CON  | 35E | _                        | -      | _         | -          | _            | _      | _         | _         | _                        | TX<br>ABT | TX<br>LARB | TX<br>ERR   | TX<br>REQ   | _     | TXPR  | I<1:0>    | 0000  |  |

| C1TX0SID  | 360 |                          |        | SID<10:6> |            |              | _      | _         | _         |                          |           | SID<       | 5:0>        |             |       | SRR   | TX<br>IDE | xxxx  |  |

| C1TX0EID  | 362 |                          | EID<   | 17:14>    |            | _            | _      | _         | _         |                          |           |            | EID<1       | 3:6>        |       | •     |           | xxxx  |  |

| C1TX0DLC  | 362 |                          |        | EID<      | :5:0>      |              |        | TX<br>RTR | TX<br>RB1 | TX<br>RB0                |           | DLC<       | 3:0>        |             | _     | _     | _         | xxxx  |  |

| C1TX0B1   | 366 | Transmit Buffer 0 Byte 1 |        |           |            |              |        |           |           | Transmit Buffer 0 Byte 0 |           |            |             |             |       |       |           |       |  |

| C1TX0B2   | 368 |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 3    |           |           | Transmit Buffer 0 Byte 2 |           |            |             |             |       |       |           |       |  |

| C1TX0B3   | 36A |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 5    |           |           | Transmit Buffer 0 Byte 4 |           |            |             |             |       |       |           |       |  |

| C1TX0B4   | 36C |                          |        | Т         | ransmit Bu | uffer 0 Byte | e 7    |           |           |                          |           | Tra        | ansmit Buff | er 0 Byte 6 | 3     |       |           | xxxx  |  |

| C1TX0CON  | 36E | _                        | _      | _         | _          | _            | _      | _         | _         | _                        | TX<br>ABT | TX<br>LARB | TX<br>ERR   | TX<br>REQ   | _     | TXPR  | I<1:0>    | 0000  |  |

Table 23-1: CAN1 Register Map (Continued)

| File Name | ADR        | Bit 15                  | Bit 14      | Bit 13    | Bit 12     | Bit 11       | Bit 10     | Bit 9      | Bit 8     | Bit 7                   | Bit 6     | Bit 5     | Bit 4        | Bit 3           | Bit 2        | Bit 1      | Bit 0           | Reset |

|-----------|------------|-------------------------|-------------|-----------|------------|--------------|------------|------------|-----------|-------------------------|-----------|-----------|--------------|-----------------|--------------|------------|-----------------|-------|

| C1RX1SID  | 370        | _                       | _           | _         |            |              | SID<10:6   | >          |           |                         |           | SID<      | 5:0>         |                 |              | SRR        | RX<br>IDE       | xxxx  |

| C1RX1EID  | 372        | _                       | _           | _         | _          |              | EID<       | 17:14>     |           |                         |           |           | EID<1        | 3:6>            |              |            |                 | xxxx  |

| C1RX1DLC  | 374        |                         |             | EID<      | :0:5>      |              |            | RX<br>RTR  | RX<br>RB1 | RX DLC<3:0>             |           |           |              |                 |              |            |                 | xxxx  |

| C1RX1B1   | 376        |                         |             | F         | Receive Bu | ıffer 1 Byte | e 1        |            |           |                         |           | Re        | eceive Buff  | er 1 Byte 0     |              |            |                 | XXXX  |

| C1RX1B2   | 378        |                         |             | F         | Receive Bu | ıffer 1 Byte | e 3        |            |           |                         |           | Re        | eceive Buff  | er 1 Byte 2     |              |            |                 | xxxx  |

| C1RX1B3   | 37A        |                         |             | F         | Receive Bu | ıffer 1 Byte | e 5        |            |           |                         |           | Re        | eceive Buff  | er 1 Byte 4     |              |            |                 | xxxx  |

| C1RX1B4   | 37C        | Receive Buffer 1 Byte 7 |             |           |            |              |            |            |           |                         |           | R         | eceive Buff  | er 1 Byte 6     |              |            |                 | xxxx  |

| C1RX1CON  | 37E        | _                       | _           | _         | _          | _            | _          | _          | _         | RX<br>FUL               | _         | _         | RX<br>ERR    | RX<br>RTR<br>R0 | F            | FILHIT<2:0 | >               | 0000  |

| C1RX1SID  | 380        | _                       | _           | _         |            |              | SID<10:6   | >          |           |                         |           | SID<      | 5:0>         |                 |              | SRR        | RX<br>IDE       | xxxx  |

| C1RX1EID  | 382        | _                       | _           | _         | _          |              | EID<       | 17:14>     |           | EID<13:6>               |           |           |              |                 |              |            |                 |       |

| C1RX1DLC  | 384        |                         |             | EID<      | :0:5>      |              |            | RX<br>RTR  | RX<br>RB1 | _                       | _         | _         | RX<br>RB0    |                 | DLC          | <3:0>      |                 | xxxx  |

| C1RX0B1   | 386        |                         |             | F         | Receive Bu | iffer 0 Byte | e 1        |            |           |                         |           | R         | eceive Buff  | er 0 Byte 0     |              |            |                 | xxxx  |

| C1RX0B2   | 388        |                         |             | F         | Receive Bu | iffer 0 Byte | e 3        |            |           | Receive Buffer 0 Byte 2 |           |           |              |                 |              |            |                 | xxxx  |

| C1RX0B3   | 38A        |                         |             | F         | Receive Bu | iffer 0 Byte | e 5        |            |           | Receive Buffer 0 Byte 4 |           |           |              |                 |              |            |                 | XXXX  |

| C1RX0B4   | 38C        |                         |             | F         | Receive Bu | iffer 0 Byte | e 7        |            |           | Receive Buffer 0 Byte 6 |           |           |              |                 |              |            |                 | xxxx  |

| C1RX0CON  | 38E        | _                       | _           | _         | -          | _            | _          | _          | _         | RX<br>FUL               | -         | _         | RX<br>ERR    | RX<br>RTR<br>R0 | RXB0<br>DBEN | JTOFF      | FIL<br>HIT<br>0 | 0000  |

| C1CTRL    | 390        | CAN<br>CAP              | _           | C<br>SIDL | ABAT       | CAN<br>CKS   | F          | REQOP<2    | :0>       | OF                      | PMODE<2:  | 0>        | _            | ı               | CODE<2:0     | )>         | _               | 0480  |

| C1CFG1    | 392        | _                       | _           | _         | _          | _            | _          | _          | _         | SJW<                    | 1:0>S     |           | •            | BRP<            | <5:0>        |            | •               | 0000  |

| C1CFG2    | 394        | _                       | WAK<br>FIL  | _         | _          | _            | S          | EG2PH<2    | :0>       | SEG2<br>PHTS            | SAM       | SI        | EG1PH<2:0    | )>              | F            | PRSEG<2:0  | )>              | 0000  |

| C1INTF    | 396        | RXB0<br>OVR             | RXB1<br>OVR | TXBO      | TXBP       | RXBP         | TX<br>WARN | RX<br>WARN | E<br>WARN | IVR<br>IF               | WAK<br>IF | ERR<br>IF | TXB2<br>IF   | TXB1<br>IF      | TXB0<br>IF   | RXB1<br>IF | RXB0<br>IF      | 0000  |

| C1INTE    | 398        | _                       | _           | _         | _          | _            | _          | _          | _         | IVR<br>IE               | WAK<br>IE | ERR<br>IE | TXB2<br>IE   | TXB1<br>IE      | TXB0<br>IE   | RXB1<br>IE | RXB0<br>IE      | 0000  |

| C1EC      | 39A        |                         |             | 7         | Γransmit Ε | rror Count   | ter        |            |           |                         |           | R         | Receive Erro | or Counter      |              |            |                 | 0000  |

| Reserved  | 39C<br>3FE | _                       | _           | _         | _          | _            | _          | _          | _         | _                       | _         | _         | _            | _               | _            | _          | _               | xxxx  |

Table 23-2: CAN2 Register Map

| File Name  | ADR | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10   | Bit 9  | Bit 8 | Bit 7     | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset |  |

|------------|-----|--------|--------|--------|--------|------------|----------|--------|-------|-----------|-----------------|-------|-------|-------|-------|-------|-------|-------|--|

| C2RXF0SID  | 3C0 | _      | _      | _      |        |            | SID<10:6 | >      |       | SID<5:0>  |                 |       |       |       |       |       | EXIDE | XXXX  |  |

| C2RXF0EIDH | 3C2 | _      | _      | _      | _      |            | EID<     | 17:14> |       | EID<13:6> |                 |       |       |       |       |       |       | XXXX  |  |

| C2RXF0EIDL | 3C4 |        |        | EID<   | <5:0>  |            |          | _      | -     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| Unused     | 3C6 | _      | _      | _      | _      | _          | _        | _      | -     | _         | _               | _     | _     | _     | _     | -     | _     | xxxx  |  |

| C2RXF1SID  | 3C8 | _      | _      | _      |        |            | SID<10:6 | >      |       |           |                 | SID<  | 5:0>  |       |       | -     | EXIDE | xxxx  |  |

| C2RXF1EIDH | 3CA | -      | _      | _      | _      |            | EID<     | 17:14> |       |           |                 |       | EID<1 | 3:6>  | ā.    |       | xxxx  |       |  |

| C2RXF1EIDL | 3CC |        |        | EID<   | <5:0>  |            |          | _      | I     | -         | _               | _     | -     |       | _     | I     | -     | XXXX  |  |

| Unused     | 3CE | _      | _      | _      | _      | _          | _        | _      | 1     | _         | _               | _     | _     | _     | _     | -     | _     | xxxx  |  |

| C2RXF2SID  | 3D0 | -      | _      | _      |        |            | SID<10:6 | >      |       |           |                 | SID<  | 5:0>  |       |       | 1     | EXIDE | xxxx  |  |

| C2RXF2EIDH | 3D2 | _      | _      | _      | _      |            | EID<     | 17:14> |       |           |                 |       | EID<1 | 3:6>  |       |       |       | xxxx  |  |

| C2RXF2EIDL | 3D4 |        |        | EID<   | <5:0>  |            |          | _      | 1     | _         | _               | _     | _     | _     | _     | -     | _     | xxxx  |  |

| Unused     | 3D6 | _      | _      | _      | _      | _          | _        | _      | -     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| C2RXF3SIDH | 3D8 | _      | _      | _      |        |            | SID<10:6 | >      |       |           |                 | SID<  | 5:0>  |       |       | -     | EXIDE | xxxx  |  |

| C2RXF3EID  | 3DA | _      | _      | _      | _      |            | EID<     | 17:14> |       |           |                 |       | EID<1 | 3:6>  |       |       |       | xxxx  |  |

| C2RXF3EIDL | 3DC |        |        | EID<   | <5:0>  |            |          | _      | -     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| Unused     | 3DE | _      | _      | _      | _      | _          | _        | _      | 1     | _         | _               | _     | _     | _     | _     | -     | _     | xxxx  |  |

| C2RXF4SID  | 3E0 | _      | _      | _      |        |            | SID<10:6 | >      |       | SID<5:0>  |                 |       |       |       |       |       | EXIDE | xxxx  |  |

| C2RXF4EIDH | 3E2 | _      | _      | _      | _      |            | EID<     | 17:14> |       | EID<13:6> |                 |       |       |       |       |       |       | xxxx  |  |

| C2RXF4EIDL | 3E4 |        |        | EID<   | <5:0>  |            |          | _      | _     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| Unused     | 3E6 | _      | _      | _      | _      | _          | _        | _      | _     | _         | _               | _     | _     | _     | _     |       | _     | xxxx  |  |

| C2RXF5SID  | 3E8 | _      | _      | _      |        |            | SID<10:6 | >      |       |           |                 | SID<  | 5:0>  |       |       | _     | EXIDE | xxxx  |  |

| C2RXF5EIDH | 3EA | _      | _      | _      | _      |            | EID<     | 17:14> |       | EID<13:6> |                 |       |       |       |       |       |       | xxxx  |  |

| C2RXF5EIDL | 3EC |        |        | EID<   | <5:0>  |            |          | _      | _     | _         | _               | _     | _     | _     | _     |       | _     | xxxx  |  |

| Unused     | 3EE | _      | _      | _      | _      | _          | _        | _      | _     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| C2RXM0SID  | 3F0 | _      | _      | _      |        |            | SID<10:6 | >      |       |           |                 | SID<  | 5:0>  |       |       | _     | MIDE  | xxxx  |  |

| C2RXM0EIDH | 3F2 | _      | _      | _      | _      |            | EID<     | 17:14> |       |           |                 |       | EID<1 | 3:6>  |       |       |       | xxxx  |  |

| C2RXM0EIDL | 3F4 |        |        | EID<   | <5:0>  |            |          | _      | _     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| Unused     | 3F6 | _      | _      | _      | _      | _          | _        | _      | _     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| C2RXM1SID  | 3F8 | _      | _      | _      |        | SID<10:6>  |          |        |       |           | SID<5:0> — MIDE |       |       |       |       |       |       |       |  |

| C2RXM1EIDH | 3FA | _      | _      | _      | _      | EID<17:14> |          |        |       |           |                 |       | EID<1 | 3:6>  |       |       |       | xxxx  |  |

| C2RXM1EIDL | 3FC |        |        | EID<   | <5:0>  |            |          | _      | _     | _         | _               | _     | _     | _     | _     | _     | _     | xxxx  |  |

| Unused     | 3FE |        | _      |        | _      | _          |          | _      | -     | _         | _               | _     |       |       | _     | -     |       | xxxx  |  |

© 2003 Microchip Technology Inc.

Table 23-2: **CAN2** Register Map (Continued)

| File Name | ADR | Bit 15                   | Bit 14 | Bit 13                       | ,<br>Bit 12 | Bit 11      | Bit 10 | Bit 9     | Bit 8                                        | Bit 7                    | Bit 6     | Bit 5      | Bit 4       | Bit 3       | Bit 2 | Bit 1  | Bit 0     | Reset |

|-----------|-----|--------------------------|--------|------------------------------|-------------|-------------|--------|-----------|----------------------------------------------|--------------------------|-----------|------------|-------------|-------------|-------|--------|-----------|-------|

| C2TX2SID  | 400 |                          |        | SID<10:6>                    | •           |             | _      | _         | _                                            |                          |           | SID<5      | 5:0>        |             |       | SRR    | TX<br>IDE | xxxx  |

| C2TX2EID  | 402 |                          | EID<   | 17:14>                       |             | _           | _      | _         | -                                            | EID<13:6>                |           |            |             |             |       |        |           |       |

| C2TX2DLC  | 404 | EID<5:0>                 |        |                              |             |             |        |           |                                              | TX<br>RB0                |           | DLC<       | 3:0>        |             | _     | _      | _         | xxxx  |

| C2TX2B1   | 406 |                          |        | 1                            | ransmit B   | uffer 0 Byt | e 1    |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 0 | )     |        |           | XXXX  |

| C2TX2B2   | 408 | Transmit Buffer 0 Byte 3 |        |                              |             |             |        |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 2 | 2     |        |           | XXXX  |

| C2TX2B3   | 40A |                          |        | 1                            | ransmit B   | uffer 0 Byt | e 5    |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 4 | 1     |        |           | XXXX  |

| C2TX2B4   | 40C | Transmit Buffer 0 Byte 7 |        |                              |             |             |        |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 6 | 3     |        |           | XXXX  |

| C2TX2CON  | 40E | _                        | _      | _                            | _           | _           | _      | _         | _                                            | _                        | TX<br>ABT | TX<br>LARB | TX<br>ERR   | TX<br>REQ   | _     | TXPR   | l<1:0>    | 0000  |

| C2TX1SID  | 410 |                          |        | SID<10:6> — — — SID<5:0> SRR |             |             |        |           |                                              |                          | SRR       | TX<br>IDE  | xxxx        |             |       |        |           |       |

| C2TX1EID  | 412 |                          | EID<   | 17:14>                       |             | _           | _      | _         | _                                            | EID<13:6>                |           |            |             |             |       |        |           | XXXX  |

| C2TX1DLC  | 414 | EID<5:0> TX<br>RTR       |        |                              |             |             |        |           | TX<br>RB1                                    | TX<br>RB0                |           |            |             |             |       |        |           | xxxx  |

| C2TX1B1   | 416 |                          |        | 7                            | ransmit B   | uffer 0 Byt | e 1    |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 0 | )     |        |           | XXXX  |

| C2TX1B2   | 418 |                          |        | 7                            | ransmit B   | uffer 0 Byt | e 3    |           |                                              | Transmit Buffer 0 Byte 2 |           |            |             |             |       |        |           |       |

| C2TX1B3   | 41A |                          |        | 1                            | ransmit B   | uffer 0 Byt | e 5    |           |                                              | Transmit Buffer 0 Byte 4 |           |            |             |             |       |        |           |       |

| C2TX1B4   | 41C |                          |        | 7                            | ransmit Bu  | uffer 0 Byt | e 7    |           |                                              | Transmit Buffer 0 Byte 6 |           |            |             |             |       |        |           |       |

| C2TX1CON  | 41E | _                        | _      | _                            | _           | _           | _      | _         | _                                            | _                        | TX<br>ABT | TX<br>LARB | TX<br>ERR   | TX<br>REQ   | _     | TXPR   | I<1:0>    | 0000  |

| C2TX0SID  | 420 |                          |        | SID<10:6>                    | •           |             | _      | _         | _                                            |                          |           | SID<5      | 5:0>        |             |       | SRR    | TX<br>IDE | xxxx  |

| C2TX0EID  | 422 |                          | EID<   | 17:14>                       |             | _           | _      | _         | _                                            |                          |           |            | EID<1       | 3:6>        |       |        |           | XXXX  |

| C2TX0DLC  | 424 |                          |        | EID<                         | <5:0>       |             |        | TX<br>RTR | TX<br>RB1                                    | TX<br>RB0                |           | DLC<       | 3:0>        |             | _     | _      | _         | xxxx  |

| C2TX0B1   | 426 |                          |        | 7                            | ransmit B   | uffer 0 Byt | e 1    |           |                                              | Transmit Buffer 0 Byte 0 |           |            |             |             |       |        |           |       |

| C2TX0B2   | 428 |                          |        | 7                            | ransmit B   | uffer 0 Byt | e 3    |           |                                              | Transmit Buffer 0 Byte 2 |           |            |             |             |       |        |           |       |

| C2TX0B3   | 42A |                          |        | 1                            | ransmit B   | uffer 0 Byt | e 5    |           |                                              | Transmit Buffer 0 Byte 4 |           |            |             |             |       |        |           |       |

| C2TX0B4   | 42C |                          |        | 7                            | ransmit B   | uffer 0 Byt | e 7    |           |                                              |                          |           | Tra        | ansmit Buff | er 0 Byte 6 | 3     |        |           | xxxx  |

| C2TX0CON  | 42E | _                        | _      | _                            | _           | _           | _      | _         | TX TX TX TX TX - TXPRI<1:0> ABT LARB ERR REQ |                          |           |            |             |             |       | I<1:0> | 0000      |       |

DS70070D-page 23-27

#### 23.4 CAN Module Features

The CAN module is a communication controller implementing the CAN 2.0A/B protocol as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a Full CAN system.

The module features are as follows:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- Data length from 0-8 bytes

- · Programmable bit rate up to 1 Mbit/sec

- · Support for remote data frames

- · Double buffered receiver with two prioritized received message storage buffers

- Six full (standard/extended identifier) acceptance filters, 2 associated with the high priority receive buffer and 4 associated with the low priority receive buffer

- Two full acceptance filter masks, one each associated with the high and low priority receive buffers

- · Three Transmit Buffers with application specified prioritization and abort capability

- · Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- · Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- · Programmable link to input capture module for time-stamping and network synchronization

- · Low-Power Sleep mode

## 23.5 CAN Module Implementation

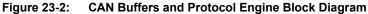

The CAN bus module consists of a Protocol Engine and message buffering and control. The Protocol Engine can best be understood by defining the types of data frames to be transmitted and received by the module. These blocks are shown in Figure 23-2.

## 23.5.1 CAN Message Formats

The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the two receive registers.

The CAN Module supports the following frame types:

- · Standard Data Frame

- · Extended Data Frame

- Remote Frame

- · Error Frame

- · Interframe Space

#### 23.5.1.1 Standard Data Frame

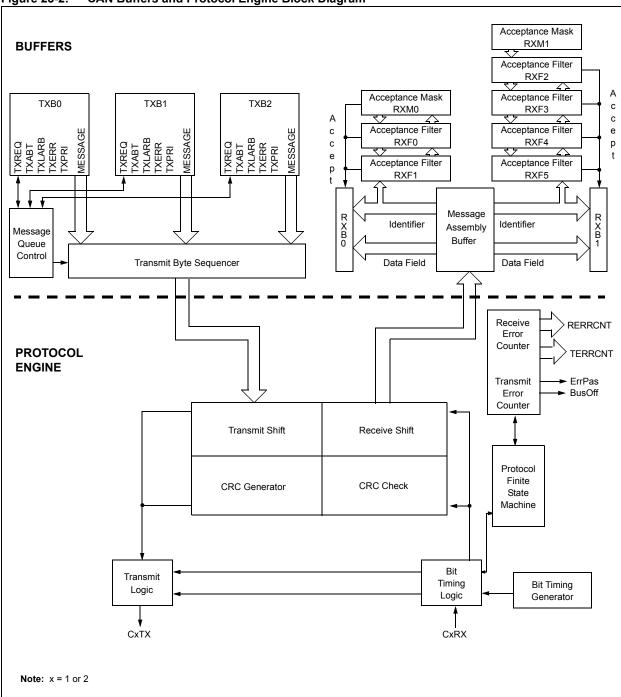

A standard data frame is generated by a node when the node wishes to transmit data. The standard CAN data frame is shown in Figure 23-3. In common with all other frames, the frame begins with a Start-Of-Frame bit (SOF-dominant state) for hard synchronization of all nodes.

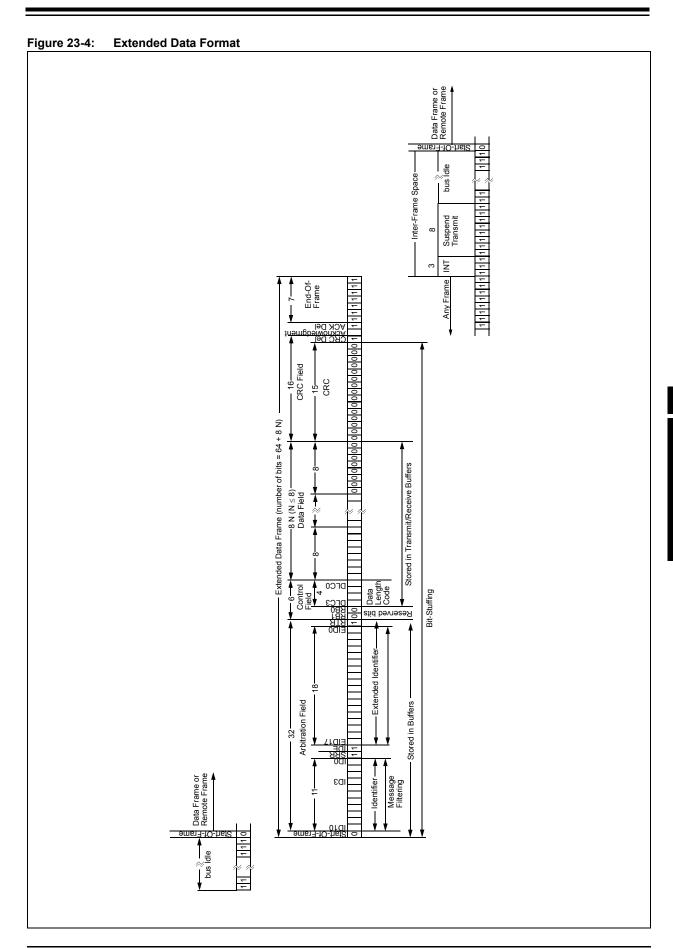

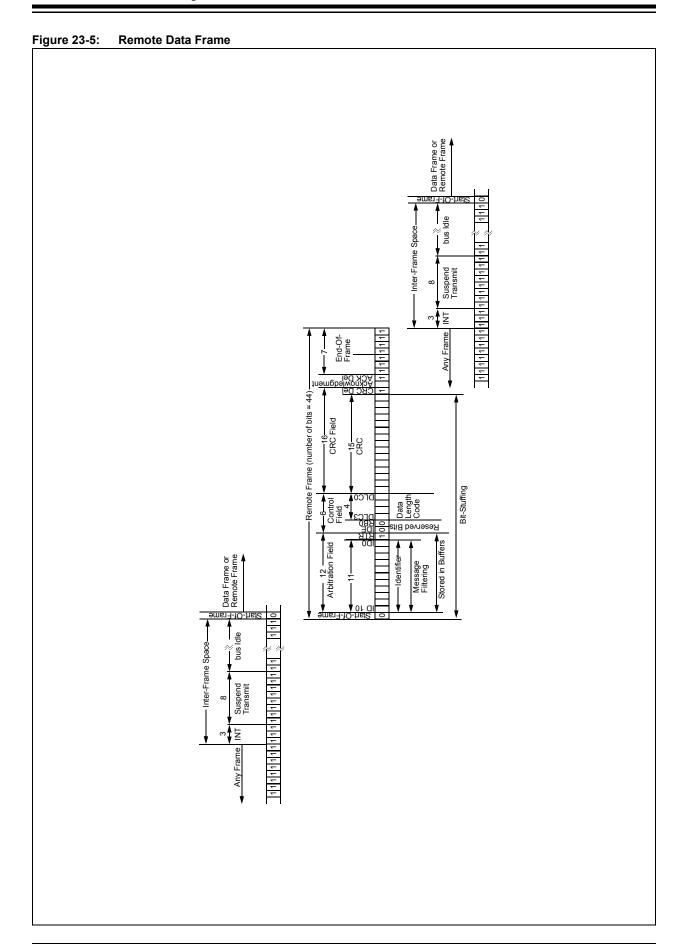

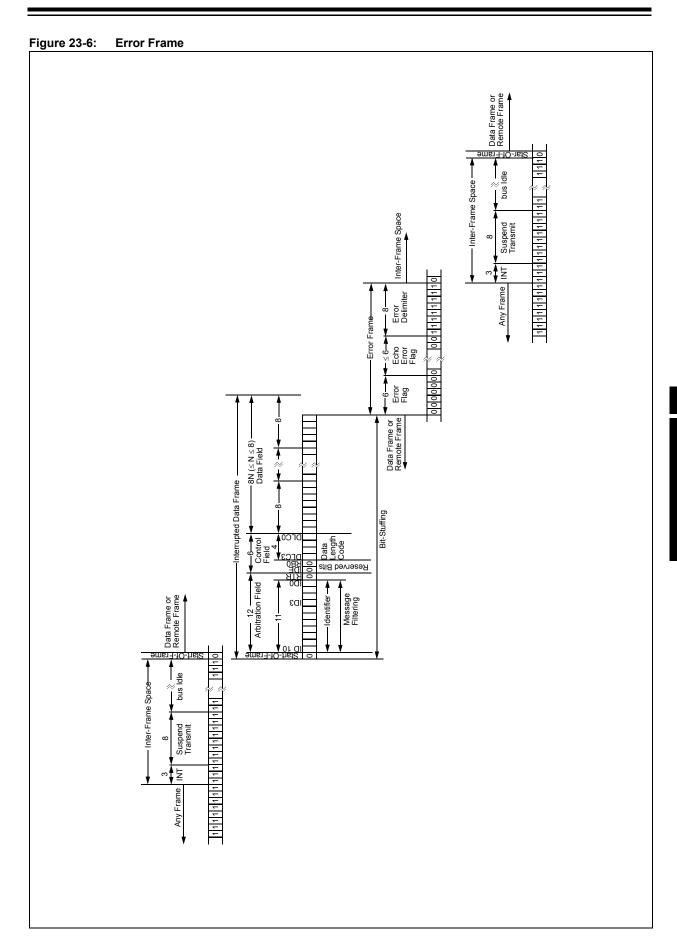

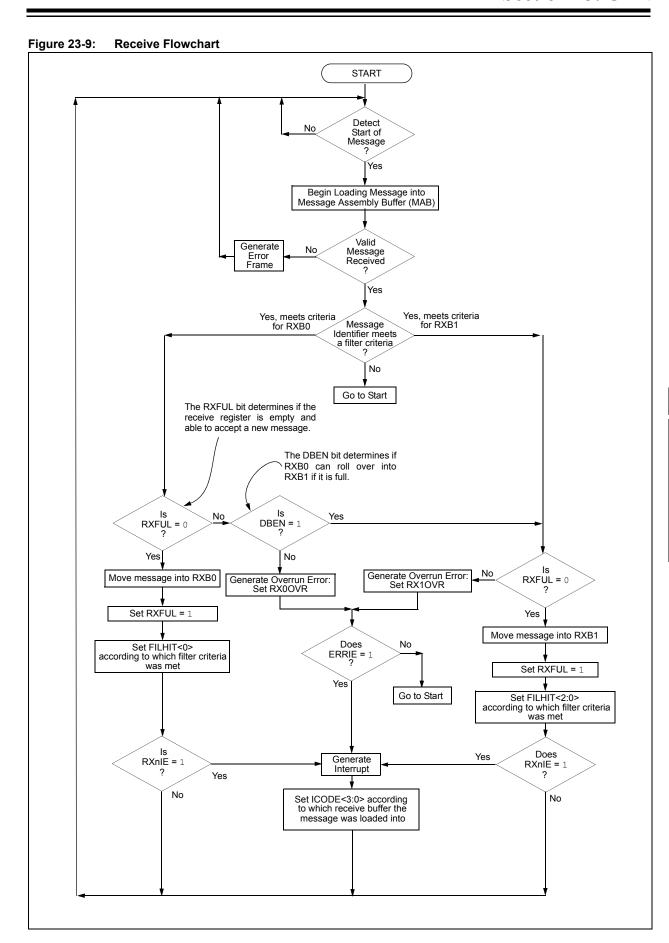

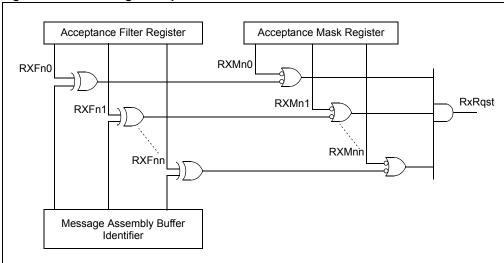

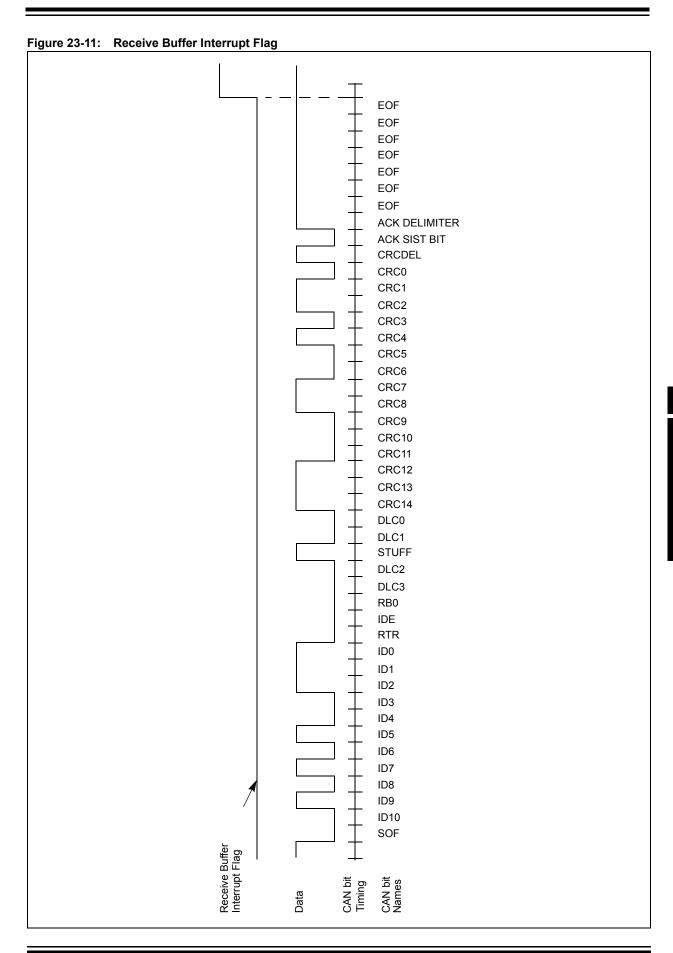

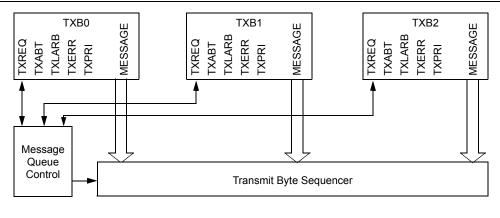

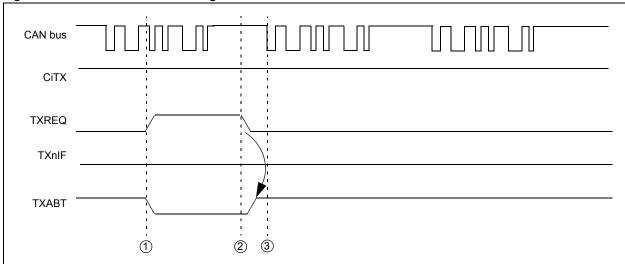

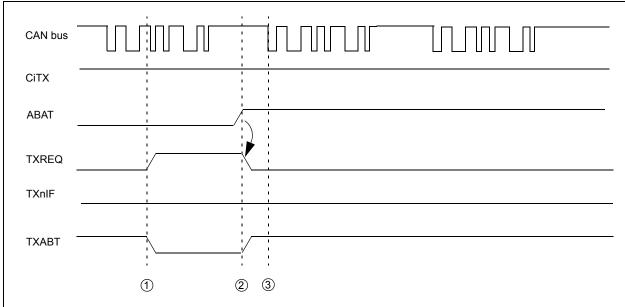

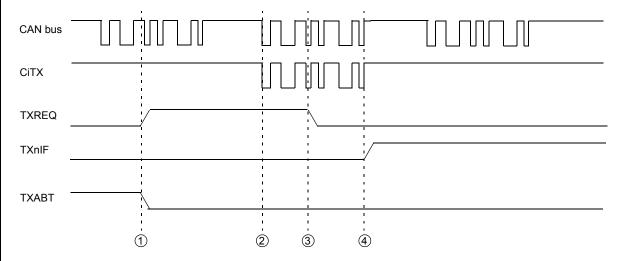

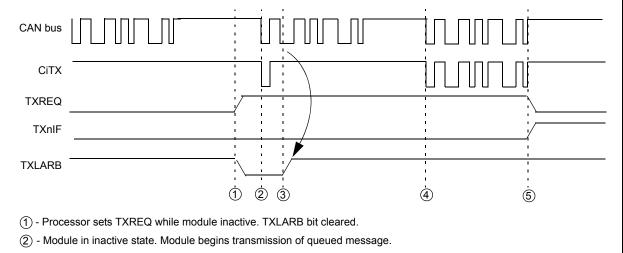

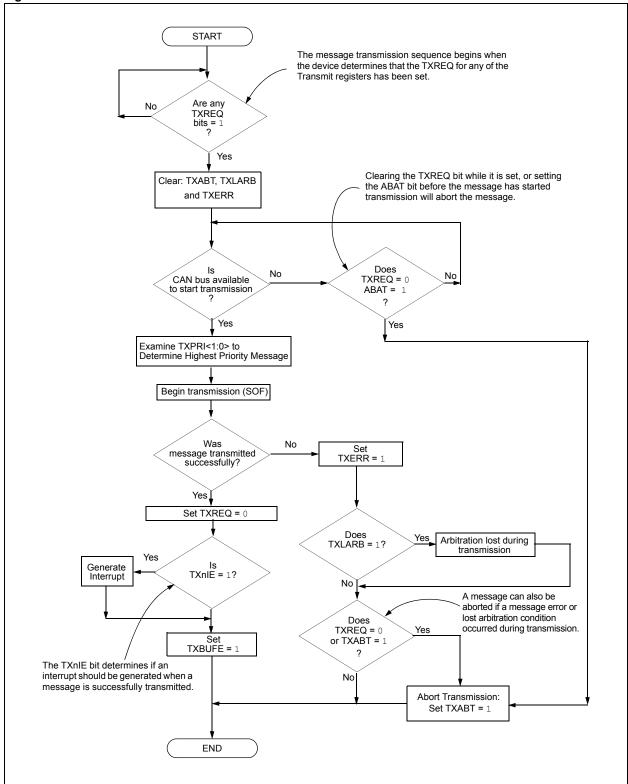

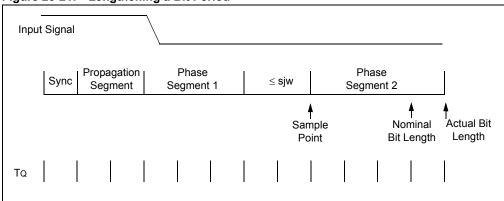

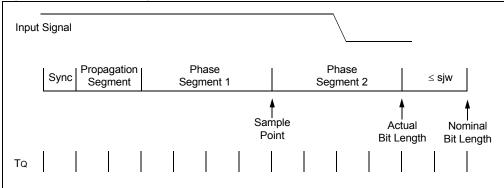

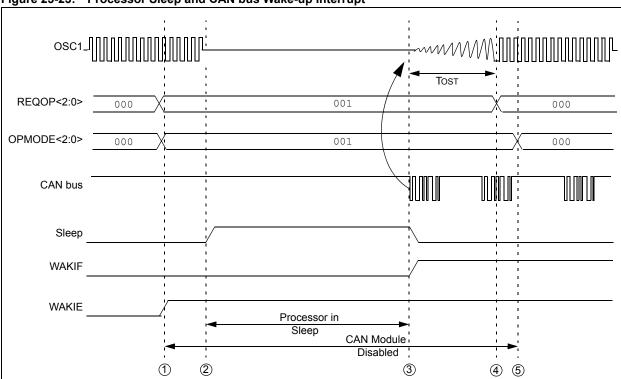

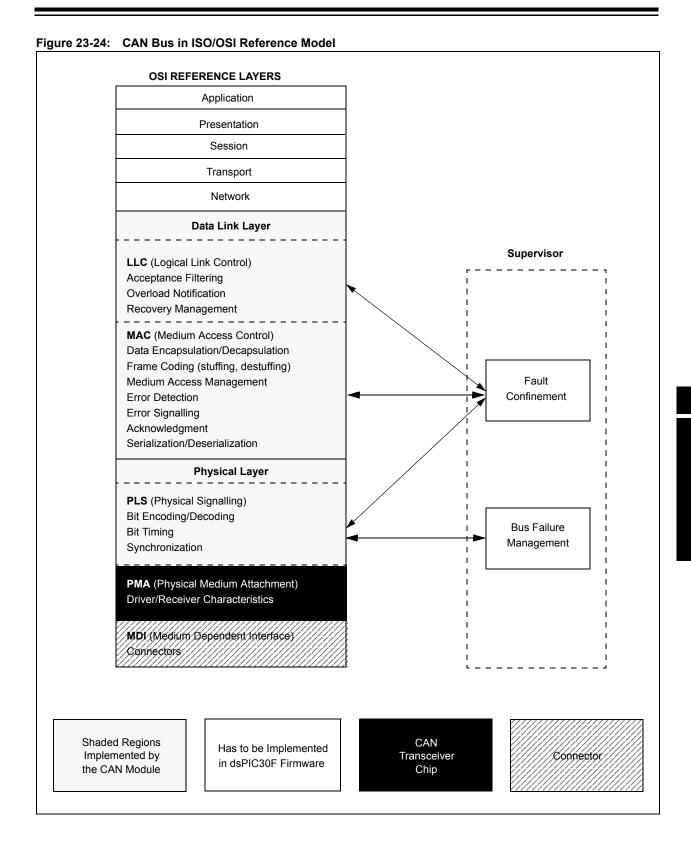

The SOF is followed by the Arbitration field consisting of 12 bits, the 11-bit identifier (reflecting the contents and priority of the message) and the Remote Transmission Request bit (RTR bit). The RTR bit is used to distinguish a data frame (RTR-dominant) from a remote frame.