# Section 21. Inter-Integrated Circuit<sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>)

## **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 21.1  | Overview                                                 | 21-2  |

|-------|----------------------------------------------------------|-------|

| 21.2  | I <sup>2</sup> C Bus Characteristics                     | 21-4  |

| 21.3  | Control and Status Registers                             | 21-8  |

| 21.4  | Enabling I <sup>2</sup> C Operation                      | 21-13 |

| 21.5  | Communicating as a Master in a Single-Master Environment | 21-15 |

| 21.6  | Communicating as a Master in a Multi-Master Environment  | 21-29 |

| 21.7  | Communicating as a Slave                                 | 21-32 |

| 21.8  | Connection Considerations for I <sup>2</sup> C Bus       | 21-47 |

| 21.9  | Module Operation During PWRSAV Instruction               | 21-49 |

| 21.10 | Effects of a Reset                                       | 21-49 |

| 21.11 | Register Maps                                            | 21-50 |

| 21.12 | Posign Tips                                              | 21-51 |

| 21.13 | Related Application Notes                                | 21-52 |

| 21.14 | Revision History                                         | 21-53 |

#### 21.1 Overview

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D converters and so on.

The I<sup>2</sup>C module can operate in any of the following I<sup>2</sup>C systems:

- · Where the dsPIC30F acts as a Slave Device

- Where the dsPIC30F acts as a Master Device in a Single Master System (Slave may also be active)

- Where the dsPIC30F acts as a Master/Slave Device in a Multi-Master System (Bus collision detection and arbitration available)

The  $I^2C$  module contains independent  $I^2C$  master logic and  $I^2C$  slave logic, each generating interrupts based on their events. In multi-master systems, the software is simply partitioned into master controller and slave controller.

When the I<sup>2</sup>C master logic is active, the slave logic remains active also, detecting the state of the bus and potentially receiving messages from itself in a single master system or from other masters in a multi-master system. No messages are lost during multi-master bus arbitration.

In a multi-master system, bus collision conflicts with other masters in the system are detected and the module provides a method to terminate then restart the message.

The I<sup>2</sup>C module contains a baud rate generator. The I<sup>2</sup>C baud rate generator does not consume other timer resources in the device.

#### 21.1.1 Module Features

- · Independent Master and Slave logic

- · Multi-Master support. No messages lost in arbitration

- · Detects 7-bit and 10-bit device addresses

- Detects general call addresses as defined in the I<sup>2</sup>C protocol

- · Bus Repeater mode. Accept all messages as a slave regardless of the address

- Automatic SCL clock stretching provides delays for the processor to respond to a slave data request

- · Supports 100 kHz and 400 kHz bus specifications

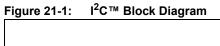

Figure 21-1 illustrates the I<sup>2</sup>C module block diagram.

## 21.2 I<sup>2</sup>C Bus Characteristics

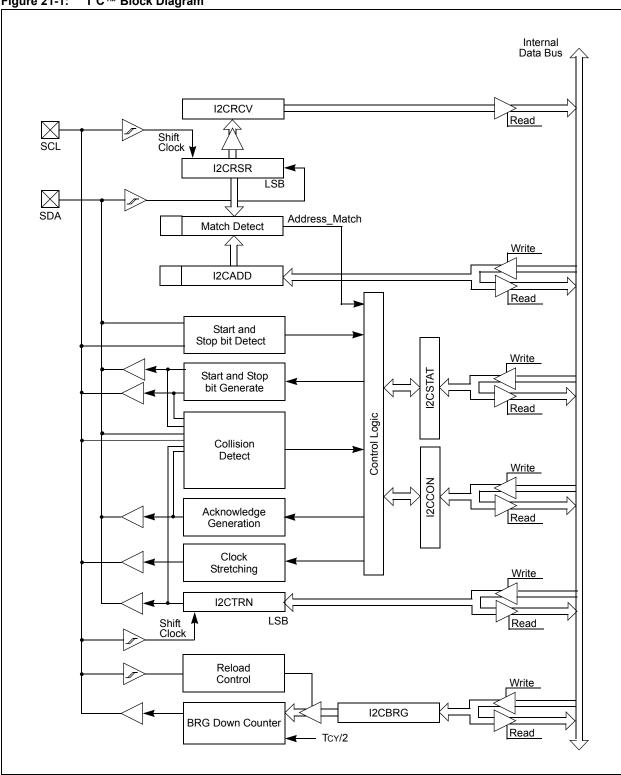

The I<sup>2</sup>C bus is a two-wire serial interface. Figure 21-2 is a schematic of a typical I<sup>2</sup>C connection between the dsPIC30F device and a 24LC256 I<sup>2</sup>C serial EEPROM.

The I<sup>2</sup>C interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When communicating, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave" responding to the transfer. The clock line, "SCL", is output from the master and input to the slave, although occasionally the slave drives the SCL line. The data line, "SDA", may be output and input from both the master and slave.

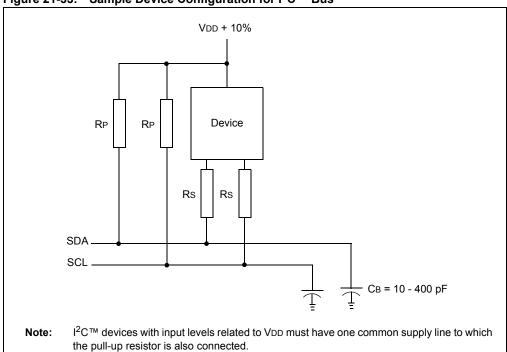

Because the SDA and SCL lines are bidirectional, the output stages of the devices driving the SDA and SCL lines must have an open drain in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down.

In the  $I^2C$  interface protocol, each device has an address. When a master wants to initiate a data transfer, it first transmits the address of the device that it wants to "talk" to. All devices "listen" to see if this is their address. Within this address, bit 'o' specifies if the master wants to read from or write to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is, they can be thought of as operating in either of these two relations:

- · Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases, the master originates the SCL clock signal.

Figure 21-2: Typical I<sup>2</sup>C™ Interconnection Block Diagram

#### 21.2.1 Bus Protocol

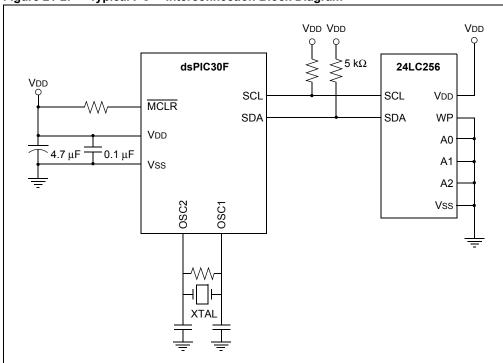

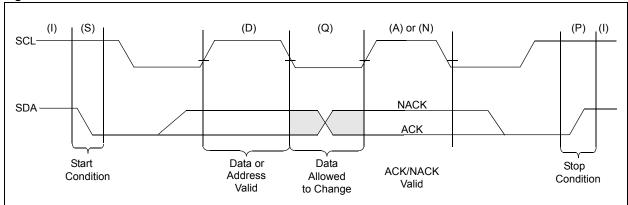

The following I<sup>2</sup>C bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the SCL clock line is HIGH.

Changes in the data line while the SCL clock line is HIGH will be interpreted as a Start or Stop condition.

Accordingly, the following bus conditions are defined in Figure 21-3.

### 21.2.1.1 Start Data Transfer (S)

After a bus Idle state, a HIGH-to-LOW transition of the SDA line while the clock (SCL) is HIGH determines a Start condition. All data transfers must be preceded by a Start condition.

#### 21.2.1.2 Stop Data Transfer (P)

A LOW-to-HIGH transition of the SDA line while the clock (SCL) is HIGH determines a Stop condition. All data transfers must end with a Stop condition.

#### 21.2.1.3 Repeated Start (R)

After a WAIT state, a HIGH-to-LOW transition of the SDA line while the clock (SCL) is HIGH determines a Repeated Start condition. Repeated Starts allow a master to change bus direction without relinquishing control of the bus.

## 21.2.1.4 Data Valid (D)

The state of the SDA line represents valid data when, after a Start condition, the SDA line is stable for the duration of the HIGH period of the clock signal. There is one bit of data per SCL clock.

#### 21.2.1.5 Acknowledge (A) or Not-Acknowledge (N)

All data byte transmissions must be Acknowledged (ACK) or Not-Acknowledged (NACK) by the receiver. The receiver will pull the SDA line low for an ACK or release the SDA line for a NACK. The Acknowledge is a one-bit period, using one SCL clock.

#### 21.2.1.6 WAIT/Data Invalid (Q)

The data on the line must be changed during the LOW period of the clock signal. Devices may also stretch the clock low time, by asserting a low on SCL line, causing a WAIT on the bus.

### 21.2.1.7 Bus Idle (I)

Both data and clock lines remain HIGH at those times after a Stop condition and before a Start condition.

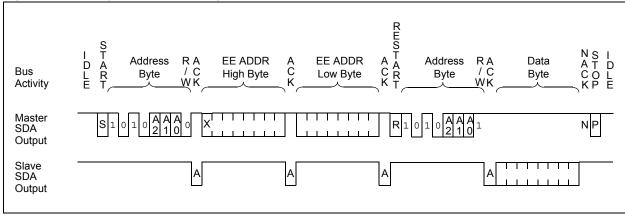

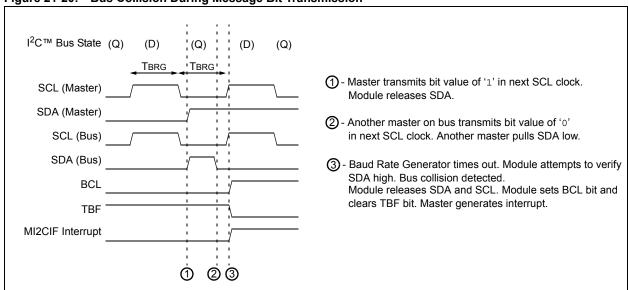

## 21.2.2 Message Protocol

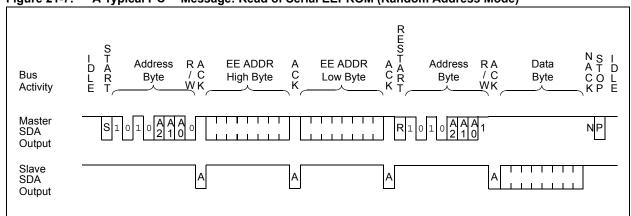

A typical  $I^2C$  message is shown in Figure 21-4. In this example, the message will read a specified byte from a 24LC256  $I^2C$  serial EEPROM. The dsPIC30F device will act as the master and the 24LC256 device will act as the slave.

Figure 21-4 indicates the data as driven by the master device and the data as driven by the slave device, remembering that the combined SDA line is a wired-AND of the master and slave data. The master device controls and sequences the protocol. The slave device will only drive the bus at specifically determined times.

Figure 21-4: A Typical I<sup>2</sup>C™ Message: Read of Serial EEPROM (Random Address Mode)

#### 21.2.2.1 Start Message

Each message is initiated with a "Start" condition and terminated with a "Stop" condition. The number of the data bytes transferred between the Start and Stop conditions is determined by the master device. As defined by the system protocol, the bytes of the message may have special meaning such as "device address byte" or "data byte".

### 21.2.2.2 Address Slave

In the Figure 21-4, the first byte is the device address byte that must be the first part of any  $I^2C$  message. It contains a device address and a R/W bit. Refer to "Section 26. Appendix" for additional information on Address Byte formats. Note that R/W = 0 for this first address byte, indicating that the master will be a transmitter and the slave will be a receiver.

#### 21.2.2.3 Slave Acknowledge

The receiving device is obliged to generate an Acknowledge signal, "ACK", after the reception of each byte. The master device must generate an extra SCL clock, which is associated with this Acknowledge bit.

#### 21.2.2.4 Master Transmit

The next 2 bytes, sent by the master to the slave, are data bytes containing the location of the requested EEPROM data byte. The slave must Acknowledge each of the data bytes.

### 21.2.2.5 Repeated Start

At this point, the slave EEPROM has the address information necessary to return the requested data byte to the master. However, the R/W bit from the first device address byte specified master transmission and slave reception. The bus must be turned in the other direction for the slave to send data to the master.

To do this function without ending the message, the master sends a "Repeated Start". The Repeated Start is followed with a device address byte containing the same device address as before and with the  $R\overline{W} = 1$  to indicate slave transmission and master reception.

## 21.2.2.6 Slave Reply

Now the slave transmits the data byte driving the SDA line, while the master continues to originate clocks but releases its SDA drive.

## 21.2.2.7 Master Acknowledge

During reads, a master must terminate data requests to the slave by NOT Acknowledging (generate a "NACK") on the last byte of the message.

## 21.2.2.8 Stop Message

The master sends Stop to terminate the message and return the bus to an Idle state.

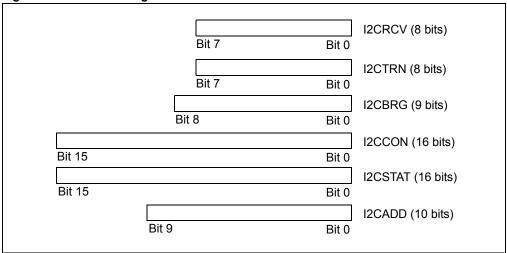

## 21.3 Control and Status Registers

The I<sup>2</sup>C module has six user-accessible registers for I<sup>2</sup>C operation. The registers are accessible in either Byte or Word mode. The registers are shown in Figure 21-5 and listed below:

- Control Register (I2CCON): This register allows control of the I<sup>2</sup>C operation.

- Status Register (I2CSTAT): This register contains status flags indicating the module state during I<sup>2</sup>C operation.

- Receive Buffer Register (I2CRCV): This is the buffer register from which data bytes can be read. The I2CRCV register is a read only register.

- Transmit Register (I2CTRN): This is the transmit register; bytes are written to this register during a transmit operation. The I2CTRN register is a read/write register.

- Address Register (I2CADD): The I2CADD register holds the slave device address.

- Baud Rate Generator Reload Register (I2CBRG): Holds the baud rate generator reload value for the I<sup>2</sup>C module baud rate generator.

Figure 21-5: I<sup>2</sup>C™ Programmer's Model

Register 21-1 and Register 21-2 define the I<sup>2</sup>C module Control and Status registers, I2CCON and I2CSTAT.

The I2CTRN is the register to which transmit data is written. This register is used when the module operates as a master transmitting data to the slave or as a slave sending reply data to the master. As the message progresses, the I2CTRN register shifts out the individual bits. Because of this, the I2CTRN may not be written to unless the bus is Idle. The I2CTRN may be reloaded while the current data is transmitting.

Data being received by either the master or the slave is shifted into a non-accessible Shift register called I2CRSR. When a complete byte is received, the byte transfers to the I2CRCV register. In receive operations, the I2CRSR and I2CRCV create a double-buffered receiver. This allows reception of the next byte to begin before reading the current byte of received data.

If the module receives another complete byte before the software reads the previous byte from the I2CRCV register, a receiver overflow occurs and sets the I2COV (I2CCON<6>). The byte in the I2CRSR is lost.

The I2CADD register holds the slave device address. In 10-bit mode, all bits are relevant. In 7-bit addressing mode, only I2CADD<6:0> are relevant. The A10M (I2CCON<10>) specifies the expected mode of the slave address.

| Register 21-1:   | I2CCON: I <sup>2</sup> C™ Contro | l Register |

|------------------|----------------------------------|------------|

| itogiotoi = i ii | 1200011.10                       | togiotoi   |

| Upper Byte: |     |         |             |                       |       |        |       |

|-------------|-----|---------|-------------|-----------------------|-------|--------|-------|

| R/W-0       | U-0 | R/W-0   | R/W-1<br>HC | R/W-0                 | R/W-0 | R/W-0  | R/W-0 |

| I2CEN       | _   | I2CSIDL | SCLREL      | IPMIEN <sup>(1)</sup> | A10M  | DISSLW | SMEN  |

| bit 15      |     |         |             |                       |       |        | bit 8 |

| Lower Byte | :     |       |             |            |           |            |           |

|------------|-------|-------|-------------|------------|-----------|------------|-----------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0       | R/W-0      | R/W-0     | R/W-0      | R/W-0     |

| GCEN       | STREN | ACKDT | HC<br>ACKEN | HC<br>RCEN | HC<br>PEN | HC<br>RSEN | HC<br>SEN |

| bit 7      |       |       |             |            |           |            | bit 0     |

- bit 15 **I2CEN:** I<sup>2</sup>C Enable bit

- 1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

- 0 = Disables I<sup>2</sup>C module. All I<sup>2</sup>C pins are controlled by port functions

- bit 14 Unimplemented: Read as '0'

- bit 13 I2CSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters an Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 **SCLREL:** SCL Release Control bit (when operating as I<sup>2</sup>C Slave)

- 1 = Release SCL clock

- 0 = Hold SCL clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software may write '0' to initiate stretch and write '1' to release clock)

Hardware clear at beginning of slave transmission.

Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software may only write '1' to release clock)

Hardware clear at beginning of slave transmission.

- bit 11 **IPMIEN:** Intelligent Platform Management Interface (IPMI) Enable bit<sup>(1)</sup>

- 1 = Enable IPMI Support mode. All addresses Acknowledged

- 0 = IPMI mode not enabled

- bit 10 A10M: 10-Bit Slave Address bit

- 1 = I2CADD is a 10-bit slave address

- 0 = I2CADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CRSR (module is enabled for reception)

- 0 = General call address disabled

- bit 6 **STREN:** SCL Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (When operating as I<sup>2</sup>C Master. Applicable during master receive.) Value that will be transmitted when the software initiates an Acknowledge sequence.

- 1 = Send NACK during acknowledge

- 0 = Send ACK during acknowledge

Note 1: The IPMIEN bit should not be set when operating as a master.

## dsPIC30F Family Reference Manual

## Register 21-1: I2CCON: I<sup>2</sup>C™ Control Register (Continued)

bit 4 ACKEN: Acknowledge Sequence Enable bit

(When operating as I<sup>2</sup>C master. Applicable during master receive.)

1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit Hardware clear at end of master Acknowledge sequence.

0 = Acknowledge sequence not in progress

bit 3 **RCEN**: Receive Enable bit (when operating as I<sup>2</sup>C master)

1 = Enables Receive mode for  $I^2C$

Hardware clear at end eighth bit of master receive data byte.

0 = Receive sequence not in progress

bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

1 = Initiate Stop condition on SDA and SCL pins Hardware clear at end of master Stop sequence.

0 = Stop condition not in progress

bit 1 RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

1 = Initiate Repeated Start condition on SDA and SCL pins Hardware clear at end of master Repeated Start sequence.

0 = Repeated Start condition not in progress

bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

1 = Initiate Start condition on SDA and SCL pins Hardware clear at end of master Start sequence.

0 = Start condition not in progress

Note 1: The IPMIEN bit should not be set when operating as a master.

#### Legend:

R = Readable C = Clearable bit U = Unimplemented bit, read as '0'

W = Writable HS = Set by Hardware S = Settable bit

HC = Cleared by Hardware '0' = Bit cleared at POR x = Bit is unknown at POR

'1' = Bit is set at POR

## Register 21-2: I2CSTAT: I<sup>2</sup>C™ Status Register

| Upper Byte:  |        |     |     |     |       |        |        |

|--------------|--------|-----|-----|-----|-------|--------|--------|

| R-0          | R-0    | U-0 | U-0 | U-0 | R/C-0 | R-0    | R-0    |

| HS, HC       | HS, HC |     |     |     | HS    | HS, HC | HS, HC |

| ACKSTAT      | TRSTAT | _   | _   | _   | BCL   | GCSTAT | ADD10  |

| bit 15 bit 8 |        |     |     |     |       |        |        |

| Lower Byte: |             |                 |               |               |               |               |               |

|-------------|-------------|-----------------|---------------|---------------|---------------|---------------|---------------|

| R/C-0<br>HS | R/W-0<br>HS | R-0<br>HS, HC   | R-0<br>HS, HC | R-0<br>HS, HC | R-0<br>HS, HC | R-0<br>HS, HC | R-0<br>HS, HC |

| IWCOL       | I2COV       | D/ <del>A</del> | Р             | S             | R/W           | RBF           | TBF           |

| bit 7 bit 0 |             |                 |               |               |               |               |               |

#### bit 15 ACKSTAT: Acknowledge Status bit

(When operating as I<sup>2</sup>C master. Applicable to master transmit operation.)

- 1 = NACK received from slave

- 0 = ACK received from slave

Hardware set or clear at end of slave Acknowledge.

#### bit 14 TRSTAT: Transmit Status bit

(When operating as I<sup>2</sup>C master. Applicable to master transmit operation.)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission.

Hardware clear at end of slave Acknowledge.

#### bit 13-11 Unimplemented: Read as '0'

#### bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

Hardware set at detection of bus collision.

#### bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address.

Hardware clear at Stop detection.

#### bit 8 ADD10: 10-Bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address.

Hardware clear at Stop detection.

### bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CTRN while busy (cleared by software).

#### bit 6 **I2COV:** Receive Overflow Flag bit

- 1 = A byte was received while the I2CRCV register is still holding the previous byte

- 0 = No overflow

Hardware set at attempt to transfer I2CRSR to I2CRCV (cleared by software).

## bit 5 $D/\overline{A}$ : Data/Address bit (when operating as $I^2C$ slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was a device address

Hardware clear at device address match; hardware set by reception of slave byte or is set after the transmission is complete and the TBF flag is cleared.

## dsPIC30F Family Reference Manual

## Register 21-2: I2CSTAT: I<sup>2</sup>C<sup>™</sup> Status Register (Continued)

bit 4 P: Stop bit

1 = Indicates that a Stop bit has been detected last

0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

bit 3 S: Start bit

1 = Indicates that a Start (or Repeated Start) bit has been detected last

0 = Start bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

bit 2 R/W: Read/Write bit Information (when operating as  $I^2C$  slave)

1 = Read - indicates data transfer is output from slave

0 = Write - indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

bit 1 RBF: Receive Buffer Full Status bit

1 = Receive complete, I2CRCV is full

0 = Receive not complete, I2CRCV is empty

Hardware set when I2CRCV written with received byte.

Hardware clear when software reads I2CRCV.

bit 0 TBF: Transmit Buffer Full Status bit

1 = Transmit in progress, I2CTRN is full

0 = Transmit complete, I2CTRN is empty

Hardware set when software writes I2CTRN.

Hardware clear at completion of data transmission.

Legend:

R = Readable W = Writable C = Clearable bit

HC = Cleared by Hardware HS = Set by Hardware U = Unimplemented bit, read as '0'

'1' = Bit is set at POR '0' = Bit cleared at POR x = Bit is unknown at POR

## 21.4 Enabling I<sup>2</sup>C Operation

The module is enabled by setting the I2CEN (I2CCON<15>) bit.

The I<sup>2</sup>C module fully implements all master and slave functions. When the module is enabled, the master and slave functions are active simultaneously and will respond according to the software or the bus events.

When initially enabled, the module will release SDA and SCL pins, putting the bus into the Idle state. The master functions will remain in the Idle state unless software sets a control bit to initiate a master event. The slave functions will begin to monitor the bus. If the slave logic detects a Start event and a valid address on the bus, the slave logic will begin a slave transaction.

## 21.4.1 Enabling I<sup>2</sup>C I/O

Two pins are used for bus operation. These are the SCL pin, which is the clock, and the SDA pin, which is the data. When the module is enabled, assuming no other module with higher priority has control, the module will assume control of the SDA and SCL pins. The module software need not be concerned with the state of the port I/O of the pins, the module overrides the port state and direction. At initialization, the pins are tri-state (released).

## 21.4.2 I<sup>2</sup>C Interrupts

The I<sup>2</sup>C module generates two interrupts. One interrupt is assigned to master events and the other interrupt is assigned to slave events. These interrupts will set a corresponding interrupt flag bit and will interrupt the software process if the corresponding interrupt enable bit is set and the corresponding interrupt priority is high enough.

The master interrupt is called MI2CIF and is activated on completion of a master message event.

The following events generate the MI2CIF interrupt:

- · Start condition

- · Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated Start

- · Detection of a bus collision event

The slave interrupt is called SI2CIF and is activated on detection of a message directed to the slave.

- · Detection of a valid device address (including general call)

- · Transmission of data byte

- · Reception of data byte

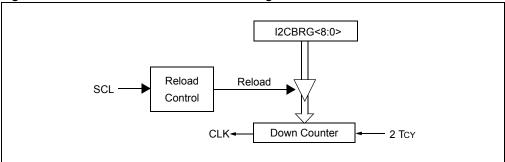

## 21.4.3 Setting Baud Rate when Operating as a Bus Master

When operating as an  $I^2C$  master, the module must generate the system SCL clock. Generally,  $I^2C$  system clocks are specified to be either 100 kHz, 400 kHz or 1 MHz. The system clock rate is specified as the minimum SCL low time plus the minimum SCL high time. In most cases, that is defined by 2 TBRG intervals.

The reload value for the baud rate generator is the I2CBRG register, as shown in Figure 21-6. When the baud rate generator is loaded with this value, the generator counts down to '0' and stops until another reload has taken place. The generator count is decremented twice per instruction cycle (TcY). The baud rate generator is reloaded automatically on baud rate restart. For example, if clock synchronization is taking place, the baud rate generator will be reloaded when the SCL pin is sampled high.

Note: I2CBRG value of 0x0 is not supported.

To compute the baud rate generator reload value, use the following equation.

Equation 21-1: BRG Reload Value Calculation

$$I2CBRG = \left[ \left( \frac{1}{F_{SCL}} - PGD \right) \cdot F_{CY} \right] - 1$$

Table 21-1: I<sup>2</sup>C™ Clock Rates

| Required<br>System<br>FSCL | FcY    | PGD <sup>(1)</sup> | I2CBRG<br>Decimal | I2CBRG<br>HEX |

|----------------------------|--------|--------------------|-------------------|---------------|

| 100 kHz                    | 30 MHz | 250 ns             | 272               | 0x110         |

| 100 kHz                    | 20 MHz | 250 ns             | 181               | 0x0B5         |

| 100 kHz                    | 1 MHz  | 250 ns             | 8                 | 0x008         |

| 400 kHz                    | 10 MHz | 250 ns             | 15                | 0x00F         |

| 400 kHz                    | 5 MHz  | 250 ns             | 7                 | 0x007         |

| 400 kHz                    | 1 MHz  | 250 ns             | 1                 | 0x001         |

| 1 MHz <sup>(2)</sup>       | 20 MHz | 250 ns             | 1                 | 0x001         |

**Note 1:** The typical value of the Pulse Gobbler Delay (PGD) is 250 ns. Refer to the device specific data sheet for more information.

2: Fcy = 20 MHz is the minimum input clock frequency to have Fscl = 1 MHz.

Figure 21-6: Baud Rate Generator Block Diagram

## 21.5 Communicating as a Master in a Single-Master Environment

Typical operation of the  $I^2C$  module in a system is using the  $I^2C$  to communicate with an  $I^2C$  peripheral, such as an  $I^2C$  serial memory. In an  $I^2C$  system, the master controls the sequence of all data communication on the bus. In this example, the dsPIC30F and its  $I^2C$  module have the role of the single master in the system. As the single master, it is responsible for generating the SCL clock and controlling the message protocol.

**Note:** The IPMIEN (I2CxCON<11>) bit should not be set when operating as a master.

In the I<sup>2</sup>C module, the module controls individual portions of the I<sup>2</sup>C message protocol, however, sequencing of the components of the protocol to construct a complete message is a software task

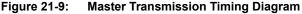

For example, a typical operation in a single master environment may be to read a byte from an I<sup>2</sup>C serial EEPROM. This example message is depicted in Figure 21-7.

To accomplish this message, the software will sequence through the following steps:

- 1. Assert a Start condition on SDA and SCL.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the serial memory address high byte to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Wait for and verify an Acknowledge from the slave.

- 8. Assert a Repeated Start condition on SDA and SCL.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDA and SCL.

Figure 21-7: A Typical I<sup>2</sup>C™ Message: Read of Serial EEPROM (Random Address Mode)

The  $I^2C$  module supports Master mode communication with the inclusion of Start and Stop generators, data byte transmission, data byte reception, Acknowledge generator and a baud rate generator.

Generally, the software will write to a control register to start a particular step, then wait for an interrupt or poll status to wait for completion.

Subsequent sub-sections detail each of these operations.

**Note:** The I<sup>2</sup>C module does not allow queueing of events. For instance, the software is not allowed to initiate a Start condition and immediately write the I2CxTRN register to initiate transmission before the Start condition is complete. In this case, the I2CxTRN register will not be written to and the IWCOL status bit will be set, indicating that this write to the I2CxTRN register did not occur.

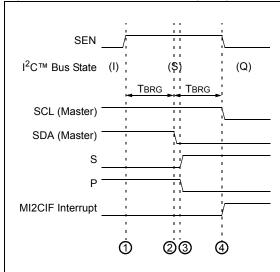

## 21.5.1 Generating Start Bus Event

To initiate a Start event, the software sets the Start enable bit, SEN (I2CCON<0>). Prior to setting the Start bit, the software can check the P (I2CSTAT<4>) status bit to ensure that the bus is in an Idle state.

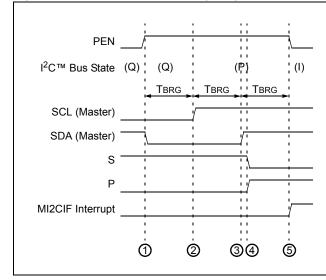

Figure 21-8 shows the timing of the Start condition.

- Slave logic detects the Start condition, sets the S bit (I2CSTAT<3>) and clears the P bit (I2CSTAT<4>).

- SEN bit is automatically cleared at completion of the Start condition.

- · MI2CIF interrupt generated at completion of the Start condition.

- · After Start condition, the SDA line and SCL line are left low (Q state).

#### 21.5.1.1 IWCOL Status Flag

If the software writes the I2CTRN when a Start sequence is in progress, then IWCOL is set and the contents of the transmit buffer are ignored.

**Note:** Since queueing of events is not allowed, writing to the lower 5 bits of I2CCON is disabled until the Start condition is complete.

Figure 21-8: Master Start Timing Diagram

- ① Writing SEN = 1 initiates a master Start event. Baud Rate Generator starts.

- Baud Rate Generator times out. Master module drives SDA low.

Baud Rate Generator restarts.

- 3 Slave module detects Start, sets S = 1, P = 0.

- 4 Baud Rate Generator times out. Master module drives SCL low, generates interrupt and clears SEN.

## 21.5.2 Sending Data to a Slave Device

Transmission of a data byte, a 7-bit device address byte or the second byte of a 10-bit address, is accomplished by simply writing the appropriate value to the I2CTRN register. Loading this register will start the following process:

- The software loads the I2CTRN with the data byte to transmit.

- Writing I2CTRN sets the buffer full flag bit, TBF (I2CSTAT<0>).

- The data byte is shifted out the SDA pin until all 8 bits are transmitted. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL.

- On the ninth SCL clock, the module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit (I2CCON<15>).

- The module generates the MI2CIF interrupt at the end of the ninth SCL clock cycle.

Note that the module does not generate or validate the data bytes. The contents and usage of the byte is dependant on the state of the message protocol maintained by the software.

### 21.5.2.1 Sending a 7-bit Address to the Slave

Sending a 7-bit device address involves sending  $\underline{1}$  byte to the slave. A 7-bit address byte must contain the 7 bits of  $I^2C$  device address and a R/W bit that defines if the message will be a write to the slave (master transmission and slave receiver) or a read from the slave (slave transmission and master receiver).

**Note:** In 7-bit addressing mode, each node using the I<sup>2</sup>C protocol should be configured with a unique address that is stored in the I2CxADD register.

## 21.5.2.2 Sending a 10-bit Address to the Slave

Sending a 10-bit device address involves sending 2 bytes to the slave. The first byte contains 5 bits of  $I^2C$  device address reserved for 10-bit Addressing modes and 2 bits of the 10-bit address. Because the next byte, which contains the remaining 8 bits of the 10-bit address must be received by the slave, the R/W bit in the first byte must be '0', indicating master transmission and slave reception. If the message data is also directed toward the slave, the master can continue sending the data. However, if the master expects a reply from the slave, a Repeated Start sequence with the R/W bit at '1' will change the R/W state of the message to a read of the slave.

**lote:** In 10-bit addressing mode, each node using the I<sup>2</sup>C protocol should be configured with a unique address that is stored in the I2CxADD register.

## 21.5.2.3 Receiving Acknowledge from the Slave

On the falling edge of the eighth SCL clock, the TBF bit is cleared and the master will de-assert the SDA pin allowing the slave to respond with an Acknowledge. The master will then generate a ninth SCL clock.

This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurs, or if data was received properly. A slave sends an Acknowledge when it has recognized its device address (including a general call), or when the slave has properly received its data.

The status of  $\overline{ACK}$  is written into the Acknowledge status bit, ACKSTAT (I2CSTAT<15>), on the falling edge of the ninth SCL clock. After the ninth SCL clock, the module generates the MI2CIF interrupt and enters an Idle state until the next data byte is loaded into I2CTRN.

#### 21.5.2.4 ACKSTAT Status Flag

The ACKSTAT bit (I2CCON<15>) is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ), and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ).

### 21.5.2.5 TBF Status Flag

When transmitting, the TBF bit (I2CSTAT<0>) is set when the CPU writes to I2CTRN and is cleared when all 8 bits are shifted out.

### 21.5.2.6 IWCOL Status Flag

If the software writes the I2CTRN when a transmit is already in progress (i.e., the module is still shifting out a data byte), then IWCOL is set and the contents of the buffer are ignored. IWCOL must be cleared in software.

**Note:** Since queueing of events is not allowed, writing to the lower 5 bits of I2CCON is disabled until the transmit condition is complete.

- (1) Writing the I2CTRN register will start a master transmission event. TBF bit is set.

- (2) Baud Rate Generator starts. The MSB of the I2CTRN drives SDA. SCL remains low. TRSTAT bit is set.

- (3) Baud Rate Generator times out. SCL released. Baud Rate Generator restarts.

- (4) Baud Rate Generator times out. SCL driven low. After SCL detected low, next bit of I2CTRN drives SDA.

- (5) While SCL is low, the slave can also pull SCL low to initiate a WAIT (clock stretch).

- **(6)** Master has already released SCL, and slave can release to end WAIT. Baud Rate Generator restarts.

- (7) At falling edge of eighth SCL clock, master releases SDA. TBF bit is cleared. Slave drives ACK/NACK.

- (8) At falling edge of ninth SCL clock, master generates interrupt. SCL remains low until next event. Slave releases SDA. TRSTAT bit is clear.

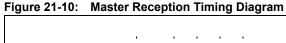

## 21.5.3 Receiving Data from a Slave Device

Setting the receive enable bit, RCEN (I2CCON<3>), enables the master to receive data from a slave device.

**Note:** The lower 5 bits of I2CCON must be '0' before attempting to set the RCEN bit. This ensures the master logic is inactive.

The master logic begins to generate clocks and before each falling edge of the SCL, SDA line is sampled and data is shifted into the I2CRSR.

After the falling edge of the eighth SCL clock:

- · The RCEN bit is automatically cleared.

- · The contents of the I2CRSR transfer into the I2CRCV.

- · The RBF flag bit is set.

- The module generates the MI2CIF interrupt.

When the CPU reads the buffer, the RBF flag bit is automatically cleared. The software can process the data and then do an Acknowledge sequence.

#### 21.5.3.1 RBF Status Flag

When receiving data, the RBF bit is set when a device address or data byte is loaded into I2CRCV from I2CRSR. It is cleared when software reads the I2CRCV register.

#### 21.5.3.2 I2COV Status Flag

If another byte is received in the I2CRSR while the RBF bit remains set and the previous byte remains in the I2CRCV register, the I2COV bit is set and the data in the I2CRSR is lost.

Leaving I2COV set does not inhibit further reception. If RBF is cleared by reading the I2CRCV, and the I2CRSR receives another byte, that byte will be transferred to the I2CRCV.

### 21.5.3.3 IWCOL Status Flag

If the software writes the I2CTRN when a receive is already in progress (i.e., I2CRSR is still shifting in a data byte), then the IWCOL bit is set and the contents of the buffer are ignored.

**Note:** Since queueing of events is not allowed, writing to the lower 5 bits of I2CCON is disabled until the data reception condition is complete.

- ① Typically, the slave can pull SCL low (clock stretch) to request a wait to prepare data response. The slave will drive MSB of data response on SDA when ready.

- ② Writing the RCEN bit will start a master reception event. The Baud Rate Generator starts. SCL remains low.

- 3 Baud Rate Generator times out. Master attempts to release SCL.

- 4 When slave releases SCL, Baud Rate Generator restarts.

- (5) Baud Rate Generator times out. MSB of response shifted to I2CRSR. SCL driven low for next baud interval.

- 6 At falling edge of eighth SCL clock, I2CRSR transferred to I2CRCV. Module clears RCEN bit. RBF bit is set. Master generates interrupt.

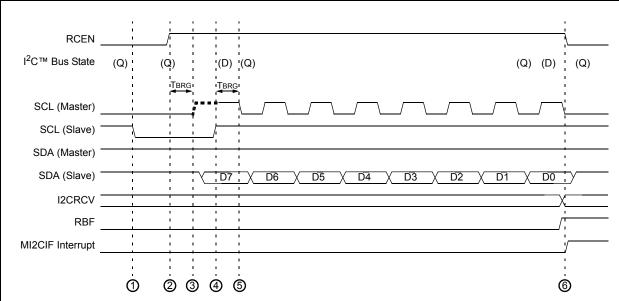

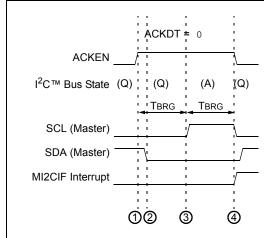

## 21.5.4 Acknowledge Generation

Setting the Acknowledge sequence enable bit, ACKEN (I2CCON<4>), enables generation of a master Acknowledge sequence.

**Note:** The lower 5 bits of I2CCON must be '0' (master logic inactive) before attempting to set the ACKEN bit.

Figure 21-11 shows an  $\overline{ACK}$  sequence and Figure 21-12 shows a NACK sequence. The Acknowledge data bit, ACKDT (I2CCON<5>), specifies  $\overline{ACK}$  or NACK.

After two baud periods:

- · The ACKEN bit is automatically cleared

- · The module generates the MI2CIF interrupt

#### 21.5.4.1 IWCOL Status Flag

If the software writes the I2CTRN when an Acknowledge sequence is in progress, then IWCOL is set and the contents of the buffer are ignored.

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of I2CCON is disabled until the Acknowledge condition is complete.

Figure 21-11: Master Acknowledge (ACK) Timing Diagram

- ① Writing ACKDT = 0 specifies sending an ACK.

Writing ACKEN = 1 initiates a master Acknowledge event.

Baud Rate Generator starts. SCL remains low.

- 2 When SCL detected low, module drives SDA low.

- Baud Rate Generator times out. Module releases SCL. Baud Rate Generator restarts.

- Baud Rate Generator times out.

Module drives SCL low then releases SDA.

Module clears ACKEN. Master generates interrupt.

Figure 21-12: Master Not-Acknowledge (NACK) Timing Diagram

- Writing ACKDT = 1 specifies sending an NACK.

Writing ACKEN = 1 initiates a master Acknowledge event.

Baud Rate Generator starts.

- (2) When SCL detected low, module releases SDA.

- Baud Rate Generator times out. Module releases SCL. Baud Rate Generator restarts.

- Baud Rate Generator times out.

Module drives SCL low then releases SDA.

Module clears ACKEN. Master generates interrupt.

## 21.5.5 Generating Stop Bus Event

Setting the Stop sequence enable bit, PEN (I2CCON<2>), enables generation of a master Stop sequence.

**Note:** The lower 5 bits of I2CCON must be '0' (master logic inactive) before attempting to set the PEN bit.

When the PEN bit is set, the master generates the Stop sequence as shown in Figure 21-13.

- The slave detects the Stop condition, sets the P bit (I2CSTAT<4>) and clears the S bit (I2CSTAT<3>)

- · The PEN bit is automatically cleared

- · The module generates the MI2CIF interrupt

#### 21.5.5.1 IWCOL Status Flag

If the software writes the I2CTRN when a Stop sequence is in progress, then the IWCOL bit is set and the contents of the buffer are ignored.

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of I2CCON is disabled until the Stop condition is complete.

Figure 21-13: Master Stop Timing Diagram

- ① Writing PEN = 1 initiates a master Stop event.

Baud Rate Generator starts. Module drives SDA low.

- ② Baud Rate Generator times out. Module releases SCL. Baud Rate Generator restarts.

- 3 Baud Rate Generator times out. Module releases SDA. Baud Rate Generator restarts.

- $\bigcirc$  Slave logic detects Stop. Module sets P = 1, S = 0.

- ⑤ The Baud Rate Generator times out. Module clears PEN. Master generates interrupt.

## 21.5.6 Generating Repeated Start Bus Event

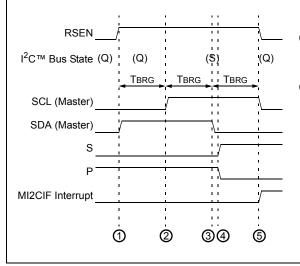

Setting the Repeated Start sequence enable bit, RSEN (I2CCON<1>), enables generation of a master Repeated Start sequence (see Figure 21-14).

**Note:** The lower 5 bits of I2CCON must be '0' (master logic inactive) before attempting to set the RSEN bit.

To generate a Repeated Start condition, software sets the RSEN bit (I2CCON<1>). The module asserts the SCL pin low. When the module samples the SCL pin low, the module releases the SDA pin for one baud rate generator count (TBRG). When the baud rate generator times out, if the module samples SDA high, the module de-asserts the SCL pin. When the module samples SCL pin high, the baud rate generator reloads and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin low for one TBRG while SCL is high.

The following is the Repeated Start sequence:

- The slave detects the Start condition, sets the S bit (I2CSTAT<3>) and clears the P bit (I2CSTAT<4>)

- · The RSEN bit is automatically cleared

- · The module generates the MI2CIF interrupt

#### 21.5.6.1 IWCOL Status Flag

If the software writes the I2CTRN when a Repeated Start sequence is in progress, then IWCOL is set and the contents of the buffer are ignored.

**Note:** Since queueing of events is not allowed, writing of the lower 5 bits of I2CCON is disabled until the Repeated Start condition is complete.

Figure 21-14: Master Repeated Start Timing Diagram

- ① Writing RSEN = 1 initiates a master Repeated Start event. Baud Rate Generator starts. Module drives SCL low and releases SDA.

- Baud Rate Generator times out. Module releases SCL.

Baud Rate Generator restarts.

- Baud Rate Generator times out. Module drives SDA low. Baud Rate Generator restarts.

- (4) Slave logic detects Start. Module sets S = 1, P = 0.

- (5) The Baud Rate Generator times out. Module drives SCL low. Module clears RSEN. Master generates interrupt.

## 21.5.7 Building Complete Master Messages

As described at the beginning of **21.5** "Communicating as a Master in a Single-Master Environment", the software is responsible for constructing messages with the correct message protocol. The module controls individual portions of the I<sup>2</sup>C message protocol, however, sequencing of the components of the protocol to construct a complete message is a software task.

The software can use polling or interrupt methods while using the module. The examples shown use interrupts.

The software can use the SEN, RSEN, PEN, RCEN and ACKEN bits (Least Significant 5 bits of the I2CCON register) and the TRSTAT bit as a "state" flag when progressing through a message. For example, Table 21-2 shows some example state numbers associated with bus states.

Table 21-2: Master Message Protocol States

| Example<br>State Number | I2CCON<4:0> | TRSTAT<br>(I2CSTAT<14>) | State                        |

|-------------------------|-------------|-------------------------|------------------------------|

| 0                       | 00000       | 0                       | Bus Idle or WAIT             |

| 1                       | 00001       | N/A                     | Sending Start Event          |

| 2                       | 00000       | 1                       | Master Transmitting          |

| 3                       | 00010       | N/A                     | Sending Repeated Start Event |

| 4                       | 00100       | N/A                     | Sending Stop Event           |

| 5                       | 01000       | N/A                     | Master Reception             |

| 6                       | 10000       | N/A                     | Master Acknowledgement       |

Note: Example state numbers for reference only. User software may assign as desired.

The software will begin a message by issuing a Start command. The software will record the state number corresponding to Start.

As each event completes and generates an interrupt, the interrupt handler may check the state number. So, for a Start state, the interrupt handler will confirm execution of the Start sequence and then start a master transmission event to send the I<sup>2</sup>C device address, changing the state number to correspond to master transmission.

On the next interrupt, the interrupt handler will again check the state, determining that a master transmission just completed. The interrupt handler will confirm successful transmission of the data, then move on to the next event, depending on the contents of the message.

In this manner, on each interrupt, the interrupt handler will progress through the message protocol until the complete message is sent.

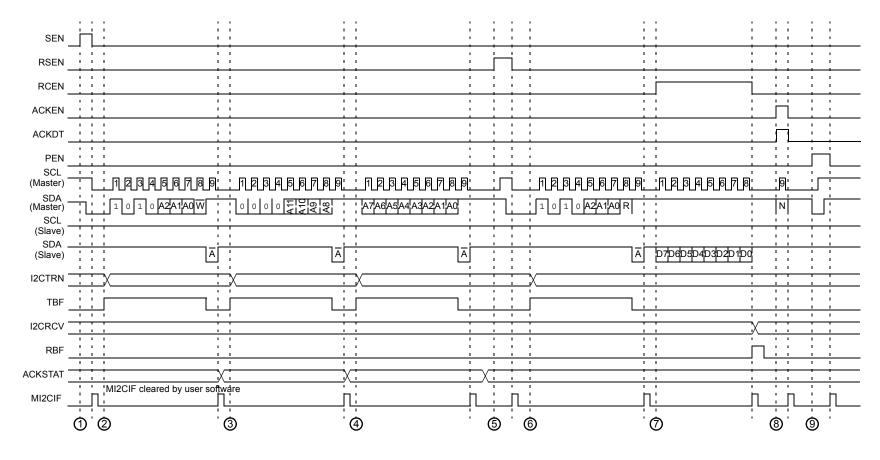

Figure 21-15 provides a more detailed examination of the same message sequence of Figure 21-7.

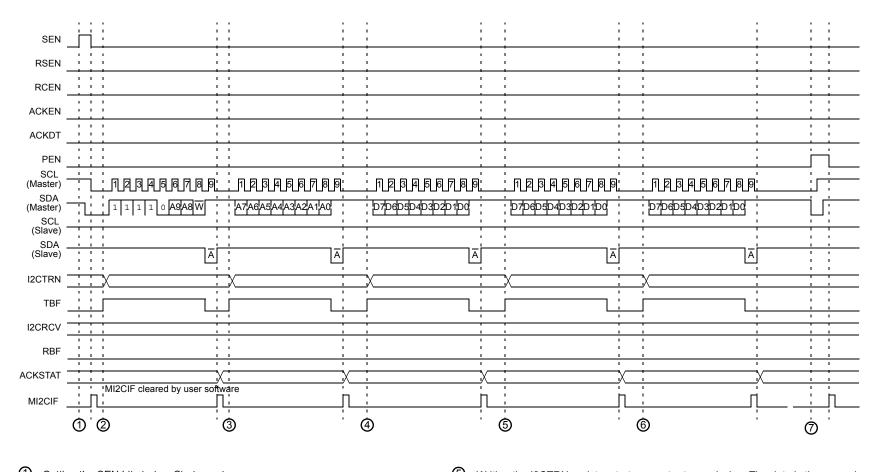

Figure 21-16 shows some simple examples of messages using 7-bit addressing format.

Figure 21-17 shows an example of a 10-bit address format message sending data to a slave.

Figure 21-18 shows an example of a 10-bit address format message receiving data from a slave.

DS70068F-page 21-25

- 1 Setting the SEN bit starts a Start event.

- $\ \, 2$  Writing the I2CTRN register starts a master transmission. The data is the serial EE device address byte, with R/W clear indicating a write.

- 3 Writing the I2CTRN register starts a master transmission. The data is the first byte of the EE data address.

- Writing the I2CTRN register starts a master transmission. The data is the second byte of the EE data address.

- (5) Setting the RSEN bit starts a Repeated Start event.

- 6 Writing the I2CTRN register starts a master transmission. The data is a resend of the serial EE device address byte, but with R/W bit set indicating a read.

- 7 Setting the RCEN bit starts a master reception. On interrupt, the software reads the I2CRCV register, which clears the RBF flag.

- 8 Setting the ACKEN bit starts an Acknowledge event. ACKDT = 1 to send NACK.

- 9 Setting the PEN bit starts a master Stop event.

DS70068F-page 21-26

Figure 21-16: Master Message (7-Bit Address: Transmission and Reception) RSEN RCEN ACKEN ACKDT PEN SCL \_1\_2\_3\_4\_5\_6\_7\_8;9 (Master) SDA A6A5A4A3A2A1A0 R Ν (Master) SCL (Slave) SDA D7D6D5D4D3D2D1D0 (Slave) **I2CTRN I2CRCV RBF ACKSTAT** MI2CIF cleared by user software MI2CIF 3 0 2 4 **⑤** 6 7 8 9 6 - Writing the I2CTRN register starts a master transmission. The data is the address byte with R/W bit set. 1 - Setting the SEN bit starts a Start event. ② - Writing the I2CTRN register starts a master transmission. The data is the address byte with R/W bit clear. 7 - Setting the RCEN bit starts a master reception. ③ - Writing the I2CTRN register starts a master transmission. The data is the (8) - Setting the ACKEN bit starts an Acknowledge event. ACKDT = 1 to send NACK. message byte. (9) - Setting the PEN bit starts a master Stop event. 4 - Setting the PEN bit starts a master Stop event. ⑤ - Setting the SEN bit starts a Start event.

① - Setting the SEN bit starts a Start event.

Figure 21-17: Master Message (10-Bit Transmission)

- $\ensuremath{ \bigcirc}$  Writing the I2CTRN register starts a master transmission. The data is the first byte of the address.

- ③ Writing the I2CTRN register starts a master transmission. The data is the second byte of the address.

- Writing the I2CTRN register starts a master transmission. The data is the first byte of the message data.

- ⑤ Writing the I2CTRN register starts a master transmission. The data is the second byte of the message data.

- ⑥ Writing the I2CTRN register starts a master transmission. The data is the third byte of the message data.

- 7 Setting the PEN bit starts a master Stop event.

DS70068F-page 21-28

Figure 21-18: Master Message (10-Bit Reception) SEN **RSEN RCEN ACKEN ACKDT** PEN SCL 1 2 3 4 5 6 7 8 (Master) (Master) SCL (Slave) SDA Ā (Slave) **TBF I2CRCV RBF ACKSTAT** MI2CIF cleared in user software MI2CIF 3 9 0 2 4 6 **⑦** 8 (10)**⑥** - Setting the RCEN bit starts a master reception. On interrupt, the software reads the I2CRCV register, which clears the RBF flag. 1 - Setting the SEN bit starts a Start event. ② - Writing the I2CTRN register starts a master transmission. The data is the first byte of the address with the R/W bit cleared.  $\bigcirc$  - Setting the ACKEN bit starts an Acknowledge event. ACKDT = 0 to send  $\overline{ACK}$ . 3 - Writing the I2CTRN register starts a master transmission. The data is the second 8 - Setting the RCEN bit starts a master reception. byte of the address. 9 - Setting the ACKEN bit starts an Acknowledge event. ACKDT = 1 to send NACK. Setting the RSEN bit starts a master REStart event. ⑤ - Writing the I2CTRN register starts a master transmission. The data is a resend of the first byte with the R/W bit set. 10 - Setting the PEN bit starts a master Stop event.

## 21.6 Communicating as a Master in a Multi-Master Environment

The I<sup>2</sup>C protocol allows for more than one master to be attached to a system bus. Remembering that a master can initiate message transactions and generate clocks for the bus, the protocol has methods to account for situations where more than one master is attempting to control the bus. Clock synchronization ensures that multiple nodes can synchronize their SCL clocks to result in one common clock on the SCL line. Bus arbitration ensures that if more than one node attempts a message transaction, one and only one node will be successful in completing the message. The other nodes will lose bus arbitration and be left with a bus collision.

**Note:** The IPMIEN (I2CxCON<11>) bit should not be set when operating as a master.

### 21.6.1 Multi-Master Operation

The master module has no special settings to enable multi-master operation. The module performs clock synchronization and bus arbitration at all times. If the module is used in a single master environment, clock synchronization will only occur between the master and slaves and bus arbitration will not occur.

## 21.6.2 Master Clock Synchronization

In a multi-master system, different masters may have different baud rates. Clock synchronization will ensure that when these masters are attempting to arbitrate the bus, their clocks will be coordinated.

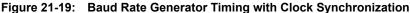

Clock synchronization occurs when the master de-asserts the SCL pin (SCL intended to float high). When the SCL pin is released, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of I2CBRG<8:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device, as shown in Figure 21-19.

- 1) The baud counter decrements twice per Tcy. On rollover, the master SCL will transition.

- 2 The slave has pulled SCL low to initiate a wait.

- 3 At what would be the master baud counter rollover, detecting SCL low holds counter.

- (4) Logic samples SCL once per Tcy. Logic detects SCL high.

- (5) The baud counter rollover occurs on next cycle.

- 6 On next rollover, the master SCL will transition.

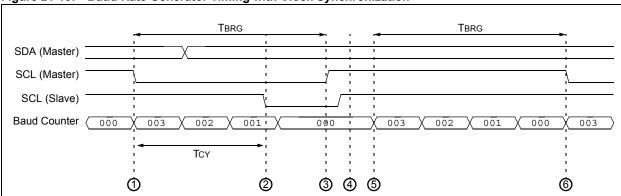

#### 21.6.3 Bus Arbitration and Bus Collision

Bus arbitration supports multi-master system operation.

The wired-and nature of the SDA line permits arbitration. Arbitration takes place when the first master outputs a '1' on SDA by letting SDA float high and, simultaneously, the second master outputs a '0' on SDA by pulling SDA low. The SDA signal will go low. In this case, the second master has won bus arbitration. The first master has lost bus arbitration and thus has a bus collision.

For the first master, the expected data on SDA is a '1' yet the data sampled on SDA is a '0'. This is the definition of a bus collision.

The first master will set the bus collision bit, BCL (I2CSTAT<10>), and generate a master interrupt. The master module will reset the I<sup>2</sup>C port to its Idle state.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by the master module, with the result placed in the BCL bit.

The states where arbitration can be lost are:

- · A Start condition

- · A Repeated Start condition

- · Address, Data or Acknowledge bit

- · A Stop condition

### 21.6.4 Detecting Bus Collisions and Resending Messages

When a bus collision occurs, the I<sup>2</sup>C module sets the BCL bit and generates a master interrupt. If bus collision occurs during a byte transmission, the transmission is halted, the TBF flag is cleared and the SDA and SCL pins are de-asserted. If bus collision occurs during a Start, Repeated Start, Stop or Acknowledge condition, the condition is aborted, the respective control bits in the I2CCON register are cleared and the SDA and SCL lines are de-asserted.

The software is expecting an interrupt at the completion of the master event. The software can check the BCL bit to determine if the master event completed successfully or if a collision occurred. If a collision occurs, the software must abort sending the rest of the pending message and prepare to resend the entire message sequence beginning with Start condition, after the bus returns to an Idle state. The software can monitor the S and P bits to wait for an Idle bus. When the software services the master Interrupt Service Routine (ISR) and the I<sup>2</sup>C bus is free, the software can resume communication by asserting a Start condition.

## 21.6.5 Bus Collision During a Start Condition

Before issuing a Start command, the software should verify an Idle state of the bus using the S and P status bits. Two masters may attempt to initiate a message at a similar point in time. Typically, the masters will synchronize clocks and continue arbitration into the message until one loses arbitration. However, certain conditions can cause a bus collision to occur during a Start. In this case, the master that loses arbitration during the Start bit generates a bus collision interrupt.

## 21.6.6 Bus Collision During a Repeated Start Condition

Should two masters not collide throughout an address byte, a bus collision may occur when one master attempts to assert a Repeated Start while another transmits data. In this case, the master generating the Repeated Start will lose arbitration and generate a bus collision interrupt.

### 21.6.7 Bus Collision During Message Bit Transmission

The most typical case of data collision occurs while the master is attempting to transmit the device address byte, a data byte or an Acknowledge bit.

If the software is properly checking the bus state, it is unlikely that a bus collision will occur on a Start condition. However, because another master can, at a very similar time, check the bus and initiate its own Start condition, it is likely that SDA arbitration will occur and synchronize the starts of two masters. In this condition, both masters will begin and continue to transmit their messages until one master loses arbitration on a message bit. Remember that SCL clock synchronization will keep the two masters synchronized until one loses arbitration.

Figure 21-20 shows an example of message bit arbitration.

Figure 21-20: Bus Collision During Message Bit Transmission

### 21.6.8 Bus Collision During a Stop Condition

If the master software loses track of the state of the I<sup>2</sup>C bus, there are conditions which cause a bus collision during a Stop condition. In this case, the master generating the Stop condition will lose arbitration and generate a bus collision interrupt.

## 21.7 Communicating as a Slave

In some systems, particularly where multiple processors communicate with each other, the dsPIC30F device may communicate as a slave (see Figure 21-21). When the module is enabled, the slave module is active. The slave may not initiate a message, it can only respond to a message sequence initiated by a master. The master requests a response from a particular slave as defined by the device address byte in the I<sup>2</sup>C protocol. The slave module replies to the master at the appropriate times as defined by the protocol.

As with the master module, sequencing the components of the protocol for the reply is a software task. However, the slave module detects when the device address matches the address specified by the software for that slave.

Figure 21-21: A Typical Slave I<sup>2</sup>C™ Message: Multiprocessor Command/Status

After a Start condition, the slave module will receive and check the device address. The slave may specify either a 7-bit address or a 10-bit address. When a device address is matched, the module will generate an interrupt to notify the software that its device is selected. Based on the R/W bit sent by the master, the slave will either receive or transmit data. If the slave is to receive data, the slave module automatically generates the Acknowledge (ACK), loads the I2CRCV register with the received value currently in the I2CRSR register and notifies the software through an interrupt. If the slave is to transmit data, the software must load the I2CTRN register.

#### 21.7.1 Sampling Receive Data

All incoming bits are sampled with the rising edge of the clock (SCL) line.

## 21.7.2 Detecting Start and Stop Conditions

The slave module will detect Start and Stop conditions on the bus and indicate that status on the S bit (I2CSTAT<3>) and P bit (I2CSTAT<4>). The Start (S) and Stop (P) bits are cleared when a Reset occurs or when the I<sup>2</sup>C module is disabled. After detection of a Start or Repeated Start event, the S bit is set and the P bit is cleared. After detection of a Stop event, the P bit is set and the S bit is clear.

### 21.7.3 Detecting the Address

Once the module has been enabled, the slave module waits for a Start condition to occur. After a Start, depending on the A10M bit (I2CCON<10>), the slave will attempt to detect a 7-bit or 10-bit address. The slave module will compare 1 received byte for a 7-bit address or 2 received bytes for a 10-bit address. A 7-bit address also contains a R/W bit that specifies the direction of data transfer after the address. If R/W = 0, a write is specified and the slave will receive data from the master. If R/W = 1, a read is specified and the slave will send data to the master. The 10-bit address contains a R/W bit, however by definition, it is always R/W = 0 because the slave must receive the second byte of the 10-bit address. In either case, the received address byte is transferred to the I2CRCV register and a dummy read of this register must be performed to clear the RBF Status bit.

Table 21-3: Slave Addresses Supported by the I<sup>2</sup>C™ Module

| Address   | Description                           |

|-----------|---------------------------------------|

| 0x00      | General call address or start byte    |

| 0x01-0x07 | Reserved                              |

| 0x08-0x77 | Valid 7-bit addresses                 |

| 0x78-0x7b | Valid 10-bit addresses (lower 7 bits) |

| 0x7c-0x7f | Reserved                              |

#### 21.7.3.1 7-bit Address and Slave Write

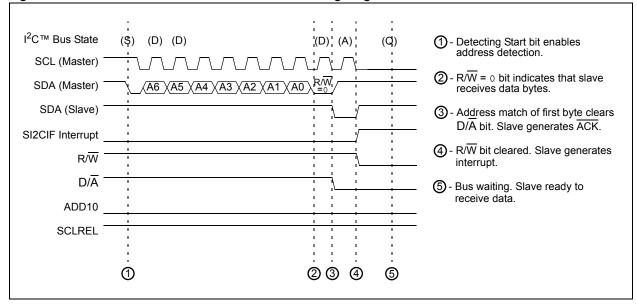

Following the Start condition, the module shifts 8 bits into the I2CRSR register (see Figure 21-22). The value of register I2CRSR<7:1> is compared to the value of the I2CADD<6:0> register. The device address is compared on the falling edge of the eighth clock (SCL). If the addresses match, the following events occur:

- 1. An  $\overline{ACK}$  is generated.

- 2. The  $D/\overline{A}$  and  $R/\overline{W}$  bits are cleared.

- 3. The I<sup>2</sup>C module generates the SI2CIF interrupt on the falling edge of the ninth SCL clock.

- 4. The I<sup>2</sup>C module will wait for the master to send data.

Figure 21-22: Slave Write 7-Bit Address Detection Timing Diagram

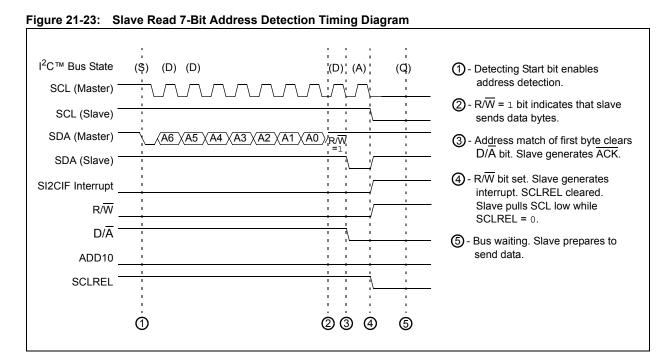

#### 21.7.3.2 7-Bit Address and Slave Read

When a slave read is specified by having  $R/\overline{W} = 1$  in a 7-bit address byte, the process of detecting the device address is similar to that of a slave write (see Figure 21-23). If the addresses match, the following events occur:

- 1. An  $\overline{ACK}$  is generated.

- 2. The  $D/\overline{A}$  bit is cleared and the  $R/\overline{W}$  bit is set.

- 3. The module generates the SI2CIF interrupt on the falling edge of the ninth SCL clock.

Since the slave module is expected to reply with data at this point, it is necessary to suspend the operation of the  $I^2C$  bus to allow the software to prepare a response. This is done automatically when the module clears the SCLREL bit. With SCLREL low, the slave module will pull down the SCL clock line, causing a wait on the  $I^2C$  bus. The slave module and the  $I^2C$  bus will remain in this state until the software writes the I2CTRN register with the response data and sets the SCLREL bit.

**Note:** SCLREL will automatically clear after detection of a slave read address regardless of the state of the STREN bit.

DS70068F-page 21-34

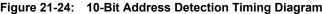

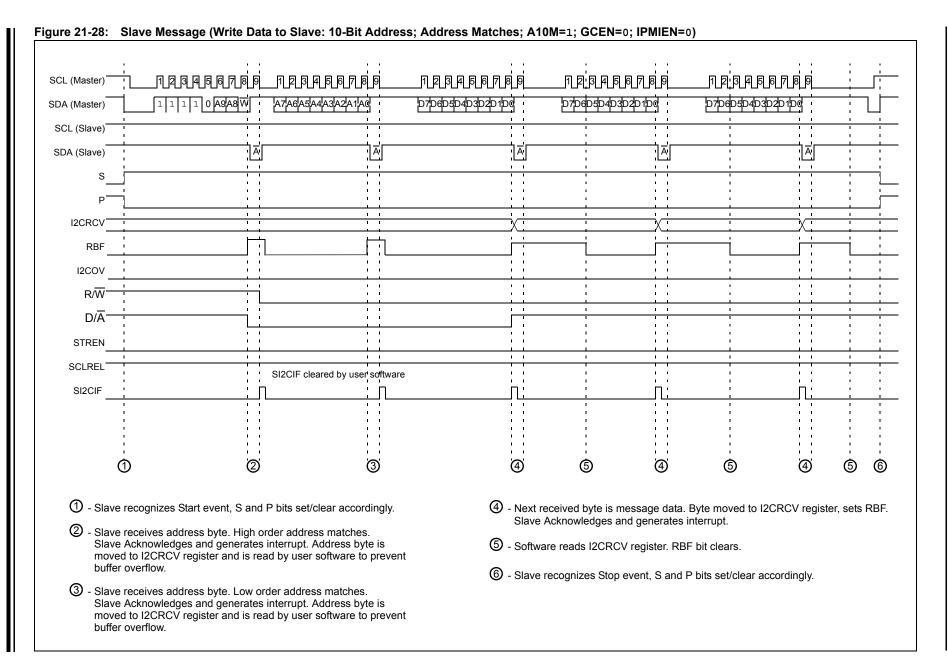

#### 21.7.3.3 10-Bit Address

In 10-bit Address mode, the slave must receive two device address bytes (see Figure 21-24). The five Most Significant bits (MSbs) of the first address byte specify a 10-bit address. The R/W bit of the address must specify a write, causing the slave device to receive the second address byte. For a 10-bit address the first byte would equal '11110 A9 A8 0', where A9 and A8 are the two MSbs of the address.

Following the Start condition, the module shifts 8 bits into the I2CRSR register. The value of register I2CRSR<2:1> is compared to the value of the I2CADD<9:8> register. The value of I2CRSR<7:3> is compared to '11110'. The device address is compared on the falling edge of the eighth clock (SCL). If the addresses match, the following events occur:

- 1. An  $\overline{ACK}$  is generated.

- 2. The  $D/\overline{A}$  and  $R/\overline{W}$  bits are cleared.

- 3. The module generates the SI2CIF interrupt on the falling edge of the ninth SCL clock.

The module does generate an interrupt after the reception of the first byte of a 10-bit address, however this interrupt is of little use.

The module will continue to receive the second byte into I2CRSR. This time, I2CRSR<7:0> is compared to I2CADD<7:0>. If the addresses match, the following events occur:

- 1. An ACK is generated.

- 2. The ADD10 bit is set.

- The module generates the SI2CIF interrupt on the falling edge of the ninth SCL clock.

- 4. The module will wait for the master to send data or initiate a Repeated Start condition.

**Note:** Following a Repeated Start condition in 10-bit mode, the slave module only matches the first 7-bit address, '11110 A9 A8 0'.

- 1 Detecting Start bit enables address detection.

- (2) Address match of first byte clears  $D/\overline{A}$  bit and causes slave logic to generate  $\overline{ACK}$ .

- 3 Reception of first byte clears R/W bit. Slave logic generates interrupt.

- 4 Address match of first and second byte sets ADD10 and causes slave logic to generate ACK.

- (5) Reception of second byte completes 10-bit address. Slave logic generates interrupt.

- 6 Bus waiting. Slave ready to receive data.

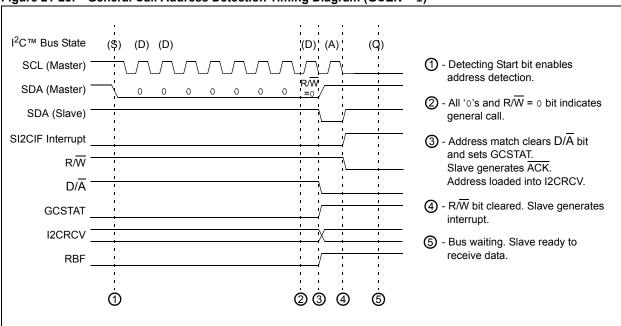

#### 21.7.3.4 General Call Operation

The addressing procedure for the  $I^2C$  bus is such that the first byte after a Start condition usually determines which slave device the master is addressing. The exception is the general call address, which can address all devices. When this address is used, all enabled devices should respond with an Acknowledge. The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0. The general call is always a slave write operation.

The general call address is recognized when the general call enable bit, GCEN (I2CCON<7>), is set (see Figure 21-25). Following a Start bit detect, 8 bits are shifted into the I2CRSR and the address is compared against the I2CADD, and is also compared to the general call address.

If the general call address matches, the following events occur:

- 1. An  $\overline{ACK}$  is generated.

- 2. Slave module will set the GCSTAT bit (I2CSTAT<9>).

- 3. The  $D/\overline{A}$  and  $R/\overline{W}$  bits are cleared.

- The module generates the SI2CIF interrupt on the falling edge of the ninth SCL clock.

- The I2CRSR is transferred to the I2CRCV and the RBF flag bit is set (during the eighth bit).

- The module will wait for the master to send data.

When the interrupt is serviced, the cause for the interrupt can be checked by reading the contents of the GCSTAT bit to determine if the device address was device specific or a general call address.

Note that general call addresses are 7-bit addresses. If A10M bit is set, configuring the slave module for 10-bit addresses and GCEN is set, the slave module continues to detect the 7-bit general call address.

Figure 21-25: General Call Address Detection Timing Diagram (GCEN = 1)

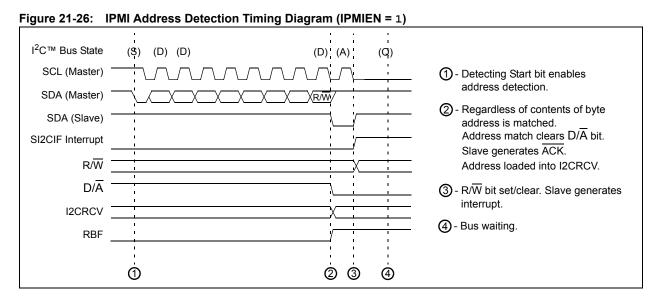

#### 21.7.3.5 Receiving All Addresses (IPMI Operation)

Some I<sup>2</sup>C system protocols require a slave to act upon all messages on the bus. For example, the Intelligent Platform Management Interface (IPMI) bus uses I<sup>2</sup>C nodes as message repeaters in a distributed network. To allow a node to repeat all messages, the slave module must accept all messages, regardless of the device address.

Setting the IPMIEN bit (I2CCON<11>) enables this mode (see Figure 21-26). Regardless of the state of the I2CADD register and the A10M and GCEN bits, all addresses will be accepted. This includes all valid 7-bit addresses, General Call, Start Byte, CBUS, Reserved and HS modes, as well as 10-bit address preambles.

**Note:** The user application must clear the IPMIEN bit during an I<sup>2</sup>C Master operation, and set it only while acting as an IPMI slave.

### 21.7.3.6 When an Address is Invalid

If a 7-bit address does not match the contents of I2CADD<6:0>, the slave module will return to an Idle state and ignore all bus activity until after the Stop condition.

If the first byte of a 10-bit address does not match the contents of I2CADD<9:8>, the slave module will return to an Idle state and ignore all bus activity until after the Stop condition.

If the first byte of a 10-bit address matches the contents of I2CADD<9:8>, however, the second byte of the 10-bit address does not match I2CADD<7:0>, the slave module will return to an Idle state and ignore all bus activity until after the Stop condition.

## 21.7.4 Receiving Data from a Master Device

When the  $R/\overline{W}$  bit of the device address byte is zero and an address match occurs, the  $R/\overline{W}$  bit (I2CSTAT<2>) is cleared. The slave module enters a state waiting for data sent by the master. After the device address byte, the contents of the data byte are defined by the system protocol and are only received by the slave module.

The slave module shifts 8 bits into the I2CRSR register. On the falling edge of the eighth clock (SCL), the following events occur:

- 1. The module begins to generate an ACK or NACK.

- 2. The RBF bit is set to indicate received data.

- 3. The I2CRSR byte is transferred to the I2CRCV register for access by the software.

- 4. The  $D/\overline{A}$  bit is set.

- 5. A slave interrupt is generated. Software may check the status of the I2CSTAT register to determine the cause of the event and then clear the SI2CIF flag.

- 6. The module will wait for the next data byte.

#### 21.7.4.1 Acknowledge Generation

Normally, the slave module will Acknowledge all received bytes by sending an  $\overline{ACK}$  on the <u>ninth</u> SCL clock. If the receive buffer is overrun, the slave module does not generate this  $\overline{ACK}$ . Overrun is indicated if either (or both):

- 1. The buffer full bit, RBF (I2CSTAT<1>), was set before the transfer was received.

- 2. The overflow bit, I2COV (I2CSTAT<6>), was set before the transfer was received.

Table 21-4 shows what happens when a data transfer byte is received, given the status of the RBF and I2COV bits. If the RBF bit is already set when the slave module attempts to transfer to the I2CRCV, the transfer does not occur but the interrupt is generated and the I2COV bit is set. If both the RBF and I2COV bits are set, the slave module acts similarly. The shaded cells show the condition where software did not properly clear the overflow condition. No reception or clock stretching occurs while I2COV bit is set.

Reading the I2CRCV clears the RBF bit. The I2COV bit is cleared by writing to a '0' through software. This bit is also cleared automatically on a Stop or Repeat Start event.

Table 21-4: Data Transfer Received Byte Actions

|     | Bits as Data<br>Received | Transfer         | Generate | Generate<br>SI2CIF Interrupt  | Set       | Set<br>I2COV |  |

|-----|--------------------------|------------------|----------|-------------------------------|-----------|--------------|--|

| RBF | I2COV                    | I2CRSR to I2CRCV | ACK      | (Interrupt occurs if enabled) | RBF       |              |  |

| 0   | 0                        | Yes              | Yes      | Yes                           | Yes       | No change    |  |

| 1   | 0                        | No               | No       | Yes                           | No change | Yes          |  |

| 1   | 1                        | No               | No       | Yes                           | No change | Yes          |  |

| 0   | 1                        | Yes              | No       | Yes                           | Yes       | No change    |  |

**Note:** Shaded cells show state where the software did not properly clear the overflow condition.

#### 21.7.4.2 WAIT States During Slave Receptions

When the slave module receives a data byte, the master can potentially begin sending the next byte immediately. This allows the software controlling the slave module 9 SCL clock periods to process the previously received byte. If this is not enough time, the slave software may want to generate a bus WAIT period.

The STREN bit (I2CCON<6>) enables a bus WAIT to occur on slave receptions. When STREN = 1 at the falling edge of the ninth SCL clock of a received byte, the slave module clears the SCLREL bit. Clearing the SCLREL bit causes the slave module to pull the SCL line low, initiating a WAIT. The SCL clock of the master and slave will synchronize, as shown in **21.6.2** "Master Clock Synchronization".

When the software is ready to resume reception, the software sets SCLREL. This causes the slave module to release the SCL line and the master resumes clocking.

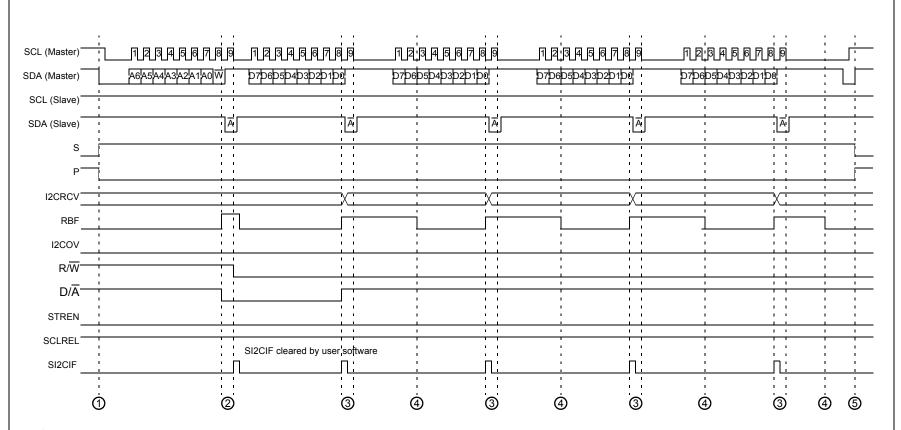

#### 21.7.4.3 Example Messages of Slave Reception

Receiving a slave message is a rather automatic process. The software handling the slave protocol uses the slave interrupt to synchronize to the events.

When the slave detects the valid address, the associated interrupt will notify the software to perform a dummy read and expect a message. On receive data, as each data byte transfers to the I2CRCV register, an interrupt notifies the software to unload the buffer.

Figure 21-27 shows a simple receive message. Being a 7-bit address message, only one interrupt occurs for the address bytes. Then, interrupts occur for each of four data bytes.

At an interrupt, the software may monitor the RBF,  $D/\overline{A}$  and  $R/\overline{W}$  bits to determine the condition of the byte received.

Figure 21-28 shows a similar message using a 10-bit address. In this case, two bytes are required for the address.

Figure 21-29 shows a case where the software does not respond to the received byte and the buffer overruns. On reception of the second byte, the module will automatically NACK the master transmission. Generally, this causes the master to resend the previous byte. The I2COV bit indicates that the buffer has overrun. The I2CRCV buffer retains the contents of the first byte. On reception of the third byte, the buffer is still full and again the module will NACK the master. After this, the software finally reads the buffer. Reading the buffer will clear the RBF bit, however the I2COV bit remains set. The software must clear the I2COV bit. The next received byte will be moved to the I2CRCV buffer and the module will respond with a ACK.

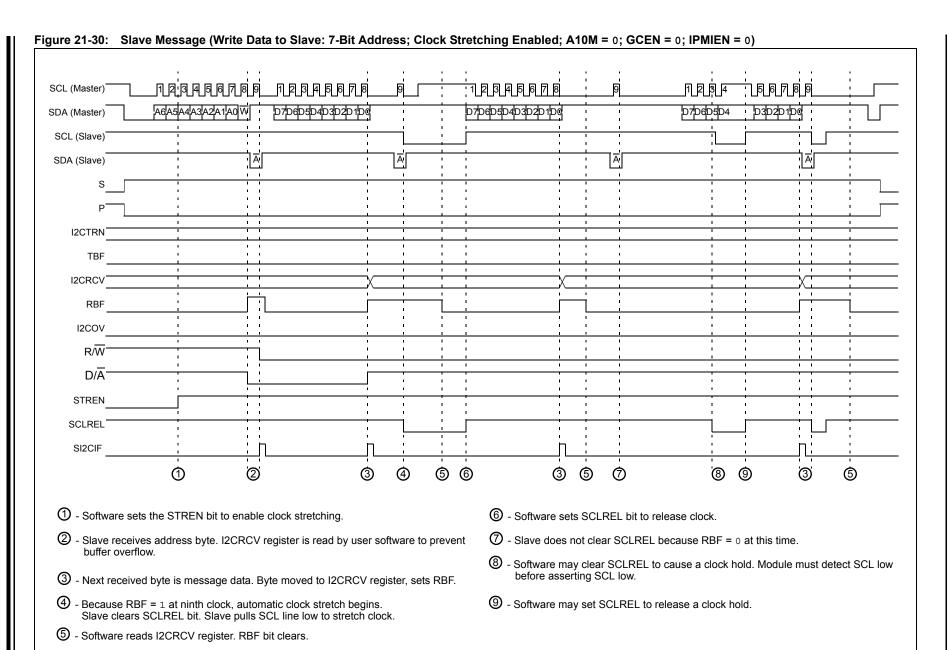

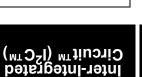

Figure 21-30 highlights clock stretching while receiving data. Note in the previous examples, STREN = 0 which disables clock stretching on receive messages. In this example, the software sets STREN to enable clock stretching. When STREN = 1, the module will automatically clock stretch after each received data byte, allowing the software more time to move the data from the buffer. Note that if RBF = 1 at the falling edge of the ninth clock, the module will automatically clear the SCLREL bit and pull the SCL bus line low. As shown with the second received data byte, if the software can read the buffer and clear the RBF before the falling edge of the ninth clock, the clock stretching will not occur. The software can also suspend the bus at any time. By clearing the SCLREL bit, the module will pull the SCL line low after it detects the bus SCL low. The SCL line will remain low, suspending transactions on the bus until the SCLREL bit is set.

Figure 21-27: Slave Message (Write Data to Slave: 7-Bit Address; Address Matches; A10M = 0; GCEN = 0; IPMIEN = 0)

dsPIC30F Family Reference Manual

- ① Slave recognizes Start event, S and P bits set/clear accordingly.

- O Slave receives address byte. Address matches. Slave Acknowledges and generates interrupt. Address byte is moved to I2CRCV register and is read by user software to prevent buffer overflow.

- 3 Next received byte is message data. Byte moved to I2CRCV register, sets RBF. Slave generates interrupt. Slave Acknowledges reception.

- 4 Software reads I2CRCV register. RBF bit clears.

- ⑤ Slave recognizes Stop event, S and P bits set/clear accordingly.

DS70068F-page 21-42

Figure 21-29: Slave Message (Write Data to Slave: 7-Bit Address; Buffer Overrun; A10M = 0; GCEN = 0; IPMIEN = 0) \_1\_2\_3\_4\_5\_6\_7 8 9 11 2 3 4 5 6 7 8 9 SCL (Master) D7D6D5D4D3D2D1D0 D7D6D5D4D3D2D1D0 D7D6D5D4D3D2D1D0 D7D6D5D4D3D2D1D0 SDA (Master) SCL (Slave) Ā N N Ā SDA (Slave) 12CRCV **RBF** 12COV R/W  $D/\overline{A}$ **STREN SCLREL** SI2CIF cleared by user software SI2CIF 3 1 2 **⑤** 2 **⑤** 4 ① - Slave receives address byte. Address matches. Slave generates interrupt. Address byte is moved to I2CRCV register and is read by user software to prevent Next byte also received before I2CRCV read by software.

I2CRCV register unchanged. Slave generates interrupt.

Slave sends NACK for reception. buffer overflow. 5 - Software reads I2CRCV register. RBF bit clears. ② - Next received byte is message data. Byte moved to I2CRCV register, sets RBF. Slave generates interrupt. Slave Acknowledges reception. 6 - Software clears I2COV bit. ③ - Next byte received before I2CRCV read by software. I2CRCV register unchanged. I2COV overflow bit set. Slave generates interrupt. Slave sends NACK for reception.

### 21.7.5 Sending Data to a Master Device

When the R/ $\overline{W}$  bit of the incoming device address byte is one and an address match occurs, the R/ $\overline{W}$  bit (I2CSTAT<2>) is set. At this point, the master device is expecting the slave to respond by sending a byte of data. The contents of the byte are defined by the system protocol and are only transmitted by the slave module.