## Section 18. 12-bit A/D Converter

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 18.1 Introd    | uction                                                         |  |

|----------------|----------------------------------------------------------------|--|

| 18.2 Contro    | ol Registers                                                   |  |

| 18.3 A/D R     | esult Buffer                                                   |  |

| 18.4 A/D Te    | erminology and Conversion Sequence                             |  |

|                | lodule Configuration                                           |  |

| 18.6 Select    | ting the Voltage Reference Source                              |  |

| 18.7 Select    | ting the A/D Conversion Clock                                  |  |

| 18.8 Select    | ting Analog Inputs for Sampling                                |  |

| 18.9 Enabl     | ing the Module                                                 |  |

| 18.10 How t    | o Start Sampling                                               |  |

| 18.11 How t    | o Stop Sampling and Start Conversions                          |  |

| 18.12 Contro   | olling Sample/Conversion Operation                             |  |

|                | ying How Conversion Results are Written into the Buffer        |  |

| 18.14 Turnir   | ig the A/D Module Off                                          |  |

| 18.15 Conve    | ersion Sequence Examples                                       |  |

| 18.16 A/D S    | ampling Requirements                                           |  |

| 18.17 Readi    | ng the A/D Result Buffer                                       |  |

| 18.18 Trans    | fer Function                                                   |  |

| 18.19 A/D A    | ccuracy/Error                                                  |  |

| 18.20 Conne    | ection Considerations                                          |  |

| 18.21 Initiali | zation                                                         |  |

| 18.22 A/D C    | onversion Speeds                                               |  |

| 18.23 Opera    | tion During Sleep and Idle Modes                               |  |

| 18.24 Effect   | s of a Reset                                                   |  |

| 18.25 Specia   | al Function Registers Associated with the 12-bit A/D Converter |  |

| 18.26 Desig    | n Tips                                                         |  |

|                | ed Application Notes                                           |  |

| 18.28 Revis    | ion History                                                    |  |

|                |                                                                |  |

#### 18.1 Introduction

The dsPIC30F 12-bit A/D converter has the following key features:

- · Successive Approximation Register (SAR) conversion

- · Up to 200 ksps conversion speed

- Up to 16 analog input pins

- · External voltage reference input pins

- Unipolar differential S/H amplifier

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable Buffer Fill modes

- Four result alignment options

- Operation during CPU Sleep and Idle modes

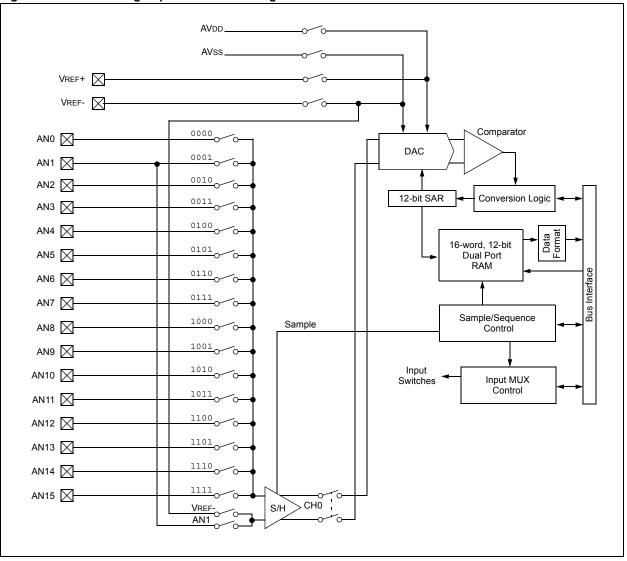

A block diagram of the 12-bit A/D is shown in Figure 18-1. The 12-bit A/D converter can have up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific dsPIC30F device. Refer to the dsPIC30F device data sheets (DS70082 and DS70083) for further details.

The analog inputs are connected via multiplexers to the S/H amplifier, designated CH0. The analog input multiplexer can be switched between two sets of analog inputs during conversions. Unipolar differential conversions are possible using certain input pins (see Figure 18-1).

An Analog Input Scan mode may be enabled for the CH0 S/H amplifier. A Control register specifies which analog input channels will be included in the scanning sequence.

The 12-bit A/D is connected to a 16-word result buffer. Each 12-bit result is converted to one of four 16-bit output formats when it is read from the buffer.

18

#### 18.2 Control Registers

The A/D module has six Control and Status registers. These registers are:

- ADCON1: A/D Control Register 1

- ADCON2: A/D Control Register 2

- ADCON3: A/D Control Register 3

- ADCHS: A/D Input Channel Select Register

- · ADPCFG: A/D Port Configuration Register

- ADCSSL: A/D Input Scan Selection Register

The ADCON1, ADCON2 and ADCON3 registers control the operation of the A/D module. The ADCHS register selects the input pins to be connected to the S/H amplifiers. The ADPCFG register configures the analog input pins as analog inputs or as digital I/O. The ADCSSL register selects inputs to be sequentially scanned.

#### 18.3 A/D Result Buffer

The module contains a 16-word dual port RAM, called ADCBUF, to buffer the A/D results. The 16 buffer locations are referred to as ADCBUF0, ADCBUF1, ADCBUF2, ..., ADCBUFE, ADCBUFF.

Note: The A/D result buffer is a read only buffer.

| Jpper By  |                                                                                |                                                                    |                                                                         |                                                                                                       |                                                            |                                        |                       |                |         |        |

|-----------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|-----------------------|----------------|---------|--------|

| R/W-0     | <u>U-</u>                                                                      | .0                                                                 | R/W-0                                                                   | U-0                                                                                                   | U-0                                                        | U-0                                    | R/                    |                | /W-0    |        |

| ADON      |                                                                                | -                                                                  | ADSIDL                                                                  | —                                                                                                     | —                                                          | —                                      |                       | FORM<1:0       |         |        |

| oit 15    |                                                                                |                                                                    |                                                                         |                                                                                                       |                                                            |                                        |                       |                | bit 8   |        |

|           |                                                                                | Lower                                                              | Byte:                                                                   |                                                                                                       |                                                            |                                        |                       |                |         |        |

|           |                                                                                | R/W                                                                | -0 R/W                                                                  | /-0 R/W-                                                                                              | 0 U-                                                       | C                                      | U-0                   | R/W-0          | R/W-0   | R/C-0  |

|           |                                                                                |                                                                    |                                                                         |                                                                                                       |                                                            |                                        |                       |                | HC, HS  | HC, HS |

|           |                                                                                |                                                                    | SSRC                                                                    | <2:0>                                                                                                 |                                                            |                                        | _                     | ASAM           | SAMP    | DONE   |

|           |                                                                                | bit 7                                                              |                                                                         |                                                                                                       |                                                            |                                        |                       |                |         | bit 0  |

| bit 15    |                                                                                | convert                                                            | erating Mod<br>er module is<br>er is off                                |                                                                                                       |                                                            |                                        |                       |                |         |        |

| oit 14    | Unimple                                                                        | emente                                                             | d: Read as                                                              | ʻ0 <b>'</b>                                                                                           |                                                            |                                        |                       |                |         |        |

| oit 13    |                                                                                |                                                                    | n Idle Mode                                                             |                                                                                                       |                                                            |                                        |                       |                |         |        |

|           |                                                                                |                                                                    |                                                                         | eration when d<br>tion in Idle mo                                                                     |                                                            | s Idle mo                              | de                    |                |         |        |

| oit 12-10 |                                                                                |                                                                    | d: Read as '                                                            |                                                                                                       | ue                                                         |                                        |                       |                |         |        |

| oit 9-8   |                                                                                |                                                                    | ata Output F                                                            |                                                                                                       |                                                            |                                        |                       |                |         |        |

|           | 11 = Sig<br>10 = Fra<br>01 = Sig                                               | ned fra<br>ctional<br>ned inte                                     | ctional (DOL<br>(DOUT = d<br>eger (DOUT                                 | JT = sddd dd<br>ddd dddd dd<br>= ssss sddd<br>) dddd dddd                                             | ddd 0000 <b>)</b><br>d dddd dd                             |                                        |                       |                |         |        |

| oit 7-5   | 111 = In<br>110 = Re<br>101 = Re<br>100 = Re<br>011 = M<br>010 = G<br>001 = Ae | ternal c<br>eserved<br>eserved<br>otor Co<br>eneral p<br>ctive tra | counter ends<br>d<br>d<br>ontrol PWM i<br>purpose Tim<br>ansition on II | igger Source S<br>sampling and<br>nterval ends s<br>er3 compare e<br>NT0 pin ends s<br>nds sampling a | l starts conv<br>ampling and<br>ends sampli<br>sampling an | d starts co<br>ng and st<br>d starts c | onversio<br>tarts cor | on<br>nversion |         |        |

| oit 4-3   | Unimple                                                                        | emente                                                             | d: Read as                                                              | ʻ0 <b>'</b>                                                                                           |                                                            |                                        |                       |                |         |        |

| oit 2     | 1 = Sam                                                                        | pling be                                                           |                                                                         | tart bit<br>liately after las<br>SAMP bit set                                                         | t conversio                                                | n comple                               | tes. SA               | MP bit is au   | ito set |        |

| pit 1     | 1 = At le<br>0 = A/D<br>When As                                                | ast one<br>sample<br>SAM =                                         | /hold amplifi<br>0, writing '1'                                         | bit<br>e/hold amplifie<br>ers are holding<br>to this bit will<br>'0' to this bit w                    | g<br>start sampli                                          | ng.                                    | start co              | onversion.     |         |        |

| oit O     | <b>DONE:</b> A<br>1 = A/D<br>0 = A/D<br>Clearing                               | VD Cor<br>convers<br>convers<br>this bit                           | nversion Sta<br>sion is done<br>sion is not do<br>will not effe         | tus bit                                                                                               | on in progre                                               | -                                      |                       |                |         |        |

|           |                                                                                |                                                                    |                                                                         |                                                                                                       |                                                            |                                        |                       |                |         |        |

|           | Legend                                                                         |                                                                    | •,                                                                      |                                                                                                       |                                                            | • •                                    |                       |                |         |        |

|           | R = Rea                                                                        | dable b                                                            | π                                                                       | W = Writa                                                                                             | able bit                                                   | C = C                                  | learable              | e by softwa    | re      |        |

| R = Readable bit    | W = Writable bit  | C = Clearable by software |                    |  |  |  |

|---------------------|-------------------|---------------------------|--------------------|--|--|--|

| HC = Hardware clear | HS = Hardware set | U = Unimplemented bit,    | read as '0'        |  |  |  |

| -n = Value at POR   | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

| Register 18-2: | ADCON2: A/D Control Register 2 |

|----------------|--------------------------------|

|----------------|--------------------------------|

| Upper Byte | e:        |       |     |     |       |     |       |

|------------|-----------|-------|-----|-----|-------|-----|-------|

| R/W-0      | R/W-0     | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|            | VCFG<2:0> |       | —   | —   | CSCNA | _   | —     |

| bit 15     |           |       |     |     |       |     | bit 8 |

| Lower Byte | ə:  |       |       |       |       |       |       |

|------------|-----|-------|-------|-------|-------|-------|-------|

| R-0        | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| BUFS       | _   |       | SMPI< | :3:0> |       | BUFM  | ALTS  |

| bit 7      |     |       |       |       |       |       | bit 0 |

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | A/D VREFH          | A/D VREFL          |

|-----|--------------------|--------------------|

| 000 | AVdd               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVdd               | AVss               |

- bit 12 Reserved: User should write '0' to this location

- bit 11 Unimplemented: Read as '0'

bit 10 CSCNA: Scan Input Selections for CH0+ S/H Input for MUX A Input Multiplexer Setting bit

1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

#### bit 7 BUFS: Buffer Fill Status bit

Only valid when BUFM = 1 (ADRES split into 2 x 8-word buffers)

1 = A/D is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = A/D is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

1111 = Interrupts at the completion of conversion for each 16th sample/convert sequence

- 1110 = Interrupts at the completion of conversion for each 15th sample/convert sequence

- . . . . .

0001 = Interrupts at the completion of conversion for each 2nd sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

#### bit 1 BUFM: Buffer Mode Select bit

1 = Buffer configured as two 8-word buffers ADCBUF(15...8), ADCBUF(7...0)

0 = Buffer configured as one 16-word buffer ADCBUF(15...0)

#### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses MUX A input multiplexer settings for first sample, then alternate between MUX B and MUX A input multiplexer settings for all subsequent samples

- 0 = Always use MUX A input multiplexer settings

| Legend:           |                  |                                     |      |

|-------------------|------------------|-------------------------------------|------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'  |      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unk | nown |

| Register  | 18-3: ADCON          | 3: A/D Contro  | ol Register 3  | 6       |           |        |              |               |        |

|-----------|----------------------|----------------|----------------|---------|-----------|--------|--------------|---------------|--------|

| Upper B   | yte:                 |                |                |         |           |        |              |               |        |

| U-0       | U-0                  | U-0            | R/W-0          | R/W-0   | R/W-0     | R/W-   | 0 R/\        | W-0           |        |

|           | —                    | —              |                | 9       | SAMC<4:0> |        |              |               |        |

| bit 15    |                      |                |                |         |           |        |              | bit 8         |        |

|           |                      |                |                |         |           |        |              |               |        |

|           | Lower                | -              |                |         |           |        |              |               |        |

|           | R/W-                 | -0 U-0         | R/W-0          | 0 R/V   | /-0 R/    | W-0    | R/W-0        | R/W-0         | R/W-0  |

|           | ADR                  | C —            |                |         | 1         | ADCS<5 | 5:0>         |               |        |

|           | bit 7                |                |                |         |           |        |              |               | bit 0  |

|           |                      |                |                |         |           |        |              |               |        |

| bit 15-13 | Unimplemente         |                |                |         |           |        |              |               |        |

| bit 12-8  |                      | •              | ime bits       |         |           |        |              |               |        |

|           | 11111 = <b>31</b> TA | D              |                |         |           |        |              |               |        |

|           | 00001 <b>= 1 TAD</b> |                |                |         |           |        |              |               |        |

|           | 00000 = 0 TAD        |                |                |         |           |        |              |               |        |

| bit 7     | ADRC: A/D Co         | onversion Cloc | k Source bit   |         |           |        |              |               |        |

|           | 1 = A/D interna      |                |                |         |           |        |              |               |        |

|           | 0 = Clock deriv      | •              |                |         |           |        |              |               |        |

| bit 6     | Unimplemente         | ed: Read as '0 | )'             |         |           |        |              |               |        |

| bit 5-0   | ADCS<5:0>: A         |                |                |         |           |        |              |               |        |

|           | 1111111 = Tcy/       | 2 • (ADCS<5:0  | 0> + 1) = 32 • | • ICY   |           |        |              |               |        |

|           | 000001 = Tcy/        | 2 • (ADCS<5)   | 0> + 1) = Tcy  |         |           |        |              |               |        |

|           | 000000 = Tcy/        |                |                |         |           |        |              |               |        |

|           |                      | -              |                |         |           |        |              |               |        |

|           | Legend:              |                |                |         |           |        |              |               |        |

|           | R = Readable         | bit            | W = Writa      | ble bit | U = Unii  | mpleme | nted bit, re | ead as '0'    |        |

|           | -n = Value at P      | OR             | '1' = Bit is   | set     | '0' = Bit | •      |              | x = Bit is ui | nknown |

18

12-bit A/D Converter

## dsPIC30F Family Reference Manual

ADCHS: A/D Input Select Register

| Register 10-4. | Abonio | . AB input o | cicot i togiot |       |       |        |       |        |       |

|----------------|--------|--------------|----------------|-------|-------|--------|-------|--------|-------|

| Upper Byte:    |        |              |                |       |       |        |       |        |       |

| U-0            | U-0    | U-0          | R/W-0          | R/W-0 | R/W-0 | R/W-0  | R/V   | V-0    |       |

| _              | _      |              | CH0NB          |       | CH0S  | B<3:0> |       |        |       |

| bit 15         |        |              |                |       |       |        |       | bit 8  |       |

|                |        |              |                |       |       |        |       |        |       |

|                | Lower  | Byte:        |                |       |       |        |       |        |       |

|                | U-0    | U-0          | U-0            | R/V   | V-0 R | /W-0   | R/W-0 | R/W-0  | R/W-0 |

|                | _      | _            |                | CHO   | DNA   |        | CH0S  | A<3:0> |       |

|                | bit 7  |              |                |       |       |        |       |        | bit C |

bit 15-13 Unimplemented: Read as '0'

Register 18-4.

- bit 12 **CH0NB:** Channel 0 Negative Input Select for MUX B Multiplexer Setting bit Same definition as bit <4> (see **Note**).

- bit 11-8 **CH0SB<3:0>:** Channel 0 Positive Input Select for MUX B Multiplexer Setting bit Same definition as bits <3:0> (see **Note**).

- bit 7-5 Unimplemented: Read as '0'

# bit 4 **CH0NA:** Channel 0 Negative Input Select for MUX A Multiplexer Setting bit 1 = Channel 0 negative input is AN1

- 0 = Channel 0 negative input is VREF-

- bit 3-0 CH0SA<3:0>: Channel 0 Positive Input Select for MUX A Multiplexer Setting bit

- 1111 = Channel 0 positive input is AN15

- 1110 = Channel 0 positive input is AN14

- 1101 = Channel 0 positive input is AN13

- • • •

- 0001 = Channel 0 positive input is AN1

- 0000 = Channel 0 positive input is AN0

- **Note:** The analog input multiplexer supports two input setting configurations, denoted MUX A and MUX B. ADCHS<15:8> determines the settings for MUX B, and ADCHS<7:0> determines the settings for MUX A. Both sets of control bits function identically.

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### Register 18-5: ADPCFG: A/D Port Configuration Register

| Upper Byte | ):     |        |        |        |        |       |       |

|------------|--------|--------|--------|--------|--------|-------|-------|

| R/W-0      | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| PCFG15     | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15     |        |        |        |        |        |       | bit 8 |

| Lower Byte | e:    |       |       |       |       |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| PCFG7      | PCFG6 | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7      |       |       |       |       |       |       | bit 0 |

#### bit 15-0 PCFG<15:0>: Analog Input Pin Configuration Control bits

1 = Analog input pin in Digital mode, port read input enabled, A/D input multiplexer input connected to AVss 0 = Analog input pin in Analog mode, port read input disabled, A/D samples pin voltage

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Register 18 | -6: ADCSS | L: A/D Input | Scan Select | Register |        |       |       |

|-------------|-----------|--------------|-------------|----------|--------|-------|-------|

| Upper Byte  | e:        |              |             |          |        |       |       |

| R/W-0       | R/W-0     | R/W-0        | R/W-0       | R/W-0    | R/W-0  | R/W-0 | R/W-0 |

| CSSL15      | CSSL14    | CSSL13       | CSSL12      | CSSL11   | CSSL10 | CSSL9 | CSSL8 |

| bit 15      |           |              |             |          |        |       | bit 8 |

| Lower Byte | <b>):</b> |       |       |       |       |       |       |

|------------|-----------|-------|-------|-------|-------|-------|-------|

| R/W-0      | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CSSL7      | CSSL6     | CSSL5 | CSSL4 | CSSL3 | CSSL2 | CSSL1 | CSSL0 |

| bit 7      |           |       |       |       |       |       | bit 0 |

bit 15-0 CSSL<15:0>: A/D Input Pin Scan Selection bits

1 = Select ANx for input scan

0 = Skip ANx for input scan

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 18.4 A/D Terminology and Conversion Sequence

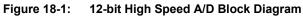

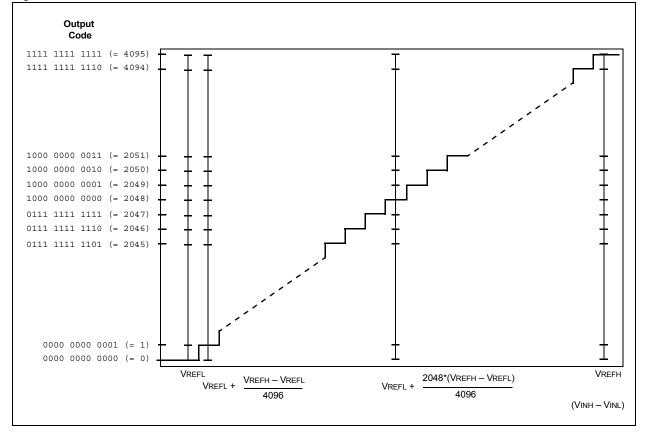

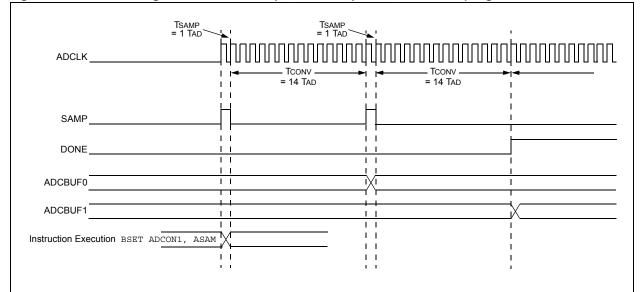

Figure 18-2 shows a basic conversion sequence and the terms that are used. A sampling of the analog input pin voltage is performed by sample and hold S/H amplifiers. The S/H amplifiers are also called S/H channels. The 12-bit A/D converter has one S/H channel, designated CH0. The S/H channel is connected to the analog input pins via the analog input multiplexer. The analog input multiplexer is controlled by the ADCHS register. There are two sets of multiplexer control bits in the ADCHS register that function identically. These two sets of control bits allow two different analog input multiplexer configurations to be programmed, which are called MUX A and MUX B. The A/D converter can optionally switch between the MUX A and MUX B configurations between conversions. The A/D converter can also optionally scan through a series of analog inputs.

Sample time is the time that the A/D module's S/H amplifier is connected to the analog input pin. The sample time may be started manually by setting the SAMP bit (ADCON1<1>) or started automatically by the A/D converter hardware. The sample time is ended manually by clearing the SAMP control bit in the user software or automatically by a conversion trigger source.

Conversion time is the time required for the A/D converter to convert the voltage held by the S/H amplifier. The A/D is disconnected from the analog input pin at the end of the sample time. The A/D converter requires one A/D clock cycle (TAD) to convert each bit of the result plus one additional clock cycle. A total of 14 TAD cycles are required to perform the complete conversion. When the conversion time is complete, the result is loaded into one of 16 A/D result registers (ADCBUF0...ADCBUFF), the S/H can be reconnected to the input pin, and a CPU interrupt may be generated.

The sum of the sample time and the A/D conversion time provides the total conversion time. There is a minimum sample time to ensure that the S/H amplifier will give the desired accuracy for the A/D conversion (see **Section 18.16** "A/D **Sampling Requirements**"). Furthermore, there are multiple input clock options for the A/D converter. The user must select an input clock option that does not violate the minimum TAD specification.

#### Figure 18-2: A/D Sample/Conversion Sequence

The start time for sampling can be controlled in software by setting the SAMP control bit. The start of the sampling time can also be controlled automatically by the hardware. When the A/D converter operates in the Auto Sample mode, the S/H amplifier(s) is reconnected to the analog input pin at the end of the conversion in the sample/convert sequence. The auto sample function is controlled by the ASAM control bit.

The conversion trigger source ends the sampling time and begins an A/D conversion or a sample/convert sequence. The conversion trigger source is selected by the SSRC control bits. The conversion trigger can be taken from a variety of hardware sources or can be controlled manually in software by clearing the SAMP control bit. One of the conversion trigger sources is an auto conversion. The time between auto conversions is set by a counter and the A/D clock. The Auto Sample mode and auto conversion trigger can be used together to provide endless automatic conversions without software intervention.

An interrupt may be generated at the end of each sample/convert sequence or multiple sample/convert sequences, as determined by the value of the SMPI control bits. The number of sample/convert sequences between interrupts can vary between 1 and 16.

#### 18.5 A/D Module Configuration

The following steps should be followed for performing an A/D conversion:

- 1. Configure the A/D module

- · Select voltage reference source to match expected range on analog inputs

- · Select the analog conversion clock to match desired data rate with processor clock

- · Determine how sampling will occur

- Determine how inputs will be allocated to the S/H channel

- · Select how conversion results are presented in the buffer

- Select interrupt rate

- Turn on A/D module

- 2. Configure A/D interrupt (if required)

- · Clear ADIF bit

- · Select A/D interrupt priority

The options for each configuration step are described in the subsequent sections.

**Note:** The SSRC<2:0>, SIMSAM, ASAM, CHPS<1:0>, SMPI<3:0>, BUFM and ALTS bits, as well as the ADCON3 and ADCSSL registers, should not be written to while ADON = 1. This would lead to indeterminate results.

#### 18.6 Selecting the Voltage Reference Source

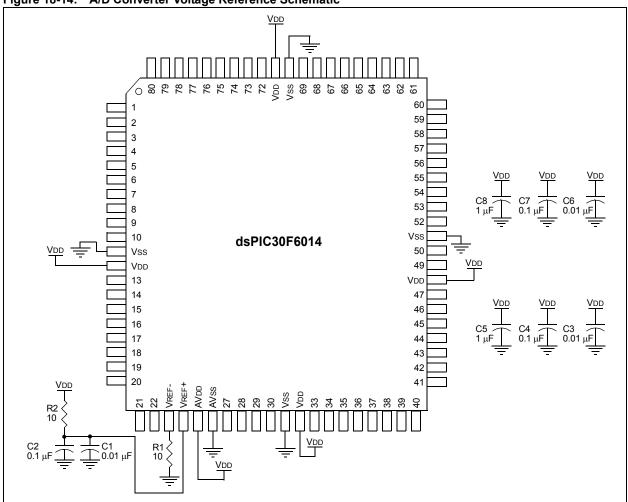

The voltage references for A/D conversions are selected using the VCFG<2:0> control bits (ADCON2<15:13>). The upper voltage reference (VREFH) and the lower voltage reference (VREFL) may be the internal AVDD and AVss voltage rails or the VREF+ and VREF- input pins.

The external voltage reference pins may be shared with the AN0 and AN1 inputs on low pin count devices. The A/D converter can still perform conversions on these pins when they are shared with the VREF+ and VREF- input pins.

The voltages applied to the external reference pins must meet certain specifications. Refer to the "Electrical Specifications" section of the device data sheet for further details.

**Note:** External VREF+ and VREF- pins must be selected for the conversion rates above 100 ksps. See **Section 18.22 "A/D Conversion Speeds"** for further details.

#### 18.7 Selecting the A/D Conversion Clock

The A/D converter has a maximum rate at which conversions may be completed. An analog module clock, TAD, controls the conversion timing. The A/D conversion requires 14 clock periods (14 TAD). The A/D clock is derived from the device instruction clock.

The period of the A/D conversion clock is software selected using a six-bit counter. There are 64 possible options for TAD, specified by the ADCS<5:0> bits (ADCON3<5:0>). Equation 18-1 gives the TAD value as a function of the ADCS control bits and the device instruction cycle clock period, Tcy.

Equation 18-1: A/D Conversion Clock Period

$$T_{AD} = \frac{T_{CY}(ADCS+1)}{2}$$

$$ADCS = \frac{2T_{AD}}{T_{CY}} - 1$$

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 333.33 nsec (see **Section 18.22 "A/D Conversion Speeds"** for further details).

The A/D converter has a dedicated internal RC clock source that can be used to perform conversions. The internal RC clock source should be used when A/D conversions are performed while the dsPIC30F is in Sleep mode. The internal RC oscillator is selected by setting the ADRC bit (ADCON3<7>). When the ADRC bit is set, the ADCS<5:0> bits have no effect on the A/D operation.

#### 18.8 Selecting Analog Inputs for Sampling

The Sample-and-Hold Amplifier has analog multiplexers (see Figure 18-1) on both its non-inverting and inverting inputs, to select which analog input(s) are sampled. Once the sample/convert sequence is specified, the ADCHS bits determine which analog inputs are selected for each sample.

Additionally, the selected inputs may vary on an alternating sample basis, or may vary on a repeated sequence of samples.

**Note:** Different devices will have different numbers of analog inputs. Verify the analog input availability against the device data sheet.

#### 18.8.1 Configuring Analog Port Pins

The ADPCFG register specifies the input condition of device pins used as analog inputs.

A pin is configured as analog input when the corresponding PCFGn bit (ADPCFG<n>) is clear. The ADPCFG register is clear at Reset, causing the A/D input pins to be configured for analog input by default at Reset.

When configured for analog input, the associated port I/O digital input buffer is disabled so it does not consume current.

The ADPCFG register and the TRISB register control the operation of the A/D port pins.

The port pins that are desired as analog inputs must have their corresponding TRIS bit set, specifying port input. If the I/O pin associated with an A/D input is configured as an output, TRIS bit is cleared, the pin is in Analog mode (ADPCFG<n> = 0) and the port digital output level (VOH or VOL) will be converted. After a device Reset, all TRIS bits are set.

A pin is configured as digital I/O when the corresponding PCFGn bit (ADPCFG<n>) is set. In this configuration, the input to the analog multiplexer is connected to AVss.

| Note 1: | When reading a port register, any pin configured as an analog input reads as a '0'. |  |

|---------|-------------------------------------------------------------------------------------|--|

| 2:      | Analog levels on any pin that is defined as a digital input (including the AN15:AN0 |  |

|         | pins) may cause the input buffer to consume current that is out of the device's     |  |

|         | specification.                                                                      |  |

#### 18.8.2 Channel 0 Input Selection

The user may select any one of the up to 16 analog inputs to connect to the positive input of the channel. The CH0SA<3:0> bits (ADCHS<3:0>) normally select the analog input for the positive input of channel 0.

The user may select either VREF- or AN1 as the negative input of the channel. The CH0NA bit (ADCHS<4>) normally selects the analog input for the negative input of channel 0.

#### 18.8.2.1 Specifying Alternating Channel 0 Input Selections

The ALTS bit (ADCON2<0>) causes the module to alternate between two sets of inputs that are selected during successive samples.

The inputs specified by CH0SA<3:0>, CH0NA, CHXSA and CHXNA<1:0> are collectively called the MUX A inputs. The inputs specified by CH0SB<3:0>, CH0NB, CHXSB and CHXNB<1:0> are collectively called the MUX B inputs. When the ALTS bit is '1', the module will alternate between the MUX A inputs on one sample and the MUX B inputs on the subsequent sample.

For channel 0, if the ALTS bit is '0', only the inputs specified by CH0SA<3:0> and CH0NA are selected for sampling.

If the ALTS bit is '1' on the first sample/convert sequence for channel 0, the inputs specified by CH0SA<3:0> and CH0NA are selected for sampling. On the next sample convert sequence for channel 0, the inputs specified by CH0SB<3:0> and CH0NB are selected for sampling. This pattern will repeat for subsequent sample conversion sequences.

#### 18.8.2.2 Scanning Through Several Inputs

Channel 0 has the ability to scan through a selected vector of inputs. The CSCNA bit (ADCON2<10>) enables the CH0 channel inputs to be scanned across a selected number of analog inputs. When CSCNA is set, the CH0SA<3:0> bits are ignored.

The ADCSSL register specifies the inputs to be scanned. Each bit in the ADCSSL register corresponds to an analog input. Bit 0 corresponds to AN0, bit 1 corresponds to AN1 and so on. If a particular bit in the ADCSSL register is '1', the corresponding input is part of the scan sequence. The inputs are always scanned from lower to higher numbered inputs, starting at the first selected channel after each interrupt occurs.

**Note:** If the number of scanned inputs selected is greater than the number of samples taken per interrupt, the higher numbered inputs will not be sampled.

The ADCSSL bits only specify the input of the positive input of the channel. The CH0NA bit still selects the input of the negative input of the channel during scanning.

If the ALTS bit is '1', the scanning only applies to the MUX A input selection. The MUX B input selection, as specified by the CH0SB<3:0>, will still select the alternating input. When the input selections are programmed in this manner, the input will alternate between a set of scanning inputs specified by the ADCSSL register and a fixed input specified by the CH0SB bits.

#### 18.9 Enabling the Module

When the ADON bit (ADCON1<15>) is '1', the module is in Active mode and is fully powered and functional.

When ADON is '0', the module is disabled. The digital and analog portions of the circuit are turned off for maximum current savings.

In order to return to the Active mode from the Off mode, the user must wait for the analog stages to stabilize. For the stabilization time, refer to the "Electrical Characteristics" section of the device data sheet.

#### 18.10 How to Start Sampling

#### 18.10.1 Manual

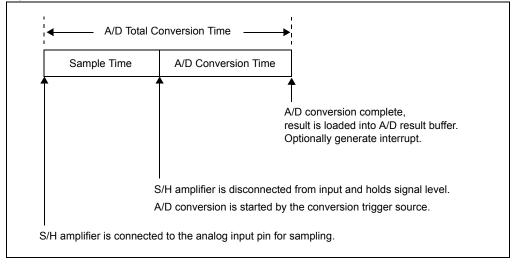

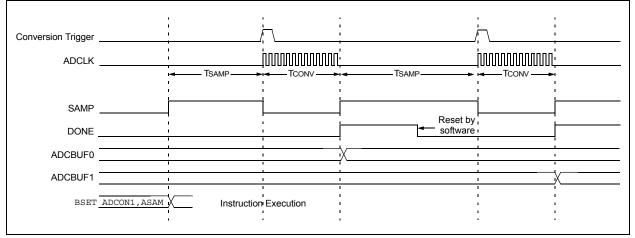

Setting the SAMP bit (ADCON1<1>) causes the A/D to begin sampling. One of several options can be used to end sampling and complete the conversions. Sampling will not resume until the SAMP bit is once again set. For an example, see Figure 18-3.

#### 18.10.2 Automatic

Setting the ASAM bit (ADCON1<2>) causes the A/D to automatically begin sampling a channel whenever a conversion is not active on that channel. One of several options can be used to end sampling and complete the conversions. Sampling on a channel resumes after the conversion of that channel completes. For an example, see Figure 18-4.

The ASAM bit should not be modified while the A/D converter is turned on. If automatic sampling is desired, the ASAM bit must be set before turning the module on. The A/D module does take some amount of time to stabilize (see the TPDU parameter in the device datasheet), therefore, if automatic sampling is enabled, there is no guarantee than the first ADC result will be correct until the ADC module stabilizes. It may be necessary to discard the first ADC result depending on the A/D clock speed.

#### 18.11 How to Stop Sampling and Start Conversions

The conversion trigger source will terminate sampling and start a selected sequence of conversions. The SSRC<2:0> bits (ADCON1<7:5>) select the source of the conversion trigger.

**Note:** The available conversion trigger sources may vary depending on the dsPIC30F device variant. Please refer to the specific device data sheet for the available conversion trigger sources.

**Note:** The SSRC selection bits should not be changed when the A/D module is enabled. If the user wishes to change the conversion trigger source, the A/D module should be disabled first by clearing the ADON bit (ADCON1<15>).

#### 18.11.1 Manual

When SSRC<2:0> = 000, the conversion trigger is under software control. Clearing the SAMP bit (ADCON1<1>) starts the conversion sequence.

Figure 18-3 is an example where setting the SAMP bit initiates sampling and clearing the SAMP bit, terminates sampling and starts conversion. The user software must time the setting and clearing of the SAMP bit to ensure adequate sampling time of the input signal.

| ADPCFG = 0xFFFB;<br>ADCON1 = 0x0000; | <pre>// all PORTB = Digital; RB2 = analog // SAMP bit = 0 ends sampling // and starts converting</pre> |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|

| ADCHS = $0 \times 0002$ ;            | <pre>// Connect RB2/AN2 as CH0 input // in this example RB2/AN2 is the input</pre>                     |

| ADCSSL = 0;                          |                                                                                                        |

| ADCON3 = 0x0002;                     | // Manual Sample, Tad = internal 2 Tcy                                                                 |

| ADCON2 = 0;                          |                                                                                                        |

| ADCON1bits.ADON = 1;                 | // turn ADC ON                                                                                         |

| while (1)                            | // repeat continuously                                                                                 |

| ADCON1bits.SAMP = 1;                 | // start sampling                                                                                      |

|                                      | // for 100 mS                                                                                          |

| ADCON1bits.SAMP = 0;                 |                                                                                                        |

| -                                    |                                                                                                        |

| while (!ADCON1bits.DONE);            |                                                                                                        |

| ADCValue = ADCBUF0;                  | // yes then get ADC value                                                                              |

| }                                    | // repeat                                                                                              |

|                                      |                                                                                                        |

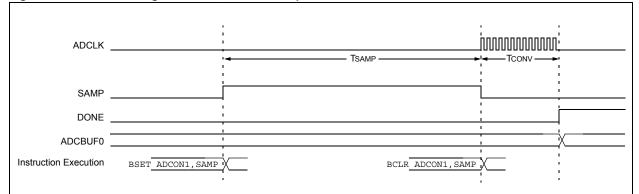

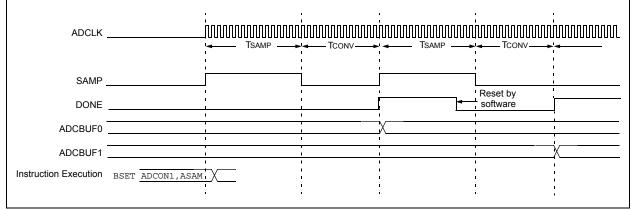

Figure 18-4 is an example where setting the ASAM bit initiates automatic sampling and clearing the SAMP bit, terminates sampling and starts conversion. After the conversion completes, the module will automatically return to a sampling state. The SAMP bit is automatically set at the start of the sample interval. The user software must time the clearing of the SAMP bit to ensure adequate sampling time of the input signal, understanding that the time between clearing of the SAMP bit includes the conversion time, as well as the sampling time.

| ADCLK | Tad0         |                  |      | TSAMP TCC    |                      |

|-------|--------------|------------------|------|--------------|----------------------|

| SAMP  |              | γ                |      |              |                      |

| -     | ADCON1, ASAM | BCF ADCON1, SAMP | BCLR | ADCON1, SAMP | nstruction Execution |

#### 18.11.2 Clocked Conversion Trigger

When SSRC<2:0> = 111, the conversion trigger is under A/D clock control. The SAMC bits (ADCON3<12:8>) select the number of TAD clock cycles between the start of sampling and the start of conversion. After the start of sampling, the module will count a number of TAD clocks specified by the SAMC bits.

#### Equation 18-2: Clocked Conversion Trigger Time

TSMP = SAMC < 4:0 > \*TAD

SAMC must always be programmed for at least 1 clock cycle to ensure sampling requirements are met.

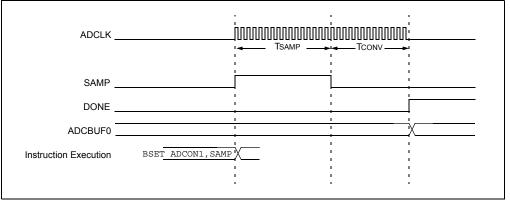

Figure 18-5 shows how to use the clocked conversion trigger with the sampling started by the user software.

Figure 18-5: Converting 1 Channel, Manual Sample Start, TAD Based Conversion Start

#### Example 18-2: Converting 1 Channel, Manual Sample Start, TAD Based Conversion Start Code Example

| ADPCFG = 0xEFFF;<br>ADCON1 = 0x00E0; | 11  | all PORTB = Digital; RB12 = analog<br>SSRC bit = 111 implies internal<br>counter ends sampling and starts<br>converting. |

|--------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| ADCHS = 0x000C;                      |     | Connect RB12/AN12 as CH0 input<br>in this example RB12/AN12 is the input                                                 |

| ADCSSL = 0;                          |     |                                                                                                                          |

| ADCON3 = 0x1F02;                     | 11  | Sample time = 31Tad, Tad = internal 2                                                                                    |

| Тсу                                  |     | -                                                                                                                        |

| ADCON2 = 0;                          |     |                                                                                                                          |

|                                      |     |                                                                                                                          |

| ADCON1bits.ADON = 1;                 | 11  | turn ADC ON                                                                                                              |

| while (1)                            | 11  | repeat continuously                                                                                                      |

| {                                    |     |                                                                                                                          |

| ADCON1bits.SAMP = 1;                 | 11  | start sampling then                                                                                                      |

|                                      | 11  | after 31Tad go to conversion                                                                                             |

| while (!ADCON1bits.DONE)             | ;// | conversion done?                                                                                                         |

| ADCValue = ADCBUF0;                  | 11  | yes then get ADC value                                                                                                   |

| }                                    | //  | repeat// repeat                                                                                                          |

|                                      |     |                                                                                                                          |

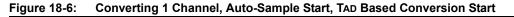

#### 18.11.2.1 Free Running Sample Conversion Sequence

As shown in Figure 18-6, using the Auto-Convert Conversion Trigger mode (SSRC = 111) in combination with the Auto-Sample Start mode (ASAM = 1) allows the A/D module to schedule sample/conversion sequences with no intervention by the user or other device resources. This "Clocked" mode allows continuous data collection after module initialization.

Note: This A/D configuration must be enabled for the conversion rate of 200 ksps (see Section 18.22 "A/D Conversion Speeds" for details).

#### 18.11.2.2 Sample Time Considerations Using Clocked Conversion Trigger and Automatic Sampling

The user must ensure the sampling time exceeds the sampling requirements as outlined in **Section 18.16 "A/D Sampling Requirements"**.

Assuming that the module is set for automatic sampling and using a clocked conversion trigger, the sampling interval is specified by the SAMC bits.

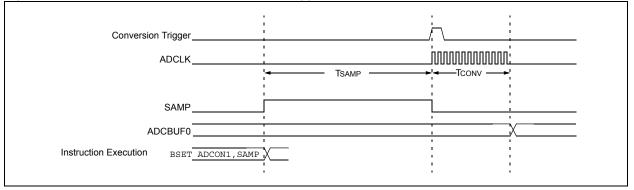

#### 18.11.3 Event Trigger Conversion Start

It is often desirable to synchronize the end of sampling and the start of conversion with some other time event. The A/D module may use one of three sources as a conversion trigger event.

#### 18.11.3.1 External INT Pin Trigger

When SSRC<2:0> = 001, the A/D conversion is triggered by an active transition on the INT0 pin. The INT0 pin may be programmed for either a rising edge input or a falling edge input.

#### 18.11.3.2 General Purpose Timer Compare Trigger

The A/D is configured in this Trigger mode by setting SSRC<2:0> = 010. When a match occurs between the 32-bit timer TMR3/TMR2 and the 32-bit Combined Period register PR3/PR2, a special ADC trigger event signal is generated by Timer3. This feature does not exist for the TMR5/TMR4 timer pair. Refer to **Section 12. "Timers"** for more details.

#### 18.11.3.3 Motor Control PWM Trigger

The PWM module has an event trigger that allows A/D conversions to be synchronized to the PWM time base. When SSRC<2:0> = 011, the A/D sampling and conversion times occur at any user programmable point within the PWM period. The special event trigger allows the user to minimize the delay between the time when A/D conversion results are acquired and the time when the duty cycle value is updated. Refer to **Section 15. "Motor Control PWM**" for more details.

#### 18.11.3.4 Synchronizing A/D Operations to Internal or External Events

The modes where an external event trigger pulse ends sampling and starts conversion (SSRC = 001, 010, 011) may be used in combination with auto sampling (ASAM = 1) to cause the A/D to synchronize the sample conversion events to the trigger pulse source. For example, in Figure 18-8 where SSRC = 010 and ASAM = 1, the A/D will always end sampling and start conversions synchronously with the timer compare trigger event. The A/D will have a sample conversion rate that corresponds to the timer comparison event rate.

Different sample/conversion sequences provide different available sampling times for the S/H channel to acquire the analog signal. The user must ensure the sampling time exceeds the sampling requirements, as outlined in **Section 18.16 "A/D Sampling Requirements**".

Assuming that the module is set for automatic sampling and an external trigger pulse is used as the conversion trigger, the sampling interval is a portion of the trigger pulse interval.

The sampling time is the trigger pulse period, less the time required to complete the conversion.

#### Equation 18-3: Available Sampling Time, Sequential Sampling

TSMP = Trigger Pulse Interval (TSEQ) – Conversion Time (TCONV) TSMP = TSEQ – TCONV Note: TSEQ is the trigger pulse interval time.

#### 18.12 Controlling Sample/Conversion Operation

The application software may poll the SAMP and CONV bits to keep track of the A/D operations, or the module can interrupt the CPU when conversions are complete. The application software may also abort A/D operations if necessary.

#### 18.12.1 Monitoring Sample/Conversion Status

The SAMP (ADCON1<1>) and CONV (ADCON1<0>) bits indicate the sampling state and the conversion state of the A/D, respectively. Generally, when the SAMP bit clears indicating end of sampling, the CONV bit is automatically set indicating start of conversion. If both SAMP and CONV are '0', the A/D is in an inactive state. In some operational modes, the SAMP bit may also invoke and terminate sampling and the CONV bit may terminate conversion.

#### 18.12.2 Generating an A/D Interrupt

The SMPI<3:0> bits control the generation of interrupts. The interrupt will occur some number of sample/conversion sequences after starting sampling and re-occur on each equivalent number of samples.

The value specified by the SMPI bits will correspond to the number of data samples in the buffer, up to the maximum of 16.

Disabling the A/D interrupt is not done with the SMPI bits. To disable the interrupt, clear the ADIE analog module interrupt enable bit.

#### 18.12.3 Aborting Sampling

Clearing the SAMP bit while in Manual Sampling mode will terminate sampling, but may also start a conversion if SSRC = 000.

Clearing the ASAM bit while in Automatic Sampling mode will not terminate an on going sample/convert sequence, however, sampling will not automatically resume after a subsequent conversion.

#### 18.12.4 Aborting a Conversion

Clearing the ADON bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the corresponding ADCBUF buffer location will continue to contain the value of the last completed conversion (or the last value written to the buffer).

#### 18.13 Specifying How Conversion Results are Written into the Buffer

As conversions are completed, the module writes the results of the conversions into the A/D result buffer. This buffer is a RAM array of sixteen 12-bit words. The buffer is accessed through 16 address locations within the SFR space, named ADCBUF0...ADCBUFF.

User software may attempt to read each A/D conversion result as it is generated, however, this might consume too much CPU time. Generally, to simplify the code, the module will fill the buffer with results and then generate an interrupt when the buffer is filled.

#### **18.13.1** Number of Conversions per Interrupt

The SMPI<3:0> bits (ADCON2<5:2>) will select how many A/D conversions will take place before the CPU is interrupted. This can vary from 1 sample per interrupt to 16 samples per interrupt. The A/D converter module always starts writing its conversion results at the beginning of the buffer, after each interrupt. For example, if SMPI<3:0> = 0000, the conversion results will always be written to ADCBUF0. In this example, no other buffer locations would be used.

#### 18.13.2 Restrictions Due to Buffer Size

The user cannot program the SMPI bits to a value that specifies more than 8 conversions per interrupt when the BUFM bit (ADCON2<1>) is '1'. The BUFM bit function is described below.

#### 18.13.3 Buffer Fill Mode

When the BUFM bit (ADCON2<1>) is '1', the 16-word results buffer (ADRES) will be split into two 8-word groups. The 8-word buffers will alternately receive the conversion results after each interrupt event. The initial 8-word buffer used after BUFM is set will be located at the lower addresses of ADCBUF. When BUFM is '0', the complete 16-word buffer is used for all conversion sequences.

The decision to use the BUFM feature will depend upon how much time is available to move the buffer contents after the interrupt, as determined by the application. If the processor can quickly unload a full buffer within the time it takes to sample and convert one channel, the BUFM bit can be '0' and up to 16 conversions may be done per interrupt. The processor will have one sample and conversion time before the first buffer location is overwritten.

If the processor cannot unload the buffer within the sample and conversion time, the BUFM bit should be '1'. For example, if SMPI<3:0> = 0111, then eight conversions will be loaded into 1/2 of the buffer, following which an interrupt will occur. The next eight conversions will be loaded into the other 1/2 of the buffer. The processor will, therefore, have the entire time between interrupts to move the eight conversions out of the buffer.

#### 18.13.4 Buffer Fill Status

When the conversion result buffer is split using the BUFM control bit, the BUFS status bit (ADCON2<7>) indicates the half of the buffer that the A/D converter is currently filling. If BUFS = 0, then the A/D converter is filling ADCBUF0-ADCBUF7 and the user software should read conversion values from ADCBUF8-ADCBUFF. If BUFS = 1, the situation is reversed, and the user software should read conversion values from ADCBUF0-ADCBUF0-ADCBUF7.

#### 18.14 Turning the A/D Module Off

The following sequence is recommended for turning the A/D module off:

- 1. Clear the ADON bit (ADCON1<15>).

- 2. Set the ADCMD bit (PMD1<0>).

- 3. Wait 2 instructions.

- 4. Clear the ADCMD bit (PMD1<0>).

- 5. Reinitialize the ADC module (optional).

The ADCMD bit is the peripheral module disable bit. Setting this bit prevents the A/D module from receiving a clock. Setting and then clearing this bit resets the A/D module.

#### 18.15 Conversion Sequence Examples

The following configuration examples show the A/D operation in different sampling and buffering configurations. In each example, setting the ASAM bit starts automatic sampling. A conversion trigger ends sampling and starts conversion.

#### 18.15.1 Example: Sampling and Converting a Single Channel Multiple Times

Figure 18-9 and Table 18-1 illustrate a basic configuration of the A/D. In this case, one A/D input, AN0, will be sampled and converted. The results are stored in the ADCBUF buffer. This process repeats 16 times until the buffer is full and then the module generates an interrupt. The entire process will then repeat.

With ALTS clear, only the MUX A inputs are active. The CH0SA bits and CH0NA bit are specified (AN0-VREF-) as the input to the sample/hold channel. All other input selection bits are not used.

| Conversion<br>Trigger _<br>ADCLK _ |              |             |           |                   | החחחחח (          |                   |

|------------------------------------|--------------|-------------|-----------|-------------------|-------------------|-------------------|

|                                    | 1<br>1<br>1  | →TCONV→     | →TCONV→   |                   | ←TCONV→           | ← TCONV→          |

| Input to CH0 -                     |              | AN0         | X ANO     | X                 | X ANO             | ANO               |

| ASAM _                             |              |             |           | <u> </u><br> <br> | <u> </u><br> <br> | 1 1<br>1 1<br>1 1 |

| SAMP                               | ſ            |             |           | SS                |                   |                   |

| DONE                               | 1<br>1<br>   |             |           | SS                | 1<br>1<br>1       |                   |

| ADCBUF0                            | <br> <br>    |             | Χ         | <u>s</u>          | <u> </u><br> <br> |                   |

| ADCBUF1                            | <br> <br>    |             |           | X                 | <u> </u><br> <br> |                   |

| ADCBUFE                            | <br> <br>    |             |           | <u>ss</u>         | <u> </u><br> <br> | X                 |

| ADCBUFF                            | <br> <br>    |             |           | <u></u>           | <u> </u><br> <br> | ×                 |

| ADIF                               | <br> <br>    |             |           | <u>ss</u>         | 1<br>1<br>1       |                   |

| BSET                               | ADCON1, ASAM | Instruction | Execution | 1<br>1<br>1       | 1<br>1<br>1       | 1 I<br>1 I<br>1 I |

|                                    | 1            |             |           | l<br>I            | 1                 | 1 I<br>1 I        |

Figure 18-9: Converting One Channel 16 Times/Interrupt

18

Example 18-3: Sampling and Converting a Single Channel Multiple Times Code Example

```

ADPCFG = 0xFFFB;

// all PORTB = Digital; RB2 = analog

ADCON1 = 0 \times 00E0;

// SSRC bit = 111 implies internal

// counter ends sampling and starts

// converting.

ADCHS = 0 \times 0002;

// Connect RB2/AN2 as CH0 input ..

// in this example RB2/AN2 is the input

ADCSSL = 0;

// Sample time = 15Tad, Tad = internal Tcy/2

ADCON3 = 0x0F00;

ADCON2 = 0 \times 003C;

// Interrupt after every 16 samples

ADCON1bits.ADON = 1;

// turn ADC ON

while (1)

// repeat continuously

{

// clear value

// initialize ADCBUF pointer

ADCValue = 0;

ADCValue = 0,

ADC16Ptr = &ADCBUF0; // initialize ADCBUF pointer

IFS0bits.ADIF = 0; // clear ADC interrupt flag

ADCON1bits.ASAM = 1; // auto start sampling

// for alfad then go to conv

// for 31Tad then go to conversion

while (!IFSObits.ADIF); // conversion done?

ADCON1bits.ASAM = 0; // yes then stop sample/convert

for (count = 0; count < 16; count++) // average the 16 ADC value

ADCValue = ADCValue + *ADC16Ptr++;

ADCValue = ADCValue >> 4;

// repeat

}

```

## Table 18-1: Converting One Channel 16 Times/Interrupt

| CONTROL BITS<br>Sequence Select |

|---------------------------------|

| SMPI<2:0> = 1111                |

| Interrupt on 16th sample        |

| BUFM = 0                        |

| Single 16-word result buffer    |

| ALTS = 0                        |

| Always use MUX A input select   |

| MUX A Input Select              |

| CH0SA<3:0> = 0000               |

| Select AN0 for CH0+ input       |

| CH0NA = 0                       |

| Select VREF- for CH0- input     |

| CSCNA = 0                       |

| No input scan                   |

| CSSL<15:0> = n/a                |

| Scan input select unused        |

| MUX B Input Select              |

| CH0SB<3:0> = n/a                |

| Channel CH0+ input unused       |

| CH0NB = n/a                     |

| Channel CH0- input unused       |

| OPERATION SEQUENCE              |

|---------------------------------|

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x0   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x1   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x2   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x3   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x4   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x5   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x6   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x7   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x8   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0x9   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xA   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xB   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xC   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xD   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xE   |

| Sample MUX A Inputs: AN0 -> CH0 |

| Convert CH0, Write Buffer 0xF   |

| Interrupt                       |

| Repeat                          |

| Buffer  | Buffer @      |  |  |  |  |

|---------|---------------|--|--|--|--|

| Address | 1st Interrupt |  |  |  |  |

| ADCBUF0 | AN0 sample 1  |  |  |  |  |

| ADCBUF1 | AN0 sample 2  |  |  |  |  |

| ADCBUF2 | AN0 sample 3  |  |  |  |  |

| ADCBUF3 | AN0 sample 4  |  |  |  |  |

| ADCBUF4 | AN0 sample 5  |  |  |  |  |

| ADCBUF5 | AN0 sample 6  |  |  |  |  |

| ADCBUF6 | AN0 sample 7  |  |  |  |  |

| ADCBUF7 | AN0 sample 8  |  |  |  |  |

| ADCBUF8 | AN0 sample 9  |  |  |  |  |

| ADCBUF9 | AN0 sample 10 |  |  |  |  |

| ADCBUFA | AN0 sample 11 |  |  |  |  |

| ADCBUFB | AN0 sample 12 |  |  |  |  |

| ADCBUFC | AN0 sample 13 |  |  |  |  |

| ADCBUFD | AN0 sample 14 |  |  |  |  |

| ADCBUFE | AN0 sample 15 |  |  |  |  |

| ADCBUFF | AN0 sample 16 |  |  |  |  |

| Buffer @      |

|---------------|

| 2nd Interrupt |

| AN0 sample 17 |

| AN0 sample 18 |

| AN0 sample 19 |

| AN0 sample 20 |

| AN0 sample 21 |

| AN0 sample 22 |

| AN0 sample 23 |

| AN0 sample 24 |

| AN0 sample 25 |

| AN0 sample 26 |

| AN0 sample 27 |

| AN0 sample 28 |

| AN0 sample 29 |

| AN0 sample 30 |

| AN0 sample 31 |

| AN0 sample 32 |

### 18.15.2 Example: A/D Conversions While Scanning Through All Analog Inputs

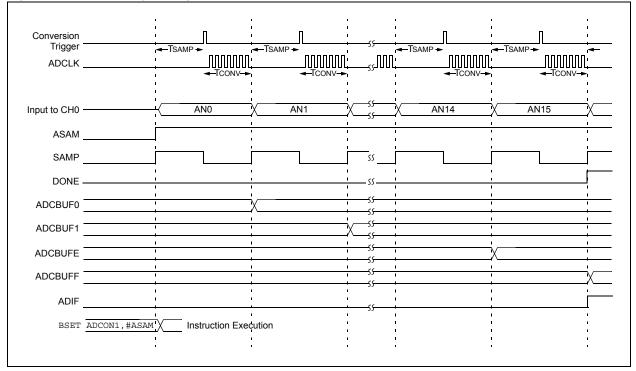

Figure 18-10 and Table 18-2 illustrate a typical setup, where all available analog input channels are sampled and converted. The set CSCNA bit specifies scanning of the A/D inputs to the CH0 positive input. Other conditions are similar to Subsection 18.15.1.

Initially, the AN0 input is sampled by CH0 and converted. The result is stored in the ADCBUF buffer. Then the AN1 input is sampled and converted. This process of scanning the inputs repeats 16 times until the buffer is full and then the module generates an interrupt. The entire process will then repeat.

## Table 18-2: Scanning Through 16 Inputs/Interrupt

| CONTROL BITS<br>Sequence Select  |  |  |  |  |  |

|----------------------------------|--|--|--|--|--|

| SMPI<2:0> = 1111                 |  |  |  |  |  |

| Interrupt on 16th sample         |  |  |  |  |  |

| BUFM = 0                         |  |  |  |  |  |

| Single 16-word result buffer     |  |  |  |  |  |

| ALTS = 0                         |  |  |  |  |  |

| Always use MUX A input select    |  |  |  |  |  |

| MUX A Input Select               |  |  |  |  |  |

| CH0SA<3:0> = n/a                 |  |  |  |  |  |

| Override by CSCNA                |  |  |  |  |  |

| CHONA = 0                        |  |  |  |  |  |

| Select VREF- for CH0- input      |  |  |  |  |  |

| CSCNA = 1                        |  |  |  |  |  |

| Scan CH0+ Inputs                 |  |  |  |  |  |

| CSSL<15:0> = 1111 1111 1111 1111 |  |  |  |  |  |

| Scan all inputs                  |  |  |  |  |  |

| MUX B Input Select               |  |  |  |  |  |

| CH0SB<3:0> = n/a                 |  |  |  |  |  |

| Channel CH0+ input unused        |  |  |  |  |  |

| CH0NB = n/a                      |  |  |  |  |  |

| Channel CH0- input unused        |  |  |  |  |  |

|                                  |  |  |  |  |  |

| OPERATION SEQUENCE                                                |  |  |  |  |  |

|-------------------------------------------------------------------|--|--|--|--|--|

| Sample MUX A Inputs: AN0 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x0                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN1 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x1                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN2 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x2                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN3 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x3                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN4 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x4                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN5 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x5                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN6 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x6                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN7 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x7                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN8 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x8                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN9 -> CH0                                   |  |  |  |  |  |

| Convert CH0, Write Buffer 0x9                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN10 -> CH0                                  |  |  |  |  |  |

| Convert CH0, Write Buffer 0xA                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN11 -> CH0                                  |  |  |  |  |  |

| Convert CH0, Write Buffer 0xB                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN12 -> CH0                                  |  |  |  |  |  |

| Convert CH0, Write Buffer 0xC                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN13 -> CH0                                  |  |  |  |  |  |

| Convert CH0, Write Buffer 0xD<br>Sample MUX A Inputs: AN14 -> CH0 |  |  |  |  |  |

| Convert CH0, Write Buffer 0xE                                     |  |  |  |  |  |

| Sample MUX A Inputs: AN15 -> CH0                                  |  |  |  |  |  |

| Convert CH0, Write Buffer 0xF                                     |  |  |  |  |  |

| Interrupt                                                         |  |  |  |  |  |

| Repeat                                                            |  |  |  |  |  |

| περεαί                                                            |  |  |  |  |  |

| 0 | 1                |

|---|------------------|

| ð | Ν                |

| n | μ                |

| ≶ | it               |

| ř | $\triangleright$ |

| Ē | $\geq$           |

|   | U                |

18

| Buffer<br>Address | Buffer @<br>1st Interrupt |  |  |  |  |  |

|-------------------|---------------------------|--|--|--|--|--|

| ADCBUF0           | AN0 sample 1              |  |  |  |  |  |

| ADCBUF1           | AN1 sample 2              |  |  |  |  |  |

| ADCBUF2           | AN2 sample 3              |  |  |  |  |  |

| ADCBUF3           | AN3 sample 4              |  |  |  |  |  |

| ADCBUF4           | AN4 sample 5              |  |  |  |  |  |

| ADCBUF5           | AN5 sample 6              |  |  |  |  |  |

| ADCBUF6           | AN6 sample 7              |  |  |  |  |  |

| ADCBUF7           | AN7 sample 8              |  |  |  |  |  |

| ADCBUF8           | AN8 sample 9              |  |  |  |  |  |

| ADCBUF9           | AN9 sample 10             |  |  |  |  |  |

| ADCBUFA           | AN10 sample 11            |  |  |  |  |  |

| ADCBUFB           | AN11 sample 12            |  |  |  |  |  |

| ADCBUFC           | AN12 sample 13            |  |  |  |  |  |

| ADCBUFD           | AN13 sample 14            |  |  |  |  |  |

| ADCBUFE           | AN14 sample 15            |  |  |  |  |  |

| ADCBUFF           | AN15 sample 16            |  |  |  |  |  |

| Buffer @<br>2nd Interrupt |

|---------------------------|

| AN0 sample 17             |

| AN1 sample 18             |

| AN2 sample 19             |

| AN3 sample 20             |

| AN4 sample 21             |

| AN5 sample 22             |

| AN6 sample 23             |

| AN7 sample 24             |

| AN8 sample 25             |

| AN9 sample 26             |

| AN10 sample 27            |

| AN11 sample 28            |

| AN12 sample 29            |

| AN13 sample 30            |

| AN14 sample 31            |

| AN15 sample 32            |

## DS70065E-page 18-25

#### 18.15.3 Example: Using Dual 8-Word Buffers

Refer to Subsection 17.15.4 in **Section 17. "10-bit A/D Converter"** for an example that uses dual buffers.

#### 18.15.4 Example: Using Alternating MUX A, MUX B Input Selections

See Subsection 17.15.5 in **Section 17. "10-bit A/D Converter**" for an example that uses the MUX A and MUX B input selections.

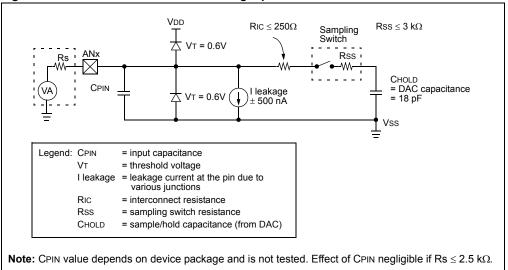

#### 18.16 A/D Sampling Requirements