# Section 16. Quadrature Encoder Interface (QEI)

# **HIGHLIGHTS**

This section of the manual contains the following topics:

| 16 1  | Introduction                                   | 16.2 |

|-------|------------------------------------------------|------|

|       |                                                |      |

| 16.2  | Control and Status Registers                   |      |

| 16.3  | Programmable Digital Noise Filters             |      |

| 16.4  | Quadrature Decoder                             |      |

| 16.5  | 16-Bit Up/Down Position Counter                |      |

| 16.6  | Using QEI as an Alternate 16-Bit Timer/Counter |      |

| 16.7  | Quadrature Encoder Interface Interrupts        |      |

| 16.8  | I/O Pin Control                                |      |

|       | QEI Operation During Power-Saving Modes        |      |

| 16.10 | ) Effects of a Reset                           |      |

| 16.11 | Register Map                                   |      |

| 16.12 | Poesign Tips                                   |      |

| 16.13 | Related Application Notes                      |      |

| 16.14 | Revision History                               |      |

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC30F devices.

Please consult the note at the beginning of the "Quadrature Encoder Interface (QEI)" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

### 16.1 Introduction

#### 16.1.1 Features Overview

Quadrature encoders, also known as incremental encoders or optical encoders, are used in the position and speed detection of rotating motion systems. Quadrature encoders enable closed-loop control of many motor control applications, such as Switched Reluctance (SR) motors and AC Induction Motors (ACIMs).

A typical incremental encoder includes a slotted wheel attached to the shaft of the motor and an emitter/detector module sensing the slots in the wheel. Typically, three output channels, Phase A, Phase B and Index pulse, provide the information on the movement of the motor shaft, including distance and direction.

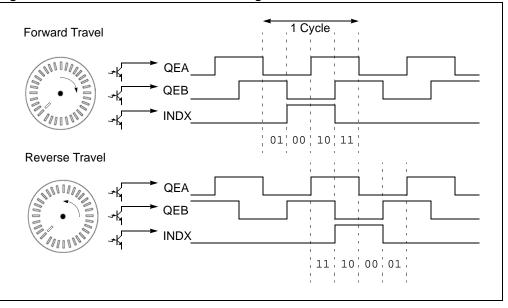

The two channels, Phase A (QEA) and Phase B (QEB), have a unique relationship. If Phase A leads Phase B, the direction (of the motor) is deemed positive or forward. If Phase A lags Phase B, the direction (of the motor) is deemed negative or reverse. A third channel, termed Index (INDX) pulse, occurs once per revolution and is used as a reference to establish an absolute position. See Figure 16-1 for a relative timing diagram of these three signals.

The quadrature signals produced by the encoder can have four unique states. These states are indicated for one count cycle in Figure 16-1. The order of the states are reversed when the direction of travel is changed.

A quadrature decoder captures the phase signals and the index pulse, and converts the information into a numeric count of the position pulses. Generally, the count will increment when the shaft is rotating one direction and decrement when the shaft is rotating in the other direction.

Figure 16-1: Quadrature Encoder Interface Signals

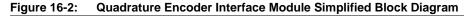

The Quadrature Encoder Interface (QEI) module provides an interface to incremental encoders. The QEI module consists of quadrature decoder logic to interpret the Phase A and Phase B signals and an up/down counter to accumulate the count. The digital filters on the inputs, conditions the input signal. The QEI module also contains the UPDN signal, which represents the QEA and QEB time relationship. Figure 16-2 is a simplified block diagram of the QEI module.

The QEI module includes:

- Three input pins for two phase signals and index pulse

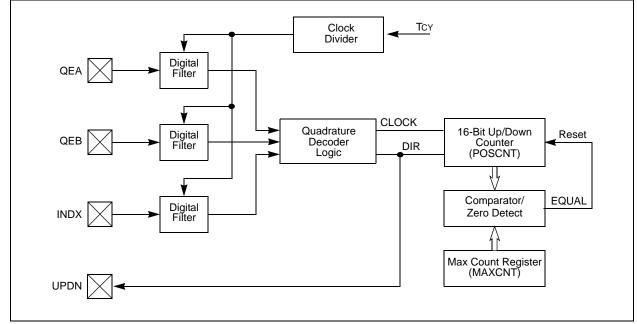

- Programmable digital noise filters on inputs

- Quadrature decoder providing counter pulses and count direction

- 16-bit up/down position counter

- Count direction status

- x2 and x4 count resolution

- Two modes of position counter reset

- General Purpose 16-bit Timer mode/Counter mode

- · Interrupts generated by QEI or counter events

16

# 16.2 Control and Status Registers

The QEI module has the following four user-accessible registers. Figure 16-3 illustrates the registers that are accessible in either Byte mode or Word mode.

- Control/Status Register (QEICON) Allows control of the QEI operation and status flags indicating the module state.

- Digital Filter Control Register (DFLTCON) Allows control of the digital input filter operation.

- Position Count Register (POSCNT) Allows reading and writing of the 16-bit position counter.

- Maximum Count Register (MAXCNT) Holds a value that will be compared to the POSCNT counter in some operations.

**Note:** The POSCNT register allows byte access. However, reading the register in Byte mode may result in partially updated values in subsequent reads. Either use Word mode reads/writes or ensure that the counter is not counting during byte operations.

#### Figure 16-3: QEI Programmer's Model

|        |       |       | QEICON (16 bits |

|--------|-------|-------|-----------------|

| Bit 15 |       | Bit 0 |                 |

|        |       |       | DFLTCON (8 bits |

|        | Bit 7 | Bit 0 |                 |

|        |       |       | POSCNT (16 bits |

| Bit 15 |       | Bit 0 |                 |

|        |       |       | MAXCNT (16 bits |

| Bit 15 |       | Bit 0 |                 |

|                           |                                                                                                                                                                                                                                | QEI Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Register                                                                                                                            |                                                                                   |               |           |        |       |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------|-----------|--------|-------|--|--|--|

| Upper B                   | -                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

| R/W-0                     |                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R-0                                                                                                                                 | R/W-0                                                                             | R/W-0         | R/W-0     | R/W-0  |       |  |  |  |

| CNTER                     | R —                                                                                                                                                                                                                            | QEISIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INDEX                                                                                                                               | UPDN                                                                              |               | QEIM<2:0> |        |       |  |  |  |

| bit 15                    |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           | D      | it 8  |  |  |  |

|                           | Lower Byte                                                                                                                                                                                                                     | Lower Byte:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | R/W-0                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                               | R/W-0                                                                             | R/W-0         | R/W-0     | R/W-0  | R/W-0 |  |  |  |

|                           | SWPAB                                                                                                                                                                                                                          | PCDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TQGATE                                                                                                                              | TQCK                                                                              | PS<1:0>       | POSRES    | TQCS   | UDSRC |  |  |  |

|                           | bit 7                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        | bit ( |  |  |  |

| oit 15                    | CNTERR: Count                                                                                                                                                                                                                  | Error Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Flag bit                                                                                                                            |                                                                                   |               |           |        |       |  |  |  |

|                           | 1 = Position cour                                                                                                                                                                                                              | nt error is occ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | urred                                                                                                                               |                                                                                   |               |           |        |       |  |  |  |

|                           | <ul> <li>0 = Position cour</li> <li>(CNTERR flag or</li> </ul>                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     | -110  or  10                                                                      | 0)            |           |        |       |  |  |  |

| bit 14                    | Unimplemented                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   | 0)            |           |        |       |  |  |  |

| bit 13                    |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | +                                                                                                                                   |                                                                                   |               |           |        |       |  |  |  |

| UL IS                     | <b>QEISIDL:</b> Stop in<br>1 = Discontinue r                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     | ice enters Idle                                                                   | e mode        |           |        |       |  |  |  |

|                           | 0 = Continue mo                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

| bit 12                    | INDEX: Index Pir                                                                                                                                                                                                               | n State Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit (read-only                                                                                                                      | )                                                                                 |               |           |        |       |  |  |  |

|                           | 1 = Index pin is h                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | 0 = Index pin is lo                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

| bit 11                    | <b>UPDN:</b> Position (<br>1 = Position cour                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | 0 = Position counter direction is negative (-)<br>(Read-only bit when QEIM<2:0> = 1xx)                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | (Read/Write b                                                                                                                                                                                                                  | oit when QEIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>/&lt;2:0&gt; =</b> 001)                                                                                                          |                                                                                   |               |           |        |       |  |  |  |

| bit 10-8                  | QEIM<2:0>: Qua                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | 111 = Quadratur<br>110 = Quadratur                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

|                           | 101 = Quadratur                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |                                                                                   |               |           |        |       |  |  |  |

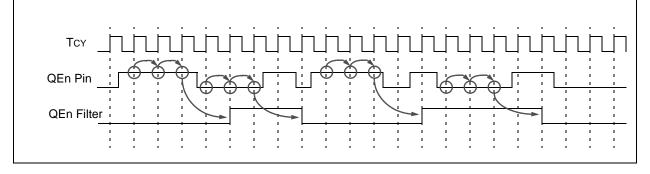

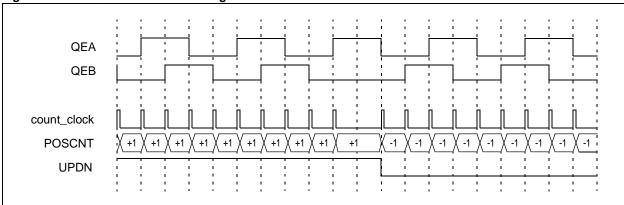

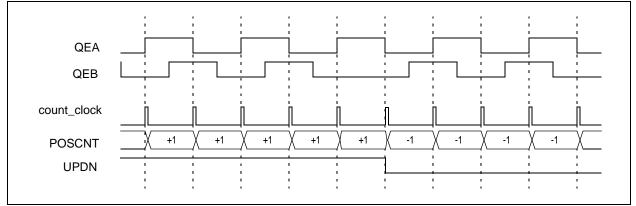

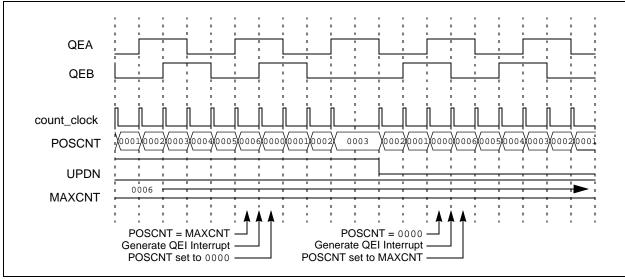

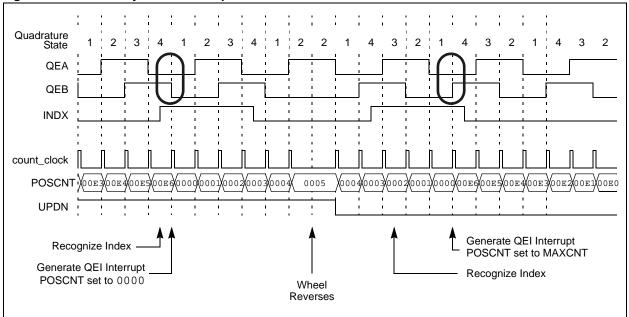

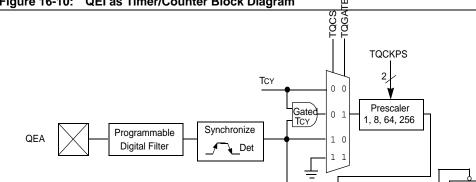

|                           | 100 = Quadratur                                                                                                                                                                                                                | e Encoder Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | erface enable                                                                                                                       |                                                                                   |               |           |        |       |  |  |  |