# Section 62. 10-bit Digital-to-Analog Converter (DAC)

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 62.1  | Introduction                    |  |

|-------|---------------------------------|--|

| 62.2  | Key Features                    |  |

| 62.3  | DAC Registers                   |  |

| 62.4  | DAC Configuration               |  |

| 62.5  | DAC Interrupt Generation        |  |

| 62.6  | DAC Configuration Example       |  |

| 62.7  | Operation in Power-Saving Modes |  |

| 62.8  | Register Map                    |  |

| 62.9  | Related Application Notes       |  |

| 62.10 | Revision History                |  |

## 62.1 INTRODUCTION

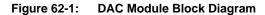

This Digital-to-Analog Converter (DAC) module has 10-bit resolution. Data input is in the form of a 10-bit digital value and it supports left and right-justified input data. Data output is an analog voltage, which is proportional to the digital input value. The module can generate output voltages between AVss and the configured positive DAC reference.

When the DAC module is disabled, it consumes minimum current and its associated output pin can be used as an I/O. The module takes warm-up time (TON) to stabilize after it is enabled. A simplified block diagram of DAC module is shown in Figure 62-1.

**Note:** For more information on Power-Down current (IPD) and TON specifications, refer to the specific device data sheet.

2: The supported trigger inputs vary with the device. For more information on supported trigger inputs, refer to the specific device data sheet.

# 62.2 KEY FEATURES

The DAC has the following key features:

- High-Precision 10-bit DAC Core

- High-Data-Throughput/Fast Settling Time

- · Supports Internal and External Reference Options

- Supports both Left and Right-Justified Input Data Options

- Integration with other Peripherals

- Selectable Trigger Options

- Input Data can be supplied by DMA

- Operates in Idle and Sleep Mode

## 62.3 DAC REGISTERS

The DAC module is controlled by two DAC registers.

DACxCON: DAC Control Register

This register configures the corresponding DAC module by:

- Enabling/Disabling the DAC Module

- Specifying Input Data Format (Right-justified or Left-justified)

- Enabling DAC Trigger Input

- Selecting DAC Trigger Source

- Enabling DAC Output

- Operations in Idle/Sleep Mode

- Selecting Reference Source

- DACxDAT: DAC Data Register

This register specifies both right and left-justified data and also holds the digital data which needs to be converted into analog voltage.

62

| •            |                                                             |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------|-------------------------------------|------------------|-----------------------------------|----------------|----------------|-----------------|--|--|--|--|--|--|

| R/W-0        | U-0                                                         | R/W-0                               | R/W-0            | R/W-0                             | U-0            | U-0            | R/W-0           |  |  |  |  |  |  |

| DACEN        |                                                             | DACSIDL                             | DACSLP           | DACFM                             | —              | —              | DACTRIG         |  |  |  |  |  |  |

| bit 15       |                                                             |                                     |                  |                                   |                |                | bit 8           |  |  |  |  |  |  |

|              |                                                             |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

| R/W-0        | R/W-0                                                       | R/W-0                               | R/W-0            | R/W-0                             | R/W-0          | R/W-0          | R/W-0           |  |  |  |  |  |  |

| DACOE        |                                                             |                                     | DACTSEL<4:0      | >                                 |                | DACR           | EF<1:0>         |  |  |  |  |  |  |

| bit 7        | bit 7                                                       |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

| Legend:      |                                                             |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

| R = Readat   | le hit                                                      | W = Writable                        | hit              | U = Unimplem                      | ented hit read | las 'O'        |                 |  |  |  |  |  |  |

| -n = Value a |                                                             | '1' = Bit is set                    |                  | $0^{\circ} = \text{Bit is clear}$ |                | x = Bit is unk | nown            |  |  |  |  |  |  |

|              |                                                             |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

| bit 15       | DACEN: DA                                                   | C Module Enab                       | le bit           |                                   |                |                |                 |  |  |  |  |  |  |

|              | 1 = Module i                                                | s enabled                           |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | 0 = Module i                                                | s disabled (pow                     | er consumptio    | n is minimal)                     |                |                |                 |  |  |  |  |  |  |

| bit 14       | Unimpleme                                                   | nted: Read as '                     | כי               |                                   |                |                |                 |  |  |  |  |  |  |

| bit 13       | DACSIDL: D                                                  | DACSIDL: DAC Stop in Idle Mode bit  |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              |                                                             | nue module ope<br>ntinues to operat |                  |                                   |                |                |                 |  |  |  |  |  |  |

| bit 12       | DACSLP: DAC Enable During Sleep Mode                        |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | 1 = DAC continues to operate and outputs the last set value |                                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | 0 = Discontir                                               | nue module ope                      | ration in Sleep  | mode                              |                |                |                 |  |  |  |  |  |  |

| bit 11       | DACFM: DA                                                   | DACFM: DAC Data Format Select bit   |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | 1 = Data is le                                              | eft-justified                       |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | 0 = Data is r                                               | ight-justified                      |                  |                                   |                |                |                 |  |  |  |  |  |  |

| bit 10-9     | Unimpleme                                                   | nted: Read as '                     | כי               |                                   |                |                |                 |  |  |  |  |  |  |

| bit 8        | DACTRIG: 7                                                  | rigger Input Ena                    | able bit         |                                   |                |                |                 |  |  |  |  |  |  |

|              |                                                             | Coutput change                      |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              |                                                             | c analog output                     |                  | when the DACx                     | DAT is written |                |                 |  |  |  |  |  |  |

| bit 7        |                                                             | C Output Buffer                     |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              | =                                                           | enabled; DAC                        | -                |                                   | DACEN = 1)     |                |                 |  |  |  |  |  |  |

|              | 0 = Output is                                               | s disabled and th                   | ne pin can be u  | ised as an I/O                    |                |                |                 |  |  |  |  |  |  |

| Note 1: 7    | The DACOE bit i                                             | s not implement                     | ed in all device | s For more info                   | ormation on DA | COE bit refer  | to the specific |  |  |  |  |  |  |

|              |                                                             | et. When implement                  |                  |                                   |                |                |                 |  |  |  |  |  |  |

|              |                                                             |                                     |                  |                                   |                |                | -               |  |  |  |  |  |  |

#### Register 62-1: DACxCON: DAC CONTROL REGISTER

2: For more information on supported trigger inputs, refer to the specific device data sheet.

3: If 2 \* INTREF is selected as a reference source, ensure that the INTREF voltage is not exceeding AVDD/2.

### Register 62-1: DACxCON: DAC CONTROL REGISTER (Continued)

| bit 6-2 | DACTSEL<4:0>: DAC Trigger Source Select bits <sup>(2)</sup>                            |

|---------|----------------------------------------------------------------------------------------|

|         | 11111                                                                                  |

|         | ••• = Reserved                                                                         |

|         | 00110                                                                                  |

|         | 00101 = DAC Trigger 6                                                                  |

|         | 00100 = DAC Trigger 5                                                                  |

|         | 00011 = DAC Trigger 4                                                                  |

|         | 00010 = DAC Trigger 3                                                                  |

|         | 00001 = DAC Trigger 2                                                                  |

|         | 00000 = DAC Trigger 1                                                                  |

| bit 1-0 | DACREF<1:0>: Reference Source Select bits                                              |

|         | 11 = Reference connected to 2 * INTREF internal reference output <sup>(3)</sup>        |

|         | 10 = AVDD                                                                              |

|         | 01 = DVREF+ Pin                                                                        |

|         | 00 = Reference not connected; analog portion of DAC consumes minimal reference current |

- **Note 1:** The DACOE bit is not implemented in all devices. For more information on DACOE bit, refer to the specific device data sheet. When implemented, it is recommended to set DACOE bit before enabling DACEN bit.

- 2: For more information on supported trigger inputs, refer to the specific device data sheet.

- 3: If 2 \* INTREF is selected as a reference source, ensure that the INTREF voltage is not exceeding AVDD/2.

| Register 62-2: | DACxDAT: DAC Data Register (DACFM = 0) – Data Right-Justified |

|----------------|---------------------------------------------------------------|

|----------------|---------------------------------------------------------------|

| U-0 U-0       |   | U-0   | U-0   | U-0   | R/W-0 | R/W-0             |

|---------------|---|-------|-------|-------|-------|-------------------|

| —             | — | —     | _     | —     | DACDA | \T<9:8>           |

|               |   |       |       |       |       | bit 8             |

|               |   |       |       |       |       |                   |

| 0 R/W-0 R/W-0 |   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0             |

|               | _ |       |       |       |       | — — — — — — DACDA |

| bit 0 |

|-------|

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 7

bit 9-0 DACDAT<9:0>: DAC Data bits

Data input register for DAC (right-justified)

#### **Register 62-3:** DACxDAT: DAC Data Register (DACFM = 1) – Data Left-Justified

| R/W-0 R/W-0     |     | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|-----------------|-----|------------------|-------|-------------------|-----------------|--------------------|-------|--|

|                 |     |                  | DACD  | AT<15:8>          |                 |                    |       |  |

| bit 15          |     |                  |       |                   |                 |                    | bit 8 |  |

|                 |     |                  |       |                   |                 |                    |       |  |

| R/W-0 R/W-0     |     | U-0              | U-0   | U-0               | U-0             | U-0                | U-0   |  |

| DACDAT<7:6>     |     | —                | —     | —                 | —               | —                  | —     |  |

| bit 7           |     |                  |       |                   |                 | ·                  | bit C |  |

|                 |     |                  |       |                   |                 |                    |       |  |

| Legend:         |     |                  |       |                   |                 |                    |       |  |

| R = Readable    | bit | W = Writable     | bit   | U = Unimplem      | nented bit, rea | d as '0'           |       |  |

| -n = Value at I | POR | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

| bit 15-6 | DACDAT<15:6>: DAC Data bits                  |

|----------|----------------------------------------------|

|          | Data input register for DAC (left-justified) |

| bit 5-0  | Unimplemented: Read as '0'                   |

## 62.4 DAC CONFIGURATION

### 62.4.1 DAC Input Data Format Selection

The 10-bit input data to DAC can either left-justified or right-justified. This can be selected using the DACFM (DACxCON<11>) bit.

## 62.4.2 DAC Reference Source Selection

There are three reference sources available for the DAC module. They are AVDD, DVREF+ pin and 2 \* INTREF is selected as a reference source, ensure that the INTREF voltage is not exceeding AVDD/2. One of these can be selected using the DACREF<1:0> (DACxCON<1:0>) bits. These reference sources are only the upper reference and the lower reference is always fixed at AVss.

## 62.4.3 DAC Trigger and Trigger Source Selection

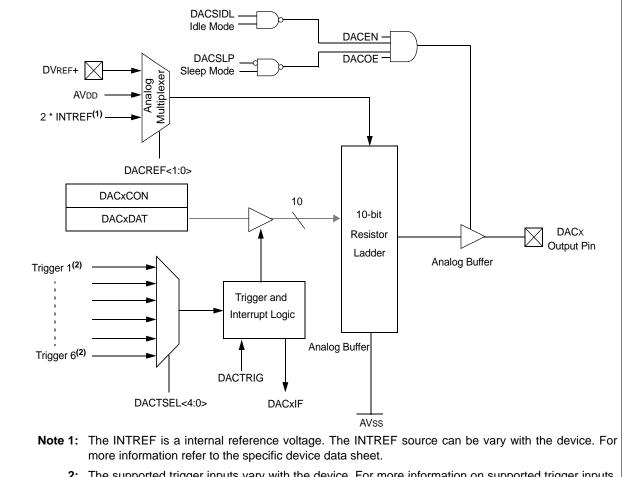

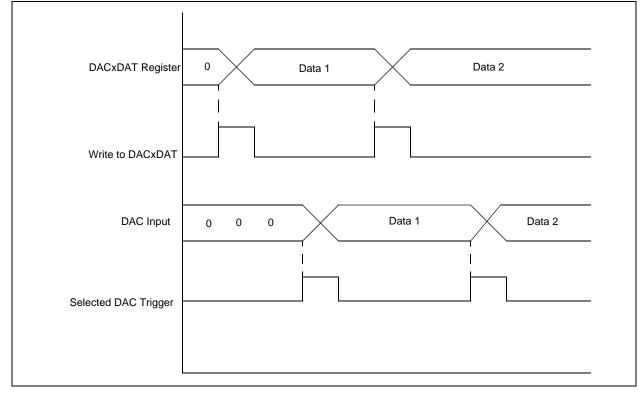

The DAC input data is provided in two ways. When the DACTRIG (DACxCON<8>) bit is '0', the input data is provided as soon as DACxDAT register is updated. When the DACTRIG bit is '1', the last DACxDAT value is provided to DAC module when the selected trigger source triggers. The trigger source can be selected using the DACTSEL<4:0> (DACxCON<6:2>) bits.

When the Trigger mode is selected, the data shadow register is automatically enabled. This shadow register provides the data available in DACxDAT register to the DAC module, only on the occurrence of the selected trigger event. This triggering is synchronised with the system clock.

Figure 62-2 and Figure 62-3 illustrate the timing diagram for DAC input when the trigger is enabled or disabled.

#### Figure 62-2: Timing Diagram – Trigger Enabled (DACTRIG = 1)

Figure 62-3: Timing Diagram – Trigger Disabled (DACTRIG = 0)

### 62.4.4 Enabling the DAC Module

The DAC module is enabled using the DACEN (DACxCON<15>) bit. When DACEN bit is '1', the DAC module is enabled and the module takes TON time to get warmed up. When DACEN bit is '0', the DAC module is disabled. When the DAC module is disabled the Reference Voltage Source is disconnected from the converter to optimize the power consumption.

## 62.4.5 Enabling DAC Output

The output of the DAC module can be enabled by using the DACOE (DACxCON<7>) bit. On enabling the output, an analog voltage corresponding to digital input data will be available on the pin as shown in Equation 62-1.

#### Equation 62-1: DAC OUTPUT VOLTAGE

$$V_{DAC} = \frac{(V_{DACREF}) \cdot (DACxDAT)}{1024}$$

Where,

$V_{DAC}$  is the analog output voltage provided to the DACx pin.

$V_{DACREF}$  is the reference voltage applied on  $DV_{REF+}$  pin,  $AV_{DD}$  or 2 \* *INTREF*, as per the selection.

## 62.5 DAC INTERRUPT GENERATION

DAC module generates interrupt only when the DAC Trigger mode is enabled (DACTRIG = 1). The interrupt is generated when the selected trigger source triggers the DAC conversion. Upon DAC interrupt generation DACxIF bit becomes '1'.

# 62.6 DAC CONFIGURATION EXAMPLE

The following steps should be followed to configure DAC module:

- 1. Select the DAC Reference Voltage (DACxCON<1:0>).

- 2. Select the Input Data Format (DACxCON<11>).

- 3. Select the Input Data Feed mode (DACxCON<8>).

- 4. Select Trigger Source, if Trigger mode is enabled (DACxCON<6:2>).

- 5. Configure the DAC interrupt (if required):

- a) Clear the DACxIF bit

- b) Select interrupt priority bit (DACxIP<2:0>)

- c) Set the DACxIE bit

- d) Enable DAC Output (DACxCON<7>)

- 6. If the DMA is used to provide input data to DAC then refer to the "DMA" section in the specific device data sheet for how to configure the DMA.

- 7. Turn-on DAC module (DACxCON<15>).

## 62.7 OPERATION IN POWER-SAVING MODES

### 62.7.1 DAC Operation during CPU Idle Mode

When the CPU enters Idle mode, the module behaves in one of two ways depending on the state of the DACSIDL (DACxCON<13>) bit.

- When DACSIDL = 0, the module operates without any change and the last output voltage remains on the pin.

- When DACSIDL = 1, the module shuts down, when device enters Idle mode tri-stating the DACO pin.

## 62.7.2 DAC Operation during CPU Doze Mode

When the CPU enters Doze mode, the DAC module is not affected and operates normally.

## 62.7.3 DAC Operation during CPU Sleep Mode

When the CPU enters Sleep mode, the module behaves in one of two ways depending on the state of the DACSLP ((DACxCON<12>) bit.

- When DACSLP = 1, the module operates without any change and the last output voltage remains on the pin.

- When DACSLP = 0, the module shuts down, when device enters Sleep mode tri-stating the DACO pin.

62

## 62.8 REGISTER MAP

### TABLE 62-2: DACx REGISTER MAP

| File Name | Bit 15                                                                     | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|----------------------------------------------------------------------------|--------|---------|--------|--------|--------|-------|---------|-------|----------|----------|----------|----------|----------|---------|---------|---------------|

| DACxCON   | DACEN                                                                      | _      | DACSIDL | DACSLP | DACFM  | _      | _     | DACTRIG | DACOE | DACTSEL4 | DACTSEL3 | DACTSEL2 | DACTSEL1 | DACTSEL0 | DACREF1 | DACREF0 | 0000          |

| DACxDAT   | DACxDAT 10-bit DACx Digital Input Value Register (right or left-justified) |        |         |        |        |        |       |         |       |          |          |          |          | 0000     |         |         |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 62.9 RELATED APPLICATION NOTES

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the PIC24F device family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to the Digital-to-Analog Converter (DAC) are:

#### Title

Application Note #

No related application notes are available at this time.

**Note:** Please visit the Microchip web site (www.microchip.com) for additional application notes and code examples for the PIC24F family of devices.

# 62.10 REVISION HISTORY

# **Revision A (August 2012)**

This is the initial released version of the document.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV — ISO/TS 16949 —

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-62076-495-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820