# Section 57. Power-Saving Features with VBAT

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 57.1  | Introduction                         |       |

|-------|--------------------------------------|-------|

| 57.2  | Overview of Power-Saving Modes       | 57-2  |

| 57.3  | Instruction-Based Power-Saving Modes | 57-4  |

| 57.4  | Vbat Mode                            | 57-15 |

| 57.5  | Microcontroller Clock Manipulation   |       |

| 57.6  | Doze Mode                            |       |

| 57.7  | Selective Peripheral Power Control   |       |

| 57.8  | Register Maps                        |       |

| 57.9  | Design Tips                          |       |

| 57.10 | Related Application Notes            |       |

| 57.11 | Revision History                     |       |

## 57.1 INTRODUCTION

All PIC24F devices offer a number of built-in strategies for reducing power consumption. These strategies can be particularly useful in applications, which are both power-constrained (such as battery operation), yet require periods of full-power operation for timing-sensitive routines (such as serial communications).

In addition, some families of PIC24F devices offer an extended range of power-saving strategies. Aside from their low-power architecture, these devices include an expanded range of dedicated hardware features that allow the microcontroller to reduce power consumption to even lower levels when long-term hibernation is required, and still be able to resume operation on short notice. For convenience, this expanded feature set is referred to as "Power-Saving Features with VBAT", for their new hardware-based features.

Devices that include Power-Saving features with VBAT use five power reduction strategies:

- Instruction-Based Power-Saving Modes

- Hardware-Based Power Reduction Features

- Microcontroller Clock Manipulation

- Software Controlled Doze Mode

- Selective Peripheral Control

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical or timing-sensitive application features. However, it is more convenient to discuss the strategies separately.

## 57.2 OVERVIEW OF POWER-SAVING MODES

In addition to full-power operation, otherwise known as Run mode, PIC24F devices that include the VBAT feature, offer three instruction-based power-saving modes and one hardware-based mode. In descending order of power consumption, they are:

- Idle

- Sleep (including Low-Voltage Sleep)

- Deep Sleep (with and without retention)

- VBAT (with and without RTCC)

By powering down all four modes, different functional areas of the microcontroller allow progressive reductions of operating and Idle power consumption. In addition, three of the modes can be tailored for more power reduction, at a trade-off of some operating features. Table 57-1 lists all of the operating modes (including Run mode, for comparison), in order of increasing power savings, and summarizes how the microcontroller exits the different modes.

| Table 57-1: | Summary of Operating Modes for PIC24F Family Devices with VBAT Power-Saving Features <sup>(5)</sup> |

|-------------|-----------------------------------------------------------------------------------------------------|

|             |                                                                                                     |

|                         | Exit Conditions                             |      |                  |                       |                     |                       |                   |           |     |     |      |            |                        |             |                           |

|-------------------------|---------------------------------------------|------|------------------|-----------------------|---------------------|-----------------------|-------------------|-----------|-----|-----|------|------------|------------------------|-------------|---------------------------|

|                         |                                             |      | Active Systems   |                       |                     | Inter                 | Interrupts Resets |           | ε   | â   | e    |            |                        |             |                           |

| Mode                    | Entry                                       | Core | Peripherals      | Data RAM<br>Retention | RTCC <sup>(1)</sup> | DSGPRn <sup>(2)</sup> | ЯΙΙ               | INT0 only | IIV | POR | MCLR | RTCC Alarm | (DS)WDT <sup>(3)</sup> | VDD Restore | Code Execution<br>Resumes |

| Run (default)           | N/A                                         | Y    | Y                | Y                     | Y                   | Y                     | N/A               | N/A       | N/A | N/A | N/A  | N/A        | N/A                    | N/A         | N/A                       |

| Idle                    | Instruction                                 | Ν    | Y                | Y                     | Y                   | Y                     | Y                 | Y         | Y   | Y   | Y    | Y          | Y                      | N/A         | Next Instruction          |

| Sleep modes:            | ·                                           |      |                  |                       |                     |                       |                   |           |     |     |      |            |                        |             |                           |

| Sleep                   | Instruction                                 | Ν    | S <sup>(4)</sup> | Y                     | Y                   | Y                     | Y                 | Y         | Y   | Y   | Y    | Y          | Y                      | N/A         | Next Instruction          |

| Low-Voltage<br>Sleep    | Instruction +<br>RETEN/LVREN bit            | Ν    | S <sup>(4)</sup> | Y                     | Y                   | Y                     | Y                 | Y         | Y   | Y   | Y    | Y          | Y                      | N/A         | 1                         |

| Deep Sleep modes        | 5:                                          |      |                  |                       |                     |                       |                   |           |     |     |      |            |                        |             |                           |

| Retention<br>Deep Sleep | Instruction + DSEN bit +<br>RETEN/LVREN bit | Ν    | Ν                | Y                     | Y                   | Y                     | N                 | Y         | Ν   | Y   | Y    | Y          | Y                      | N/A         | Next Instruction          |

| Deep Sleep              | Instruction +<br>DSEN bit                   | Ν    | N                | N                     | Y                   | Y                     | N                 | Y         | Ν   | Y   | Y    | Y          | Y                      | N/A         | Reset Vector              |

| Vbat:                   | · · · · ·                                   |      |                  |                       |                     |                       |                   |           |     |     |      |            |                        |             |                           |

| with RTCC               | Hardware                                    | Ν    | N                | Ν                     | Y                   | Y                     | Ν                 | Ν         | Ν   | Ν   | Ν    | Ν          | Ν                      | Y           | Reset Vector              |

Note 1: If RTCC is otherwise enabled in firmware.

2: Data retention in the DSGPR0 and DSGPR1 registers.

3: Deep Sleep WDT in Deep Sleep modes; WDT in all other modes.

4: Some select peripherals may continue to operate in this mode, using either the LPRC or an external clock source.

5: Verify with the device-specific data sheet if all the modes are supported.

## 57.3 INSTRUCTION-BASED POWER-SAVING MODES

PIC24F devices have three instruction-based power-saving modes; two of these have additional features that allow for additional tailoring of power consumption. All three modes are entered through the execution of the PWRSAV instruction. In descending order of power consumption, they are:

- Idle Mode: The CPU is disabled, but the system clock source continues to operate. Peripherals continue to operate, but can optionally be disabled.

- Sleep Modes: The CPU, system clock source and any peripherals that operate on the system clock source are disabled.

- Deep Sleep Modes: The CPU system clock source, and all the peripherals except RTCC and DSWDT, are disabled. This is the lowest power mode for the device. The power to RAM and Flash is also disabled. Deep Sleep modes represent the lowest power modes available without removing power from the application.

Idle and Sleep modes are entered directly with the <code>#IDLE\_MODE</code> and <code>#SLEEP\_MODE</code> arguments. For Deep Sleep mode, it is necessary to set the DSEN bit (DSCON<15>) bit, executing the <code>PWRSAV</code> instruction. To prevent inadvertent entry into Deep Sleep mode and possible loss of data, the DSEN bit must be written to twice (the repeat sequence). The <code>PWRSAV</code> instruction is then executed immediately after the second write. The writes to DSEN do not need to be back-to-back, but this is recommended as a preferred practice.

Examples of the assembly syntax for the PWRSAV instruction are provided in Example 57-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

#### Example 57-1: PWRSAV Assembly Syntax

| ,, = = = = = = = | device into Idle mode                        |

|------------------|----------------------------------------------|

| PWRSAV<br>//     | <pre>#IDLE_MODE;</pre>                       |

|                  | device into Sleep mode                       |

|                  |                                              |

| //               | #SLEEP_MODE;                                 |

|                  | levize into Deen Clean mode                  |

|                  | levice into Deep Sleep mode                  |

|                  | repeat sequence to set the DSEN bit          |

|                  | #8000, W2                                    |

| MOV              | W2, DSCON                                    |

| MOV              | W2, DSCON                                    |

| PWRSAV           | #SLEEP_MODE;                                 |

| //Alternate      | e procedure                                  |

| CLR              | DSCON                                        |

| CLR              | DSCON                                        |

| BSET             | DSCON DSEN                                   |

| NOP              | //Writes to the DSEN bit do not need         |

| NOP              | <pre>//to be sequential (back-to-back)</pre> |

| NOP              |                                              |

| BSET             | DSCON DSEN                                   |

| PWRSAV           | #SLEEP_MODE;                                 |

|                  |                                              |

The instruction-based power-saving modes are exited as a result of several different hardware triggers. When the device exits one of these three operating modes, it is said to 'wake-up'. The characteristics of the power-saving modes are described in the subsequent sections.

| Note: | A repeat sequence is required to set the DSEN bit. The repeat sequence (repeating the instruction twice) is required to write into any of the Deep Sleep registers (DSCON, DSWAKE, DSGPR0, DSGPR1). This is required to avoid the user from entering Deep Sleep by mistake. Any write to these registers has to be done twice to actually complete the write (see Example 57-2). |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | To enter Deep Sleep mode correctly, the DSCON<0> bit needs to be cleared prior to executing the SLEEP instruction (see Example 57-1). Before setting the DSEN bit, the DSCON is cleared, or alternately, the DSCON is loaded by 0x8000.                                                                                                                                          |

#### Example 57-2: The Repeat Sequence

| Example 1:              |                                   |

|-------------------------|-----------------------------------|

| mov #8000, w2           | ; enable DS                       |

| mov w2, DSCON           |                                   |

| mov w2, DSCON           | ; second write required to        |

| actually write to DSCON |                                   |

| Example 2:              |                                   |

| bset DSCON, #15         |                                   |

| nop                     |                                   |

| nop                     |                                   |

| nop                     |                                   |

| bset DSCON, #15         | ; enable DS (two writes required) |

|                         |                                   |

57

## 57.3.1 Interrupts Coincident with Power Save Instructions

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep, Idle or Deep Sleep mode is completed. The device will then wake up from the power-managed mode.

## 57.3.2 Low-Voltage Regulator

For select PIC24F device families, a second on-chip voltage regulator is used for power management in Sleep and Deep Sleep modes. This regulator, also known as the low-voltage regulator, supplies core logic and other circuits with power at a lower VCORE level, about 1.2V nominal. Running these circuits at a lower voltage allows for an additional incremental power saving over the normal minimum VCORE level.

**Note:** Refer to the device data sheet for device-specific regulator output values. These are typically specified as VLVR and VRGOUT for the low-voltage and main (on-chip) regulator, respectfully.

In Sleep and Deep Sleep modes, using the regulator maintains the entire data RAM and its contents, instead of just a few protected registers. This allows the device to exit a power-saving mode and resume code execution as its previous state.

The low-voltage regulator is controlled by the  $\overline{LPCFG}/LVRCFG$  Configuration bit (also designated as LVRCFG is some devices), and the RETEN/LVREN bit (RCON<12>). The  $\underline{LPCFG}/LVRCF$  bit makes the low-voltage regulator available for software control. By default ( $\underline{LPCFG}/LVRCFG = 1$ ), the regulator is disabled and the RETEN/LVREN bit has no effect. Programming  $\underline{LPCFG}/LVRCFG = 0$  allows the RETEN/LVREN bit to control the regulator's operation, leaving its use in power-saving modes at the user's discretion.

Setting the RETEN/LVREN bit prior to executing the PWRSAV #SLEEP\_MODE instruction puts the device into Retention Sleep mode. If the DSEN bit was also unlocked and set prior to the instruction, the device will enter Retention Deep Sleep mode.

The low-voltage regulator is not available outside of Sleep or Deep Sleep modes. Enabling it while the device is operating in Run, Idle or Doze modes does not allow the device to operate at a lower level of VCORE.

## 57.3.3 Idle Mode

When the device enters Idle mode, the following events occur:

- The CPU will stop executing instructions.

- The WDT is automatically cleared.

- The system clock source will remain active and the peripheral modules, by default, will continue to operate normally from the system clock source. Peripherals can optionally be shut down in Idle mode using their 'Stop in Idle' control bit. (See peripheral descriptions for further details.)

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The processor will wake-up from Idle mode on the following events:

- On any interrupt that is individually enabled.

- On any source of device Reset.

- On a WDT time-out.

Upon wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction, or the first instruction in the Interrupt Service Routine (ISR).

## 57.3.3.1 TIME DELAYS ON WAKE-UP FROM IDLE MODE

Unlike a wake-up from Sleep mode, there are no additional time delays associated with wake-up from Idle mode. The system clock is running during Idle mode, therefore, no start-up times are required at wake-up.

## 57.3.3.2 WAKE-UP FROM IDLE ON INTERRUPT

User interrupt sources that are assigned to CPU Priority Level 0 cannot wake-up the CPU from Idle mode because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the CPU priority level for the interrupt must be assigned to CPU Priority Level 1 or greater.

Any source of interrupt that is individually enabled using the corresponding IE control bit in the IECx register, and exceeds the current CPU priority level, will be able to wake-up the processor from Idle mode. When the device wakes from Idle mode, one of two options may occur:

- If the assigned priority for the interrupt is less than or equal to the current CPU priority, the device will wake-up and continue code execution from the instruction following the PWRSAV instruction that initiated Idle mode.

- If the assigned priority level for the interrupt source is greater than the current CPU priority, the device will wake-up and the CPU exception process will begin. Code execution will continue from the first instruction of the ISR.

The IDLE status bit (RCON<2>) is set upon wake-up.

### 57.3.3.3 WAKE-UP FROM IDLE ON RESET

Any Reset, other than a Power-on Reset (POR), will wake-up the CPU from Idle mode. On any device Reset, except a POR, the IDLE status bit is set (RCON<2>) to indicate that the device was previously in Idle mode; in a POR, the IDLE bit is cleared.

### 57.3.3.4 WAKE-UP FROM IDLE ON WDT TIME-OUT

If the WDT is enabled, then the processor will wake-up from Idle mode on a WDT time-out and continue code execution with the instruction following the PWRSAV instruction that initiated Idle mode. Note that the WDT time-out does not reset the device in this case. The WDTO and IDLE status bits (RCON<4,2>) will both be set.

## 57.3.4 Sleep Modes

Most PIC24F devices that incorporate power-saving features and VBAT offer two distinct Sleep modes: Sleep mode and Low-Voltage Sleep mode. The characteristics of both Sleep modes are:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be optimum, provided no I/O pin is sourcing the current.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- If the on-chip voltage regulator and Brown-out Reset (BOR) are enabled, the Brown-out Reset (BOR) circuit remains operational during Sleep mode.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some peripherals may continue to operate in Sleep mode. These peripherals include I/O

pins that detect a change in the input signal or peripherals that use an external clock input.

Any peripheral that operates from the system clock source will be disabled in Sleep mode.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- · On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

| Note: | The on-chip voltage regulator and the low-voltage regulator output voltages will vary    |

|-------|------------------------------------------------------------------------------------------|

|       | based on the device. Refer to the device-specific data sheet for the on-chip/low-voltage |

|       | regulator specifications.                                                                |

## 57.3.4.1 LOW-VOLTAGE SLEEP MODE

Low-Voltage Sleep mode allows for additional power savings over Sleep mode by maintaining key systems from the lower power retention regulator. When the low-voltage regulator is used, the normal on-chip voltage regulator is turned off. By using a lower voltage, a lower total power consumption is achieved.

Low-Voltage Sleep also offers the advantage of maintaining the contents of the data RAM. As a trade-off, the wake-up time is slightly longer than that for Sleep mode.

Low-Voltage Sleep is controlled by the RETEN/LVREN bit (RCON<12>) and the LPCFG/LVRCFG Configuration bit, as described in Section 57.3.2 "Low-Voltage Regulator".

### 57.3.4.2 CLOCK SOURCE CONSIDERATIONS

When the device wakes up from either of the Sleep modes, it will restart the same clock source that was active when Sleep mode was entered. Wake-up delays for the different oscillator modes are shown in Table 57-3 and Table 57-4, respectively.

If the system clock source is derived from a crystal oscillator and/or the PLL, the Oscillator Start-up Timer (OST) and/or PLL lock times must be applied before the system clock source is made available to the device. As an exception to this rule, no oscillator delays are necessary if the system clock source is the secondary oscillator and it was running while in Sleep mode.

### 57.3.4.2.1 Slow Oscillator Start-up

The OST and PLL lock times may not have expired when the power-up delays have expired.

To avoid this condition, one can enable Two-Speed Start-up by the device that will run on FRC until the clock source is stable. Once the clock source is stable, the device will switch to the selected clock source.

## 57.3.4.3 WAKE-UP FROM SLEEP ON INTERRUPT

User interrupt sources that are assigned to CPU Priority Level 0 cannot wake-up the CPU from Sleep mode because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the CPU priority level for the interrupt must be assigned to CPU Priority Level 1 or greater.

Any source of interrupt that is individually enabled, using its corresponding IE control bit in the IECx registers, can wake up the processor from Sleep mode. When the device wakes from Sleep mode, one of two following actions may occur:

- If the assigned priority for the interrupt is less than, or equal to, the current CPU priority, the device will wake-up and continue code execution from the instruction following the PWRSAV instruction that initiated Sleep mode.

- If the assigned priority level for the interrupt source is greater than the current CPU priority, the device will wake-up and the CPU exception process will begin. Code execution will continue from the first instruction of the ISR.

The SLEEP status bit (RCON<3>) is set upon wake-up. For RCON register values, refer to **Section 7. "Reset"** in the *"PIC24F Family Reference Manual"*.

#### 57.3.4.4 WAKE-UP FROM SLEEP ON RESET

All sources of device Reset will wake-up the processor from Sleep mode. Any source of Reset (other than a POR) that wakes the processor will set the SLEEP status bit (RCON<3>) to indicate that the device was previously in Sleep mode.

On a Power-on Reset (POR), the SLEEP bit is cleared.

#### 57.3.4.5 WAKE-UP FROM SLEEP ON WATCHDOG TIME-OUT

If the Watchdog Timer (WDT) is enabled and expires while the device is in Sleep mode, the processor will wake-up. The WDTO and SLEEP status bits (RCON<4:3>) are both set to indicate that the device resumed operation due to the WDT expiration. Note that this event does not reset the device. Operation continues from the instruction following the PWRSAV instruction that initiated Sleep mode.

### 57.3.4.6 CONTROL BIT SUMMARY FOR SLEEP MODES

Table 57-2 shows the settings for the bits relevant to Sleep modes.

#### Table 57-2: Bit Settings for All Sleep Modes

|                   | DOEN                | Low-Voltage Regulator                    |                           |          |  |  |  |

|-------------------|---------------------|------------------------------------------|---------------------------|----------|--|--|--|

| Mode              | DSEN<br>(DSCON<15>) | LPCFG/LVRCFG<br>(CW1<10>) <sup>(1)</sup> | RETEN/LVREN<br>(RCON<12>) | State    |  |  |  |

| Sleep             | x                   | 1                                        | x                         | Disabled |  |  |  |

|                   | x                   | 0                                        | 0                         | Disabled |  |  |  |

| Low-Voltage Sleep | x                   | 0                                        | 1                         | Enabled  |  |  |  |

**Note 1:** This bit is also designated as LVRCFG in some devices.

### 57.3.4.7 WAKE-UP DELAYS

The restart delay associated with waking up from Sleep and Retention Sleep modes parallel each other in terms of clock start-up times; they differ in the time it takes to switch over from their respective regulators. The delays for the different oscillator modes are shown in Table 57-3 and Table 57-4, respectively.

**Note:** The PMSLP/VREGS bit (RCON<8>) may also be designated as the VREGS bit in certain PIC24F devices. The functionality of the bit, and its effect on wake-up times, remains constant regardless of the name.

|              | Clock Source       | Exit Delay | Oscillator Delay | Notes      |

|--------------|--------------------|------------|------------------|------------|

| EC           |                    | Трм        | —                | 1          |

| ECPLL        |                    | Трм        | Тьоск            | 1, 3       |

| XT, HS       |                    | Трм        | Tost             | 1, 2       |

| XTPLL, HSPLL |                    | Трм        | TOST + TLOCK     | 1, 2, 3, 4 |

| SOSC         | (Off during Sleep) | Трм        | Tost             | 1, 2       |

|              | (On during Sleep)  | Трм        | —                | 1          |

| FRC, FR      | CDIV               | Трм        | TFRC             | 1, 5       |

| LPRC         | (Off during Sleep) | Трм        | TLPRC            | 1, 5       |

|              | (On during Sleep)  | Трм        | —                | 1          |

| FRCPLL       |                    | Трм        | TLOCK            | 1, 3       |

Table 57-3:

Delay Times for Exiting from Sleep Mode

**Note 1:** TPM = Start-up delay for program memory stabilization; applicable only when PMSLP/VREGS (RCON<8>) = 0.

**2:** TOST = Oscillator Start-up Timer (OST); a delay of 1024 oscillator periods before the oscillator clock is released to the system.

- **3:** TLOCK = PLL lock time.

- 4: HSPLL mode exceeds PIC24F maximum operating frequency.

- 5: TFRC and TLPRC are RC oscillator start-up times.

**Note:** Please refer to the "**Electrical Characteristics**" section of the specific product data sheet for detailed operating frequency and timing specification values.

#### Table 57-4: Delay Times for Exiting from Low-Voltage Sleep Mode

| C            | Clock Source       | Exit Delay | Oscillator Delay | Notes         |

|--------------|--------------------|------------|------------------|---------------|

| EC           |                    | Tlvr + Tpm | —                | 1, 2          |

| ECPLL        |                    | TLVR + TPM | TLOCK            | 1, 2, 4       |

| XT, HS       |                    | Tlvr + Tpm | Tost             | 1, 2, 3       |

| XTPLL, HSPLL |                    | TLVR + TPM | TOST + TLOCK     | 1, 2, 3, 4, 5 |

| SOSC         | (Off during Sleep) | TLVR + TPM | Tost             | 1, 2, 3       |

|              | (On during Sleep)  | Tlvr + Tpm | —                | 1, 2          |

| FRC, FRC     | DIV                | TLVR + TPM | TFRC             | 1, 2, 6       |

| LPRC         | (Off during Sleep) | TLVR + TPM | Tlprc            | 1, 2, 6       |

|              | (On during Sleep)  | Tlvr + Tpm | _                | 1, 2          |

| FRCPLL       |                    | TLVR + TPM | TLOCK            | 1, 2, 4       |

**Note 1:** TLVR = Low-voltage regulator start-up delay.

- **2:** TPM = Start-up delay for program memory stabilization; applicable only when PMSLP/VREGS (RCON<8>) = 0.

- **3:** TOST = Oscillator Start-up Timer; a delay of 1024 oscillator periods before the oscillator clock is released to the system.

- **4:** TLOCK = PLL lock time.

- 5: HSPLL mode exceeds PIC24F maximum operating frequency.

- **6:** TFRC and TLPRC are RC oscillator start-up times.

**Note:** Please refer to the "**Electrical Characteristics**" section of the specific product data sheet for detailed operating frequency and timing specification values.

## 57.3.5 Deep Sleep Modes

The Deep Sleep modes brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device. There are two modes available: Deep Sleep mode and Retention Deep Sleep mode.

During both Deep Sleep modes, the power to the microcontroller core is removed to reduce leakage current. Therefore, most peripherals and functions of the microcontroller become unavailable during Deep Sleep. However, a few specific peripherals and functions are powered directly from the VDD supply rail of the microcontroller, and therefore, can continue to function in Deep Sleep. In addition, two data memory locations, DSGPR0 and DSGPR1, are preserved for context information after an exit from Deep Sleep.

Devices that implement Deep Sleep mode have a dedicated Deep Sleep Brown-out Reset (DSBOR) and a Deep Sleep Watchdog Timer Reset (DSWDT) for monitoring voltage and time-out events in Deep Sleep mode. The DSBOR and DSWDT are independent of the standard BOR and WDT used with other power-managed modes (Run, Idle and Sleep).

Entering Deep Sleep mode clears the DSWAKE register. If enabled, the Real-Time Clock and Calendar (RTCC) continues to operate uninterrupted.

When a wake-up event occurs in Deep Sleep mode (by Reset, RTCC alarm, external interrupt (INT0) or DSWDT), the device will exit Deep Sleep mode and re-arm a Power-on Reset (POR). When the device is released from Reset, code execution will resume at the device's Reset vector.

## 57.3.5.1 RETENTION DEEP SLEEP MODE

In Retention Deep Sleep, the low-voltage regulator is enabled, which allows the data RAM to retain data while all other systems are powered down. This also allows the device to return to code execution where it left off, instead of going through a POR-like Reset.

As a trade-off, Retention Deep Sleep mode has greater power consumption than Deep Sleep.

Retention Deep Sleep is controlled by the RETEN/LVREN bit (RCON<12>) and the LPCFG/LVRCFG Configuration bit, as described in Section 57.3.2 "Low-Voltage Regulator".

### 57.3.5.2 ENTERING DEEP SLEEP MODES

Deep Sleep modes are entered by:

- Setting the DSEN bit (DSCON<15>)

- Executing the PWRSAV #SLEEP MODE instruction

To enter Retention Deep Sleep, the RETEN/LVREN bit must also be set prior to setting the DSEN bit.

In order to minimize the possibility of inadvertently entering Deep Sleep, the DSEN bit must be set by two separate write operations. Before setting the DSEN bit, the DSCON<0> bit should be cleared by a repeat sequence. To enter Deep Sleep, the PWRSAV instruction must be executed after setting the DSEN bit (i.e., the next instruction). If DSEN is not set when Sleep is executed, the device will enter a Sleep mode instead.

### 57.3.5.3 DEEP SLEEP WAKE-UP SOURCES

The device can be awakened from Deep Sleep modes by any of the following:

- MCLR

- POR

- RTCC alarm

- INT0 interrupt

- I/O pin interrupt

- DSWDT event

After waking from Deep Sleep mode, the device performs a POR. When the device is released from Reset, code execution will begin at the device's Reset vector.

The software can determine if the wake-up was caused from an exit from Deep Sleep mode by reading the DPSLP bit (RCON<10>). If this bit is set, the POR was caused by a Deep Sleep exit. The DS bit must be manually cleared by the software.

The software can determine the wake-up event source by reading the DSWAKE register. These registers are cleared automatically when entering Deep Sleep mode, so software should read these registers after exiting Deep Sleep mode or before re-enabling this mode.

#### 57.3.5.3.1 Clock Selection on Wake-up from Deep Sleep Mode

For Deep Sleep mode, the processor will restart with the default oscillator source, selected with the FNOSC Configuration bits. On wake-up from Deep Sleep, a POR is generated internally, hence, the system resets to its POR state with exception of the RCON, DSCON and DSGPRn registers.

For Retention Deep Sleep, the processor restarts with the same clock source that was selected before entering Retention Deep Sleep mode. Wake-up is similar to that of Sleep and Retention Sleep modes.

### 57.3.5.4 SAVING CONTEXT DATA WITH THE DSGPRn REGISTERS

As exiting Deep Sleep mode causes a POR, most Special Function Registers (SFRs) reset to their default POR values. In addition, because the core power is not supplied in Deep Sleep mode, information in data RAM may be lost when exiting this mode. Applications which require critical data to be saved prior to Deep Sleep may use the Deep Sleep General Purpose registers, DSGPR0 and DSGPR1, or data EEPROM (if available). Unlike other SFRs, the contents of these registers are preserved while the device is in Deep Sleep mode. After exiting Deep Sleep, software can restore the data by reading the registers and clearing the RELEASE bit (DSCON<0>).

Any data stored in the DSGPR registers must be written twice (the repeat sequence). Like other Deep Sleep control features, the write operations do not need to be sequential. However, back-to-back writes are a recommended programming practice.

Since the contents of data RAM are maintained in Retention Deep Sleep, the use of the DSGPR registers to store critical data is not necessary in this mode.

### 57.3.5.5 I/O PINS DURING DEEP SLEEP

During Deep Sleep, general purpose I/O pins retain their previous states. Pins that are configured as inputs (TRIS bit is set), prior to entry into Deep Sleep, remain high-impedance during Deep Sleep.

Pins that are configured as outputs (TRIS bit is clear), prior to entry into Deep Sleep, will remain as output pins during Deep Sleep. While in this mode, they will drive the output level determined by their corresponding LAT bit at the time of entry into Deep Sleep.

Once the device wakes back up, all I/O pins will continue to maintain their previous states, even after the device has finished the POR sequence and is executing application code again. Pins configured as inputs during Deep Sleep will remain high-impedance and pins configured as outputs will continue to drive their previous value. After waking up, the TRIS and LAT registers will be reset. If firmware modifies the TRIS and LAT values for the I/O pins, they will not immediately go to the newly configured states. Once the firmware clears the RELEASE bit (DSCON<0>), the I/O pins are "released". This causes the I/O pins to take the states configured by their respective TRIS and LAT bit values.

If the Deep Sleep BOR (DSBOR) is enabled, and a DSBOR event occurs during Deep Sleep (or VDD is hard cycled to Vss), the I/O pins will be immediately released similar to clearing the RELEASE bit. All previous state information will be lost, including the general purpose DSGPR0 and DSGPR1 contents.

If a MCLR Reset event occurs during Deep Sleep, the I/O pins will also be released automatically, but in this case, the DSGPR0 and DSGPR1 contents will remain valid.

In case of MCLR Reset and all other Deep Sleep wake-up cases, application firmware needs to clear the RELEASE bit (DSCON<0>) in order to reconfigure the I/O pins.

#### 57.3.5.6 DEEP SLEEP WATCHDOG TIMER (DSWDT)

Deep Sleep has its dedicated WDT (DSWDT). It is enabled through the DSWDTEN Configuration bit. The DSWDT is equipped with a postscaler for time-outs of 2.1 ms to 25.7 days, configurable through the Configuration bits, DSWDTPS<3:0>. Entering Deep Sleep mode automatically clears the DSWDT.

The DSWDT also has a configurable reference clock source for selecting the LPRC or SOSC. The reference clock source is configured through the DSWDTOSC Configuration bit.

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay, when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

### 57.3.5.7 DEEP SLEEP LOW-POWER BROWN-OUT RESET

Devices with a Deep Sleep power-saving mode also have a dedicated BOR for Deep Sleep modes (DSBOR). It has a trip point range of 1.7V-2.3V nominal, and is enabled through the DSBOREN Configuration bit.

When the device enters a Deep Sleep mode and receives a DSBOR event, the device will not wake-up and will remain in the Deep Sleep mode. When a valid wake-up event occurs and causes the device to exit Deep Sleep mode, software can determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR (DSCON<1>) status bit.

## 57.3.5.8 RTCC AND DEEP SLEEP

The RTCC can operate uninterrupted during Deep Sleep modes. It can wake-up the device from Deep Sleep by configuring an alarm. The RTCC clock source is configured with the RTCOSC Configuration bit. The available reference clock sources are the LPRC and SOSC. If the LPRC is used, the RTCC accuracy will directly depend on the LPRC tolerance.

If the RTCC is not required, Deep Sleep mode, with the RTCC disabled, affords the lowest power consumption of any of the instruction-based power-saving modes.

## 57.3.5.9 CONTROL BIT SUMMARY FOR SLEEP MODES

Table 57-5 shows the settings for the bits relevant to Deep Sleep modes.

| Table 57-5: | Bit Settings for | All Deep | Sleep Modes |

|-------------|------------------|----------|-------------|

|-------------|------------------|----------|-------------|

| Instruction Deced         | DOEN                | Low-Voltage Regulator                    |                           |          |  |  |  |

|---------------------------|---------------------|------------------------------------------|---------------------------|----------|--|--|--|

| Instruction-Based<br>Mode | DSEN<br>(DSCON<15>) | LPCFG/LVRCFG<br>(CW1<10>) <sup>(1)</sup> | RETEN/LVREN<br>(RCON<12>) | State    |  |  |  |

| Retention Deep Sleep      | 1                   | 0                                        | 1                         | Enabled  |  |  |  |

| Deep Sleep                | 1                   | 1                                        | х                         | Disabled |  |  |  |

**Note 1:** This bit is also designated as LVRCFG in some devices.

57

## 57.3.5.10 WAKE-UP DELAYS

The Reset delay associated with wake-up from Deep Sleep and Retention Deep Sleep modes, in different oscillator modes, are provided in Table 57-6 and Table 57-7, respectively.

|              | Clock Source       | Exit Delay | <b>Oscillator Delay</b> | Notes       |  |

|--------------|--------------------|------------|-------------------------|-------------|--|

| EC           |                    | TDSWU      | _                       |             |  |

| ECPLL        |                    | TDSWU      | TLOCK                   | 1, 3        |  |

| XT, HS       |                    | TDSWU      | Tost                    | 1, 2        |  |

| XTPLL, HSPLL |                    | TDSWU      | TOST + TLOCK            | 1, 2, 3, 4  |  |

| SOSC         | (Off during Sleep) | TDSWU      | Tost                    | 1, 2        |  |

|              | (On during Sleep)  | TDSWU      | —                       | 1           |  |

| FRC, FR      | CDIV               | TDSWU      | TFRC                    | 1, 5        |  |

| LPRC         | (Off during Sleep) | TDSWU      | TLPRC                   | 1, <b>5</b> |  |

|              | (On during Sleep)  | TDSWU      | —                       | 1           |  |

| FRCPLL       |                    | TDSWU      | TFRC + TLOCK            | 1, 3, 5     |  |

Table 57-6:

Delay Times for Exiting from Deep Sleep Mode

**Note 1:** TDSWU = Deep Sleep wake-up delay.

- **2:** TOST = Oscillator Start-up Timer; a delay of 1024 oscillator periods before the oscillator clock is released to the system.

- **3:** TLOCK = PLL lock time.

- 4: HSPLL mode exceeds PIC24F maximum operating frequency.

- **5:** TFRC and TLPRC are RC oscillator start-up times.

| Table 57-7: | Delay Times for Exiting Retention Deep Sleep Mode |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

| C            | lock Source      | Exit Delay | Oscillator Delay | Notes            |

|--------------|------------------|------------|------------------|------------------|

| EC           |                  | Tlvr + Tpm | —                | 1, 2, 7          |

| ECPLL        |                  | TLVR + TPM | TLOCK            | 1, 2, 4, 7       |

| XT, HS       |                  | Tlvr + Tpm | Tost             | 1, 2, 3, 7       |

| XTPLL, HSPLL |                  | TLVR + TPM | TOST + TLOCK     | 1, 2, 3, 4, 5, 7 |

| SOSC         | Off during Sleep | TLVR + TPM | Tost             | 1, 2, 3, 7       |

|              | On during Sleep  | Tlvr + Tpm | —                | 1, 2, 7          |

| FRC, FRC     | DIV              | TLVR + TPM | TFRC             | 1, 2, 6, 7       |

| LPRC:        | Off during Sleep | TLVR + TPM | TLPRC            | 1, 2, 6, 7       |

|              | On during Sleep  | TLVR + TPM | —                | 1, 2, 7          |

| FRCPLL       |                  | TLVR + TPM | TLOCK            | 1, 2, 3, 7       |

**Note 1:** TPM = Start-up delay for program memory stabilization; applicable only when PMSLP/VREGS (RCON<8>) = 0.

- **2:** TLVR = Low-voltage regulator start-up delay

- **3:** TOST = Oscillator Start-up Timer (OST); a delay of 1024 oscillator periods before the oscillator clock is released to the system.

- **4:** TLOCK = PLL lock time.

- 5: HSPLL mode exceeds PIC24F maximum operating frequency.

- 6: TFRC and TLPRC are RC oscillator start-up times.

- 7: TFLASH = Flash program memory ready delay. Setting the PMSLP/VREGS bit will provide a faster wake-up.

**Note 1:** The PMSLP/VREGS bit (RCON<8>) may also be designated as the VREGS bit in certain PIC24F devices. The functionality of the bit, and its effect on wake-up times, remains constant regardless of the name.

2: Refer to the "Electrical Characteristics" section of the specific product data sheet for maximum operating frequency, TDSWU, TFSCM, TLOCK and oscillator start-up specification values.

## 57.4 VBAT MODE

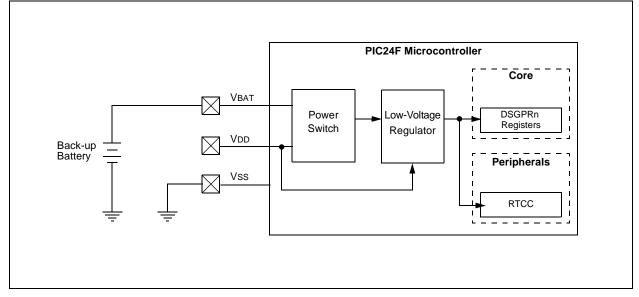

VBAT mode is a hardware-based power mode that maintains only the most critical operations when a power loss occurs on VDD. The mode does this by powering these systems from a back-up power source connected to the VBAT pin. In this mode, the RTCC can run even when there is no power on VDD.

VBAT mode is entered whenever power is removed from VDD. An on-chip power switch detects the power loss from the VDD and connects the VBAT pin so it can supply the power. RTCC (if enabled) and the DSGPRn Deep Sleep Retention registers are powered in VBAT mode (Figure 57-1).

Entering VBAT mode requires that a power source, distinct from the main VDD power source, be available on VBAT and that VDD be completely removed from the VDD pin(s).

As with Deep Sleep modes, the contents of the Deep Sleep Retention (DSGPRn) registers' content are maintained. Since the power loss on VDD may be unforeseen, it is recommended to load any data to be saved in these registers in advance.

Any data stored in the DSGPR registers must be written twice (the repeat sequence). The write operations do not need to be sequential; however, back-to-back writes are a recommended programming practice.

Figure 57-1: VBAT Power Topology

## 57.4.1 Wake-up from VBAT Modes

When VDD is restored to the device, wake-up from VBAT mode is automatic. The device executes a POR and begins executing code from the Reset vector. If the RTCC was enabled, it will continue to run. Wake-up timing is similar to a normal Power on reset.

Wake-up from VBAT mode is identified by checking the state of the VBAT bit (RCON2<0>). If this bit is set when the device is awake and starting to execute the code from the Reset vector, it indicates that the exit was from VBAT mode. To identify future VBAT wake-up events, the bit must be cleared in software.

If a POR occurs without a power source connected to the VBAT pin, the VBPOR bit (RCON2<1>) is set. If this bit is set on a POR, it indicates that a battery needs to be connected to the VBAT pin.

In addition, if the VBAT power source falls below the level needed for Deep Sleep Semaphore operation, while in VBAT mode (e.g., the battery has been drained), the VBPOR bit will be set. VBPOR is also set when the microcontroller is powered up the very first time, even if power is supplied to VBAT

With VBPOR set, the user should clear it and the next time, this bit will only set when VDD = 0 and the VBAT pin has gone below the level (0.4V-0.6V).

If the battery on VBAT becomes depleted while the device is in VBAT mode, and falls below the threshold to maintain the Deep Sleep Retention Registers, VBPOR will also become set after VDD is restored.

## 57.4.2 Saving Context Data with the DSGPRn Registers

As exiting VBAT causes a POR, most Special Function Registers reset to their default POR values. In addition, because the core power is not supplied in VBAT mode, information in data RAM will be lost when exiting this mode. Applications which require critical data to be saved should be saved in DSGPR0 and DSGPR1. If the device has a data EEPROM, critical data can also be store there.

Any data stored to the DSGPR registers must be written twice (the repeat sequence). The write operations do not need to be sequential. However, back-to-back writes are a recommended programming practice.

After exiting VBAT mode, software can restore the data by reading the registers.

## 57.4.3 I/O Pins During VBAT Mode

All I/O pins should be maintained at Vss level; no I/O pins should be given VDD (refer to the **"Absolute Maximum Ratings"** in the **"Electrical Characteristics"** section of the device-specific data sheet) during VBAT mode. The only exceptions are the SOSCI and SOSCO pins, which maintain their states if the secondary oscillator is being used as the RTCC clock source. It is the user's responsibility to restore the I/O pins to their proper states, using the TRIS and LAT bits once VDD has been restored.

Note: If the VBAT mode is not used, the recommendation is to connect the VBAT pin to VDD. When the VBAT mode is used (connected to the battery), as well as when it is not used, it is always recommended to connect a 0.1 μF capacitor from the VBAT pin to ground. The capacitor should be located very close to the VBAT pin. BOR should be enabled for reliable operation of VBAT. (It is recommended to have the BOR enabled to have reliable operation of VBAT.)

# Section 57. Power-Saving Features with VBAT

| R/W-0                     | R/W-0                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                   | R/W-0                                                                                                                                                              | U-0                               | R/W-0                             | R/W-0         | R/W-0                      |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|---------------|----------------------------|--|--|--|

| TRAPR                     | IOPUWR                                                                                                                                                                                                                           | SBOREN                                                                                                                                                                  | RETEN/LVREN                                                                                                                                                        | _                                 | DPSLP <sup>(2)</sup>              | CM            | PMSLP/VREGS <sup>(3)</sup> |  |  |  |

| bit 15                    |                                                                                                                                                                                                                                  |                                                                                                                                                                         |                                                                                                                                                                    |                                   |                                   |               | bit 8                      |  |  |  |

|                           |                                                                                                                                                                                                                                  |                                                                                                                                                                         |                                                                                                                                                                    |                                   |                                   |               |                            |  |  |  |

| R/W-0                     | R/W-0                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                   | R/W-0                                                                                                                                                              | R/W-0                             | R/W-0                             | R/W-1         | R/W-1                      |  |  |  |

| EXTR                      | SWR                                                                                                                                                                                                                              | SWDTEN                                                                                                                                                                  | WDTO                                                                                                                                                               | SLEEP <sup>(2)</sup>              | IDLE <sup>(2)</sup>               | BOR           | POR                        |  |  |  |

| bit 7                     |                                                                                                                                                                                                                                  |                                                                                                                                                                         |                                                                                                                                                                    |                                   |                                   |               | bit 0                      |  |  |  |

| Legend:                   |                                                                                                                                                                                                                                  |                                                                                                                                                                         |                                                                                                                                                                    |                                   |                                   |               |                            |  |  |  |

| R = Readal                | able bit                                                                                                                                                                                                                         | W = Writable                                                                                                                                                            | e bit                                                                                                                                                              | U = Unimpler                      | mented bit, rea                   | ad as '0'     |                            |  |  |  |

| -n = Value a              | at POR                                                                                                                                                                                                                           | '1' = Bit is se                                                                                                                                                         |                                                                                                                                                                    | '0' = Bit is cle                  |                                   | x = Bit is un | ıknown                     |  |  |  |

| bit 12<br>bit 10<br>bit 8 | RETEN/LVR<br>1 = Regulat<br>0 = Regulat<br>DPSLP: Dee<br>1 = Deep Sl<br>0 = Deep Sl                                                                                                                                              | tor is enabled<br>tor is disabled<br>ep Sleep Mod<br>Sleep has occu<br>Sleep has not c                                                                                  | tage Regulator En<br>(LPCFG/LVRCFG<br>I<br>le Flag bit <sup>(2)</sup><br>urred<br>occurred                                                                         | G Configuratio                    |                                   | נ be program  | ımed)                      |  |  |  |

| DILO                      | <ul> <li>PMSLP/VREGS: Program Memory Power During Sleep bit<sup>(3)</sup></li> <li>1 = Program memory bias voltage remains powered during Sleep</li> <li>0 = Program memory bias voltage is powered down during Sleep</li> </ul> |                                                                                                                                                                         |                                                                                                                                                                    |                                   |                                   |               |                            |  |  |  |

|                           | 0 = 1 logial                                                                                                                                                                                                                     | TI Memory Dia                                                                                                                                                           | s voltage is powe                                                                                                                                                  |                                   | ing Sleep                         |               |                            |  |  |  |

| bit 3                     | SLEEP: Wal<br>1 = Device h<br>0 = Device h                                                                                                                                                                                       | ake from Sleep<br>has been in Sl<br>has not been i                                                                                                                      | o Flag bit <sup>(2)</sup><br>leep mode<br>in Sleep mode                                                                                                            |                                   | ing Sleep                         |               |                            |  |  |  |

| bit 3<br>bit 2            | SLEEP: Wal<br>1 = Device h<br>0 = Device h<br>IDLE: Wake<br>1 = Device h                                                                                                                                                         | ake from Sleep<br>has been in Sl                                                                                                                                        | o Flag bit <sup>(2)</sup><br>leep mode<br>in Sleep mode<br>Flag bit <sup>(2)</sup><br>lle mode                                                                     |                                   | шд авер                           |               |                            |  |  |  |

| bit 2<br>Note 1:          | SLEEP: Wal<br>1 = Device h<br>0 = Device h<br>IDLE: Wake<br>1 = Device h<br>0 = Device h<br>Only those bits<br><i>"PIC24F Family</i>                                                                                             | ake from Sleep<br>has been in Sl<br>has not been i<br>e-up from Idle I<br>has been in Id<br>has not been i<br>s relevant to th<br><i>ly Reference I</i>                 | o Flag bit <sup>(2)</sup><br>leep mode<br>in Sleep mode<br>Flag bit <sup>(2)</sup><br>lle mode<br>in Idle mode<br>ne power-saving fe<br><i>Manual</i> " for a comp | eatures are de<br>plete descripti | escribed here.<br>tion of the RCC | ON register b |                            |  |  |  |

| bit 2<br>Note 1: (<br>2:  | SLEEP: Wal<br>1 = Device h<br>0 = Device h<br>IDLE: Wake<br>1 = Device h<br>0 = Device h<br>Only those bits<br><i>"PIC24F Family</i>                                                                                             | ake from Sleep<br>has been in Sl<br>has not been i<br>e-up from Idle<br>has been in Id<br>has not been i<br>s relevant to th<br><i>ly Reference M</i><br>P and IDLE bit | o Flag bit <sup>(2)</sup><br>leep mode<br>in Sleep mode<br>Flag bit <sup>(2)</sup><br>lle mode<br>in Idle mode<br>ne power-saving fe<br><i>Manual</i> " for a comp | eatures are de<br>plete descripti | escribed here.<br>tion of the RCC | ON register b |                            |  |  |  |

| U-0                                | U-0   | U-0 U-0      |                                         | U-0 U-0                                      |        | U-0                    | U-0                 |  |  |  |  |

|------------------------------------|-------|--------------|-----------------------------------------|----------------------------------------------|--------|------------------------|---------------------|--|--|--|--|

| _                                  | —     |              |                                         | _                                            | —      | —                      | _                   |  |  |  |  |

| bit 15                             |       |              |                                         | ·                                            |        |                        | bit 8               |  |  |  |  |

|                                    |       |              |                                         |                                              |        |                        |                     |  |  |  |  |

| U-0                                | U-0   | U-0          | r-0                                     | R/CO-1                                       | R/CO-1 | R/CO-1                 | R/CO-0              |  |  |  |  |

| _                                  |       |              | r                                       | VDDBOR <sup>(1)</sup> VDDPOR <sup>(1,2</sup> |        | VBPOR <sup>(1,3)</sup> | VBAT <sup>(1)</sup> |  |  |  |  |

| bit 7                              |       |              | ·                                       | ·                                            |        |                        | bit 0               |  |  |  |  |

|                                    |       |              |                                         |                                              |        |                        |                     |  |  |  |  |

| Legend:                            |       | r = Reserved |                                         | CO = Clearable Only bit                      |        |                        |                     |  |  |  |  |

| R = Readable                       | e bit | W = Writable | bit                                     | U = Unimplemented bit, read as '0'           |        |                        |                     |  |  |  |  |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |                                              |        |                        |                     |  |  |  |  |

| Register 57-2: RCON2: Reset and System Control Register 2 |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| bit 15-5 | Unimplemented: Read as '0'                                                                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4    | Reserved: Maintain as '0'                                                                                                                                                                                           |

| bit 3    | VDDBOR: VDD Brown-out Reset Flag bit <sup>(1)</sup>                                                                                                                                                                 |

|          | <ul> <li>1 = A VDD Brown-out Reset has occurred (set by hardware)</li> <li>0 = A VDD Brown-out Reset has not occurred</li> </ul>                                                                                    |

| bit 2    | VDDPOR: VDD Power-on Reset Flag bit <sup>(1,2)</sup>                                                                                                                                                                |

|          | <ul><li>1 = A VDD Power-up Reset has occurred (set by hardware)</li><li>0 = A VDD Power-up Reset has not occurred</li></ul>                                                                                         |

| bit 1    | VBPOR: Wake from Sleep Flag bit <sup>(1,3)</sup>                                                                                                                                                                    |

|          | <ul> <li>1 = A VBAT POR has occurred (no battery is connected to the VBAT pin or VBAT power is below the Deep Sleep Semaphore retention level, set by hardware)</li> <li>0 = A VBAT POR has not occurred</li> </ul> |

| bit 0    | VBAT: VBAT Flag bit <sup>(1)</sup>                                                                                                                                                                                  |

|          | <ul> <li>1 = A POR exit has occurred while power was applied to the VBAT pin (set by hardware)</li> <li>0 = A POR exit from VBAT has not occurred</li> </ul>                                                        |

## **Note 1:** This bit is set in hardware only; it can only be cleared in software.

- 2: Indicates a VDD POR. Setting the POR bit (RCON<0>) indicates a VCORE POR.

- 3: This bit is set when the device is originally powered up, even if power is present on VBAT.

| Register :                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57-3: DSC                                                                                                                                                                                                                               | ON: Deep Slee                          | p Control Re     | gister                            |               |                           |                          |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-----------------------------------|---------------|---------------------------|--------------------------|--|--|--|

| R/W-0, H                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C U-0                                                                                                                                                                                                                                   | U-0                                    | U-0              | U-0                               | U-0           | U-0                       | U-0                      |  |  |  |

| DSEN <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                       | —                                      | _                | —                                 | —             | —                         | —                        |  |  |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                         | · · · · · ·                            |                  |                                   |               |                           | bit 8                    |  |  |  |

| U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                     | U-0                                    | U-0              | U-0                               | U-0           | R/W-0, HCS <sup>(2)</sup> | R/W-0, HS <sup>(2)</sup> |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DSBOR REI                                                                                                                                                                                                                               |                                        |                  |                                   |               |                           |                          |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                       |                                        |                  |                                   | I             |                           | bit 0                    |  |  |  |

| Legend:       HC = Hardware Clearable bit       HS = Hardware Settable bit       HCS = Hardware Clearable/Settable         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                        |                  |                                   |               |                           |                          |  |  |  |

| -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                         | '1' = Bit is set                       | it.              | $0^{\circ} = \text{Bit is clear}$ |               | x = Bit is unknown        |                          |  |  |  |

| <ul> <li>1 = Deep Sleep mode is entered on a SLEEP command</li> <li>0 = Sleep mode is entered on a SLEEP command</li> <li>bit 14-2</li> <li>Unimplemented: Read as '0'</li> <li>DSBOR: Deep Sleep BOR Event Status bit<sup>(2)</sup></li> <li>1 = DSBOREN was enabled and VDD dropped below the DSBOR threshold during Deep Sleep<sup>(3)</sup></li> <li>0 = DSBOREN was disabled, or VDD did not drop below the DSBOR threshold during Deep Sleep</li> </ul> |                                                                                                                                                                                                                                         |                                        |                  |                                   |               |                           |                          |  |  |  |

| bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>RELEASE:</b> I/O Pin State Release bit <sup>(2,4)</sup><br>1 = Upon waking from Deep Sleep, the I/O pins maintain their previous states<br>0 = Release I/O pins and allow their respective TRIS and LAT bits to control their states |                                        |                  |                                   |               |                           |                          |  |  |  |

| Note 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         | enter Deep Slee<br>be consecutive      |                  | t be written to                   | in two separa | te operations. The w      | rite operations do       |  |  |  |