# MICROCOMPUTER

#### 8 Bit Microcomputer

#### **FEATURES**

- User programmable

- Intelligent controller for stand-alone applications

- 32 8-bit RAM registers

- 512 x 12-bit program ROM

- Arithmetic Logic Unit

- Real Time Clock/Counter

- Self-contained crystal oscillator

- Access to RAM registers inherent in instruction

- Wide power supply operating range (4.5V to 7.0V)

- Available in two temperature ranges: 0° to 70° C and −40° to

- 4 sets of 8 user defined TTL-compatible Input/Output lines

- 2 level stack for subroutine nesting

#### DESCRIPTION

The PIC1650XT microcomputer is an MOS/LSI device containing RAM, I/O, and a central processing unit as well as customer-defined ROM on a single chip. This combination produces a low cost solution for applications which require sensing individual inputs and controlling individual outputs. Keyboard scanning, display driving, and other system control functions can be done at the same time due to the power of the 8-bit CPU.

The internal ROM contains a customer-defined program using the PIC's powerful instruction set to specify the overall functional characteristics of the device. The 8-bit input/output registers provide latched lines for interfacing to a limitless variety of applications. The PIC can be used to scan keyboards, drive displays, control electronic games and provide enhanced capabilities to vending machines, traffic lights, radios, television, consumer appliances, industrial timing and control applications. The 12-bit instruction word format provides a powerful yet easy to use

instruction repertoire emphasizing single bit manipulation as well as logical and arithmetic operations using bytes.

The PIC1650XT is fabricated with N-Channel Ion Implant technology resulting in a high performance product with proven reliability and production history. Only a single wide range power supply is required for operation, and an on-chip oscillator provides the operating clock with an external crystal, ceramic resonator or LC network to establish the frequency. Inputs and outputs are TTL-compatible.

Extensive hardware and software support is available to aid the user in developing an application program and to verify performance before committing to mask tooling. Programs can be assembled into machine language using PICAL, eliminating the burden of coding with ones and zeros. PICAL is available in a Fortran IV version that can be run on many popular computer systems. Once the application program is developed several options are available to insure proper performance. The PIC's operation can be verified in any hardware application by using the PIC1664. The PIC1664 is a ROM-less PIC microcomputer with additional pins to connect external PROM or RAM and to accept HALT commands. The PFD1000 Field Demo System is available containing a PIC1664 with sockets for erasable CMOS PROMs. Finally, the PICES II (PIC In-Circuit Emulation System) provides the user with emulation and debugging capability in either a stand-alone mode or operation as a peripheral to a larger computer system. Easy program debugging and changing is facilitated because the user's program is stored in RAM. With these development tools, the user can quickly and confidently order the masking of the PIC's ROM and bring his application into the market.

A PIC Series Microcomputer Data Manual is available which gives additional detailed data on PIC based system design.

PIC1650XT

GENERAL INSTRUMENT

#### **ARCHITECTURAL DESCRIPTION**

The firmware architecture of the PIC series microcomputer is based on a register file concept with simple yet powerful commands designed to emphasize bit, byte, and register transfer operations. The instruction set also supports computing functions as well as these control and interface functions.

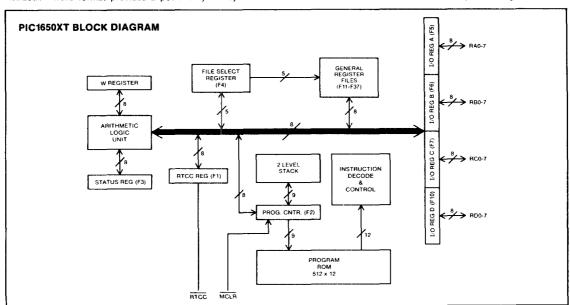

Internally, the PIC is composed of three functional elements connected together by a single bidirectional bus: the Register File composed of 32 addressable 8-bit registers, an Arithmetic Logic Unit, and a user-defined Program ROM composed of 512 words each 12 bits in width. The Register File is divided into two functional groups: operational registers and general registers. The operational registers include, among others, the Real Time Clock Counter Register, the Program Counter (PC), the Status Register,

and the I/O Registers. The general purpose registers are used for data and control information under command of the instructions.

The Arithmetic Logic Unit contains one temporary working register or accumulator (W Register) and gating to perform Boolean functions between data held in the working register and any file register.

The Program ROM contains the operational program for the rest of the logic within the controller. Sequencing of microinstructions is controlled via the Program Counter (PC) which automatically increments to execute in-line programs. Program control operations can be performed by Bit Test and Skip instructions, Jump instructions, Call instructions, or by loading computed addresses into the PC. In addition, an on-chip two-level stack is employed to provide easy to use subroutine nesting. Activating the MCLR input on power up initializes the ROM program to address 7778.

#### **PIN FUNCTIONS**

| Signal                                       | Function                                                                                                                                                                                                                                                                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1 (input), OSC2 (output)                  | Oscillator pins. The oscillator frequency can be set by a crystal ceramic resonator, external LC network or driven externally. The oscillator frequency is sixteen times the instruction frequency.                                                                     |

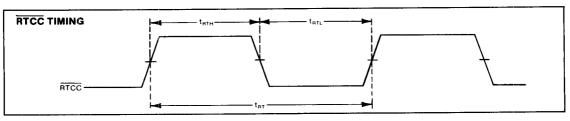

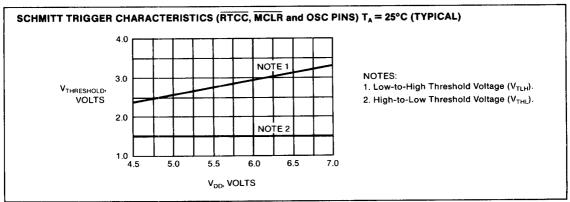

| RTCC (input)                                 | Real Time Clock Counter. Used by the microprogram to keep track of elapsed time between events. The RTCC register increments on falling edges applied to this pin. This register can be loaded and read by the program. This is a Schmitt trigger input.                |

| RA0-7, RB0-7, RC0-7, RD0-7<br>(input/output) | User programmable input/output lines. These lines can be inputs and/or outputs and are under direct control of the program.                                                                                                                                             |

| MCLR (input)                                 | Master Clear. Used to initialize the internal ROM program to address 777 <sub>8</sub> and latch all I/O register high. Should be held low at least 1-10ms past the time when the power supply is valid for the oscillator to start up. This is a Schmitt trigger input. |

| CLK OUT (output)                             | A signal derived from the internal oscillator. Used by external devices to synchronize them-<br>selves to PIC timing.                                                                                                                                                   |

| V <sub>DD</sub>                              | Primary power supply.                                                                                                                                                                                                                                                   |

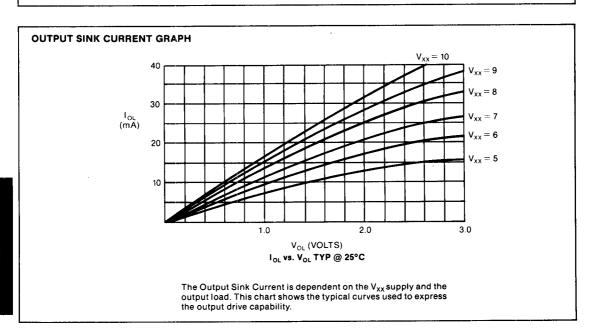

| V <sub>xx</sub>                              | Output Buffer power. Used to enhance output current sinking capability.                                                                                                                                                                                                 |

| V <sub>ss</sub>                              | Ground                                                                                                                                                                                                                                                                  |

| PIN CONFIGURATION 40 LEAD DUAL IN LINE |                         |

|----------------------------------------|-------------------------|

| 40 LEAD DOAL IN LINE                   |                         |

| Top                                    | /iew                    |

| > V <sub>ss</sub> □•1                  | 40 □ V <sub>xx</sub> ←— |

| ←→ RA0 🗖 2                             | 39 🗖 V <sub>DD</sub> ←— |

| ←→ RA1 🗖 3                             | 38 □ OSC2>              |

| ←→ RA2 🗖 4                             | 37 □ OSC1 ←             |

| —→ RTCC <b>□</b> 5                     | 36 ☐ CLKOUT>            |

| → RA3 <b>□</b> 6                       | 35 ☐ MCLR ←—            |

| ←→ RA4 <b>□</b> 7                      | 34 ☐ RD7 ←→             |

| ←→ RA5 □ 8                             | 33 D RD6 ←→             |

| ←→ RA6 🗆 9                             | 32 ☐ RD5 ←→             |

| ←→ RA7 ☐ 10                            | 31 □ RD4 ←→             |

| <→ RB0 □ 11                            | 30 □ RD3 ←→             |

| ←→ RB1 ☐ 12                            | 29 D RD2 ←→             |

| ←→ RB2 □ 13                            | 28 ☐ RD1 ←→             |

| ←→ RB3 □ 14                            | 27 □ RD0 ←→             |

| ←→ RB4 □ 15                            | 26 □ RC7 ←→             |

| ←→ RB5 ☐ 16                            | 25 ☐ RC6 ←→             |

| ←→ RB6 ☐ 17                            | 24 ☐ RC5 ←→             |

| ←→ RB7 ☐ 18                            | 23 □ RC4 ←→             |

| ←→ RC0 ☐ 19                            | 22 ☐ RC3 ←→             |

| ←→ RC1 □ 20                            | 21 □ RC2 ←→             |

# MICROCOMPUTE

#### REGISTER FILE ARRANGEMENT

| File<br>(Octal) |                                |                                                                                  |                              |                                | Function                           |                                 |                              |                                  |                                    |

|-----------------|--------------------------------|----------------------------------------------------------------------------------|------------------------------|--------------------------------|------------------------------------|---------------------------------|------------------------------|----------------------------------|------------------------------------|

| F0              | select a file re               | ally implemented<br>egister. F0 is thus<br>led to by the FSR                     | useful as an                 | indirect addi                  | ess pointer.                       | he File Select<br>For example,  | Register (lo<br>W+F0W wi     | w order 5 bits<br>Il add the con | ) to be used t<br>tents of the fil |

| F1              | counting up a<br>stored in the | ock Counter Reg<br>after zero is reach<br>RTCC register sin<br>alue and the exte | ed. The cour<br>multaneously | iter incremer<br>y with a nega | nts on the fall<br>ative transitio | ing edge of th<br>on on the RTC | e input RTC<br>C pin, the R1 | 5. However, if                   | data are being                     |

| F2              | program con                    | inter (PC). The Pitrol (MOVWF F2).                                               | The PC is n                  | ine bits wide                  | , but only its                     | low order 8 b                   | its can be re                | ad under pro                     | gram control.                      |

| F3              | Status Word                    | Register. F3 can l                                                               | e altered un                 | der program                    | control only                       | via bit set, bi                 | t clear, or M                | OVWF F3 inst                     | ruction.                           |

|                 |                                | (7)                                                                              | (6)                          | (5)                            | (4)                                | (3)                             | (2)                          | (1)                              | (0)                                |

|                 | -                              | 1                                                                                | 1                            | 1                              | 1                                  | 1                               | z                            | DC                               | С                                  |

|                 | C (Carry):                     | resultant.                                                                       |                              |                                |                                    | nere is a carry                 |                              |                                  |                                    |

|                 | DC (Digit Ca                   | rry): For ADD and                                                                | SUB instruc                  | tions, this bit                | is set if there                    | is a carry out                  | from the 4th                 | ow order bit o                   | of the resultan                    |

|                 | Z (Zero):                      | Set if the res                                                                   | ult of an arith              | nmetic opera                   | tion is zero.                      |                                 |                              |                                  |                                    |

|                 | Bits: 3-7                      | These bits as                                                                    | e defined as                 | logic ones.                    |                                    |                                 |                              |                                  |                                    |

| F4              |                                | egister (FSR). Lo<br>am control. Whe                                             |                              |                                |                                    |                                 |                              |                                  |                                    |

| F5              | I/O Register                   | A (A0-A7)                                                                        |                              |                                |                                    |                                 |                              |                                  |                                    |

|                 |                                |                                                                                  |                              |                                |                                    |                                 |                              |                                  |                                    |

| F6              | I/O Register                   | B (B0-B7)                                                                        |                              |                                |                                    |                                 |                              |                                  |                                    |

| F6<br>F7        | I/O Register I/O Register      |                                                                                  |                              |                                |                                    |                                 |                              |                                  |                                    |

|                 | 1                              | C (C0-C7)                                                                        |                              |                                |                                    |                                 |                              |                                  |                                    |

The PIC1650XT has the same basic architecture as the PIC1650A with the additional enhancement described below:

#### **Self-Contained Oscillator**

When a crystal, ceramic resonator or LC network is connected between the OSC1 and OSC2 pins, the self-contained oscillator will generate a frequency determined by the external components thus allowing an accurate timing reference, a crystal, to be used for time base control with a minimum of external parts.

The output of this oscillator is divided down by 16 to give the instruction cycle time of the microcomputer, thus with a 4MHz crystal the instruction cycle time is  $4\mu$ s.

When test mode is enabled, the basic instruction cycle time is a division of 4 of the frequency applied to OSC1 and OSC2 allowing simpler synchronizing of the device and tester.

None

## PIC1650XT INSTRUMENT

### **Basic Instruction Set Summary**

Each PIC instruction is a 12-bit word divided into an OP code which specifies the instruction type and one or more operands which further specify the operation of the instruction. The following PIC instruction summary lists byte-oriented, bit-oriented, and literal and control operations.

For byte-oriented instructions, "f" represents a file register designator and "d" represents a destination designator. The file register designator specifies which one of the 32 PIC file registers is to be utilized by the instruction. The destination designator specifies where the result of the operation performed by the instruction is to be placed. If "d" is zero, the result is placed in the

PIC W register. If "d" is one, the result is returned to the file register specified in the instruction.

For bit-oriented instructions, "b" represents a bit field designator which selects the number of the bit affected by the operation, while "f" represents the number of the file in which the bit is located

For literal and control operations, "k" represents an eight or nine bit constant or literal value.

For an oscillator frequency of 4MHz the instruction execution time is 4  $\mu$ sec, unless a conditional test is true or the program counter is changed as a result of an instruction. In these two cases, the instruction execution time is 8  $\mu$ sec.

#### BYTE-ORIENTED FILE REGISTER OPERATIONS

| (11-6)  | (5) | (4-0)      |

|---------|-----|------------|

| OP CODE | d   | f (FILE #) |

For d = 0, f - W (PICAL accepts d = 0 or d = W in the mnemonic) d = 1, f - f (If d is omitted, assembler assigns d = 1.)

| Inst   | ructio | n-Bina | ıry (Oc | ıtal)  | Name                      | Mnemonic, O | )perands | Operation                   | Status Affected |

|--------|--------|--------|---------|--------|---------------------------|-------------|----------|-----------------------------|-----------------|

| 000    | 000    | 000    | 000     | (0000) | No Operation              | NOP         |          | -                           | None            |

|        |        |        | fff     | (,     | Move W to f (Note 1)      | MOVWF       | f        | W→f                         | None            |

| 000    | 001    | 000    | 000     | (0100) | Clear W                   | CLRW        | _        | o→W                         | Z               |

| 000    | 001    | 1 f f  | fff     | (0140) | Clear f                   | CLRF        | f        | 0→f                         | Z               |

| 000    | 010    | dff    | fff     | , ,    | Subtract W from f         | SUBWF       | f, d     | f - W→d [f+W+1→d]           | C,DC,Z          |

| 000    | 011    | dff    | fff     |        | Decrement f               | DECF        | f, d     | f - 1→d                     | Z               |

| 000    | 100    | dff    | fff     | (0400) | Inclusive OR W and f      | IORWF       | f, d     | W∨f→d                       | Z               |

| 000    | 101    | dff    | fff     |        | AND W and f               | ANDWF       | f, d     | W∙f⊸d                       | Z               |

| 000    | 110    | aff    | fff     | (0600) | Exclusive OR W and f      | XORWF       | f, d     | W⊕fd                        | Z               |

| 000    | 111    | dff    | f f f   | (0700) | Add W and f               | ADDWF       | f, d     | W+f <b>→</b> d              | C,DC,Z          |

| 001    | 000    | dff    | 1 f f   | (1000) | Move f                    | MOVF        | f, d     | <u>f</u> d                  | Z               |

| 001    | 001    | dff    | fff     | (1100) | Complement f              | COMF        | f, d     | <del>Ī</del> ⊸d             | Z               |

| 001    | 010    | dff    | fff     | (1200) | Increment f               | INCF        | f, d     | f+1⊶d                       | Z               |

| 001    | 011    | dff    | fff     | (1300) | Decrement f, Skip if Zero | DECFSZ      | f, d     | f - 1→d, skip if Zero       | None            |

| 001    | 100    | dff    | fff     | (1400) | Rotate Right f            | RRF         | f, d     | f(n)→d(n-1), f(0)→C, C→d(7) |                 |

| 001    | 101    |        | fff     | (1500) | Rotate Left f             | RLF         | f, d     | f(n)-d(n+1), f(7)-C, C-d(0  | 0) C            |

| 001    | 110    |        | fff     | /      | Swap halves f             | SWAPF       | f, d     | f(0-3)≒f(4-7)→d             | None            |

| 001    | 111    | dff    | fff     | (1700) | Increment f, Skip if Zero | INCFSZ      | f, d     | f+1-d, skip if zero         | None            |

| BIT-O  |        |        |         |        | (11-8)                    | (7-5)       | (4-0)    |                             |                 |

| FILE P |        |        |         |        | OP CODE b (               | (BIT #)     | f (FILE  | #)                          |                 |

| OPERATIONS                 |                          | <u>`</u>  | _ <u>·</u> | _ <u></u>                    |                 |

|----------------------------|--------------------------|-----------|------------|------------------------------|-----------------|

| Instruction-Binary (Octal) | Name                     | Mnemonic, | Operands   | Operation                    | Status Affected |

| 010 0bb bff fff (2000)     | Bit Clear f              | BCF       | f, b       | 0→f(b)                       | None            |

| 010 1bb bff fff (2400)     | Bit Set f                | BSF       | f, b       | 1→f(b)                       | None            |

| 011 055 544 444 (2000)     | Bit Toot f Skip if Clear | DTESC     | f h        | Bit Test f(h): skin if clear | None            |

**BTFSS**

f, b

Bit Test f(b): skip is set

## LITERAL AND CONTROL OPERATIONS (11-8) (7-0) k (LITERAL)

Bit Test f, Skip if Set

| Inst | ructio | n-Bina | ry (Oc | tal)   | Name                          | Mnemonic, ( | Operands | Operation            | Status Affected |

|------|--------|--------|--------|--------|-------------------------------|-------------|----------|----------------------|-----------------|

| 100  | 0 k k  | kkk    | kkk    | (4000) | Return and place Literal in V | V RETLW     | k        | k→W, Stack→PC        | None            |

| 100  | 1 k k  | kkk    | kkk    | (4400) | Call subroutine (Note 1)      | CALL        | k        | PC+1 → Stack, k → PC | None            |

| 101  | kkk    | kkk    | kkk    | (5000) | Go To address (k is 9 bits)   | GOTO        | k        | k→PC                 | None            |

| 110  | 0 k k  | kkk    | kkk    | (6000) | Move Literal to W             | MOVLW       | k        | k→W                  | None            |

| 110  | 1 k k  | kkk    | kkk    | (6400) | Inclusive OR Literal and W    | IORLW       | k        | kVW-+W               | Z               |

| 111  | Okk    | kkk    | kkk    | (7000) | AND Literal and W             | ANDLW       | k        | k•W→W                | Z               |

|      |        |        |        | (7400) | Exclusive OR Literal and W    | XORLW       | k        | k⊕W→W                | Z               |

#### NOTES

- 1. The 9th bit of the program counter in the PIC is zero for a CALL and a MOVWF F2. Therefore, subroutines must be located in program memory locations 0-377<sub>8</sub>. However, subroutines can be called from anywhere in the program memory since the Stack is 9 bits wide.

- 2. When an I/O register is modified as a function of itself, the value used will be that value present on the output pins. For example, an output pin which has been latched high but is driven low by an external device, will be relatched in the low state.

- 3. See notes on input only and output only ports.

011 1bb bff fff (3400)

#### SUPPLEMENTAL INSTRUCTION SET SUMMARY

The following supplemental instructions summarized below represent specific applications of the basic PIC instructions. For example, the "CLEAR CARRY" supplemental instruction is equiv-

alent to the basic instruction BCF 3,0 ("Bit Clear, File 3, Bit 0"). These instruction mnemonics are recognized by the PIC Cross Assembler (PICAL).

| Instruction-Binary (Octa              | l) Name                                 | Mnemonic,<br>Operands | Equivalent<br>Operation(s) | Status<br>Affected |

|---------------------------------------|-----------------------------------------|-----------------------|----------------------------|--------------------|

| 010 000 000 011                       | 2003) Clear Carry                       | CLRC                  | BCF 3, 0                   | _                  |

| 010 100 000 011                       | 2403) Set Carry                         | SETC                  | BSF 3, 0                   | _                  |

| 010 000 100 011                       | 2043) Clear Digit Carry                 | CLRDC                 | BCF 3, 1                   | _                  |

| 010 100 100 011                       | 2443) Set Digit Carry                   | SETDC                 | BSF 3, 1                   | _                  |

| 010 001 000 011                       | 2103) Clear Zero                        | CLRZ                  | BCF 3, 2                   | -                  |

| 010 101 000 011                       | 2503) Set Zero                          | SETZ                  | BSF 3, 2                   | _                  |

| 011 100 000 011                       | 3403) Skip on Carry                     | SKPC                  | BTFSS 3, 0                 | _                  |

| 011 000 000 011                       | 3003) Skip on No Carry                  | SKPNC                 | BTFSC 3, 0                 | _                  |

| 011 100 100 011                       | 3443) Skip on Digit Carry               | SKPDC                 | BTFSS 3, 1                 | _                  |

| 011 000 100 011                       | 3043) Skip on No Digit Carry            | SKPNDC                | BTFSC 3, 1                 | _                  |

| 011 101 000 011                       | 3503) Skip on Zero                      | SKPZ                  | BTFSS 3, 2                 | _                  |

| 011 001 000 011                       | 3103) Skip on No Zero                   | SKPNZ                 | BTFSC 3, 2                 | _                  |

| 001 000 1ff fff                       | 1040) Test File                         | TSTF f                | MOVF f, 1                  | Z                  |

| 001 000 Off fff                       | 1000) Move File to W                    | MOVFW f               | MOVF f, 0                  | Z                  |

|                                       | 1140) Negate File<br>1200)              | NEGF f,d              | COMF f, 1<br>INCF f, d     | z                  |

|                                       | 3003) Add Carry to File<br>1200)        | ADDCF f, d            | BTFSC 3,0<br>INCF f, d     | z                  |

|                                       | 3003) Subtract Carry from File<br>0300) | SUBCF f,d             | BTFSC 3,0<br>DECF f, d     | z                  |

|                                       | 3043) Add Digit Carry to File           | ADDDCF f,d            | BTFSG 3,1<br>INCF f,d      | Z                  |

|                                       | 3043) Subtract Digit Carry from File    | SUBDCF f,d            | BTFSC 3,1<br>DECF f,d      | z                  |

| 101 kkk kkk kkk                       | 5000) Branch                            | Bk                    | GОТО к                     |                    |

|                                       | 3003) Branch on Carry<br>5000)          | BC k                  | BTFSC 3,0<br>GOTO k        | _                  |

|                                       | 3403) Branch on No Carry<br>5000)       | BNC k                 | BTFSS 3,0<br>GOTO k        | _                  |

| · · · · · · · · · · · · · · · · · · · | 3043) Branch on Digit Carry<br>5000)    | BDC k                 | BTFSC 3,1<br>GOTO k        | _                  |

|                                       | 3443) Branch on No Digit Carry<br>5000) | BNDC k                | BTFSS 3,1<br>GOTO k        |                    |

|                                       | 3103) Branch on Zero<br>5000)           | BZ k                  | BTFSC 3,2<br>GOTO k        | -                  |

| · · · · · · · · · · · · · · · · · · · | 3503) Branch on No Zero<br>5000)        | BNZ k                 | BTFSS 3,2<br>GOTO k        | _                  |

### I/O Interfacing

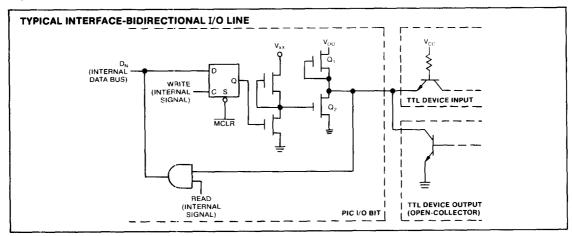

The equivalent circuit for an I/O port bit is shown below as it would interface with either the input of a TTL device (PIC is outputting) or the output of an open collector TTL device (PIC is inputting). Each I/O port bit can be individually time multiplexed between input and output functions under software control. When outputting thru a PIC I/O Port, the data is latched at the port and the pin

can be connected directly to a TTL gate input. When inputting data thru an I/O Port, the port latch must first be set to a high level under program control. This turns off  $Q_2$ , allowing the TTL open collector device to drive the pad, pulled up by  $Q_1$ , which can source a minimum of  $100\mu A$ . Care, however, should be exercised when using open collector devices due to the potentially high TTL leakage current which can exist in the high logic state.

### **Programming Cautions**

The use of the bidirectional I/O ports are subject to certain rules of operation. These rules must be carefully followed in the instruction sequences written for I/O operation.

#### **Bidirectional I/O Ports**

The bidirectional ports may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction. The outputs are latched and remain unchanged until the output latch is rewritten. For use as an input port the output latch must be set in the high state. Thus the external device inputs to the PIC circuit by forcing the latched output line to the low state or keeping the latched output high. This principle is the same whether operating on individual bits or the entire port.

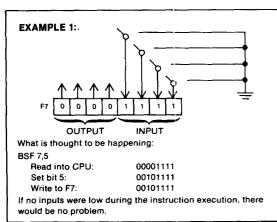

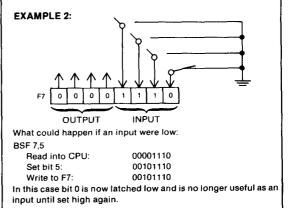

Some instructions operate internally as input followed by output operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation, and re-output the result. Caution must be used when using these instructions.

As an example a BSF operation on bit 5 of F7 (port RC) will cause all eight bits of F7 to be read into the CPU. Then the BSF operation takes place on bit 5 and F7 is re-output to the output latches. If another bit of F7 is used as an input (say bit 0) then bit 0 must be latched high. If during the BSF instruction on bit 5 an external device is forcing bit 0 to the low state then the input/output nature of the BSF instruction will leave bit 0 latched low after execution. In this state bit 0 cannot be used as an input until it is again latched high by the programmer. Refer to the examples below.

#### Successive Operations on Bidirectional I/O Ports

| GENERAL<br>INSTRUMENT | PIC1650XT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. 431 KOIVIE AT      | ł control of the cont |

#### **ELECTRICAL CHARACTERISTICS**

|         | 7       | r |

|---------|---------|---|

| Maximum | Ratings |   |

|         |         |   |

| Ambient Temperature Under Bias                                 |

|----------------------------------------------------------------|

| Storage Temperature                                            |

| Voltage on any Pin with Respect to V <sub>SS</sub>             |

| (except Open Drain)0.3V to +10.0V                              |

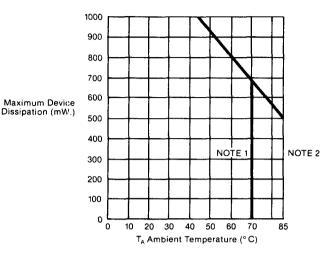

| Power Dissipation (Note 1) 800mW                               |

| Voltage on any Pin with Respect to Voc (Open Drain)0.3 to +10V |

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### Standard Conditions (unless otherwise stated):

#### **DC CHARACTERISTICS**

Operating Temperature  $T_A = 0$ °C to -70°C

| Characteristics                                  | Sym              | Min                | Тур† | Max             | Units | Conditions                                            |

|--------------------------------------------------|------------------|--------------------|------|-----------------|-------|-------------------------------------------------------|

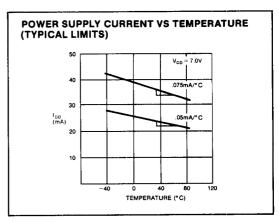

| Primary Supply Voltage                           | V <sub>DD</sub>  | 4.5                | _    | 7.0             | ٧     |                                                       |

| Supply Current                                   | I <sub>DD</sub>  | _                  |      | 55              | mA    | All I/O pins @ V <sub>DD</sub>                        |

| nput Low Voltage                                 | V <sub>IL</sub>  | -0.2               | _    | 0.8             | ٧     |                                                       |

| nput High Voltage (except<br>MCLR, RTCC & OSC1)  | V <sub>IH1</sub> | 2.4                |      | V <sub>DD</sub> | v     |                                                       |

| nput High Voltage (OSC1)                         | V <sub>IH2</sub> | V <sub>DD</sub> -1 | _    | V <sub>DD</sub> | ٧     |                                                       |

| nput Low-to-High Threshold Voltage (MCLR & RTCC) | VILH             | V <sub>DD</sub> -1 | 2.6  | V <sub>DD</sub> | v     |                                                       |

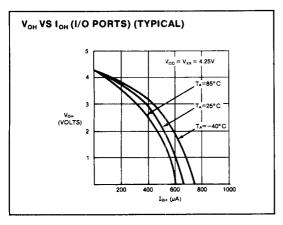

| Output High Voltage                              | V <sub>OH</sub>  | 2.4<br>3.5         | _    | V <sub>DD</sub> | V     | $I_{OH} = -100\mu A \text{ (Note 2)}$<br>$I_{OH} = 0$ |

| Output Low Voltage (I/O only)                    | V <sub>OL1</sub> | _                  | _    | 0.45            | V     | I <sub>OL</sub> = 1.6mA, (Note 3)                     |

| put Leakage Current (MCLR, RTCC)                 | I <sub>LC</sub>  | -5                 | _    | +5              | μΑ    | $V_{SS} \leqslant V_{IN} \leqslant V_{DD}$            |

| nput Low Current (all I/O ports)                 | I <sub>IL</sub>  | -0.2               | _    | -2.0            | mA    | V <sub>IL</sub> = 0.4V (internal pullup)              |

| nput High Current (all I/O ports)                | I <sub>IH</sub>  | -0.1               | -0.4 | -1.6            | mA    | V <sub>IH</sub> = 2.4V                                |

| utput Leakage Current<br>(open drain I/O pins)   | loLC             |                    | -    | 10              | μΑ    | 0V ≤ V <sub>PIN</sub> ≤ 10V                           |

<sup>&</sup>lt;sup>†</sup>Typical data is at  $T_A = 25^{\circ} \, \text{C}$ ,  $V_{DD} = 5.0 \, \text{V}$ .

#### NOTES:

- 1. Total power dissipation for the package is calculated as follows:

- $P_{D} = (V_{DD}) (I_{DD}) + \sum (V_{DD} V_{IL}) (|I_{IL}|) + \sum (V_{DD} V_{OH}) (|I_{OH}|) + \sum (V_{OL}) (|I_{OL}|).$

- 2. Positive current indicates current into pin. Negative current indicates current out of pin.

- 3. Total I<sub>OL</sub> for all output pins must not exceed 175mA.

#### Standard Conditions (unless otherwise stated):

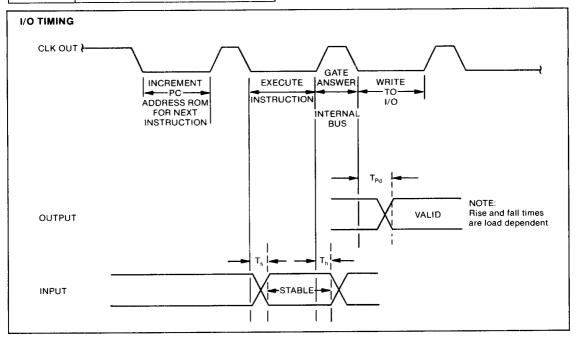

#### **AC CHARACTERISTICS**

Operating Temperature T<sub>A</sub> = 0°C to +70°C

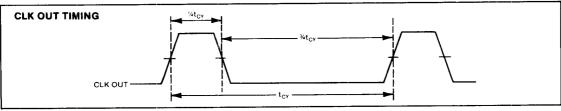

| Characteristic                | Sym              | Min                    | Тур† | Max                     | Units    | Conditions                                  |

|-------------------------------|------------------|------------------------|------|-------------------------|----------|---------------------------------------------|

| Instruction Cycle Time        | toy              | 4                      | _    | 20                      | μs       | 0.2MHz — 1.0MHz external time base (Note 1) |

| RTCC Input                    |                  |                        |      |                         | <u> </u> |                                             |

| Period                        | t <sub>AT</sub>  | t <sub>CY</sub> +0.2µs |      | -                       |          |                                             |

| High Pulse Width              | t <sub>RTH</sub> | ½t <sub>RT</sub>       | _    | -                       | –        |                                             |

| Low Pulse Width               | tATL             | ½t <sub>RT</sub>       | _    |                         | -        | (Notes 2 and 4)                             |

| I/O Ports                     |                  |                        |      |                         |          |                                             |

| Data Input Setup Time         | ts               | -                      | _    | 1/4t <sub>CY</sub> -125 | ns       |                                             |

| Data Input Hold Time          | t <sub>h</sub>   | 0                      | _    | -                       | ns       |                                             |

| Data Output Propagation Delay | tpd              | -                      | 500  | 900                     | ns       | Capacitive load = 50pF                      |

<sup>†</sup>Typical data is at  $T_A = 25^{\circ}$  C,  $V_{DD} = 5.0$ V.

- 1. Instruction cycle period ( $t_{CY}$ ) equals four times the input oscillator time base period.

- 2. Due to the synchronous timing nature between CLK OUT and the sampling circuit used on the RTCC input, CLK OUT may be directly tied to the RTCC input.

- 3. If an RTCC prescaler division ratio of 2, 4, 8 or 16 is selected, the maximum rise and fall times of the signal input to the RTCC pin is 200 nsecs and its duty cycle must be between 40% and 60%.

- 4. The maximum frequency which may be input to the  $\overline{RTCC}$  pin is calculated as follows:  $f_{(max)} = \frac{1}{t_{RT\ (min)}} = \frac{1}{t_{CY\ (min)} + 0.2\mu s}$  For example:

$$f_{(max)} = \frac{1}{f_{--}} = \frac{1}{f_{--}}$$

if

$$t_{CY} = 4\mu s$$

,  $f_{(max)} = \frac{1}{4.2\mu s} = 238 \text{KHz}$ .

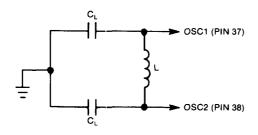

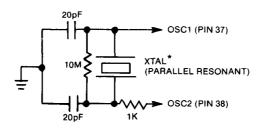

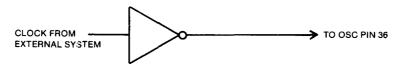

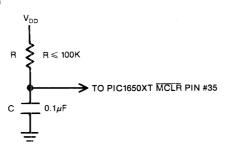

#### PIC1650XT OSCILLATOR OPTIONS (TYPICAL CIRCUITS)

#### LC INPUT OPERATION

$$f_{OSC} \approx \frac{1}{2\pi \sqrt{L (C_L + C_{INT})}},$$

where  $C_{INT} = 10$ pF.

#### **CRYSTAL INPUT OPERATION**

\* or ceramic resonator

#### **EXTERNAL CLOCK INPUT OPERATION**

#### MASTER CLEAR (TYPICAL CIRCUIT)

Master Clear requires 10ms delay (assuming a 4MHz crystal) before activation after power is applied to the  $V_{DD}$  pin, for the crystal to start up. To achieve this, an external RC configuration as shown can be used (assuming  $V_{DD}$  is applied as a step function).

#### **POWER DISSIPATION DERATING GRAPH**

#### NOTES:

- 1.70°C is the maximum operating temperature for standard parts.

- 2.85°C is the maximum operating temperature for "I" suffix parts.

#### PIC1650XT EMULATION CAUTIONS

When emulating a PIC1650XT using a PICES II development system certain precautions should be taken.

- A. Be sure that the PICES II Module being used is programmed for the PIC1650XT mode. (Refer to PICES II Manual). The PIC1664 contained within the module should have the MODE pin #22 set to a high state.

- 1. This causes the MCLR to force all I/O registers high.

- 2. The interrupt system becomes disabled and the RTCC always counts on the trailing edges.

- 3. Bits 3 through 7 on file register F3 are all ones.

- B. Make sure to only use two levels of stack within the program.

- C. Make sure all I/O cautions contained in this spec sheet are used.

- D. Be sure to use the 40 pin socket for the module plug.

- E. Make sure that during an actual application the  $\overline{MCLR}$  input swings from a low to high level a minimum of 10msec after the supply voltage is applied to allow for the crystal to start up.

- F. The cable length and internal variations may cause some parameter values to differ between the PICES II module and a production PIC1650XT.

- G. The emulator PFD board or PICES II module offers only "internal" oscillator operation (i.e. the crystal is on the PFD or module board), as the long cable might cause unreliable crystal operation.