# An I<sup>2</sup>C<sup>TM</sup> Network Protocol for Environmental Monitoring

Authors: Stephen Bowling, Richard L. Fischer Microchip Technology Incorporated

### INTRODUCTION

Communication network systems are rapidly growing in size and complexity. These systems have many high speed integrated circuits with critical operating parameters and must provide extremely reliable service with zero down time. To maintain the performance of these systems, adequate environmental monitoring must be performed, so a failure or a data trend leading to a potential failure can be rapidly identified. Furthermore, this monitoring must be performed cheaply to keep system costs low.

To minimize system down time and increase flexibility, these communication network systems feature modular, hot-swappable components. Each component in the system typically contains multiple sub-systems that require monitoring. These sub-systems might include DC/DC regulators, high speed microprocessors, FPGAs, and cooling fans. Some of the monitored system parameters include power supply output voltage, power supply current, device temperature, ambient temperature, and fan speed.

A network is required so all sensor data is collected and fed to a central computer for monitoring and analysis. Because many of the sensors are located in close proximity to each other, the  $I^2C$  bus offers a solution that can be implemented with minimal hardware cost. Furthermore, low cost microcontrollers (MCUs) with a wide range of peripherals and an  $I^2C$  interface are widely available.

For the I<sup>2</sup>C bus to be an effective solution for networked environmental sensors, a suitable bus protocol is required that prevents system bus errors from affecting sensor data. The purpose of this application note is to define such a network protocol, which may be easily adapted to most any networked application. The bus protocol must be immune to adverse network conditions, such as hot-swapping, or a malfunctioning network node.

# THE I<sup>2</sup>C BUS SPECIFICATION

Although a complete discussion of the  $I^2C$  bus specification is outside the scope of this application note, some of the basics will be covered here. For more information on the  $I^2C$  bus specification, refer to sources indicated in the *References* section on page 15. A *Glossary of Terms* is also located on page 15.

The Inter-Integrated Circuit, or I<sup>2</sup>C bus specification, was originally developed by Philips Semiconductors for the transfer of data between ICs at the PCB level. The physical interface for the bus consists of two open drain lines; one for the clock (SCL) and one for data (SDA). The SDA and SCL lines are pulled high by resistors connected to the VDD rail. The bus may have a one master/many slave configuration or may have multiple master devices. The master device is responsible for generating the clock source for the linked slave devices.

The I<sup>2</sup>C protocol supports either a 7-bit addressing mode, or a 10-bit addressing mode, permitting 128 or 1024 physical devices to be on the bus, respectively. In practice, the bus specification reserves certain addresses so slightly fewer usable addresses are available. For example, the 7-bit addressing mode allows 112 usable addresses.

All data transfers on the bus are initiated by the master device and are done eight bits at a time, MSb first. There is no limit to the amount of data that can be sent in one transfer.

The I<sup>2</sup>C protocol includes a handshaking mechanism. After each 8-bit transfer, a 9th clock pulse is sent by the master. At this time, the transmitting device on the bus releases the SDA line and the receiving device on the bus acknowledges the data sent by the transmitting device. An ACK (SDA held low) is sent if the data was received successfully, or a NACK (SDA left high) is sent if it was not received successfully. A NACK is also used to terminate a data transfer after the last byte is received.

According to the  $l^2C$  specification, all changes on the SDA line must occur while the SCL line is low. This restriction allows two unique conditions to be detected on the bus; a START sequence (**S**) and a STOP sequence (**P**). A START sequence occurs when the master device pulls the SDA line low, while the SCL line is high. The START sequence tells all slave devices on the bus that address bytes are about to be sent. The STOP sequence occurs when the SDA line goes high, while the SCL line is high and it terminates the transmission. Slave devices on the bus should reset their receive logic after the STOP sequence has been detected.

The  $l^2C$  protocol also permits a Repeated START condition (**Rs**), which allows the master device to execute a START sequence without preceding it with a STOP sequence. Repeated START is useful, for example, when the master device changes from a write operation to a read operation and does not release control of the bus.

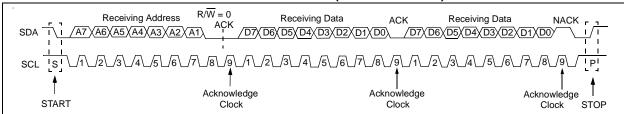

A typical I<sup>2</sup>C write transmission would proceed as shown in Figure 1. In this example, the master device will write two bytes to a slave device. The transmission is started when the master initiates a START condition on the bus. Next, the master sends an address byte to the slave. The upper seven bits of the address byte contain the slave address. The LSb of the address byte specifies whether the I<sup>2</sup>C operation will be a read (LSb = 1), or a write (LSb = 0). On the ninth clock pulse, the master releases the SDA line so the slave can acknowledge the reception. If the address byte was received by the slave and was the correct address, the slave responds with an ACK by holding the SDA line low. Assuming an ACK was received, the master sends out the data bytes. On the ninth clock pulse after each data byte, the slave responds with an ACK. After the last data byte, a NACK is sent by the slave to the master to indicate that no more bytes should be sent. After the NACK pulse, the master initiates the STOP condition to free the bus.

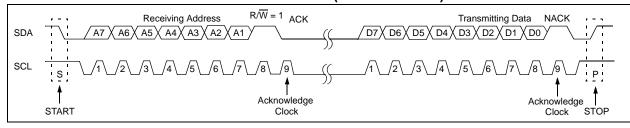

A read operation is performed similar to the write operation and is shown in Figure 2. In this case, the R/W bit in the address byte is set to indicate a read operation. After the address byte is received, the slave device sends an ACK pulse and holds the SCL line low. By holding the SCL line, the slave can take as much time as needed to prepare the data to be sent back to the master. When the slave is ready, it releases SCL and the master device clocks the data from the slave buffer. On the ninth clock pulse, the slave releases the SDA line and latches the value of the ACK bit received from the master. If an ACK pulse was received, the slave must prepare the next byte of data to be transmitted. If a NACK was received, the data transmission is complete. In this case, the slave resets its  $I^2C$  receive logic and waits for the next START condition.

For many I<sup>2</sup>C peripherals, such as non-volatile EEPROM memory, an I<sup>2</sup>C write operation and a read operation are done in succession. For example, the write operation specifies the address to be read and the read operation gets the byte of data. Since the master device does not release the bus after the memory address is written to the device, a Repeated START sequence is performed to read the contents of the memory address.

# **DEFINING NETWORK PROTOCOL**

Now that the basics of the I<sup>2</sup>C bus have been covered, let's examine the needs of the sensor network. In this system, a single master device is on the bus and will periodically initiate communications with slave devices. The protocol must allow the master device to read or write data from a particular slave device. The type and length of data read from, or written to, the slave will depend, of course, on the specific function of the slave. For this reason, it would be efficient for the network protocol to support a variable data length dependent on the sensor node. The protocol should also allow a data address to be specified. Using a data address and data length, the master node can request any or all of the data available from the slave node.

There must be a method in the network protocol to ensure that data was transmitted or received successfully. Using checksums, the master and slave devices in the system verify that the data received was valid. If the data is not valid, the data should be retransmitted. Furthermore, the network protocol must handle bus errors gracefully. The sources of error include glitches due to hot-swapping, multiple devices responding to the same address (bus collisions), and no-response conditions from devices on the bus.

#### FIGURE 1: TYPICAL I<sup>2</sup>C WRITE TRANSMISSION (7-BIT ADDRESS)

### FIGURE 2: TYPICAL I<sup>2</sup>C READ TRANSMISSION (7-BIT ADDRESS)

#### **Master Device Message Formats**

Since all communication on the  $I^2C$  bus is initiated by the master device, a description of the protocol implemented by the master is required. In this application, the master device may initiate one of two message types; a *data write* message, or a *data request* message.

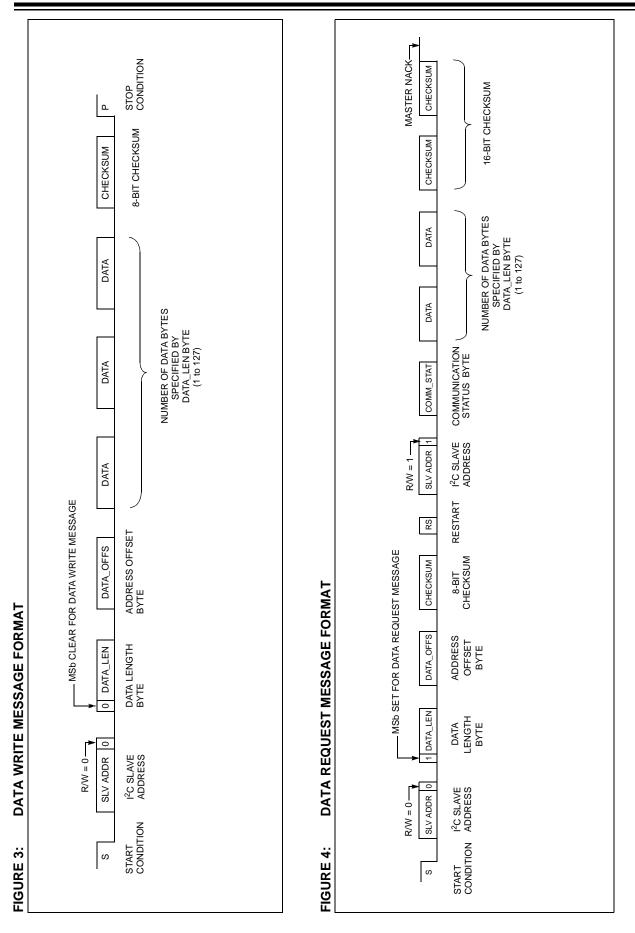

#### Data Write Message Format

The format for a data write message is shown in Figure 3. The data write message begins with the master initiating a START condition. When the START condition completes, the master device sends the  $l^2C$  address of the slave node with the R/W bit cleared to indicate data will be written to the slave device.

The next byte sent provides the byte count information. For this discussion, this byte will be referred to as the DATA\_LEN byte. The DATA\_LEN byte serves two purposes. First, the lower seven LSb's indicate the number of data bytes to be written to the slave device. Second, the MSb indicates whether data will be written to, or read from the slave. In this case, the MSb is cleared to indicate that a data write will be performed. The MSb of the DATA\_LEN byte performs a similar function for the network protocol as the R/W bit in the I<sup>2</sup>C address byte, but the two should not be confused.

The next byte sent by the master indicates the starting address in the slave node data buffer that will be written to, or read from. This byte will be referred to as the DATA\_OFFS byte. Each slave device on the network maintains a range of data memory for received data and data to be transmitted. In a data write message, the number of data bytes specified by the DATA\_LEN byte will follow the DATA\_OFFS byte. When the last byte of data has been sent, the master sends an 8-bit, two's complement checksum of all data previously sent, including the I<sup>2</sup>C slave node address byte. Finally, the master device terminates the data write message by initiating a STOP condition.

#### Data Request Message Format

The format for a data request message is shown in Figure 4. Following the START condition, the master device sends the address of the slave node with the R/W bit cleared to indicate a data write to the l<sup>2</sup>C slave device. Next, the DATA\_LEN byte is sent. The seven LSb's of this byte indicate the number of data bytes to be read from the slave. Because a data read from the slave should be performed, the MSb is set. The DATA\_OFFS byte follows the data length byte and indicates the starting address in the slave node data memory from which data will be read. Next, the master device sends an 8-bit, two's complement checksum of the slave address, data length byte, and data offset byte that were sent in the data request message.

#### Slave Node Message Processing

In general, the master device may read data from the slave after a data write or data request message, by initiating a Restart condition on the I<sup>2</sup>C bus and sending the slave address with the R/W bit set. The type of message that was previously sent by the master and its validity determines what data will be returned by the slave.

Each slave node maintains several status bits to indicate the validity of messages sent by the master device. These status bits are stored in the communication status (COMM\_STAT) byte and Table 1 indicates the significance of each bit.

The COMM\_STAT byte is always the first data byte to be returned in any data transfer from the slave node to the master node. This allows the master to verify that the previously sent message was processed correctly by the slave node. If, for example, the master sent a data write message, the value of the COMM\_STAT byte would be 00h, if the data was successfully received by the slave. If a data request message was previously sent by the master, the value of the COMM\_STAT byte would be 80h. If the master receives any other values for the COMM\_STAT byte, some type of error has occurred and the master should send the data write or data request message again.

If a data write message was previously sent to the slave node, the master does not need to receive any more bytes from the slave node, after the COMM\_STAT byte is read. For a data request message, the master should read number of data bytes specified by DATA\_LEN.

A two's complement, 16-bit checksum is calculated for the data returned to the master. The checksum value includes the COMM\_STAT byte, plus all data bytes that were returned. The master device should receive the two checksum bytes after the data bytes. If the master determines that a checksum error occurred while receiving the data bytes, it should try to read the data from the slave again.

#### TABLE 1: COMM\_STAT BIT DEFINITIONS

| Bit                                                                                                          | Bit Name          | Description                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit 0                                                                                                        | comm_stat.chkfail | Indicates a checksum<br>failure occurred for the last<br>message sent.                                                                                                                            |  |  |

| Bit 1                                                                                                        | comm_stat.rxerror | Indicates the slave node<br>did not interpret the last<br>master message correctly.                                                                                                               |  |  |

| Bit 2                                                                                                        | comm_stat.ovflw   | Indicates the master<br>device has requested to<br>read/write one or more<br>bytes of data from the<br>slave node, outside the<br>valid range of addresses<br>for that particular slave.          |  |  |

| Bit 3                                                                                                        | comm_stat.sspov   | Indicates an overflow has<br>occurred in the SSP<br>module for a given slave<br>address, because the<br>slave device was not able<br>to process incoming I <sup>2</sup> C<br>data quickly enough. |  |  |

| Bit 4                                                                                                        |                   | Unused                                                                                                                                                                                            |  |  |

| Bit 5                                                                                                        |                   | Unused                                                                                                                                                                                            |  |  |

| Bit 6                                                                                                        |                   | Unused                                                                                                                                                                                            |  |  |

| Bit 7                                                                                                        | comm_stat.r_w     | Indicates whether the last message from the master was a data request message ( $R/W = 1$ ), or a data write message ( $R/W = 0$ ).                                                               |  |  |

| Note: The bit structure 'comm_stat' is used in the<br>C source code to access bits in the<br>COMM_STAT byte. |                   |                                                                                                                                                                                                   |  |  |

# PUTTING IT ALL TOGETHER

Now that the basic implementation of the network protocol is defined, the functional operation of the master and slave controllers is presented.

#### The Master Node

#### General Overview

For this application, a PICmicro<sup>®</sup> PIC16F873 is implemented as the Master I<sup>2</sup>C bus controller. This 28-pin FLASH based PICmicro device provides both the MSSP and USART modules for I<sup>2</sup>C and USART communications, respectively.

The firmware code for this application is written in C, using the Hi-Tech PIC C Compiler<sup>TM</sup> and is included in Appendix B. Table 2 provides a brief description of the system files.

In addition to these C source files, some generic assembly  $I^2C$  master read and write routines were developed and are included in Appendix E. Table 3 provides a brief description of these files.

In this application, the master performs three basic tasks:

- 1. I<sup>2</sup>C slave reads.

- 2. I<sup>2</sup>C slave writes.

- 3. Transmission of received I<sup>2</sup>C slave data and bus status to the PC.

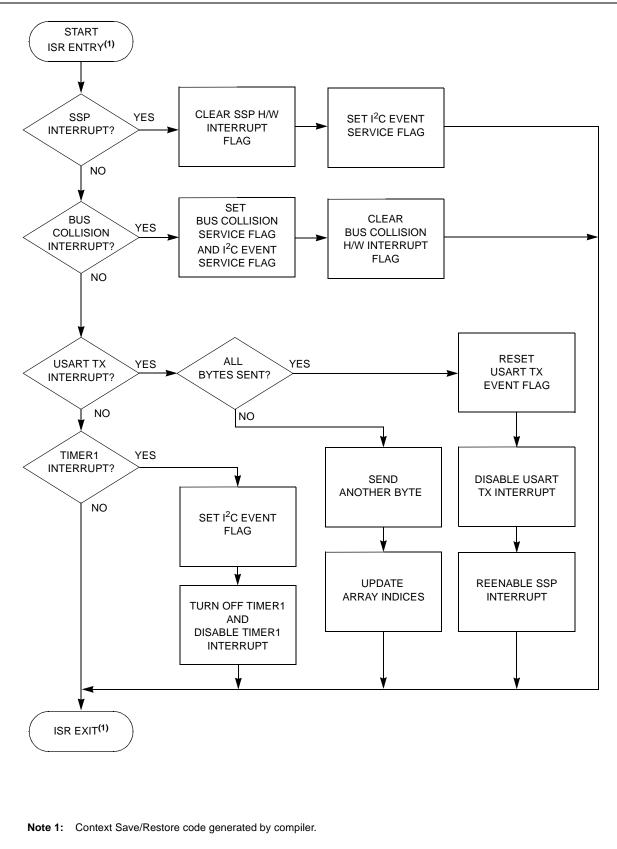

For the most part, these tasks occur on an interrupt basis.

There are four types of interrupts that are implemented:

- I<sup>2</sup>C Event Completion Interrupt. This I<sup>2</sup>C event interrupt indicates that an I<sup>2</sup>C event has completed. I<sup>2</sup>C events include START, STOP, Restart, Acknowledge, Read and Write. The hardware peripheral SSPIF bit (PIR1<6>) is asserted upon an event completion.

- 2. Bus Collision Interrupt. This interrupt is used for handling the detection of a bus collision. Typically, in a single master system (as described in this application), a bus collision is unlikely.

- Timer1 Overflow Interrupt. This interrupt is used to generate a 100 ms time tick for initiating I<sup>2</sup>C communications. When the master completes a current round of I<sup>2</sup>C communications, Timer1 is restarted. When Timer1 overflows (100 ms later), the next round of I<sup>2</sup>C communications begins.

- 4. USART Transmission Interrupt. This interrupt is used to send out 10 data bytes to the PC. After the master communicates with each slave device, a data packet is composed. The packet consists of the data read from the slave and the I<sup>2</sup>C bus status. Each byte is transmitted to the PC on an interrupt basis at 19200 baud.

For the Master I<sup>2</sup>C implementation, the MSSP module on the PICmicro MCU is used. The functional operation of this module is not covered within this document. For more information, consult AN735, "Using the PICmicro<sup>®</sup> MSSP Module for Master I<sup>2</sup>C<sup>™</sup> Communications", or refer to the specific PICmicro data sheet.

| File Name  | Description                                                           |  |  |

|------------|-----------------------------------------------------------------------|--|--|

| mstri2c.c  | Main code loop and interrupt control functions.                       |  |  |

| mstri2c.h  | Variable declarations & definitions.                                  |  |  |

| i2c_comm.c | Routines for communicating with the I <sup>2</sup> C slave device(s). |  |  |

| i2c_comm.h | Variable declarations & definitions.                                  |  |  |

| init.c     | Routines for initializing the PICmicro peripherals and ports.         |  |  |

| cnfig87x.h | Configuration bit definitions for the PICmicro PIC16F87X.             |  |  |

| pic.h      | Required by compiler for SFR declarations (Hi-Tech file).             |  |  |

| delay.h    | Delay function prototypes (Hi-Tech file).                             |  |  |

#### TABLE 2:MASTER I<sup>2</sup>C 'C' SOURCE CODE FILES

# TABLE 3: MASTER I<sup>2</sup>C 'ASM' SOURCE CODE FILES

| File Name    | Description                                                                 |  |  |

|--------------|-----------------------------------------------------------------------------|--|--|

| mastri2c.asm | Main code loop and interrupt control functions.                             |  |  |

| mastri2c.inc | Variable declarations & definitions.                                        |  |  |

| i2ccomm1.inc | Reference linkage for variables used in i2ccomm.asm file.                   |  |  |

| i2ccomm.asm  | Routines for communicating with the I <sup>2</sup> C slave device.          |  |  |

| i2ccomm.inc  | Variable declarations & definitions.                                        |  |  |

| flags.inc    | Common flag definitions used within the mastri2c.asm and i2ccomm.asm files. |  |  |

| init.asm     | Routines for initializing the PICmicro peripherals and ports.               |  |  |

| p16f873.inc  | PICmicro SFR definition file.                                               |  |  |

| 16f873.lkr   | Modified linker script file.                                                |  |  |

#### Master Implementation

The master device, upon completion of the internal power-up cycle, performs some basic peripheral and key variable initialization. The functions used for peripheral initialization are listed:

- Init\_Usart()

- Init\_Ports()

- Init\_Timer1()

- Init\_Ssp()

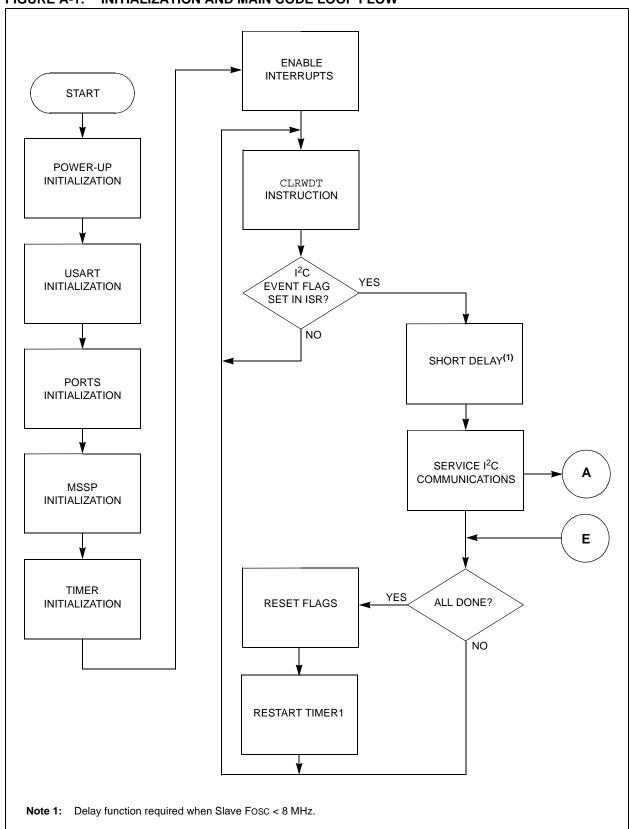

These functions are located within the <code>init.c</code> file. Within the <code>Init\_Ssp()</code> function, the MSSP module is initialized for Master I<sup>2</sup>C mode, 400 kHz baud rate and slew rate is enabled. Once the peripheral initialization is completed, peripheral and global interrupts are enabled and the main code execution loop is entered (see Figure A-1).

In the main loop, the application firmware (F/W) tests the state of two flags:

- sflag.event.read\_i2c

- sflag.event.i2c\_event

These flags are initially asserted high in the Timer1 Interrupt Service Routine (ISR). The Timer1 interrupt starts the  $I^2C$  communication process and repeats every 100 ms. In the Timer1 ISR, the timer is shut off, the respective interrupt is disabled and the referenced event flags are set (see Figure A-2):

When the main loop program execution resumes, the F/W tests the state of these two flags. If both are a logic '1', the function Service\_I2CSlave() is called. If one or both of the flags are negated (logic '0'), a loop comprised of a CLRWDT instruction and the flag test process repeats.

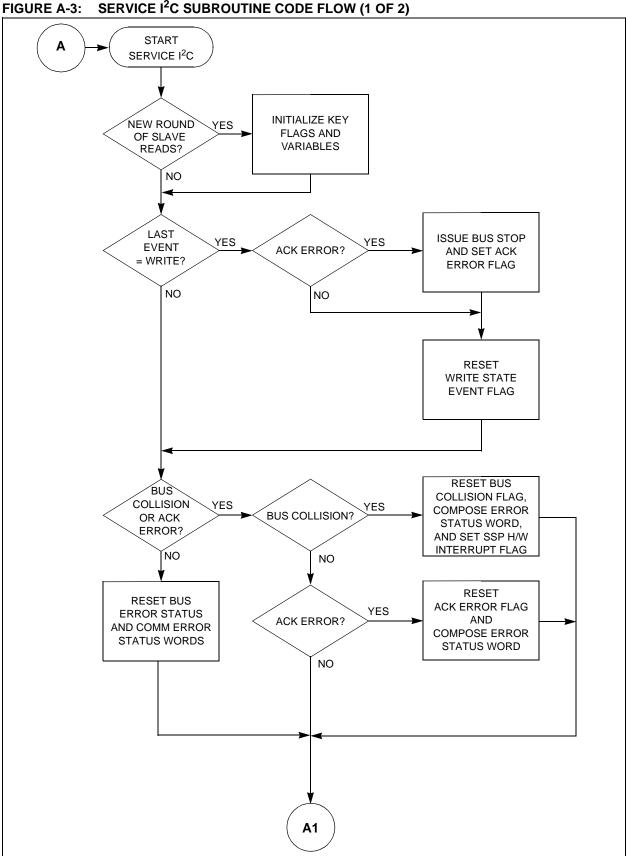

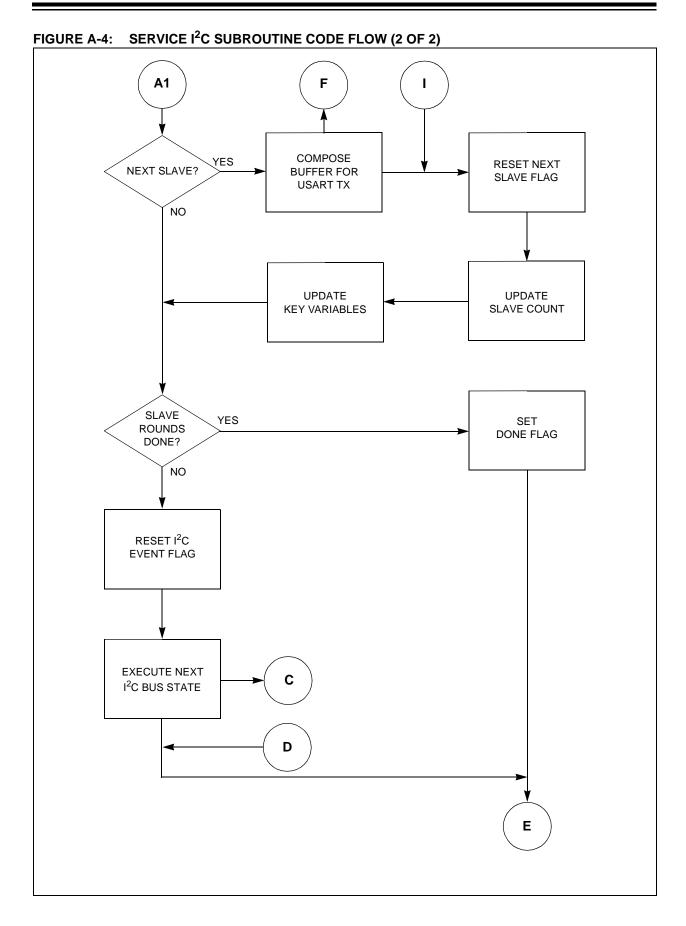

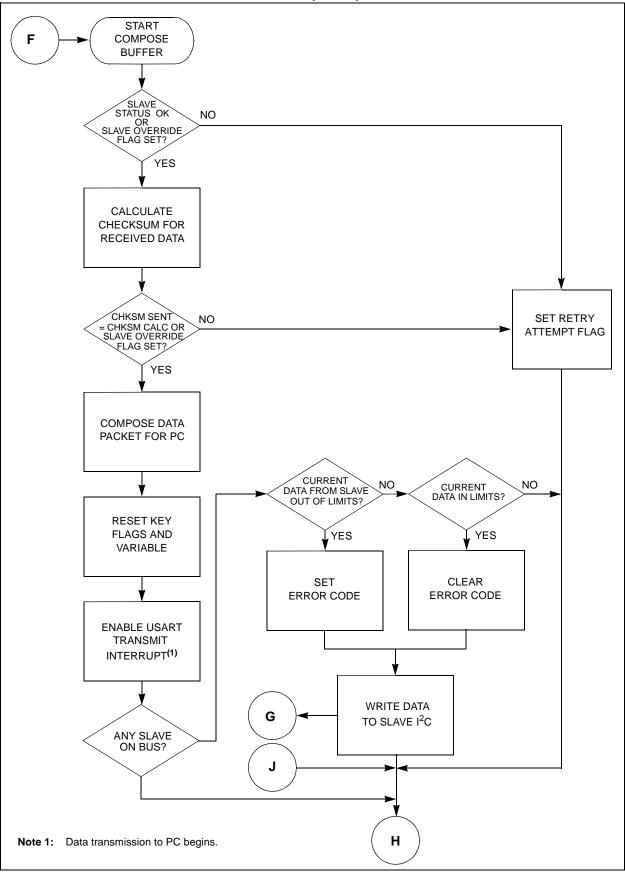

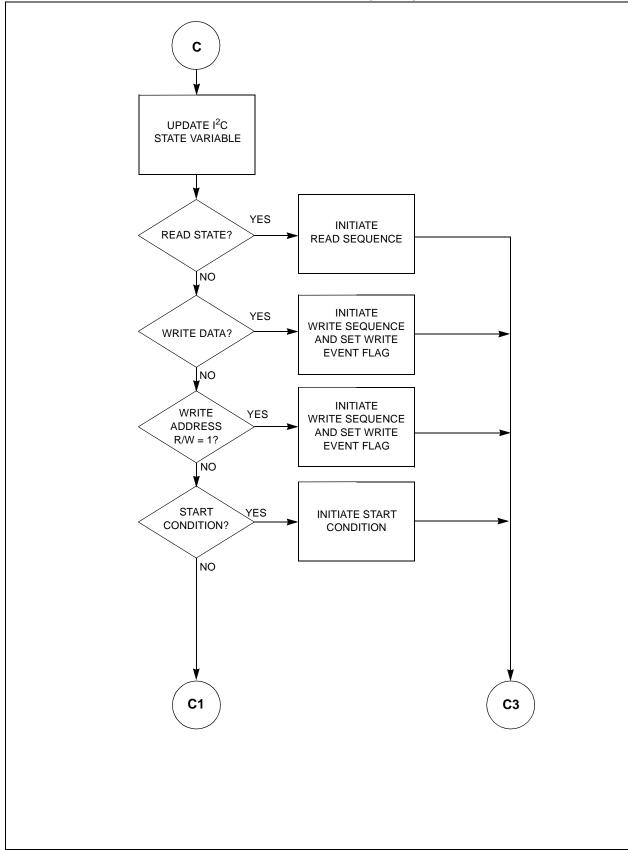

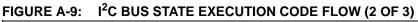

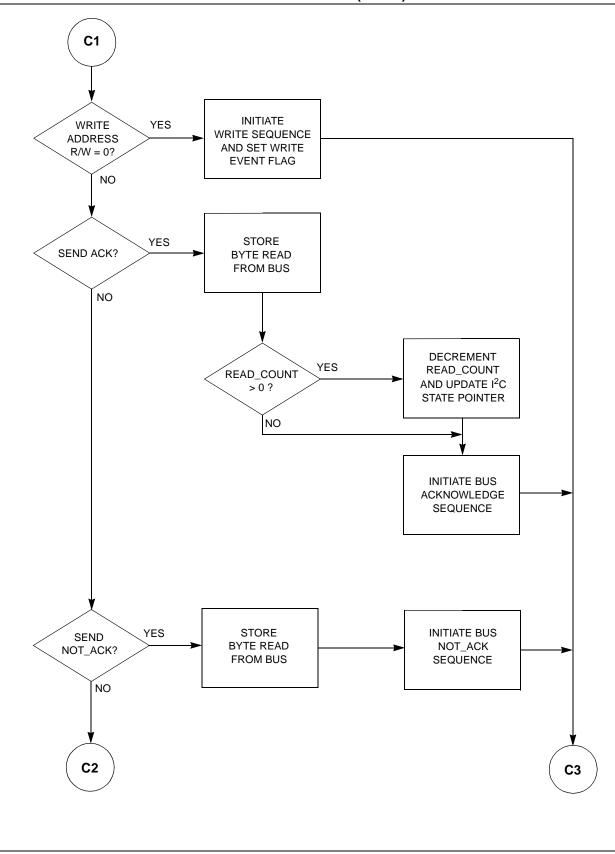

When the Service\_I2CSlave() function is called, several operational code states are tested and executed, if true (see Figure A-3 through Figure A-4):

- Test if a new round of slave communications is to start. If so, initialize key variables and flags. This test is true every Timer1 rollover event.

- Test if the previous I<sup>2</sup>C bus state was an I<sup>2</sup>C write state. If so, test for Acknowledge error. If error exists, then issue bus STOP condition.

- Test if there was a I<sup>2</sup>C bus or Acknowledge error. If true, compose error status for transmission to PC. If false, clear same error status.

- Test if the I<sup>2</sup>C master should communicate with the next slave device. If true, then perform the following:

- Initialize key variables and flags.

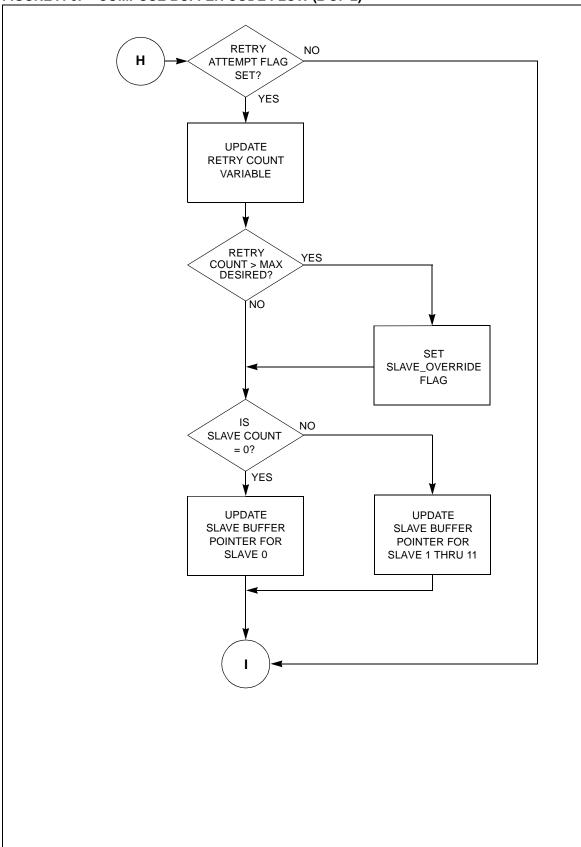

- Call Compose\_Buffer() function. In this function, a test is made to determine if the data packet read from the slave is valid. If valid, start transmission of data packet to PC. If invalid, perform an I<sup>2</sup>C communication retry with same slave (see Figure A-5 and Figure A-6).

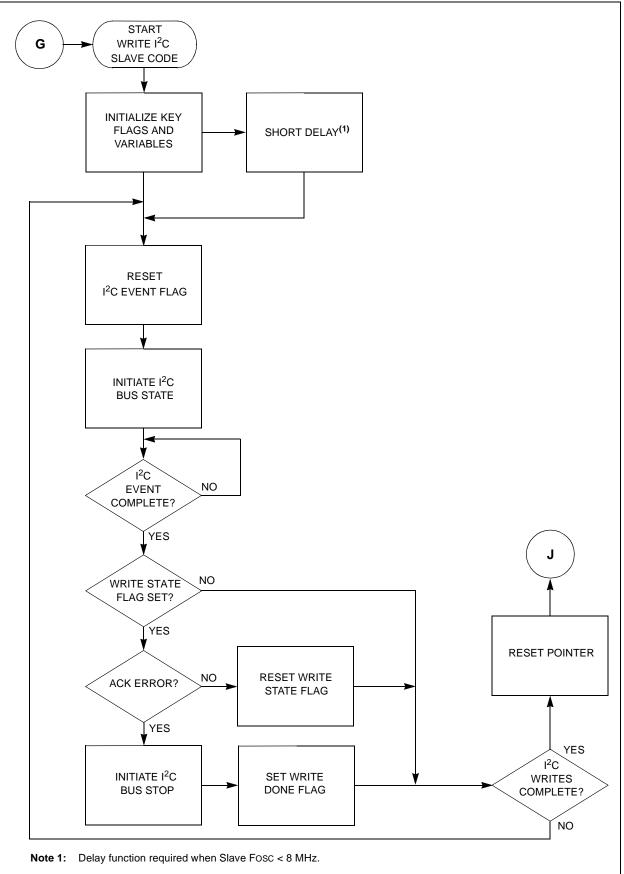

- Test if a single data value received from the slave is out of range. Perform I<sup>2</sup>C master write to the slave (see Figure A-7). The range limit test value is set by the #define limit 0x80 macro (see the i2c\_comm.c file).

- Test if the master has communicated with all slave devices. If true, return to the main code loop and wait for the next 100 ms time tick to expire. If false, initiate the next I<sup>2</sup>C bus state, which may be a START, STOP, Restart, Read, Write, Send ACK or Send NACK (see Figure A-8, Figure A-9, and Figure A-10).

As mentioned, each new round of  $I^2C$  communications starts 100 ms from the completion of the previous round. This cycle is somewhat arbitrary, since the slave data is not used other than for display on a PC, and a data collection rate of 100 ms is adequate for this application. The  $I^2C$  communication cycle with each slave takes approximately 5 ms. Following this, 10 bytes are transmitted to the PC at 19200 baud, which equates to approximately 5.3 ms. The data is transmitted to the PC on an interrupt basis within the interrupt function, interrupt\_piv() located in the mastri2c.c file.

In this application, the master I<sup>2</sup>C device communicates with twelve slave devices. It is possible to increase the number of slaves, but PICmicro resources must be considered. For example, a slave device, upon request, may transmit up to 127 data bytes to the master. The data read from the slave must fit into contiguous memory, since an array variable is used to hold the data. This may, or may not be possible, based on the total master I<sup>2</sup>C device resource requirements. In addition, a RAM array variable is defined and initialized with a data length byte, address offset byte, and 8-bit checksum for each slave (see Figure 4 for the message format). For twelve slaves, the array size totals 36 bytes. One can see that the size of the array depends on the number of slaves. Although this array is placed in RAM, it could have been placed in program memory, but then a dynamic update to the array would not be possible.

In short, this application may be modified to allow for more slave I<sup>2</sup>C devices with minor code changes, but additional PICmicro resources may be required.

During each slave communication cycle, the master reads slave data and status while monitoring and recording errors, such as bus collision and Acknowledge errors (NACK). While bus collisions are more typical in a 'multi-master' environment, a bus collision may still occur in a single master system. For example, a slave device may experience a malfunction (firmware and/or hardware), and as a result, the SDA and SCL bus levels are driven low during a transmission. The later error condition may result in a permanent bus fault until corrective action is taken. In any case, the master I<sup>2</sup>C device should monitor for this condition and take the appropriate action. When a bus collision is detected, a status bit will be set to a logic '1' for that particular slave. When the bus collision error is corrected, the same status bit will be set to a logic zero. This status information is part of the data packet sent to the PC. In addition, the master will attempt at least one I<sup>2</sup>C communication retry. Additional retries are attempted by changing the substitution text in the macro defined in file i2c\_comm.h. For example, one communication retry is implemented for:

#define MaxSlaveRetry 1

Two communication retries are made for:

#### #define MaxSlaveRetry 2

Another error condition the master I<sup>2</sup>C device should monitor for is the Not Acknowledge (NACK) condition. If, for any reason, the slave issues a Not Acknowledge (does not drive SDA low during the ninth clock pulse of a write), the master should detect this and take the appropriate action. As with the bus collision error, a status bit will be asserted according to the error state. For this condition, the master issues a STOP condition after detecting a NACK. This action differs from the bus collision, in that as a result of a bus collision, the MSSP module goes into an IDLE state. The next valid I<sup>2</sup>C state should be a START condition. As a result of a NACK condition, the module does not go into an IDLE state. An I<sup>2</sup>C bus Restart or STOP/START combination should be executed, depending on the desired action.

For this application, (see Figure 4) the master reads five bytes of information from each slave, three bytes of data, and two bytes for the checksum. The data, along with the slave ID, bus and communication error status is transmitted to the PC for display. While the USART transmission is in progress, the master may also execute an I<sup>2</sup>C write sequence to the slave. The write sequence is automatic per each slave, but the data written depends on the value of the second byte read from the slave. The Write I2CSlave() function performs this write sequence and is called from within the Compose Buffer() function. This write sequence is concurrent with the USART communications. For this application, the Write I2CSlave() function provides the slave I<sup>2</sup>C device with a response from the master, based upon the limit evaluation of this second byte (see Figure A-7). This function executes as a control loop using the I<sup>2</sup>C event completion interrupt.

Finally, for each I<sup>2</sup>C communication state with a slave, excluding the Write I2CSlave() function, the master generates each  $I^2C$  bus state within the I2CBusState() function. This function is based upon switch/case control statements. Upon entering this function, the F/W performs a table lookup for the next I<sup>2</sup>C state. The states for each sequence are predefined in the const unsigned char arrav. ReadFSlaveI2CStates declared in the file i2c comm.h. This implementation allows simple addition or deletion of I<sup>2</sup>C bus states. When the next I<sup>2</sup>C state has been obtained, a switch statement evaluates the state variable i2cstate and the correct case statement initiates the next bus state. The F/W then returns to the main code loop and waits for the next I<sup>2</sup>C event completion interrupt.

#### The Slave Node

The slave node firmware is provided in Appendix D and was written for a PIC16C72A device using the Hi-Tech PICC compiler. The PIC16C72A device was chosen for the sensor node, because it is a low cost device that has the SSP module required for  $I^2C$  communications. The slave firmware contains the following primary C functions:

- Setup()

- ISR\_Handler()

- SSP\_Handler()

- AD\_Handler()

- CCP2\_Handler()

The Setup() function initializes all of the Special Function Registers (SFR) in the PIC16C72A and all of the program variables.

#### Interrupts

The slave node firmware is primarily interrupt-driven. The SSP module, CCP2 module, and A/D module are the sources of interrupts. The ISR\_Handler() function polls the interrupt flag bits and calls the appropriate module handler function.

#### Event Timing

The CCP2 module is used in the Compare mode as an event timer for the firmware and provides an interrupt every 1 msec. The CCP2\_Handler() function is called when a CCP2 interrupt occurs. In addition to the 1 msec interrupt, CCP2\_Handler() also maintains 10 msec, 100 msec, and 1000 msec timing flags for scheduling other events.

#### Slave Node Data Buffers

Three data buffers are used in the slave node application. The first of these data buffers is SensorBuf, which is 12 bytes in length and holds all sensor data to be sent to the master node. The SensorBuf buffer is implemented as a union that allows this data space to be addressed, both as bit fields and as bytes. The first byte of SensorBuf holds the communication status (COMM\_STAT) byte, which has status bits indicating the success or failure of an operation by the master device. The next two bytes in SensorBuf hold status bits reserved for indicating out-of-range conditions for each sensor channel in the slave node. These bits could be read by the master device to get a quick 'go/no-go' response for all of the parameters the slave node is monitoring. The remaining nine bytes in SensorBuf hold 8-bit data values for each of the slave node sensor measurements. Constants are defined at the beginning of the source code for the index values to SensorBuf.

The next buffer is RXBuffer, which holds bytes sent by the master device during data request and data write messages. The length of this buffer is defined to be eight bytes in the firmware. This buffer has to be large enough to hold the slave address byte (SLAVE\_ADDR), the data length byte (DATA\_LEN), the data offset byte (DATA\_OFFS), the transmit checksum, plus the total number of data bytes the master may write to the slave.

The third buffer used in the firmware is CmdBuf, which holds data bytes written to the slave device. For this application, up to four bytes may be written to a particular slave node. The four data bytes are copied from RXBuffer to CmdBuf, when a valid data write message from the master has been received. If the data write message is invalid, the data bytes in RXBuffer are discarded.

#### Sensor Data

The firmware for the PIC16C72A performs the following measurements as a remote sensor node:

- Analog Voltage/Current, 4 channels

- Fan Tachometer, 4 channels

- Temperature, 1 channel

This particular combination of sensor inputs was arbitrarily chosen, based on parameters commonly measured in an environmental monitoring application. In fact, the master firmware in this application only requests three of the nine available sensor data values. In practice, you may want to modify the firmware to accommodate a different combination of input channels. Furthermore, the firmware will operate on most any PICmicro device that has a SSP or MSSP module, with minor modifications. For example, you may want to select another device if you need more I/O pins, more A/D channels, non-volatile EEPROM data memory, or a higher resolution A/D converter.

#### A/D Conversions

A new A/D conversion is started in main() each time the 10 msec timing flag is detected. The AD\_Handler() function is called from the Interrupt Service Routine each time an A/D interrupt occurs. The AD\_Handler() function determines the presently selected A/D channel and stores the result in the correct location in SensorBuf. The A/D input multiplexer is then set to the next channel to be read. Each A/D input channel is sampled every 50 msec, which is adequate for most applications.

A thermistor is connected to CH4, which requires linearization to provide correct temperature readings. The A/D result from CH4 is used as an index to a temperature lookup table that provides the correct temperature in degrees Fahrenheit. The values in the temperature lookup table will depend on the thermistor and external circuit chosen for your design.

#### Fan Tachometer Data

I/O pins RB7:RB4 are used for fan tachometer inputs. These four pins have the weak pull-up feature and minimize the amount of hardware required in the design. Every 1 msec, the tachometer inputs are sampled and compared with their values from the previous sample. A count variable is maintained for each tachometer input. If a change has occurred on an input pin since the last sample, the count variable for that input is incremented. Each time a 1000 msec timing flag is detected in main(), the number of counts accumulated in the count variables are stored in the appropriate locations of SensorBuf and the count variables are cleared so that a new speed sample can be acquired.

The characteristics of the tachometer output depends on the particular fan that is used. Some brushless DC cooling fans, for example, have an open collector tachometer option that provides between 1 and 4 pulses per revolution. A small DC cooling fan with the following specifications was selected to provide design data for calculations:

- Voltage: 12 VDC

- Speed: 3000 RPM

- Tach: open collector square wave output, 2 pulses per revolution, 50% duty cycle

Based on these specifications, the fan will provide a tachometer output frequency of 100 Hz at its rated speed and the tachometer count variable will advance at the rate of 200 counts per second at the maximum fan speed. The I/O pin must be sampled at a frequency greater than 200 Hz to avoid signal aliasing and the accumulation time must be adjusted to scale the maximum fan speed data value. In this case, unsigned integers are used to hold the tachometer values, which allows a maximum data value of 255. If a 1000 msec accumulation time is used, the tachometer reading will be 200 at the rated fan speed. This choice of accumulation time allows some overhead to prevent overflow of the accumulated tachometer data.

#### SSP Event Handling

I<sup>2</sup>C bus events are processed in the SSP\_Handler() function, which is the heart of the I<sup>2</sup>C network protocol. If you need more general information on using the SSP module as an I<sup>2</sup>C slave device, please refer to AN734, "Using the PICmicro<sup>®</sup> SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication".

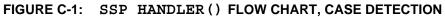

The SSP module is configured for  $I^2C$  Slave mode, 7-bit addressing. When a SSP interrupt occurs, the SSP\_Handler() function must identify the  $I^2C$  event that just occurred on the bus and take the appropriate action. For the purposes of explanation, it is helpful to identify all possible states of SSP module after an  $I^2C$ event and discuss each one individually.

The following five states are recognized and handled in the SSP\_Handler() function by testing bits in the SSPSTAT register:

- State 1: I<sup>2</sup>C write operation, last byte received was an address, buffer is full

- State 2: I<sup>2</sup>C write operation, last byte received was data, buffer is full

- State 3: I<sup>2</sup>C read operation, last byte received was an address, buffer is empty

- State 4: I<sup>2</sup>C read operation, last byte received was data, buffer is empty

- State 5: I<sup>2</sup>C logic reset by NACK from master device

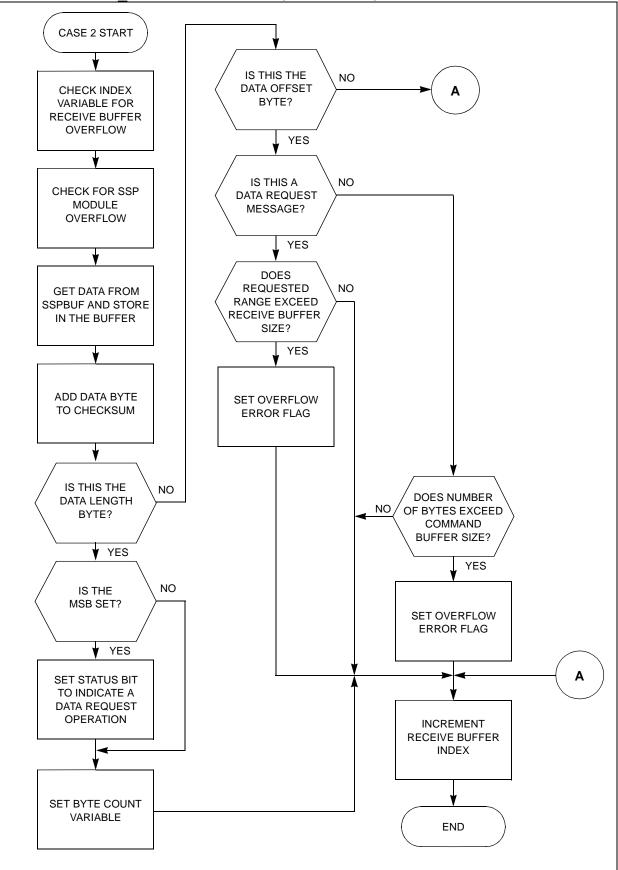

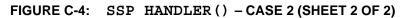

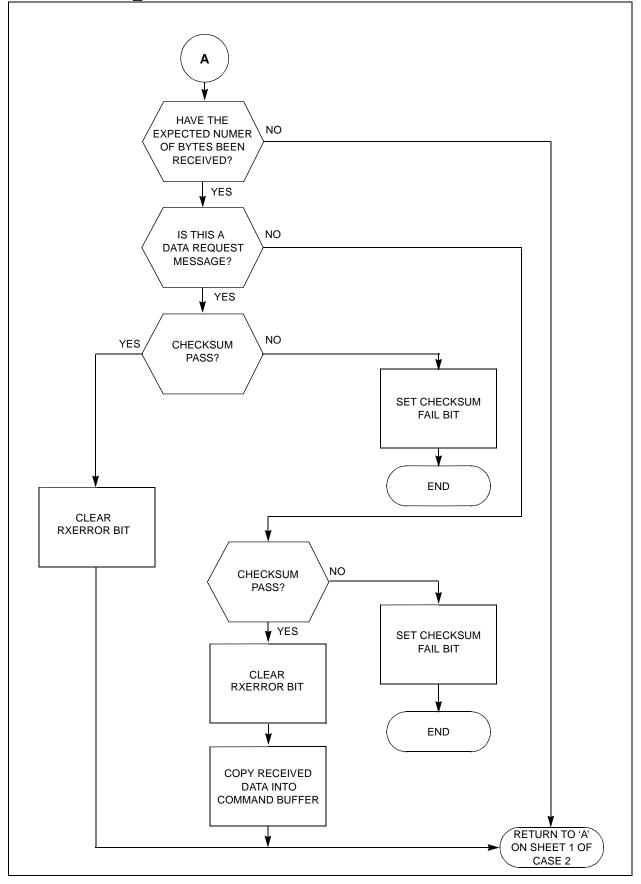

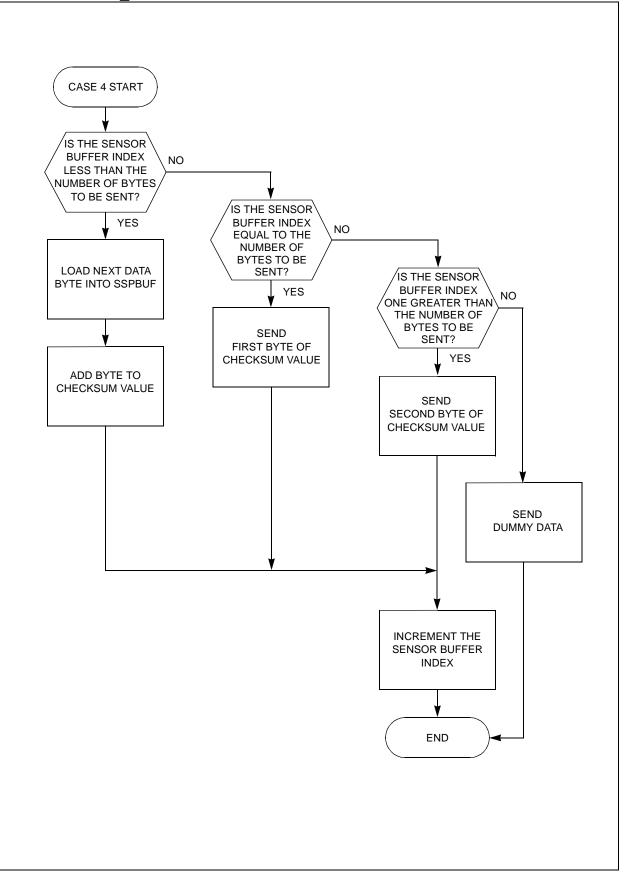

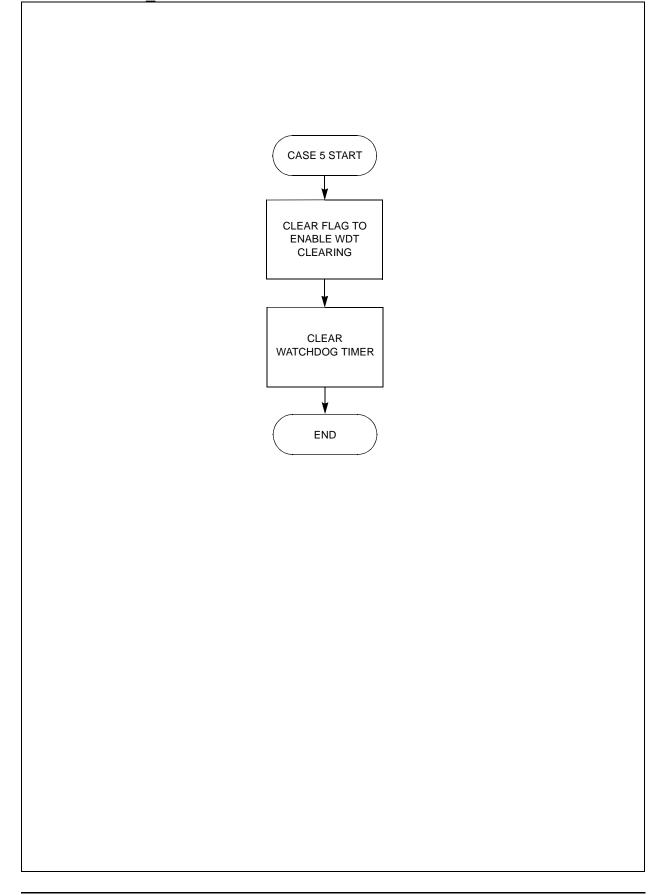

Flow charts for the  $\mathtt{SSP}_{\mathtt{Handler}}()$  function are given in Appendix C.

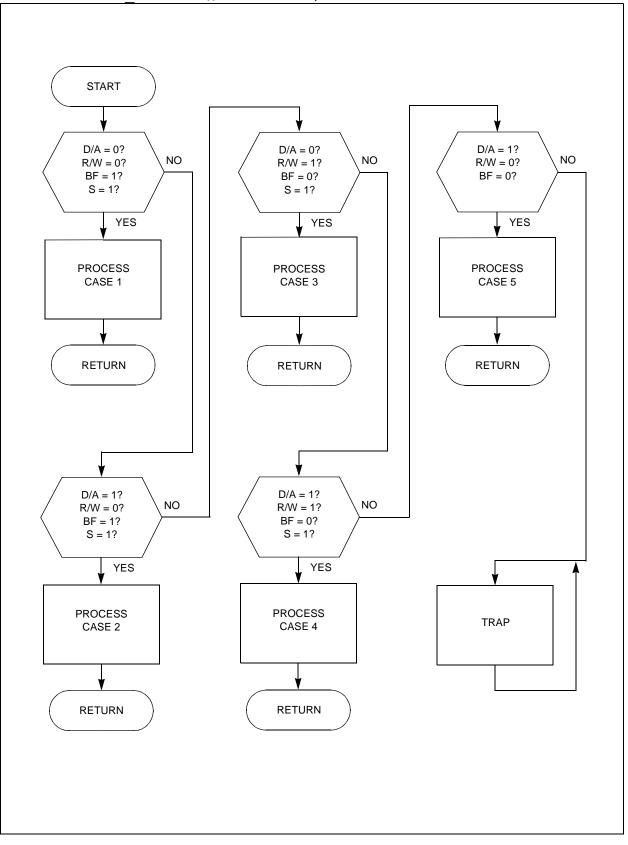

#### State 1

State 1 occurs after a valid START condition has occurred on the bus and an address was transmitted that caused an address match in the SSP module of the slave device. The LSb of the address byte is '0', which indicates a I<sup>2</sup>C write operation. This condition indicates that the master device is about to send the bytes for a new data write, or data request message. Since this is the beginning of a new transaction on the bus, a status flag is set in software to disable clearing of the Watchdog Timer in the main program loop. If the transaction takes longer than expected, due to a problem with the slave device, or an error on the bus, then the Watchdog Timer will reset the slave device and SSP module. In addition, the COMM\_STAT byte is initialized with the comm stat.rxerror bit set. This bit will not be cleared until all bytes in the data write or data request message have been received and a valid transmission has been verified. The RXBufferIndex variable is set to '0' and RXBuffer is cleared. The address byte that is currently in SSPBUF is stored in RXBuffer and is also used to initialize the value of RXChecksum.

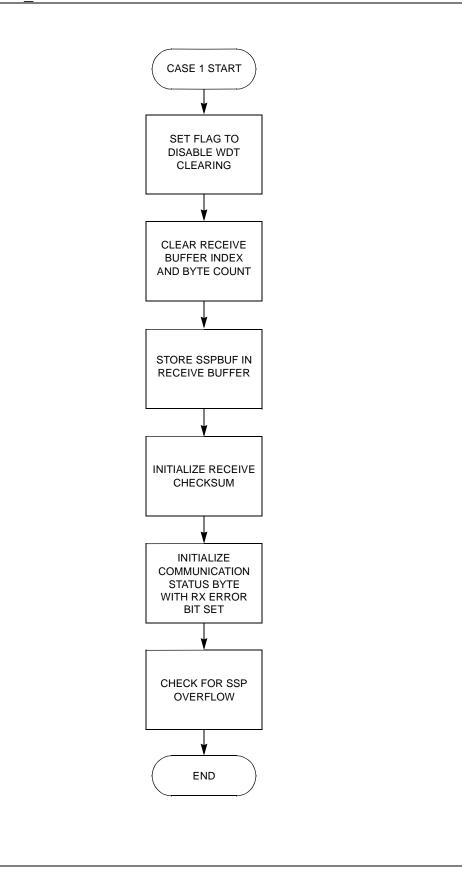

#### State 2

In the second state recognized by SSP Handler(), the bytes for a data write or data request message are stored in RXBuffer and RXBufferIndex is incremented after each byte received, to point to the next empty buffer location. The value of RXBufferIndex is checked against the length of RXBuffer to ensure that a buffer overflow does not occur. If a RXBuffer overflow occurs, the value of RXBufferIndex is set to the last location in the buffer and the comm stat.ovflw bit is set in the COMM\_STAT byte to indicate that the overflow occurred. If a SSP module overflow has occurred, the comm stat.sspov bit is set in COMM\_STAT. After each data byte is received, its value is added to RXChecksum and RXBufferIndex is compared against constant index values to determine the significance of the present byte in SSPBUF.

If the byte just received is the DATA\_LEN byte (byte #1), the MSb is checked to see if a data write or a data request is to be performed and the comm\_stat.r\_w bit in the COMM\_STAT byte is set to indicate the status of the message. If the MSb of the DATA\_LEN byte is set, indicating a data request message, this bit is masked to '0' so that it will not affect future calculations using the data length value stored in the 7 LSbs. The DATA\_LEN value is used to determine the value of RXByteCount, which holds the expected number of bytes to be received for the message. For a data request message, RXByteCount is always set to '3', because the number of expected bytes is fixed. For a data write message, RXByteCount is set to '3', plus the number of bytes indicated by the DATA\_LEN byte.

If the byte just received is the DATA\_OFFS byte (byte #2), a check is performed to see if the data request message or data write message will exceed the size of SensorBuf or CmdBuf. If the message exceeds the size of the buffer, the comm stat.ovflw status bit is set.

If the number of bytes received is equal to RXByte-Count, the end of the message has been reached. If the value of RXChecksum is not '0', the comm\_stat.chkfail status bit in the COMM\_STAT byte is set. If a data write message was sent and RXChecksum is '0', then the data contained in the message is considered valid and is transferred from RXBuffer into CmdBuf.

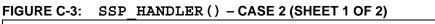

#### State 3

State 3 occurs after a valid START condition has occurred on the bus and an address was transmitted that caused an address match in the SSP module of the slave device. The LSb of the address byte is '1', which indicates a  $I^2C$  read operation. This condition indicates that the master device wishes to read bytes from the slave device.

As mentioned, the COMM\_STAT byte will always be the first byte returned during a read from the slave. This byte is written to SSPBUF and the value of TXChecksum is initialized. The value of SensBufIndex is set to '0' for future read operations.

#### State 4

In State 4, the slave node will send data bytes in SensorBuf to the master based on the values of the DATA\_LEN and DATA\_OFFS bytes. Each byte that is sent is added to the value of TXChecksum. If the number of bytes specified in the DATA\_LEN byte have been sent, then the 16-bit value of TXChecksum is returned. If there are no more bytes to be returned to the master, then the slave simply returns dummy data.

#### State 5

The final state detected in  $\texttt{SSP}_Handler()$  is caused by a NACK from the master device. This action indicates to the slave device that the master does not wish to receive any more data. The NACK event is used as a signal in this protocol to indicate the completion of a transaction on the  $I^2C$  bus. Consequently, the stat.wdtdis flag is cleared in the slave firmware to re-enable clearing of the Watchdog Timer.

#### Design Calculations for the I<sup>2</sup>C Bus

When designing an  $I^2C$  network, the number of devices on the bus, physical characteristics of the bus wiring, and the length of the bus must be considered. These variables determine the total amount of capacitive load on the bus, which the  $I^2C$  specification limits to 400pF. The value of the bus pull-up resistors are chosen based on the bus capacitance.

If the electrical characteristics of the wiring used for the  $I^2C$  bus are known, then it is easy to determine the total bus capacitance. All that is required is to figure out the capacitance contribution of each device on the bus. If the capacitance of each device is not known, then 10pF per device is a good estimate.

Another way to find the total bus capacitance is to pick preliminary values for the pull-up resistors and analyze the rise time on the bus, using a digital storage oscillocope. For most applications,  $2000\Omega$  would be a good starting value for the pull-up resistors. The rise time is the time that the signal takes to go from 10% to 90% of the final value. Then, the total bus capacitance can be determined using Equation 1.

$$C_{BUS} = \frac{t_R}{2.2 \cdot R}$$

Next, the rise time specification for the  $I^2C$  bus must be known, which is dependent on the bus frequency. For high speed mode (400kHz), the maximum rise time is 300nS. For standard mode (100kHz), the maximum rise time is 1µs. Equation 1 can be rearranged to find the required value of the pull-up resistors as shown in Equation 2.

# EQUATION 2: PULL-UP RESISTANCE

$$R_{PULLUP} = \frac{t_R}{2.2 \cdot C_{BUS}}$$

The I<sup>2</sup>C specification limits the amount of current on the bus to 3mA, which indirectly places a limit on the value of the pull-up resistors. So for a 5V bus, the minimum pull-up resistance that could be used is 5V/3mA, or approximately  $1600\Omega$ .

#### Driving Longer Distances

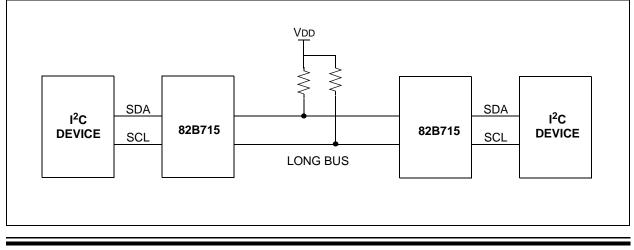

If the bus length in the application exceeds a few feet, selection of pull-up resistor values that satisfy the I<sup>2</sup>C specifications is a bit harder. In this case, bus extender IC's are available that allow you to use a longer bus in your design. One such IC, the Philips 82B715, provides a 10x current gain. This IC allows the total bus capacitance to increase to 4000pF and the maximum current on the bus to 30mA. Figure 4 shows how the bus extender IC's are connected. It may be possible to eliminate the need for the bus extenders since PICmicro I/O pins can sink or source greater than 3mA. Refer to the appropriate device data sheet for further details.

### FIGURE 5: I<sup>2</sup>C BUS EXTENSION BLOCK DIAGRAM

#### Example Design Calculations

As a design example, the characteristics of the wire that was used to test the application firmware provided in this application note, will be used in the calculations that follow. A 24 ft. length of wire was used to connect two PIC16F873 devices with  $200\Omega$  pull-up resistors on the SDA and SCL lines. The SCL line was observed on an oscilloscope and the rise time was determined to be 464ns. The wiring capacitance, per foot, is calculated in Example 1.

#### EXAMPLE 1: WIRING CAPACITANCE CALCULATION

$$C_{WIRE} = \frac{464 \text{ ns}}{(2.2)(200 \ \Omega)(24 \text{ ft})} = \frac{44 \text{ pF}}{\text{ft}}$$

The maximum bus length that could be used with this wire, without bus extenders, is calculated in Example 2.

#### EXAMPLE 2: MAXIMUM BUS LENGTH CALCULATION

$$L_{MAX} = \frac{400 \ pF}{44 \ pF} = 9.1 \ ft$$

Note that this length calculation also excludes the effects of device capacitance and would be reduced slightly in practice. Using the bus extenders, a theoretical bus length of 90 feet can be realized, using this wire. For further calculations, assume that the bus length is specified to be 3 feet. Using the wire chosen for this design example, would set the bus capacitance to  $3 \times 44pF/ft$  or 132pF. Now, we need to choose the bus frequency, which is arbitrarily selected to be 100kHz. Using the maximum rise time specification for a 100kHz bus frequency, the value of the pull-up resistors is calculated in Example 3.

| EXAMPLE 3: | PULL-UP RESISTOR |  |  |

|------------|------------------|--|--|

|            | CALCULATION      |  |  |

$$R_{PULLUP} = \frac{1 \,\mu s}{(2.2)(132 \, pF)} \approx 3400 \,\Omega$$

A pull-up resistor value of  $3400\Omega$  will provide approximately 1.5mA on the bus, which does not violate the maximum current limit.

Table 4 shows the maximum bus length based on the bus frequency, bus current limits, use of bus extenders, and the characteristics of our wire. Although you will need to calculate the maximum bus length for your specific application, this data table will give an approximate idea of what can be achieved.

#### Slew Rate Control

PICmicro devices with the MSSP module have a slew rate control feature. The slew rate control limits the slope of the falling edge of the SCL and SDA lines to lower EMI. Slew rate control is enabled in the MSSP module by clearing the SSPSTAT <7> bit (SMP). If a clock frequency greater than 400kHz is used, then the slew rate control should be disabled. Otherwise, the maximum fall-time specifications may be violated.

Additional SCL and SDA pin characteristics for the MSSP module are listed in Table 5.

| TABLE 4: | MAXIMUM BUS LENGTHS FOR EXAMPLE DATA |

|----------|--------------------------------------|

|          |                                      |

| Bus Capacitance = 44 pF/ft | Pull-up Resistance                                                                                                                                 | Bus Frequency = 100kHz | Bus Frequency = 400kHz |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--|

| Bus Capacitance = 44 pr/it |                                                                                                                                                    | Maximum Bus Length     | Maximum Bus Length     |  |

| No bus extender            | 1600Ω                                                                                                                                              | 6 feet                 | 1.8 feet               |  |

| 82B715 extender IC         | 160Ω                                                                                                                                               | 60 feet                | 18 feet                |  |

| •                          | : Bus length is limited by the choice of pull-up resistor values that do not exceed the maximum bus current in the I <sup>2</sup> C specification. |                        |                        |  |

#### TABLE 5: PICMICRO DEVICES WITH MSSP MODULE

|            | I <sup>2</sup> C Pin Characteristics |                                           |                                           |                                                    |

|------------|--------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------|

| Device     | Slew Rate<br>Control <sup>(1)</sup>  | Glitch Filter <sup>(1)</sup><br>on Inputs | Open Drain Pin<br>Driver <sup>(2,3)</sup> | SMbus<br>Compatible Input<br>Levels <sup>(4)</sup> |

| PIC16C717  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC16C770  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC16C771  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC16C773  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC16C774  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC16F872  | Yes                                  | Yes                                       | No                                        | Yes                                                |

| PIC16F873  | Yes                                  | Yes                                       | No                                        | Yes                                                |

| PIC16F874  | Yes                                  | Yes                                       | No                                        | Yes                                                |

| PIC16F876  | Yes                                  | Yes                                       | No                                        | Yes                                                |

| PIC16F877  | Yes                                  | Yes                                       | No                                        | Yes                                                |

| PIC17C752  | Yes                                  | Yes                                       | Yes                                       | No                                                 |

| PIC17C756A | Yes                                  | Yes                                       | Yes                                       | No                                                 |

| PIC17C762  | Yes                                  | Yes                                       | Yes                                       | No                                                 |

| PIC17C766  | Yes                                  | Yes                                       | Yes                                       | No                                                 |

| PIC18C242  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC18C252  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC18C442  | Yes                                  | Yes                                       | No                                        | No                                                 |

| PIC18C452  | Yes                                  | Yes                                       | No                                        | No                                                 |

**Note 1:** A "glitch" filter is on the SCL and SDA pins when the pin is an input. The filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency

- **2:** P-Channel driver disabled for PIC16C/FXXX and PIC18CXXX devices.

- 3: ESD/EOS protection diode to VDD rail on PIC16C/FXXX and PIC18CXXX devices.

4: SMbus input levels are not available on all PICmicro devices. Consult the respective data sheet for electrical specifications.

#### **Hardware Faults**

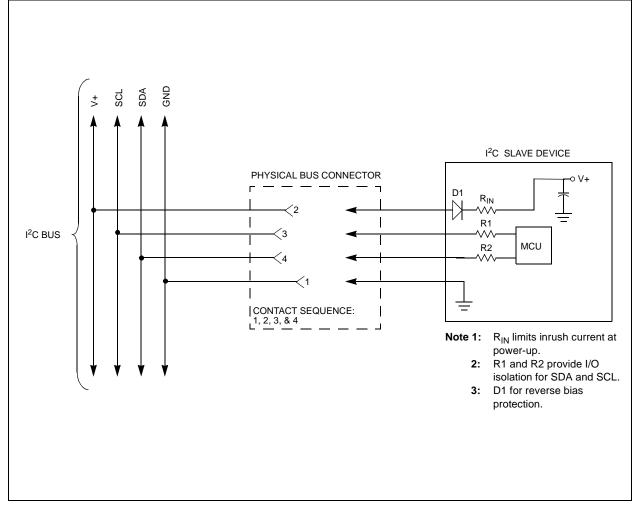

In a distributed environmental monitoring system, slave devices may be 'hot-swapped' on the bus to replace faulty systems, or for regular maintenance and testing. The application hardware will vary depending on the system requirements, but certain hardware features can be implemented in every system to ensure that minimal errors are introduced on the I<sup>2</sup>C bus, when a new device is inserted or removed. The connector hardware chosen must properly sequence the power supply and data signal connections to the host system. As a slave node is connected to the I<sup>2</sup>C bus, the first physical connection made should be the ground lead, so any residual potential is discharged into the system ground. The second connection should be the power to the slave node.

To avoid brown-out conditions on the system bus, the total amount of capacitance on the power supply rails should be considered and series current limiting resistors should be installed to limit the amount of inrush current. The SDA and SCL lines should be the last connection made through the connector. It is a good idea to install small resistors in series with the SDA and SCL lines. These resistors limit the amount of current that may flow through the I/O pins of the MCU during power-up. Figure 6 shows a sample block diagram of the physical bus connection.

### CONCLUSION

There are several established synchronous protocols available for implementation into any design requiring such. Each protocol will have its pros and cons and should be weighed accordingly, relative to the application requirements.

For this application note, the communications network is based on the  $l^2C$  protocol. Some features of the  $l^2C$  bus include:

- Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL).

- Minimal physical bus requirements; only two pull-up resistors required.

- Each device connected to the bus is software addressable by a unique address and simple master/slave relationships exist at all times; masters can operate as master-transmitters or as master-receivers.

- It is a true multi-master bus including collision detection and arbitration to prevent data corruption, if two or more masters simultaneously initiate data transfer.

- On-chip filtering spikes on the bus data line to preserve data integrity.

From the Slave I<sup>2</sup>C device to the Master I<sup>2</sup>C device, Microchip Technology offers several PICmicro devices which support these functional features. I<sup>2</sup>C based communication network systems implementing the PICmicro device are cost effective and easy to implement.

**Note:** Information contained in the application note regarding device applications and the like, is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated, with respect to the accuracy or use of such information, or infringement of patents, or other intellectual property rights arising from such use or otherwise.

### WHAT'S IN THE APPENDIX

Flow charts and C source code for the master node application have been included in Appendix A and Appendix B, respectively. Flow charts and C source code for the slave node application have been included in Appendix C and Appendix D.

Appendix E and Appendix F contain generic  $I^2C$  code written in assembly language. The assembly code does not implement the network protocol described in this application note, but you can use the routines as a starting point for your own application. The source code for the master device transmits a string of characters to the slave device and then reads the string back. The slave device stores the character string in a data memory buffer until a new string is written.

### **GLOSSARY OF TERMS**

| ACK              | Acknowledge                                  |             |

|------------------|----------------------------------------------|-------------|

| BRG              | Baud Rate Generator                          |             |

| BSSP             | Basic Synchronous Serial Po                  | rt          |

| EEPROM           | Electrically Erasable Program<br>Only Memory | imable Read |

| F/W              | Firmware                                     |             |

| I <sup>2</sup> C | Inter-Integrated Circuit                     |             |

| ISR              | Interrupt Service Routine                    |             |

| MCU              | Microcontroller Unit                         |             |

| MSSP             | Master Synchronous Serial P                  | ort         |

| NACK             | Not Acknowledge                              |             |

| SDA              | Serial Data Line                             |             |

| SCL              | Serial Clock Line                            |             |

| SSP              | Synchronous Serial Port                      |             |

# REFERENCES

The I<sup>2</sup>C-Bus Specification, Philips Semiconductor, Version 2.1, 2000,

http://www-us.semiconductors.com/i2c/

PICmicro<sup>™</sup> Mid-Range MCU Reference Manual, Microchip Technology Inc., Document Number DS33023

PIC16F87X Data Sheet, Microchip Technology Inc., Document Number DS30292

AN735, "Using the PICmicro® MSSP Module for Master  $I^2C^{TM}$  Communications", Microchip Technology Inc., Document Number DS00735

AN734, "Using the PICmicro<sup>®</sup> SSP for Slave I<sup>2</sup>C<sup>™</sup> Communication", Microchip Technology Inc., Document Number DS00734

# APPENDIX A: MASTER I<sup>2</sup>C CODE FLOW CHARTS

© 2000 Microchip Technology Inc.

FIGURE A-6: COMPOSE BUFFER CODE FLOW (2 OF 2)

#### Software License Agreement

The software supplied herewith by Microchip Technology Incorporated (the "Company") for its PICmicro® Microcontroller is intended and supplied to you, the Company's customer, for use solely and exclusively on Microchip PICmicro Microcontroller products.

The software is owned by the Company and/or its supplier, and is protected under applicable copyright laws. All rights are reserved. Any use in violation of the foregoing restrictions may subject the user to criminal sanctions under applicable laws, as well as to civil liability for the breach of the terms and conditions of this license.

THIS SOFTWARE IS PROVIDED IN AN "AS IS" CONDITION. NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATU-TORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICU-LAR PURPOSE APPLY TO THIS SOFTWARE. THE COMPANY SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

# APPENDIX B: MASTER I<sup>2</sup>C SOURCE CODE (C LANGUAGE)

```

******

I2C Master and Slave Network using the PICmicro

*****

Filename:

mstri2c.c

Date:

06/09/2000

Revision:

1.00

MPLAB 5.00.00

Tools:

Hi-Tech PIC C Compiler V7.85

Richard L. Fischer

Author:

Company:

Microchip Technology Incorporated

System files required:

mstri2c.c

i2c comm.c

init.c

delay.c

(Hi-Tech file)

pic.h

(Hi-Tech file)

delay.h

(Hi-Tech file)

mstri2c.h

i2c_comm.h

cnfig87x.h

*****

Notes:

Device Fosc -> 16.00MHz

WDT -> on

Brownout -> on

Powerup timer -> on

Code Protect -> off

Interrupt sources -

1. USART based transmissions

2. I2C events (valid events)

3. I2C Bus Collision

4. Timer1 - 100mS intervals

```

```

*

Memory Usage Map:

$0000 - $00BC $00BD ( 189) words

*

Program ROM

Program ROM

0587 - 07FF

$2007 - $2007 $0001 ( 1) words

Program ROM

$0337 ( 823) words total Program ROM*

*

*

Bank 0 RAM

$0020 - $0075 $0056 ( 86) bytes

*

Bank 0 RAM

$007F - $007F $0001 ( 1) bytes

$0057 ( 87) bytes total Bank 0 RAM *

$00A0 - $00AA $000B ( 11) bytes

Bank 1 RAM

$00FF - $00FF $0001 (

Bank 1 RAM

1) bytes

$000C ( 12) bytes total Bank 1 RAM *

* * * * * * * * * * * * * * * *

#include <pic.h>

// processor if/def file

#include "cnfig87x.h"

// configuration word definitions

#include "mstri2c.h"

#include "c:\ht-pic\samples\delay.h"

```

\_\_CONFIG ( CONBLANK & CP\_OFF & DEBUG\_OFF & WRT\_ENABLE\_OFF & CPD\_OFF & LVP\_OFF & BODEN\_ON & PWRTE\_ON & WDT\_ON & HS\_OSC );

```

MAIN PROGRAM BEGINS HERE

void main(void)

/* Initialization is done here */

Init_Usart();

// initialize USART peripheral

// initialize Ports

Init_Ports();

// initialize SSP module

Init_Ssp();

Init Timer1();

// initialize TMR1 peripheral

/* Interrupts are enabled here */

TMR1IE = 1;

// enable TMR1 Overflow interrupt

BCLIE = 1;

// enable bus collision interrupt

SSPIE = 1;

// enable I2C based interrupts

sflag.status = 0x0000;

// ensure all event flags are reset

// ensure all event flags are reset

eflag.status = 0x00;

PEIE = 1;

// enable peripheral interrupts

// enable global interrupts

ei();

for ( ;; )

// infinite loop

{

// reset WDT

CLRWDT();

//-----

Will execute these statements if Master wants to read from Slave I2C

//-----

if (sflag.event.read i2c && sflag.event.i2c ) // test if read I2C is active

{

if ( !sflag.event.reads_done ) // test if more reads are needed

{

DelayUs( 400 );

// short delay between events

// to allow for slow FOSC on Slave

Service I2CSlave();

// Service I2C slave device(s)

}

if ( sflag.event.reads done )

// test if that was last read

{

sflag.status &= 0x00F0;

// reset all I2C event flags

// reset all error event flags

eflag.status = 0x00;

TMR1ON = 1;

// turn on Timer1 module

TMR1IE = 1;

// re-enable Timer1 interrupt

}

}

}

}

//-----

Will evaluate these conditional statements on an interrupt basis

11

//-----

void interrupt piv( void )

{

if ( SSPIE && SSPIF )

// test for I2C event completion

{

SSPIF = 0;

// reset I2C based interrupt flag

sflag.event.i2c = 1;

// set I2C event service flag

PORTB ^= 0b0000001;

// ***** test purposes only *****

```

```

}

else if ( BCLIE && BCLIF )

// test for bus collision

// set bus collision flag error

eflag.i2c.bus coll error = 1;

sflaq.event.i2c = 1;

// set I2C event service flag

BCLIF = 0;

// reset bus collision interrupt flag

PORTB ^= 0b0000010;

// ***** test purposes only *****

}

else if ( TXIE && TXIF )

// test if USART based transmit interrupt

{

if ( index < MaxLength2PC )</pre>

// is all data sent ?

{

TXREG = ReadStatBufFromSlave[index]; // send another byte out

index++;

// increment array index

}

else

{

sflag.event.usart_tx = 0;

// reset USART TX in progress flag

TXIE = 0;

// disable transmit interrupt

SSPIE = 1;

// enable I2C based interrupts

index = 0x00;

// reset array index

}

}

else if ( TMR1IE && TMR1IF )

// test for valid TMR1 interrupt

{

sflag.event.read i2c = 1;

// set 100mS event service flag

// set I2C event service flag

sflaq.event.i2c = 1;

PORTB &= 0b00001110;

// ***** test purposes only *****

PORTB ^= 0b00001000;

// ***** test purposes only *****

TMR1ON = 0;

// turn off Timer1 module

TMR1IF = 0;

// reset TMR1 rollover interrupt flag

TMR1IE = 0;

// disable TMR1 based interrupt

TMR1L += 0x60;

// re-initialize TMR1 for

// 100mS intervals

TMR1H = 0x3C;

}

}

```

```

******

I2C Master and Slave Network using the PICmicro

*

i2c_comm.c

Filename:

*

06/09/2000

Date:

*

Revision:

1.00

MPLAB 5.00.00

*

Tools:

Hi-Tech PIC C Compiler V7.85

Richard L. Fischer

Author:

Microchip Technology Incorporated

Company:

*****

Files required:

pic.h

(Hi-Tech file)

delay.h

*

(Hi-Tech file)

i2c_comm.h

*****

Notes: The routines within this file are for communicating

with the I2C Slave device(s).

// processor if/def file

#include <pic.h>

#include "i2c_comm.h"

#include "c:\ht-pic\samples\delay.h"

```

```

#define LIMIT 0x80

```

```

// limit value for slave data compare

```

```

MAIN PROGRAM BEGINS HERE

void Service_I2CSlave( void )

{

//-----

_____

Will execute these statements once per each round of slave reads.

11

//-----

if ( !sflag.event.read start )

// execute once per entire rounds of

// slave reads

{

sflag.event.read start = 1;

// set reads start flag

index = 0x00;

slave_count = 0x00;

// reset running slave counter

// initialize address hold buffer

address hold = SlaveAddress[slave count];

// (1st slave)

Write2Slave Ptr = &WriteStatBuf2Slave[0];

// (bytecount, functional, checksum)

read count = OperChannelsPerSlave + 1;

// set byte read count

// (bytes + 1/2checksum)

ReadFSlave Ptr = &ReadStatBufFromSlave[0];

// set up pointer for data read from

// Slave

I2CState_Ptr = &ReadFSlaveI2CStates[0];

// initialize I2C state pointer

}

//-----

// Will execute these statements if last I2C bus state was a WRITE

//-----

if (sflag.event.write_state) // test if previous I2C state was a write

{

if ( ACKSTAT )

// was NOT ACK received?

// generate bus stop condition

PEN = 1;

eflag.i2c.ack error = 1;

// set acknowledge error flag

}

sflag.event.write_state = 0;

// reset write state flag

}

//-----

// Will execute these statements if a bus collision or an acknowledge error

//-----

if ( eflag.i2c.bus coll error || eflag.i2c.ack error )

{

sflag.event.read loop = 0;

// reset read loop flag for any error

sflag.event.next i2cslave = 1;

// set flag indicating next slave

temp.error = error mask << slave count; // compose error status word

if ( eflag.i2c.bus_coll_error )

// test for bus collision error

eflag.i2c.bus coll error = 0;

// reset bus collision error flag

bus.error_word |= temp.error;

// compose bus error status word

SSPIF = 1;

// set false interrupt to restart comm

if ( eflag.i2c.ack_error )

// test for acknowledge error

eflag.i2c.ack error = 0;

// reset acknowledge error flag

comm.error_word |= temp.error;

// compose communication error status word

}

}

```

```

// else no error for this slave

else

{

temp.error = error_mask << slave_count; // compose error status word</pre>

bus.error_word &= ~temp.error; // reset bus error bit for this slave

comm.error word &= ~temp.error;

// reset comm error bit for this slave

}

//-----

// Will execute these statements for each new slave device after the first

//-----

if (sflag.event.next_i2cslave) // if next slave is being requested

{

ComposeBuffer();

// compose buffer for sending to PC

sflag.event.next_i2cslave = 0;

// reset next slave status flag

if ( sflag.event.usart tx )

// test if USART TX still in progress

{

// increment slave counter

slave count ++;

// disable SSP based interrupt

SSPIE = 0;

if ( !sflag.event.usart_tx )

// test if interrupt occurred while here

SSPIE = 1;

// re-enable SSP based interrupt

}

}

address_hold = SlaveAddress[slave_count]; // obtain slave address (repeat or next)

read_count = OperChannelsPerSlave + 1; // set byte read count (bytes, 1/2checksum)

ReadFSlave_Ptr = &ReadStatBufFromSlave[0];// set up pointer for data read from Slave

I2CState_Ptr = &ReadFSlaveI2CStates[0]; // re-initialize I2C state pointer

//-----

// Test if all slaves have been communicated with or continue with next bus state

//-----

if ( slave_count < OperNumberI2CSlaves ) // test if all slaves have not been accessed

{

sflag.event.i2c = 0;

// reset I2C state event flag

// execute next I2C state

I2CBusState();

}

// else

else

{

// set flag indicating all slaves are read

sflag.event.reads done = 1;

}

}

//-----

// Will execute this switch/case evaluation for next I2C bus state

//-----

void I2CBusState ( void )

{

// retrieve next I2C state

i2cstate = *I2CState_Ptr++;

switch ( i2cstate )

// evaluate which I2C state to execute

{

case ( READ ):

// test for I2C read

RCEN = 1;

// initiate i2C read state

break;

```

```

case ( WRITE_DATA ):

// test for I2C write (DATA)

SSPBUF = *Write2Slave_Ptr++;

sflag.event.write_state = 1;

// initiate I2C write state

// set flag indicating write event in action

break;

case ( WRITE ADDRESS1 ):

// test for I2C address (R/W=1)

SSPBUF = address_hold + 1;

// initiate I2C address write state

sflag.event.write_state = 1;

// set flag indicating write event in action

break;

case ( START ):

// test for I2C start state

// initiate I2C bus start state

SEN = 1;

break;

case ( WRITE_ADDRESS0 ):

SSPBUF = address_hold;

sflag.event.write_state = 1;

// test for I2C address (R/W=0)

// initiate I2C address write state

// set flag indicating write event in action

break;

// test for send acknowledge state

case ( SEND ACK ):

*ReadFSlave Ptr++ = SSPBUF;

// save off byte

if ( read_count > 0)

// test if still in read loop

read count -= 1;

// reduce read count

I2CState_Ptr -= 2;

// update state pointer

}

ACKDT = 0;

// set acknowledge data state (true)

ACKEN = 1;

// initiate acknowledge state

break;

case ( SEND_NACK ):

// test if sending NOT acknowledge state

*ReadFSlave Ptr = SSPBUF;

// save off byte

ACKDT = 1;

// set acknowledge data state (false)

ACKEN = 1;

// initiate acknowledge sequence

break;

case ( STOP ):

// test for stop state

// initiate I2C bus stop state

PEN = 1;

sflag.event.next_i2cslave = 1;

// set flag indicating next slave

// reset flag, write is done

sflag.event.writes_done = 1;

break;

case ( RESTART ):

// test for restart state

RSEN = 1;

// initiate I2C bus restart state

break;

default:

11

break;

}

//-----

// Compose Buffer to transmit to PC and Slave I2C (slave I2C if overlimit)

//-----

void ComposeBuffer( void )

{

if ( ( ReadStatBufFromSlave[0] & 0x80 ) || ( eflag.i2c.slave_override ) )

{

checksum.word = Calc Checksum( &ReadStatBufFromSlave[0], 4 );

```

}

```

temp.hold.lobyte = ReadStatBufFromSlave[4];

temp.hold.hibyte = ReadStatBufFromSlave[5];

if ( ( checksum.word + temp.checksum ) == 0 ) || ( eflag.i2c.slave override ) )

{

ReadStatBufFromSlave[6] = bus.error.hibyte;

11

ReadStatBufFromSlave[7] = bus.error.lobyte;

11

ReadStatBufFromSlave[8] = comm.error.hibyte;

11

ReadStatBufFromSlave[9] = comm.error.lobyte;

11

if ( eflag.i2c.slave override ) // test if comm failed with Slave

{

ReadStatBufFromSlave[5] = 0x00; // null out voltage data

ReadStatBufFromSlave[4] = 0x00; // null out rpm data

ReadStatBufFromSlave[3] = 0x00; // null out temperature data

}

else

// else comm with Slave OK

{

ReadStatBufFromSlave[5] = ReadStatBufFromSlave[3];

// voltage data

ReadStatBufFromSlave[4] = ReadStatBufFromSlave[2];

// rpm data

ReadStatBufFromSlave[3] = ReadStatBufFromSlave[1];

// temperature data

}

ReadStatBufFromSlave[2] = ( slave count + 1 );

// slave ID

ReadStatBufFromSlave[1] = 0x55; // start sync character 2

ReadStatBufFromSlave[0] = 0xAA; // start sync character 1

sflag.event.usart tx = 1;

// set flag indicating USART TX in progress

TXIE = 1;

// enable USART TX interrupts

if ( comm.error word & 0x0FFF )

// test if any slave is on the bus

{

if ( (ReadStatBufFromSlave[5] >= LIMIT) && ( !eflag.i2c.slave_override ) )

{

WriteData2Slave[3] = 0x01; // out of limits indicator to slave

Write_I2CSlave();

// write "error" code to slave

}

else if ( (ReadStatBufFromSlave[5] < LIMIT) && ( !eflag.i2c.slave_override ) )</pre>

{

WriteData2Slave[3] = 0x00; // in limits indicator to slave

Write I2CSlave();

// write "valid" code to slave

}

}

eflag.i2c.slave_override = 0;

// reset slave override flag

read retry = 0 \times 00;

// reset retry count

eflag.i2c.retry attempt = 0;

// reset retry communication flag

}

else

{

eflag.i2c.retry_attempt = 1; // set retry communications flag

}

else

// set retry communications flag

eflag.i2c.retry_attempt = 1;

if ( eflag.i2c.retry attempt )

// test if there was a retry request

```

}

{

{

```

read retry ++;

// update retry counter

if ( read retry > MaxSlaveRetry -1 )

// test if all retries have been attempted

{

eflag.i2c.slave_override = 1;

// set flag to process next packet no matter

// what

if ( slave_count == 0 )

// test for first slave

{

Write2Slave Ptr = &WriteStatBuf2Slave[0];

// reinitialize pointer

}

else

// else slave 1 -> X

{

Write2Slave_Ptr = &WriteStatBuf2Slave[slave_count * 3]; // reinitialize pointer

}

}

}

//-----

// Will execute these statements when requiring to write to a Slave I2C device

//-----

void Write_I2CSlave( void )

{

// define auto variable

unsigned char temp_ptr;

sflag.event.writes_done = 0;

temp_ptr = Write2Slave_Ptr;

unsigned char temp ptr;

// ensure flag is reset

temp_ptr = Write2Slave_Ptr; // save off current write pointer