# AN691

# Optimizing Digital Potentiometer Circuits to Reduce Absolute and Temperature Variations

Author: Bonnie C. Baker, Microchip Technology Inc.

# INTRODUCTION

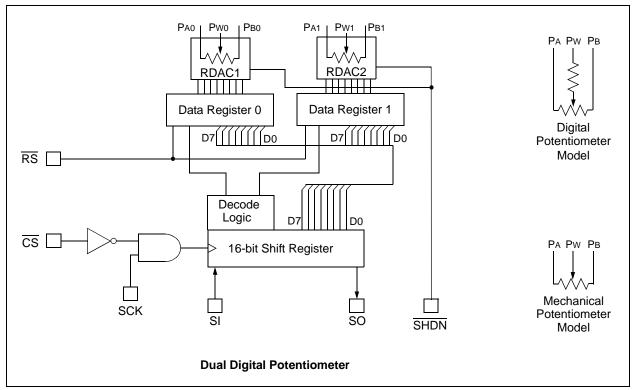

Mechanical potentiometers are typically used to adjust system reference levels, gain errors and offset errors. Digital potentiometers can be used for the same functions while offering the added capability of digital adjustment control. Devices, such as Microchip's MCP41XXX and MCP42XXX digital potentiometer families, can be used much like a mechanical potentiometer in that they have three resistive terminals for the single versions (MCP41010, MCP41050, and MCP41100) and six resistive terminals for the dual versions (MCP42010, MCP42050, and MCP42100) as illustrated in Figure 1. The two modes that a potentiometer can be configured in are the Rheostat mode and Voltage Divider mode. When used in the Rheostat mode, the wiper (terminal Pw), is shorted to either the PA or PB terminal of the device. This configuration is shown in Figure 2. When a digital potentiometer is used in the Voltage Divider mode (Figure 2.b) all three terminals are connected to differing nodes in the circuit.

In both of these configurations, the digital potentiometer will have a nominal resistance and temperature coefficient error that may affect the overall application unless precautions are taken. In this application note, circuit ideas will be presented that use the necessary design techniques to mitigate these errors, consequently optimizing the performance of the digital potentiometer.

**FIGURE 1:** The operation of the digital potentiometer as compared to the mechanical potentiometer is functionally the same. The adjustment of the digital potentiometer is done with a serial code to the device. Although the mechanical potentiometer provides simplicity, the digital potentiometer provides flexibility and reliability.

# **Rheostat Mode Operation and Specifications**

In the Rheostat mode, either terminal PA or PB are connected to the wiper terminal as shown in Figure 2.a. In this mode, the output resistance is digitally adjusted from the maximum nominal value, minus one LSB, down to zero ohms. The nominal resistance of the element in the Rheostat mode is calculated with the following formulas:

or

$$R_{AW} = \frac{R_{AB} \left(2^N - D_N\right)}{2^N} + R_W$$

$R_{BW} = \frac{R_{AB}(D_N)}{2^N} + R_W$

where:

RAW is the resistance between pin A and pin W of the digital potentiometer.

RAB is the nominal resistance across the entire potentiometer, from pin A to pin B.

RBW is the resistance between pin B and pin W of the digital potentiometer.

n is the number of digital potentiometer bits. For the MCP4XXXX family of potentiometers, the number of bits is eight.

Dn is the digital code in decimal form that is used to program the digital potentiometer. With the MCP4XXXX 8-bit digital potentiometers the programmable digital code ranges from 0 to  $2^8$  - 1 or 255.

Rw is the parasitic resistance through the wiper.

As summarized in the table in Figure 2, the nominal resistance of the digital potentiometer varies, depending on the device selected. Additionally, the part to part variation of the nominal resistance is specified to be within a given percentage. For example, the nominal resistance of the MCP4X010 is 10 k $\Omega \pm 20\%$ . The resistance variation of these digital potentiometers is primarily dependent on the process variation of the sheet-rho of a diffused p-silicon layer and the on-resistance of the internal switches.

The temperature variance of the digital potentiometers element is also shown in Figure 2. For instance, the variance of the MCP41010 (10 k $\Omega$ ) digital potentiometer is 800 ppm/°C (typical). With this specification, the expected change of the total resistance of the MCP41010 is from 10 k $\Omega$  at 25°C to 9.52 k $\Omega$  at 85°C.

| PA PB ○<br>a. Rheostat Mode |                                       |                                            |                                      | PA<br>PB<br>PW<br>Divider Mode              |                                                  |                                       |

|-----------------------------|---------------------------------------|--------------------------------------------|--------------------------------------|---------------------------------------------|--------------------------------------------------|---------------------------------------|

| Device                      | Nominal<br>RAB<br>Resistance<br>(typ) | RAB Change<br>with<br>Temperature<br>(typ) | Nominal<br>Resistance<br>Match (typ) | RA, RB<br>Relative<br>Accuracy INL<br>(typ) | Tempco<br>Variance<br>Between RA<br>and Rв (typ) | Code to Code<br>Variance<br>DNL (typ) |

| MCP41010<br>(single)        | 10 KΩ ±20%                            | 800 ppm/°C                                 |                                      | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

| MCP42010 (dual)             | 10 KΩ ±20%                            | 800 ppm/°C                                 | 0.2%                                 | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

| MCP41050<br>(single)        | 50 KΩ ±30%                            | 800 ppm/°C                                 |                                      | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

| MCP42050 (dual)             | 50 KΩ ±30%                            | 800 ppm/°C                                 | 0.2%                                 | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

| MCP41100<br>(single)        | 100 KΩ ±30%                           | 800 ppm/°C                                 |                                      | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

| MCP42100 (dual)             | 100 KΩ ±30%                           | 800 ppm/°C                                 | 0.2%                                 | ±0.25 LSB                                   | 1%                                               | ±0.25 LSB                             |

**FIGURE 2:** The resistive elements of the digital potentiometer can be configured in (a.) the Rheostat mode or (b.) the Voltage Divider mode. Each mode has its own set of performance specifications.

# Digital Potentiometer Circuits Configured in the Rheostat Mode

The level of nominal resistive matching that is shown in Figure 2 can be acceptable for some applications. However, if a degree of precision is desired, the dual potentiometer can be used to an advantage in the Rheostat mode. With the dual digital potentiometer, the nominal resistances between the two potentiometers are ratio matched to a very small percentage as shown in Figure 2. For instance, the matching of the two resistive potentiometer elements in the MCP42010 (dual, 10 k $\Omega$ ) is guaranteed to be less than ±0.2% (typ). This close relationship between the two resistor arrays can be used to a distinct advantage.

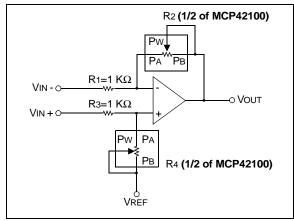

One circuit that takes advantage of the relationship between the two potentiometers in the dual, MCP42100 is shown in Figure 3.

**FIGURE 3:** The digital potentiometers in this differential amplifier can be programmed to change the gain of the circuit as well as enhance the common-mode rejection. The common-mode rejection of this circuit is fairly immune to temperature changes.

In Figure 3, the arrangement of the resistors around an operational amplifier is called the difference amplifier or op amp subtractor. The DC transfer function of this circuit is equal to:

$$V_{OUT} = \frac{V_1 R_4 (R_1 + R_2)}{((R_3 + R_4)R_1)} - V_2 \left(\frac{R_2}{R_1}\right) + V_{REF} R_3 \frac{(R_1 + R_2)}{((R_3 + R_4)R_1)}$$

If  $R_1/R_2$  is equal to  $R_3/R_4$ , the system gain of this circuit equals:

$$V_{OUT} = (V_1 - V_2) \left(\frac{R_2}{R_1}\right) + V_{REF}$$

The fact that  $R_1/R_2$  is equal to  $R_3/R_4$  simplifies the mathematics in this system considerably. Since the gain of both input signals are the same, the common-mode voltage (CMV) of the two signals is conveniently subtracted from the output results.

Ideally, CMV changes are rejected by this circuit. The calculated common-mode rejection (CMR) error that is attributed to resistor mismatches in this circuit is equal to:

$$CMR = 100 \frac{\left(1 + \frac{R_1}{R_2}\right)}{\% \text{ of mismatch error}}$$

where (% of mismatch error) is the mismatch in the equation  $R_1/R_2 = R_3/R_4$ .

An example of the impact of this error is demonstrated with a 12-bit, 5V system, where the gain of the circuit is 100V/V, the common-mode voltage ranges 0 to 5V and the matching error is  $\pm 0.2\%$ . Using the formula above, the contributed error of this type of common-mode excursion is equal to 0.2 mV. This voltage is five times less than 1 LSB.

Adjustable gain is easily implemented by making the discrete resistors equal ( $R_1=R_3$ ) and changing both potentiometers together as desired. Although, any digital potentiometer can be used in the  $R_2$  and  $R_4$  position in this circuit, the higher the nominal value of the digital potentiometer, the wider the adjustable gain range will be.

In a single supply environment, a voltage reference is used to center the output signal between ground and the power supply. This voltage is represented in this circuit as VREF. The VREF circuit function can be implemented with a precision voltage reference or with an adjustable voltage reference circuit that uses a digital potentiometer as shown in Figures 5, 6 and 7. The adjustable voltage reference designs offer the flexibility of removing offset system errors.

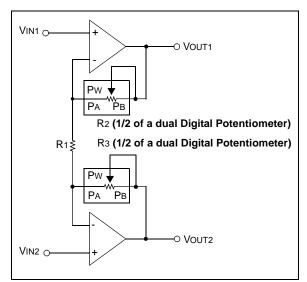

An alternative to the circuit shown in Figure 3 is illustrated in Figure 4. In this circuit configuration, the differential inputs are high impedance and the output is differential. There are three resistors used in this circuit, two of which are 1/2 of a dual potentiometer.

**FIGURE 4:** This differential in and differential out circuit uses two digital potentiometers in the Rheostat mode. When the two digital potentiometers are set to be equal, the gains on the two input signals are equal.

If  $R_2 = R_3$ , the transfer function of this circuit is:

$$(V_{OUT1} - V_{OUT2}) = (V_{IN1} - V_{IN2}) \left(1 + \frac{2R_2}{R_1}\right)$$

This flexible gain circuit uses the matching of nominal resistance and thermal shifts of the dual potentiometer to an advantage.

# Voltage Divider Mode: Operation and Specifications

In the Voltage Divider mode shown in Figure 2, all three terminals to the potentiometer are connected to separate nodes in the circuit. In this mode, the total resistance of the device is separated into two resistors. The first being the resistance from terminal PB to the wiper (Pw) and the second is between terminal PA to the wiper. The relationship between these two resistors is equal to:

$$R_{B} = R_{AB} \frac{(D_{n})}{2^{n}}$$

$$R_{A} = R_{AB} \frac{(2^{n} - D_{n})}{2^{n}}$$

where:

RB is equal to the resistance between the PB terminal and PW terminal minus the wiper resistance.

RA is equal to the resistance between the PA terminal and PW terminal minus the wiper resistance.

There is a third resistance from the digital potentiometers element to the wiper terminal. This resistance is called the wiper resistance or Rw. If the wiper of the digital potentiometer is followed by a high impedance node, errors caused by the wiper resistance are eliminated.

The absolute value of these resistances will still vary between  $\pm 20\%$  and  $\pm 30\%$  (depending on the device used), however as shown in the table in Figure 2, the ratio between the two elements will be much lower. In the case of the MCP4X010, the maximum mismatch error between RB and RA is  $\pm 0.098\%$  (DNL specification).

The related temperature performance of these two resistors is also lower than the absolute temperature behavior at a typical 1 ppm/°C. Since the resistive elements of RB and RA are manufactured with the same material on the same chip, the ratio of the thermal changes with temperature is considerably better as compared to the single resistive element in the Rheostat mode.

## Digital Potentiometer Circuits Configured in the Voltage Divider Mode

The digital potentiometer can be used very effectively in a variety of circuits when it is configured in the Voltage Divider mode. All of the following circuits take advantage of the resistive ratio matching of the two resistive elements (RB and RA).

## Voltage Reference Circuits

One form of offset voltage adjustment is implemented with a voltage reference. This type of adjustment usually compensates for all of the system offset errors in the signal path.

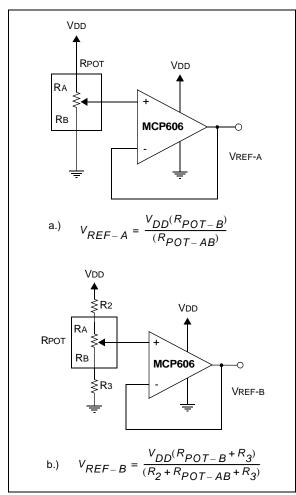

In Figure 5, a digital potentiometer is used to design an adjustable voltage reference. In Figure 5.a, the potentiometer is placed between the positive power supply and ground. The output voltage of the adjustable reference is equal to:

$$V_{REF} = \frac{V_{DD}R_{POT-B}}{R_{POT-AB}}$$

The resolution of this reference circuit is dependent on the number of programmable bits of the digital potentiometer and the value of VDD. When using any of the 8bit digital potentiometers from Microchip and a 5V supply, the nominal LSB size would be 19.53 mV.

**FIGURE 5:** A digitally adjustable reference can be designed using the power supply across the digital potentiometer (a). Higher accuracy can be achieved by using additional resistors (b) in series with the digital potentiometer.

In this circuit, the operational amplifier acts to isolate or buffer the digital potentiometer resistance from following stages.

The absolute accuracy and over temperature performance of the voltage presented to the input of the amplifier is dependent on the matching of the digital potentiometer resistive elements as well as the stability of the power supply.

As an example of the effects of the digital potentiometer errors, the MCP4X010 (10 k $\Omega$  digital potentiometer) would perform with an absolute accuracy less than ±0.25 LSB (typ) or ±3.9065 mV at 25°C. Over temperature, the output voltage would typically vary 1% due to resistance matching. This translates into a typical variance over temperature (-40°C to +85°C) of 1.172 mV or ±0.585 mV. Adding this to the error at room temperature, the total possible error becomes ±4.99 mV. In this example, it is assumed that the power supply is a stable 5V.

If a smaller LSB size is required for an adjustable voltage reference that has the full dynamic range of the power supply voltage, the circuit in Figure 6 can be used.

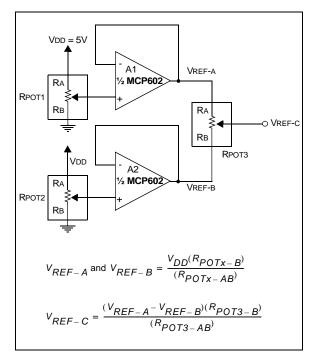

**FIGURE 6:** Three digital potentiometers in combination with a dual amplifier can be configured for a wide dynamic range, adjustable voltage reference that has an ideal LSB size of  $VDD/2^{2n}$ , where n is the number of digital potentiometer bits.

In this circuit, the wiper voltage of RPOT1 is buffered with A1, a single supply, CMOS amplifier and RPOT2 is buffered with A2. The dynamic range of the output of A1 and A2 is equal to approximately (GND+50 mV) to (VDD–1.2V). The positive output swing range is primarily restricted by the amplifiers maximum input common mode voltage. The theoretical LSB size of the voltages at VREF-A and VREF-B are equal to VDD/2<sup>n</sup> or 19.53 mV.

The voltage difference of VREF-A and VREF-B is impressed across RPOT3. The difference of these voltages are then divided again by the third digital potentiometer to have an ideal LSB size equal to:

$$V_{REF-C} = \frac{(V_{DD}/2^n)}{2^n}$$

$$V_{REF-C} = \frac{V_{DD}}{2^{2n}}$$

The configuration in Figure 6 provides an theoretical output resolution of 16 bits. When VDD is equal to 5V, the theoretical LSB size is 76.29  $\mu$ V.

The value of the output of this precision adjustable reference is compromised by the absolute matching resistance and temperature coefficient of the digital potentiometers.

In the error analysis of this circuit, it can quickly be found that at 25°C, the nominal errors of the digital potentiometer have the highest potential to create the largest errors. This in shown in Table 1.

|                                    | Room<br>Temp. | Over -40°C<br>to 85°C<br>range |

|------------------------------------|---------------|--------------------------------|

| RPOT1<br>(±0.25 LSB typical error) | ±0.019 mV     | ±0.003 mV                      |

| RPOT2<br>(±0.25 LSB typical error) | ±0.019 mV     | ±0.003 mV                      |

| RPOT3<br>(±0.25 LSB typical error) | ±0.019 mV     | ±0.003 mV                      |

| Total typical error<br>at VREF-C   | ±0.057 mV     | ±0.009 mV                      |

**TABLE 1:** This table shows the nominal and temperature errors effecting adjustable voltage reference shown in Figure 6. Calculations assume A1 and A2 are ideal amplifiers, the MCP4X010 digital potentiometers are used and VDD = 5V. All values are referred to the output, VREF-C.

The errors of the first stage (including the amplifiers) are divided down by the second stage. Given this error analysis, the circuit in Figure 6 is accurate to 13.3 bits or  $\pm 0.057$  mV. This analysis does not take into account variations in VDD over temperature.

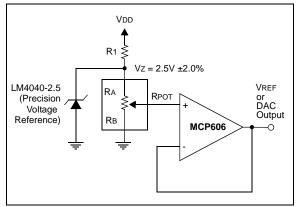

Another technique that can be used to design a precision adjustable voltage reference is shown in Figure 7.

**FIGURE 7:** A precision adjustable reference can be configured using a precision reference that is not adjustable along with a digital potentiometer. The value of R1 is set so that the current through the LM4040 does not go below its minimum operating current.

In this circuit, the variability of the power supply is stabilized with a precision voltage reference. Since the digital potentiometer is configured in the Voltage Divider mode, the errors at the output of the amplifier is similar to the errors discussed in Figure 5. The only difference being that the power supply is replaced with a precision reference. This configuration is often used when the digital potentiometer is used as a DAC.

## Offset Adjustment Circuits

Offset adjustment can be implemented in the analog circuit by injecting a voltage into the signal path with a simple voltage divider or a complete adjustable voltage reference.

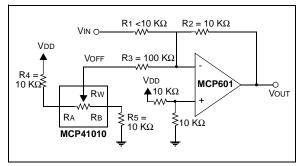

In Figures 8 and 9, a digital potentiometer is used to change the offset errors of a simple amplifier circuit.

**FIGURE 8:** A high resolution offset adjust circuit is implemented in this standard inverting amplifier configuration with the addition of a digital potentiometer, R3, R4 and R5.

In this circuit, the amplifier is configured in a inverting configuration. The transfer function for the input signal, VIN is equal to:

$$V_{OUT} = -V_{IN} \left(\frac{R_2}{R_1}\right) + \frac{V_{DD}}{2}$$

An offset voltage is injected with the same voltage divider that was used in the circuit in Figure 5.b. The transfer function of the offset voltage, VOFF is:

$$V_{OUT} = -V_{OFF} \left(\frac{R_2}{R_3}\right)$$

With the resistor values shown in the figure, the gain on the VIN is 10V/V and the gain on VOFF is 0.1V/V. With VDD = 5V, the LSB size of the offset adjust circuitry is 651  $\mu$ V.

With this configuration, the nominal errors and over temperature errors that are generated by the digital potentiometer is 10X smaller than the errors discussed in Figure 5.b.

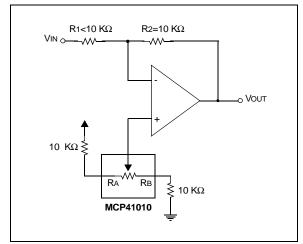

Another method of implementing an analog offset adjustment with a digital potentiometer is shown in Figure 9.

**FIGURE 9:** A lower resolution offset adjust circuit using a digital potentiometer can be used to adjust large system offsets.

In this circuit, the gain of the signal is equal to:

$$V_{OUT} = -V_{IN} \left(\frac{R_2}{R_1}\right)$$

And the gain of the offset adjust circuitry is equal to:

$$V_{OUT} = V_{DD}R_{POT-B} \frac{\left(1 + \frac{R_2}{R_1}\right)}{\left(R_{POT-AB} + R_2 + R_3\right)}$$

The offset adjustment circuit used in this application has the same topology as the circuit in Figure 5.b. Consequently, the errors due to this configuration is consistent with previous discussions.

## Gain Adjust Amplifier Circuits

Circuit gain errors can compromise the analog dynamic range of a circuit. These types of errors can be easily calibrated out of the system digitally with the microcontroller, however, the analog dynamic range is never fully utilized. Consequently, analog gain adjustments are done where the full dynamic analog range is needed.

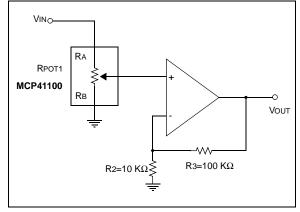

An example of an amplifier circuit that has an adjustable positive (noninverted) gain is shown in Figure 10.

**FIGURE 10:** An amplifier circuit designed with an adjustable noninverting gain.

In this circuit, the transfer function is:

$$V_{OUT} = V_{IN} \frac{\left(1 + \frac{R_3}{R_2}\right)}{\left(\frac{R_{POT1-B}}{R_{POT1-AB}}\right)}$$

The adjustable gain is implemented with the digital potentiometer, RPOT. Digital potentiometers that have higher nominal values are best suited for this circuit. Higher value resistances minimize the error that is contributed by the source resistance of VIN.

The maximum gain is equal to:

Gain (max) =

$$\left(1 + \frac{R_3}{R_2}\right) - \left(\frac{2^n - 1}{2^n}\right)$$

Using the values of resistors in Figure 10:

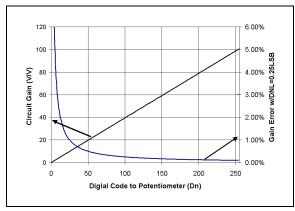

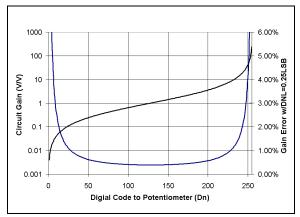

At room temperature, the digital potentiometer's DNL error effects the circuit gain accuracy with gains that are lower 10% of the range (assuming DNL (max) =  $\pm 0.25$  LSB). This relationship is shown graphically in Figure 11.

**FIGURE 11:** For the circuit in Figure 10, the gain vs. digital code is linear. The maximum possible gain error is logarithmic, decreasing with higher digital potentiometer codes.

In terms of temperature effects on the digital potentiometer in this configuration, the changes of RA and RB over temperature track at a rate of 800 ppm/°C (typ). Since these elements are configured as a mathematical ratio, this error is cancelled. The variance between the two elements over temperature is 1% (typ). This variance will be directly translated into gain error over temperature.

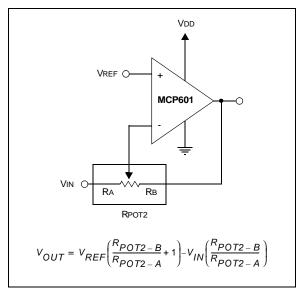

Another amplifier gain circuit that uses a digital potentiometer is shown in Figure 12. In this circuit, the amplifier circuit executes an inverting adjustable gain function.

**FIGURE 12:** This amplifier circuit uses a digital potentiometer to implement an adjustable inverting gain.

The circuit transfer function is:

$$V_{OUT} = V_{IN} \left( \frac{R_{POT2-A}}{R_{4-B}} \right) + V_{REF} \left( \frac{R_{POT2-A}}{R_{POT2-B}} \right) + 1$$

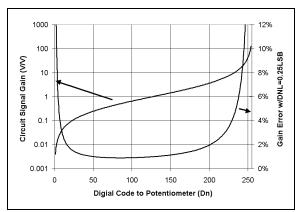

With this circuit, the gain function versus digital potentiometer code is nonlinear as shown in Figure 13.

**FIGURE 13:** The transfer function of VOUT to VIN of the circuit shown in Figure 12 has a nonlinear response over the code span of the digital potentiometer. This phenomena creates a circuit that gains the input signal below digital potentiometer codes of 128 and attenuates the signal with codes above 128.

The nominal accuracy of this gain cell is minimized because the two sides of the digital potentiometer are ratioed in the circuit transfer function. Any gain error at room temperature is due to the DNL error of the digital potentiometer. The maximum effects of the error is shown graphically in Figure 13.

In terms of temperature effects on the digital potentiometer in this configuration, RA and RB are configured as a mathematical ratio in the transfer function. This cancels the change in the 800 ppm/°C (typ) resistive element. The variance between the two elements over temperature is 1% (typ). This variance will be directly translated into gain error over temperature.

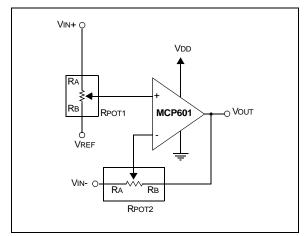

The circuits in Figure 10 and Figure 12 can be combined to build an adjustable gain difference amplifier much like the circuit shown in Figure 3. This configuration is shown Figure 14.

**FIGURE 14:** A difference amplifier that has stable resistor matching and temperature coefficients.

If the digital code setting for RPOT1 and RPOT2 are equal, the transfer function for this circuit is:

$$V_{OUT} = (V_1 - V_2) \left( \frac{R_{POTX-B}}{R_{X-A}} \right) + V_{REF}$$

The gain of this circuit (VOUT/(V1-V2)) versus the digital potentiometer code is shown graphically in Figure 15.

**FIGURE 15:** The gain of circuit in Figure 14 is greater than one with digital code settings larger than 128 and between zero and one for digital code settings less than 128. The gain error, due to typical DNL errors, is less than 1% between 28 and 229.

The temperature performance of this circuit is significantly improved over the circuit shown in Figure 3 because all of the resistors in this circuit are elements of the digital potentiometers. Once again, the common-mode rejection (CMR) error that is attributed to resistor mismatches in this circuit is equal to:

$$CMR = 100 \frac{\left(1 + \frac{R_1}{R_2}\right)}{\% \text{ of mismatch error}}$$

where (% of mismatch error) is the mismatch in the equation  $R_1/R_2 = R_3/R_4$ .

# CONCLUSION

The digital potentiometer has entered the market with clear advantages over the mechanical potentiometer. Its programmability allows to change the offset, gain and voltage references reliably as well as on the fly. The effects of variances of the absolute resistances and temperature drifts can be minimized if good circuit design techniques are used.

# AN691

NOTES:

-

"All rights reserved. Copyright © 2001, Microchip Technology Incorporated, USA. Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights."

#### Trademarks

The Microchip name, logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, KEELOQ, SEEVAL, MPLAB and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, FilterLab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM, MPLINK, MPLIB, PICDEM, ICEPIC, Migratable Memory, FanSense, ECONOMONITOR, Select Mode and microPort are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2001, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# WORLDWIDE SALES AND SERVICE

# AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

Rocky Mountain

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

Atlanta 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

Austin

Analog Product Sales 8303 MoPac Expressway North Suite A-201 Austin, TX 78759

Tel: 512-345-2030 Fax: 512-345-6085 Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

Boston Analog Product Sales Unit A-8-1 Millbrook Tarry Condominium 97 Lowell Road Concord, MA 01742 Tel: 978-371-6400 Fax: 978-371-0050

Chicago 333 Pierce Road, Suite 180

Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

**Dayton** Two Prestige Place, Suite 130 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

Tel: 937-291-1654 Fax: 937-291-9175 Detroit Tri Atria Office Building

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

Mountain View

Analog Product Sales 1300 Terra Bella Avenue Mountain View, CA 94043-1836 Tel: 650-968-9241 Fax: 650-967-1590

## New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335 **San Jose** Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955 **Toronto** 6285 Northam Drive, Suite 108

Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

# ASIA/PACIFIC

Australia Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing Microchip Technology Beijing Office Unit 915 New China Hong Kong Manhattan Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104 China - Shanghai Microchip Technology Shanghai Office Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 Hong Kong Microchip Asia Pacific RM 2101, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 India Microchip Technology Inc. India Liaison Office **Divyasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062 Japan Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

# ASIA/PACIFIC (continued)

Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

## EUROPE

#### Denmark

Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Arizona Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Arizona Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Germany Analog Product Sales Lochhamer Strasse 13 D-82152 Martinsried, Germany Tel: 49-89-895650-0 Fax: 49-89-895650-22 Italy Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883 United Kingdom Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/30/01

All rights reserved. © 2001 Microchip Technology Incorporated. Printed in the USA. 5/01 💭 Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, except as maybe explicitly expressed herein, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.