# AN676

## **Physical Slot Identification Techniques for the 24LCS61/62**

### INTRODUCTION

With the complexity of systems ever increasing, system designers are faced with new challenges in identifying and assigning system resources on-the-fly. Often a system will have multiple peripheral cards that must be added on demand to fill a processing requirement or configuration. These cards will need to be dynamically identified and added to the system's resource management database.

Various Plug and Play (PnP) solutions have been developed to meet these requirements. A common thread among PnP schemes is to have a lower bandwidth channel, such as the l<sup>2</sup>C bus, allocated as a means of interrogating newly added system cards. Through this data link, the system master can get or assign crucial information and calibration data from a specific card, without impacting the system's higher bandwidth bus.

# SOFTWARE ADDRESSABLE SOLUTIONS

The Microchip Technology Inc. 24LCS61/62 is a 1K/2K bit Serial EEPROM developed for applications that require non-volatile storage of data and to have many devices on the same bus but do not have the spare I/O pins required to address each device individually. These devices contain an 8-bit address register that is set upon power-up and allows the connection of up to 255 devices on the same bus. When the process of assigning ID values to each device is in progress, the device will automatically handle bus arbitration if more than one device is operating on the bus. In addition, an external open drain output pin (EDS) is available that can be used to enable other circuitry associated with each individual system. See the Microchip 24LCS61/ 62 (DS21226) data sheet for further information on these devices.

### A PNP SCENARIO APPLICATION

This application will utilize a system made of multiple circuit cards plugged into a backplane. A common high bandwidth bus and an  $l^2C^{TM}$  bus will interconnect the slots of the backplane. The system master must create a table that correlates the card type inserted into each slot. To do this, the system master needs to read the information about each board in the system. This information is stored in the 24LCS61/62 on that board. The system master also needs to determine the physical slot number that the board is plugged into. Listed below are five methods for determining physical slot locations.

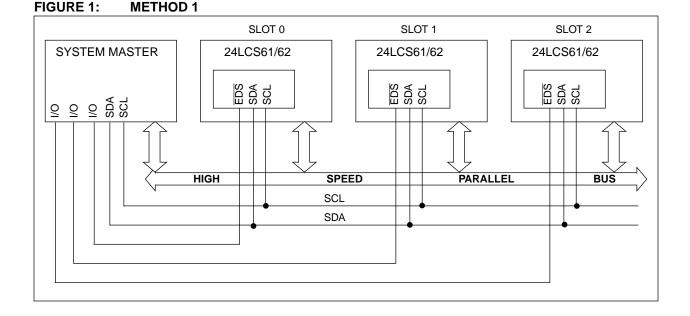

# Method 1: Direct Connection of the $\overline{\text{EDS}}$ Pins to the System Master

The simplest method to determine the physical slot location is to route the  $\overline{\text{EDS}}$  output pin from each card back to the system master. This physical connection, or return line, serves as a fixed slot identifier. Each device on the bus would then be identified by connecting this

line to a unique input pin on the system master. After performing the arbitration process, the system master can toggle the output of the  $\overline{\text{EDS}}$  pin on a particular device, and sense the resulting physical slot location indicated by poling the I/O pins.

This method requires equal number of return lines as there are devices on the bus.

I<sup>2</sup>C is a trademark of Philips Corporation.

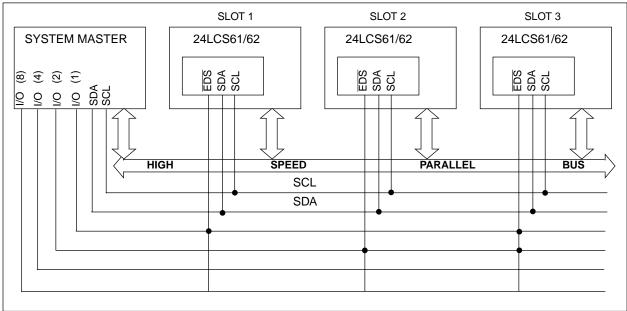

## Method 2: Encoded Return Lines to System Master

Dedicated return lines can be encoded to identify physical slots. The encoding is made by the connections, or lack of connections, between the EDS pin on a particular device, and the return lines going back to the system master. These connections take place on the main bus backplane. After arbitration, the system master would activate the EDS pin on a single device in sequence, and read the encoded value on the return lines connected to the I/O pins. The physical slot identifier will be returned in binary coded form. In the example shown below, asserting the EDS pin on the device in slot 1 will yield the binary "0001", indicating to the master that this device is in slot 1. In this method, N return lines can encode a maximum of  $2^{N}$  devices on the bus.

This method has the advantage that it only consumes one pin on the connector between the board and the backplane. Therefore, the entire bus to identify and interrogate boards in the system will only require three pins (SCL, SDA and  $\overline{EDS}$ ) on the backplane connector.

For further reliability assurance, the designer can drop the code which has no physical connections to any return lines (i.e., "0000"). This would make every valid slot identifier assert at least one return line. This eliminates the possibility of a faulty device being erroneously assigned the '0' slot identifier. This lowers the total allowable number of slots given N return lines to  $2^{N} - 1$ .

### FIGURE 2: METHOD 2

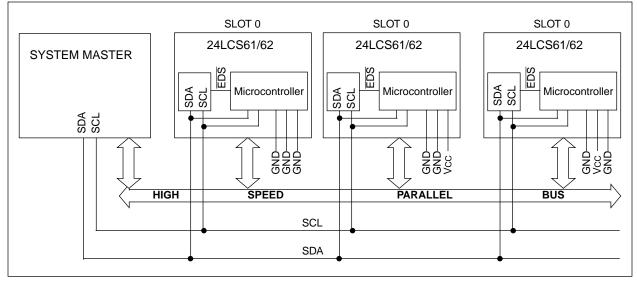

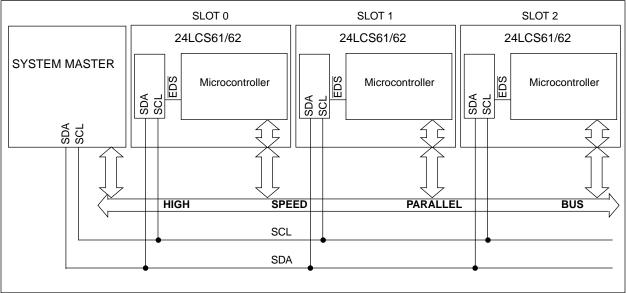

### Method 3: Microcontroller Slot Address Sensing, and Serial Communication

Each card contains a 24LCS61/62 nonvolatile memory device, and a dedicated microcontroller (this example uses the Microchip PIC16C57) for transmitting slot information serially over the  $I^2C$  bus. Both are connected to the backplane's  $I^2C$  bus. The microcontroller on the card uses two dedicated I/O lines for SDA and SCL connections. This provides a feedback path for determining the physical slot in which a card resides. Other dedicated I/O lines by the microcontroller to sense a slot number from the dedicated connector pins. These pins are encoded with the slot identifier on the backplane.

First, the system master processor will initiate the 24LCS61/62 arbitration process until all memory devices are assigned unique ID. Next, the system

master will sequentially address each 24LCS61/62 and assert the EDS pin. The EDS line serves as a select line for that particular microcontroller, and puts that microcontroller into a state where it will respond to commands from the system master. The microcontroller can wake up to a normally formatted  $I^2C$  command and respond with the physical slot identifier. Because the memory devices on the bus wake up to 06XH, and the microcontroller wakes up to 0AXH, there will never be a bus contention issue between them.

The number of I/O lines dedicated to sensing physical slot information will determine the number of devices addressable on the bus. If the microcontroller has eight I/O lines then the full number (255) of 24LCS61/62's can be addressed.

#### FIGURE 3: METHOD 3

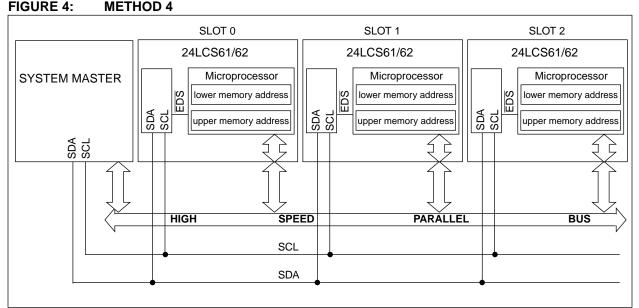

## Method 4: Virtual Memory Addressing on Cards

This method is applicable when all communication between boards is accomplished by transfers between memory spaces on each board. In this scenario, the system master starts by querying the I<sup>2</sup>C bus looking for unassigned 24LCS61/62 devices. This is done by repeatedly sending the assign address command and checking for acknowledging devices. If a device acknowledges, then a software address is assigned to that device after the arbitration cycle has been completed. The system master can then either continue assigning software addresses to any remaining 24LCS61/62 devices on the bus, or it may immediately assign a "virtual memory address" to the board associated with the just assigned 24LCS61/62 device (hereafter referred to as the "slave board"). The first step of assigning the virtual address is to read the configuration data from the 24LCS61/62 device. This tells the system master the amount of virtual memory space to reserve for the slave board. The system master would then issue a command to the 24LCS61/62

## FIGURE 4: METHOD 4

device with the OE bit set to '1', which enables the EDS pin on the 24LCS61/62 device. The EDS pin is tied to an input on the slave board microcontroller which signals it to enter a "receive virtual address" mode. Once the slave board is ready to receive the virtual address the system master sends the necessary information out over the main system bus to be received by the current slave board. Any necessary communication between the system master and the slave board is completed and the system master then issues a command to the 24LCS61/62 device with the OE bit set to a '0', which signals the slave board microcontroller to terminate the assign virtual memory address mode. This sequence is then repeated until no unassigned 24LCS61/62 devices remain on the I<sup>2</sup>C bus. Once the process is complete the slave board can be addressed by its virtual address.

This method has the advantage of requiring only one I/O pin on the slave board microcontroller, and may be used when it is not necessary to know which physical slot a slave board is in.

### Method 5: Microcontroller Slot Address Sensing and Communication over System Bus

This method may be used if the physical slot must be identified and thus the slot ID number is hard-coded into the slave board connector. In this scenario the EDS pin of the 24LCS61/62 device is used to enable the slave board microcontroller in the same way as in the method above, however, once enabled, the slave board microcontroller reads the hard coded physical slot number and then sends this information to the system master via the system bus. From that point on the slave board can be addressed by using its slot ID number.

This method again requires only a single I/O on the slave board microcontroller, and is effective when the physical location of a given slave board must be known.

## CONCLUSION

The Microchip 24LCS61/62 is a powerful building block in creating a board identification solution for multiboard systems. The methods outlined above are generic in nature, and meant to serve as a starting point for development of individual solutions for physical slot identification.

NOTES:

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

**Corporate Office** Microchip Technology Inc. 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-786-7200 Fax: 480-786-7277 Technical Support: 480-786-7627 Web Address: http://www.microchip.com

#### Atlanta

Microchip Technology Inc. 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

Microchip Technology Inc. 5 Mount Royal Avenue Marlborough, MA 01752 Tel: 508-480-9990 Fax: 508-480-8575

#### Chicago

Microchip Technology Inc. 333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

#### Dallas

Microchip Technology Inc. 4570 Westgrove Drive, Suite 160 Addison, TX 75248 Tel: 972-818-7423 Fax: 972-818-2924

#### Dayton

Microchip Technology Inc. Two Prestige Place, Suite 150 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

#### Detroit

Microchip Technology Inc. Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

#### Los Angeles

Microchip Technology Inc. 18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

#### **New York**

Microchip Technology Inc. 150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

## **AMERICAS** (continued)

Toronto

Microchip Technology Inc. 5925 Airport Road, Suite 200 Mississauga, Ontario L4V 1W1, Canada Tel: 905-405-6279 Fax: 905-405-6253 ASIA/PACIFIC

Hong Kong Microchip Asia Pacific Unit 2101, Tower 2 Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2-401-1200 Fax: 852-2-401-3431 Beijing Microchip Technology, Beijing Unit 915, 6 Chaoyangmen Bei Dajie Dong Erhuan Road, Dongcheng District New China Hong Kong Manhattan Building Beijing 100027 PRC Tel: 86-10-85282100 Fax: 86-10-85282104 India Microchip Technology Inc. India Liaison Office No. 6, Legacy, Convent Road Bangalore 560 025, India Tel: 91-80-229-0061 Fax: 91-80-229-0062 Japan

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa 222-0033 Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea

168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934 Shanghai

Microchip Technology RM 406 Shanghai Golden Bridge Bldg. 2077 Yan'an Road West, Hong Qiao District Shanghai, PRC 200335 Tel: 86-21-6275-5700 Fax: 86 21-6275-5060

#### ASIA/PACIFIC (continued)

Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore 188980 Tel: 65-334-8870 Fax: 65-334-8850

Taiwan, R.O.C

Microchip Technology Taiwan 10F-1C 207 Tung Hua North Road

Taipei, Taiwan, ROC

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139 **EUROPE**

### **United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5858 Fax: 44-118 921-5835

#### Denmark

Microchip Technology Denmark ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

#### France

Arizona Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann-Ring 125 D-81739 München, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

11/15/99

DNV MSC **DNV Certification. Inc** USA The Netherland Accredited by the RvA ANSI \* RAB CCRED DIN ISO 9001 / QS-9000 **REGISTERED FIRM**

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro<sup>®</sup> 8-bit MCUs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

Printed on recycled paper. All rights reserved. © 1999 Microchip Technology Incorporated. Printed in the USA. 11/99

Information contained in this publication regarding device applications and the like is intended for suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infiningement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No incorpose and no version of the otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.