**Implementation of the Data Encryption Standard Using PIC17C42**

Authors: Al Lovrich Mark Palmer Microchip Technology Inc.

# INTRODUCTION

In January 1977, The United States government adopted a product cipher developed by IBM as its official encryption standard [1]. This algorithm, called the Data Encryption Standard (DES), has been adopted as a worldwide standard for data encryption by ISO (International Standards Organization) [2, 3]. This application note describes the implementation of the DES algorithm on PIC17C42.

# THE DATA ENCRYPTION STANDARD

The DES algorithm is a substitution cipher which takes a block of 64 bits of input (plaintext) into a unique block of 64 bits of output (ciphertext), under the control of a 64-bit key, which is known only to the people intended to read the message. In this system, plaintext information is divided into several blocks which are then operated upon independently to generate a sequence of ciphertext blocks. The basic idea behind DES is to build a strong system out of simple, individually weak, components. The DES encryption system is based on a system of transpositions and permutations. The permutation box or P-box, is used to transpose, or map a sequence of input values to another sequence of values of the same length. Substitutions are performed by what are called S-boxes. A combination of the S-boxes and P-boxes can be viewed as a decoder/coder operation, where the output is simply a linear mapping of the input values. Each combination of the S-box and P-box comprises a single weak component of the algorithm. By including a sufficiently large number of stages in the product cipher, the output can be made to be a nonlinear function of the input.

The mapping of input to output is one-to-one and invertible, since the encrypted messages can be decrypted. The DES has three distinct components: key schedule, cipher function, and invertibility.

# **KEY SCHEDULE**

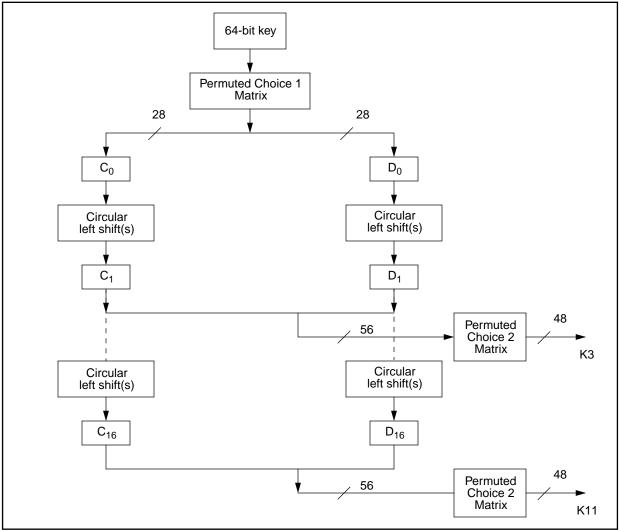

The DES uses a 64-bit key for encryption and decryption process. Initially, the original 64-bit key is reduced to 56-bit by ignoring every eighth bit. In general these bits are used as parity bits to make sure that there were no errors when entering the key or during key transmission. After the 56-bit key is extracted a different 48-bit key, referred to as subkey, is generated for each of the 16 rounds of the DES. These keys, K<sub>i</sub>, are determined as shown in Figure 1. The 56-bit key is divided into two 28-bit halves C<sub>i</sub> and D<sub>i</sub> which are then shifted left by either 1 or 2 digits, depending on the round. Table 1 shows the number of circular left shifts for C<sub>i</sub> and D<sub>i</sub> halves. After the shifting operation, 48 out of the 56 bits are selected. Since this operation permutes the order of the bits as well as selecting a subset of the original bits, it is called compression permutation or permuted choice. The permuted choice 1 and permuted choice 2 matrices are shown in Figure 2 and Figure 3 respectively.

### TABLE 1: LEFT SHIFTS FOR KEY GENERATION

| Iteration | # of left shifts |

|-----------|------------------|

| 1         | 1                |

| 2         | 1                |

| 3         | 2                |

| 4         | 2                |

| 5         | 2                |

| 6         | 2                |

| 7         | 2                |

| 8         | 2                |

| 9         | 1                |

| 10        | 2                |

| 11        | 2                |

| 12        | 2                |

| 13        | 2                |

| 14        | 2                |

| 15        | 2                |

| 16        | 1                |

# FIGURE 1: KEY GENERATION

| l | FIGURI | E 2: |    | ERMU<br>Atrix | '  | CHOI | CE 1 |    |

|---|--------|------|----|---------------|----|------|------|----|

|   | 57     | 49   | 41 | 33            | 25 | 17   | 9    | 1  |

|   | 58     | 50   | 42 | 34            | 26 | 18   | 10   | 2  |

|   | 59     | 51   | 43 | 35            | 27 | 19   | 11   | 3  |

|   | 60     | 52   | 44 | 36            | 63 | 55   | 47   | 39 |

|   | 31     | 23   | 15 | 7             | 62 | 54   | 46   | 38 |

|   | 30     | 22   | 14 | 6             | 61 | 53   | 45   | 37 |

|   |        |      |    |               |    |      |      |    |

| FIGURE 3: |    |    |    | PERMUTED CHOICE 2<br>MATRIX |    |    |    |    |  |

|-----------|----|----|----|-----------------------------|----|----|----|----|--|

|           | 14 | 17 | 11 | 24                          | 1  | 5  | 3  | 28 |  |

|           | 15 | 6  | 21 | 10                          | 23 | 19 | 12 | 4  |  |

|           | 26 | 8  | 16 | 7                           | 27 | 20 | 13 | 2  |  |

|           | 41 | 52 | 31 | 37                          | 47 | 55 | 30 | 40 |  |

|           | 51 | 45 | 33 | 48                          | 44 | 49 | 39 | 56 |  |

|           | 34 | 53 | 46 | 42                          | 50 | 36 | 29 | 32 |  |

# **CIPHER FUNCTION**

The strength of the DES is based on the cipher function component. This is a fixed, highly nonlinear function which guarantees that each bit of the ciphertext depend on every bit of the plaintext and every bit of the key.

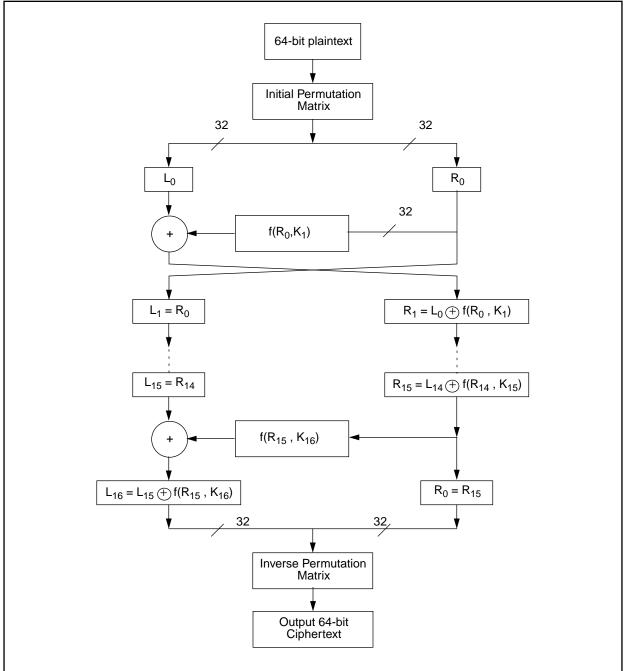

After an initial permutation, the 64-bit block of plaintext is broken into a right half and left half, each 32 bits long. This step is followed by 16 identical rounds of operation, called function *f*, that combines the data with a 48-bit key,  $K_{j}$ . At each stage *i*, the inputs are the left block  $L_{i-1}$  and the right block  $R_{i-1}$  of the previous stage, and the outputs are the left shift block  $L_i$  and right block  $R_i$  of this stage. The outputs of  $L_i$  and  $R_i$  of each stage are computed from  $L_{j-1}$  and  $R_{j-1}$ , and a subkey  $K_i$  that is generated from the encryption key. In other words a round of the DES can be shown as:

$L_i = R_i$

$$R_i = L_{i-1} XOR f(R_{i-1}, K_i)$$

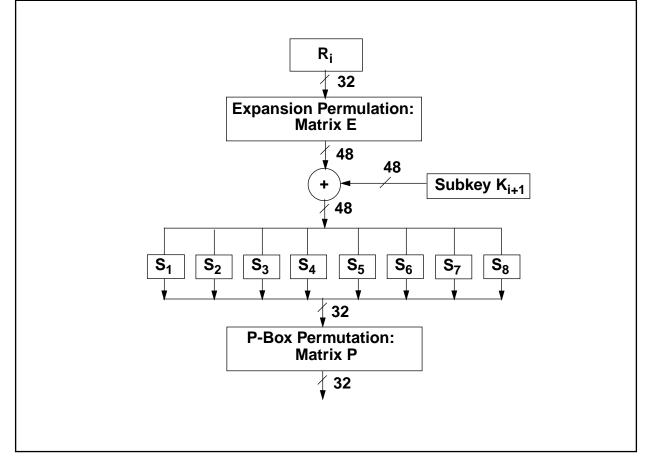

All the complexity of the DES algorithm lies in the function f, as shown in Figure 4. The function has four steps that are carried out in sequence. First a 48-bit number, *E*, is constructed by expanding the 32-bit previous right value,  $R_{i-1}$ , according to a fixed transposition and duplication rule. Then,  $K_i$  and  $R_{i-1}$  are XORed together, generating a 48-bit result. This output is then partitioned into eight groups of 6-bits each, each of which is fed into a different S-box or substitution box. The S-boxes generate four instead of six outputs. In other words, the 64-bit input is mapped into a 32-bit output. Each S-box is a table of 4 rows and 16 columns. Each entry in the box is a 4-bit number. The six input bits of the S-box specify under which row and column number to look for the output. Figure 7 shows the 8 S-boxes.

The six input bits specify an entry in the Sbox in a particular fashion as follows: the first and last bits of the sequence, taken together, represent a number between 0 and 3 (row entry), while the middle 4-bits represent a number between 0 and 15 (column entry). The output is simply the entry that corresponds to the (row, column) entry. For example, that the input to the first S-box is the binary sequence 110010. The first and last bits combine to form 10 which corresponds to the third row of the S-box. The middle 4-bits are combined to form 1001 which corresponds to the ninth column of the for 110010. The substitution boxes are the most critical step in the DES algorithm and more than anything else give DES its security.

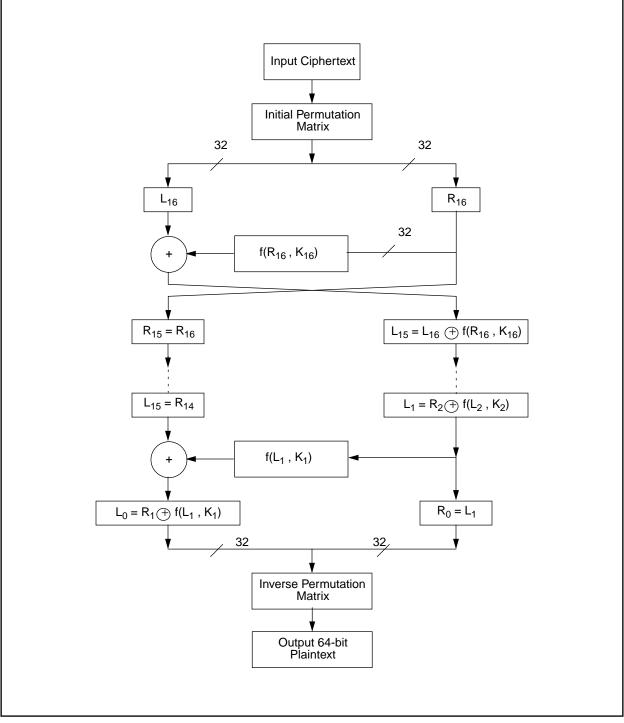

Finally, the last stage consists of a permutation stage that generates a 32-bit output. After the 16 rounds, the left and right halves are joined, and a final permutation generates the ciphertext. The final permutation is the inverse of the initial permutation. Figure 10 shows a block diagram of the enciphering portion of the algorithm. The reverse process of deciphering is shown in Figure 11. The initial permutation and inverse initial permutation matrices in Figure 10 are shown in Figure 8 and Figure 9. Where the algorithm requires bit manipulation of a stream of data according to a matrix, the matrix is read from left to right, top to bottom, and interpreted as the bit position in the output block. For example, the initial permutation matrix transposes bit1 to bit58, bit2 to bit50, bit3 to bit42, etc.

# INVERTIBILITY

The DES cipher function is not necessarily invertible, meaning to decode a message, it is not necessary to recover the input to the cipher function from its output and a knowledge of the key. In fact the cipher function must be highly nonlinear to be resistant to plaintext attack (a method used for breaking a given algorithm). Invertibility of the DES is that one half-word of the output is precisely the bit configuration which was used to encode the other half, with the aid of the particular stage subkey. Therefore, by using the subkeys in reverse order, the encryption process can be reversed. This is really the reason that one half-word is always passed through unchanged - to provide the means of decrypting the other half-word.

# PIC17C42 IMPLEMENTATION OF DES

CPU processing is required to generate the encryption key into the DES subkeys. The 64-bit encryption key is reduced to 56-bits, by ignoring every eighth bit, usually used as parity bit.

The majority of the DES code is for the Implementation of the permutation of the block of bits. The 56-bits of the key, stored in K1 through K8, scrambled-bit output is stored in the eight bytes D0-D7. The scrambling is accomplished by constructing D0-D7, one bit at a time. This is accomplished by initializing the D0 to D7 locations to a known state (cleared). Then the 64-bits of plain text are processed through the Initial Permutation Matrix (IP), which permutes the plain text and divides the information into two 32-bit blocks.

The use of Indirect addressing and the PICmicro<sup>™</sup> single word instructions allows tight efficient coding of the DES algorithm. These bit testing capabilities allows the same code structure to generate the different subkey blocks. This permutation macro looks like:

| Permute | Macro  | KEY,TEST,BIT |

|---------|--------|--------------|

|         | BTFS C | KEY,TEST,BIT |

|         | BSF    | INDOF0,BIT   |

|         | endm   |              |

Where KEY is the DES key and TEST is the bit is the KEY being tested. If the KEY<TEST> bit is set, then the bit position (BIT) in the data location pointed to by INDF0 is set.

The main algorithm requires that the 16 subkeys, each 48-bits long, be generated. These 16 subkeys are then used at the 16 stages of the algorithm.

Using the generated subkeys, the incoming stream of bits can be encrypted or decrypted. Table 2 shows the requirements of the DES algorithm.

### TABLE 2: DES ALGORITHM REQUIREMENTS

|                                            | Execution                  | time                  |       |

|--------------------------------------------|----------------------------|-----------------------|-------|

| Function                                   | Program<br>Memory<br>words | Instruction<br>cycles | ms    |

| Key management<br>and subkey<br>generation | 382                        | 2729                  | 0.436 |

| Encryption                                 | 789                        | 7714                  | 1.234 |

A bit rate of about 51 Kbps baud can be achieved, with a device utilization of 100%. This makes the PIC17C42 a price/performance leader for DES algorithms.

# CONCLUSION

We have demonstrated the implementation of the DES algorithm on the PIC17C42 microcontroller. The 160 ns cycle time of the PIC17C42 makes possible a half-duplex rate of 51 Kbps for the DES. This rate is as good or superior to other implementations of the algorithm. The high performance of the PIC17C42 provides a low-cost alternative to many dedicated solutions resulting in minimum system cost because of the programmability of the device.

### References

- NBS FIPS PUB 46, "Data Encryption Standard," National Bureau of Standards, US Department of Commerce, January 1977.

- SO DIS 8730, "Banking Requirements for Message Authentication (Wholesale)," Association for Payment Clearing Services, London, July 1987.

- 3. ISO DIS 8732, "Banking Key Management (Wholesale)," Association for Payment Clearing Services, London, December 1987.

| FIC | GURE 5:           | : <b>M</b>     | ATRIX  | Е             |                 |       |      | F   | IGURE      | E 7:     |

|-----|-------------------|----------------|--------|---------------|-----------------|-------|------|-----|------------|----------|

|     | 32                | 1 2            | 3      | 4             | 5               | 4     | 5    | 1 Г | /*         | S6 */    |

|     | 6                 | 7 8            | 9      | 8             | 9               | 10    | 11   |     | 12         | 2 1 1    |

|     | 12 1              | 3 12           | 13     | 14            | 15              | 16    | 17   |     | 10         | 15       |

|     | 16 1              | 7 18           | 19     | 20            | 21              | 20    | 21   |     | 9          | 14 1     |

|     | 22 2              | 23 24          | 25     | 24            | 25              | 26    | 27   |     | 4          | 32       |

|     | 28 2              | .9 28          | 29     | 30            | 31              | 32    | 1    |     | /*         | S7 */    |

|     | GURE 6            | . M            | ATRIX  | D             |                 |       |      | -   |            | 11 2     |

|     |                   | . IVI.<br>7 20 | 21     | 29            | 12              | 28    | 17   | ן ר | 13         | 0 1      |

|     | 1 1:              |                | 26     | 5             | 18              | 31    | 10   |     | 1          | 4 11     |

|     |                   | <br>3 24       | 14     | 32            | 27              | 3     | 9    |     | 6          | 11 1     |

|     | 19 13             | -              | 6      | 22            | 11              | 4     | 25   |     |            |          |

|     |                   |                |        |               |                 |       |      |     | /*         | S8 */    |

| FIC | SURE 7            |                | MATR   | ICES          |                 |       |      | - I | 13         | 28       |

|     | /* S1 */          |                |        |               |                 |       |      |     |            | 15 1     |

|     |                   | 13 1 2         |        |               |                 |       | 07   |     |            | 11 4     |

|     | 0 15              |                | 2 13 1 |               |                 |       | 38   |     | 2          | 1 14     |

|     |                   | 4813<br>824    | 6 2 11 |               |                 |       | 50   | L   |            |          |

|     | 15 12             | 024            | 5 1 7  | 5 11          | 5 14            | 10 0  | 0 15 | F   | IGURE      | E 8:     |

|     | /* S2 */          | ,              |        |               |                 |       |      | Г   | <b>E</b> 0 | <u> </u> |

|     | 15 1              | 8 14 6         | 11 3 4 | 97            | 2 13            | 12 0  | 5 10 |     | 58<br>60   | 50       |

|     | 3 13              | 4715           | 2 8 14 | 12 0          | 1 10            | 69    | 11 5 |     | 60<br>62   | 52       |

|     | 0 14              | 7 11 10        | 4 13   | 158           | 12 6            | 93    | 2 15 |     | 62         | 54       |

|     | 13 8 <sup>-</sup> | 10 1 3         | 15 4 2 | 11 6          | 7 12            | 05    | 14 9 |     | 64         | 56       |

|     |                   |                |        |               |                 |       |      |     | 57         | 49       |

|     | /* S3 */          | ,              |        |               |                 |       |      |     | 59         | 51       |

|     | 10 0              | 9 14 6         | 3 15 5 | 5 1 13        | 12 7            | 11 4  | 28   |     | 61         | 53       |

|     | -                 |                | 4 6 10 |               |                 |       |      |     | 63         | 55       |

|     |                   | 4981<br>1306   |        |               |                 |       |      | F   | IGURE      | E 9:     |

|     |                   |                |        |               |                 |       |      | Г   | 40         | 8        |

|     | /* S4 */          | ,              |        |               |                 |       |      |     | 39         | 7        |

|     | 7 13 <sup>-</sup> | 14 3 0         | 6 9 10 | 12            | 85 <sup>°</sup> | 11 12 | 4 15 |     | 38         | 6        |

|     | 13 8 <sup>-</sup> | 11 5 6         | 15 0 3 | 47            | 2 12            | 1 10  | 14 9 |     | 37         | 5        |

|     | 10 6              | 9 0 12         | 11 7 1 | 3 15 <i>°</i> | 1 3 14          | 52    | 84   |     | 36         | 4        |

|     | 3 15              | 0 6 10         | 1 13 8 | 94            | 5 11            | 12 7  | 2 14 |     | 35         | 3        |

|     |                   |                |        |               |                 |       |      |     | 34         | 2        |

|     | /* S5 */          |                | o 4 -  |               | o ·-            | 40.5  |      |     | 33         | 1        |

|     |                   | 4 1 7 1        |        |               |                 |       |      | l l |            | •        |

|     |                   | 2 12 4         |        |               |                 |       |      |     |            |          |

|     | 42′               | 1 11 10        | 13 / 8 | 15 9          | 12 5            | 63    | 0 14 |     |            |          |

S matrices (CONT.)

|    |    | 1017 | 111112 | •  |    |    |   |  |

|----|----|------|--------|----|----|----|---|--|

| 58 | 50 | 42   | 34     | 26 | 18 | 10 | 2 |  |

| 60 | 52 | 44   | 36     | 28 | 20 | 12 | 4 |  |

| 62 | 54 | 46   | 38     | 30 | 22 | 14 | 6 |  |

| 64 | 56 | 48   | 40     | 32 | 24 | 16 | 8 |  |

| 57 | 49 | 41   | 33     | 25 | 17 | 9  | 1 |  |

| 59 | 51 | 43   | 35     | 27 | 19 | 11 | 3 |  |

| 61 | 53 | 45   | 37     | 29 | 21 | 13 | 5 |  |

| 63 | 55 | 47   | 39     | 31 | 23 | 15 | 7 |  |

### FIGURE 9: **INVERSE PERMUTATION** MATRIX

| 40 | 8 | 48 | 16 | 56 | 24 | 64 | 32 |

|----|---|----|----|----|----|----|----|

| 39 | 7 | 47 | 15 | 55 | 23 | 63 | 31 |

| 38 | 6 | 46 | 14 | 54 | 22 | 62 | 30 |

| 37 | 5 | 45 | 13 | 53 | 21 | 61 | 29 |

| 36 | 4 | 44 | 14 | 52 | 20 | 60 | 28 |

| 35 | 3 | 43 | 13 | 51 | 19 | 59 | 27 |

| 34 | 2 | 42 | 12 | 50 | 18 | 58 | 26 |

| 33 | 1 | 41 | 11 | 49 | 17 | 57 | 25 |

11 8 12 7 1 14 2 13 6 15 0 9 10 4 5 3

FIGURE 10: DES ENCRYPTION BLOCK DIAGRAM

FIGURE 11: DES DECRYPTION BLOCK DIAGRAM

NOTE: The PIC17C42 code implementing the DES is not published because it falls within the U.S. Department of State Export Control Regulations.

Please contact your local Microchip sales office to obtain a copy of the code.

NOTE: The PIC17C42 code implementing the DES is not published because it falls within the U.S. Department of State Export Control Regulations.

Please contact your local Microchip sales office to obtain a copy of the code.

# **APPENDIX A:**

Note: The PIC17C42 code implementing the DES is not published because it falls within the U.S. Department of State Export control Regulations.

Please contact your local Microchip sales office to obtain a copy of the code.

### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# WORLDWIDE SALES AND SERVICE

### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit Tri-Atria Office Building

32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

# 2767 S. Albright Road

Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387 Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335 San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza

223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

### India

Microchip Technology Inc. India Liaison Office **Divvasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### EUROPE

Denmark

Microchip Technology Nordic ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

### United Kinadom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02