# **TC7135 Microprocessor Interface**

Author: W

Wes Freeman, Microchip Technology, Inc.

### INTRODUCTION

Many data acquisition systems require both a visual display and a computer interface. The TC7135 from Microchip Technology is a 4-1/2 digit Analog-to-Digital converter (ADC) which can easily provide both of these functions. The TC7135's multiplexed BCD outputs interface easily to low cost LED or LCD decoder/drivers, such as the TC7211A. Also, the TC7135's data outputs simplify computer interfacing.

This application note will present both the hardware and software required to interface the TC7135 to a microprocessor. The circuit was developed for a 6502 $\mu$ P and 6522 I/O port, but the design can easily be modified for other  $\mu$ Ps and I/O ports.

The TC7135 has several features which make it an attractive choice for data acquisition where speed is not an overriding consideration. The analog features include:

- Low Roll-Over Error ..... ±1 count

- Valid Polarity at 000 reading (the + and zero states give an extra bit of resolution.

- Negligible zero drift definitely not the case with a bipolar DAC/SAR type ADC.

- The dual-slope conversion method rejects 50Hz, 60Hz and 400Hz noise.

- The ratiometric reference and differential inputs provide flexible transducer interfacing.

The TC7135 T also has features that simplify system design:

- Easy μP interfacing

- Overrange and underrange flags for autoranging and process control decisions

- Operation from ±5V supplies, with only 10mW typical power dissipation

- TTL compatible outputs (1.6mA sink current)

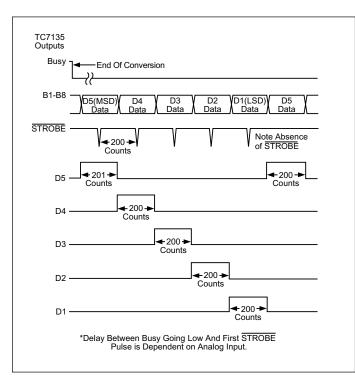

The TC7135 provides output signals which, together with one port of an LSI I/O chip, simplify a microprocessor interface. The relationship between the various TC7135 outputs is shown in Figure 1. The specific functions of these outputs are as follows:

### **TC7135 Pin Function**

- B1-B8 BCD coded data is output on the B1-B8 pins.

- DS5-DS1 Digit Select 5 (most significant digit) through Digit Select 1 (least significant) go high as data on B1-B8 becomes valid for that digit.

- STROBE For the first digit scan after a conversion STROBE goes low (for 1/2 clock period) in the middle of each digit strobe. After five pulses, STROBE stays high until the next conversion is complete.

- BUSY BUSY is high while the TC7135 is in Integrate or Deintegrate phases of a conversion. The falling of BUSY can, therefore, be used as an end of conversion signal.

- POL POLARITY is high if the analog input polarity is positive.

- OR OVERRANGE goes high if the analog input is greater than full scale (reading >20,000).

- UR While UNDERRANGE goes high if the reading is 1,800 or less.

The TC7135 also has a RUN/HOLD input. If RUN/HOLD is held low, the converter will remain in the auto-zero phase. A new conversion will not begin until RUN/HOLD goes high. This input can be used to generate conversions on command.

## **INTERFACE HARDWARE**

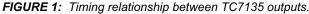

The complete TC7135 to SYP6522 interface schematic is shown in Figure 2. BCD data, POL, OR, UR, and DS5 are connected to the 6522's PA0 through PA7 inputs. The TC7135's STROBE output interrupts the microprocessor via the 6522's CA1 interrupt. RUN/HOLD can be controlled by programming CA2 as an output.

At first glance, the circuit may appear incomplete because digit selects DS4 through DS1 are not connected. However, DS5 is the only digit select required. As mentioned previously, there are only 5 STROBE pulses per conversion cycle, with the first STROBE occurring during DS5. The  $\mu$ P decodes the logical "AND" of DS5 and STROBE (DS5 • STROBE) as a conversion complete signal.

If the  $\mu P$  finds (DS • STROBE) true upon responding to an interrupt, an "end of conversion" is assumed and assembling of BCD data from the TC7135 begins. Each of the next four interrupts will provide another BCD digit. The  $\mu P$  counts interrupts in a register and stores the corresponding BCD data in successive memory locations. After five STROBE pulses, all BCD data has been transferred to the  $\mu P$  and conversion is complete.

One constraint of this interface method is that the  $\mu$ P must respond to each digit's interrupt before the next digit becomes valid. The 6522's CA1 input can be programmed to latch data into Port A, as well as provide an interrupt to the  $\mu$ P. Since latched data remains valid until the next STROBE pulse, the  $\mu$ P has the full interval between STROBE pulses to service each interrupt. STROBE pulses are 200 clock cycles apart. A TC7135 clock frequency of 100kHz will allow the  $\mu$ P two milliseconds (10 $\mu$ sec x 200 clock cycles) to respond to each interrupt without losing data.

### **INTERFACE SOFTWARE**

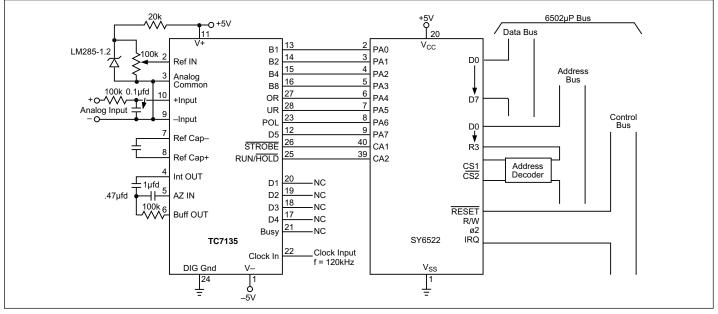

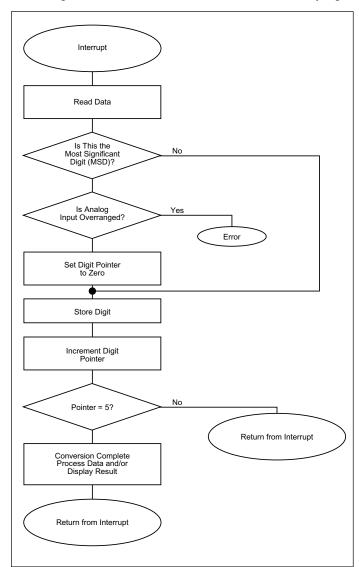

Software for the TC7135 to 6502 interface can be divided into three routines: (1) Programming the 6522's Port A for latched input and interrupt from CA1; (2) the interrupt service routine which actually acquires and stores BCD data from the TC7135; (3) display or manipulation of the acquired data. Figure 3 is a 6502 assembly language listing of the first two routines. An interrupt service routine flow chart is shown in Figure 4. Since the end of a digit scan leaves 5 digits of BCD data in successive memory locations, the user will find the interface software easy to incorporate into a specific display or manipulation routine.

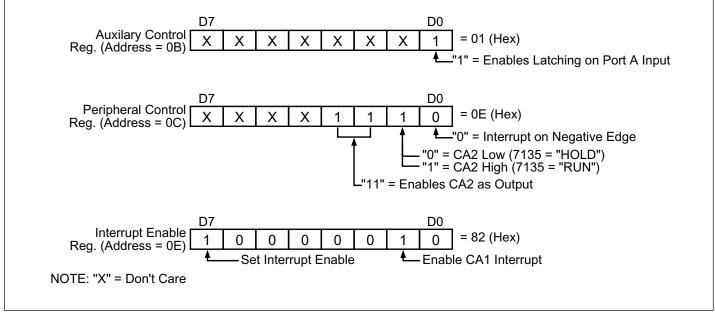

The 6522 I/O port must be programmed before data can be received from the TC7135. The code in Figure 3, beginning at location "SET-UP," writes data into the 6522's control registers to enable the following functions (1) Port A will be latched input, controlled by input of CA1; (2) CA2 will be an output, programmed high (TC7135 in "RUN" mode); (3) Interrupt enabled on the falling edge of CA1. The function of data written to each 6522 register is defined in Figure 5.

When programmed for interrupt operation, the 6522 will pull its IRQ output low on the falling edge of each STROBE pulse from the TC7135. Assuming interrupts are enabled, IRQ going low will cause the  $6502\mu$ P to load the address of an interrupt service routine from memory locations FFFE and FFFF. This routine will typically identify the interrupting device, determine its priority and jump to a program to service the interrupt. The user must provide software to vector interrupts coming from the TC7135 to the service routine located at location "INTVEC" of Figure 3. The TC7135-6522 hardware can accommodate interrupt service delays of up to 2msec, so a relatively low-priority interrupt status can be used.

FIGURE 2: TC7135 to 6502µP interface schematic.

|                | ;                                                                                                                             |                                                                                                              |                                                                                                                       |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                | ;                                                                                                                             |                                                                                                              |                                                                                                                       |  |

|                | ; TC7135 INTERFACE TO A 6502 MICROPROCESSOR<br>; USING A 6522 I/O PORT                                                        |                                                                                                              |                                                                                                                       |  |

|                | ; RESULTS ARE STORED IN 5 BYTES OF ZERO-PAGE<br>; MEMORY, BEGINNING AT LOCATION "DIGSTOR"<br>; (MOST SIGNIFICANT DIGIT FIRST) |                                                                                                              |                                                                                                                       |  |

|                | ; THE                                                                                                                         | ;<br>USER MUST PROVIDE INTERRUPT VECTOR FROM<br>; THE 6522'S CAI INTERRUPT TO A ROUTINE<br>; AT THE "INTVEC" |                                                                                                                       |  |

|                | ;                                                                                                                             |                                                                                                              |                                                                                                                       |  |

|                | ;;                                                                                                                            | ;;                                                                                                           |                                                                                                                       |  |

|                | ;                                                                                                                             |                                                                                                              | R INTERRUPT OPERATION                                                                                                 |  |

| IOPRT<br>SETUP |                                                                                                                               |                                                                                                              | ;ADDRESS OF 6522 I/O PORT<br>;ADDR OF 6522 SET UP ROUTINE                                                             |  |

|                | .ORG                                                                                                                          | SETUP                                                                                                        | ;SET PORT A FOR<br>3:LATCHED INPUT<br>;CA1-INT ON NEG EDGE<br>:CC2=HIGH (7135 IN "RUN" MODE)<br>;ENABLE CA1 INTERRUPT |  |

|                | STA                                                                                                                           | IOPRT_0E                                                                                                     | ; SET PORT A FOR<br>3; LATCHED INPUT                                                                                  |  |

|                | LDA                                                                                                                           | #0E                                                                                                          | CA1-INT ON NEG EDGE                                                                                                   |  |

|                | LDA                                                                                                                           | #082                                                                                                         | ;ENABLE CA1 INTERRUPT                                                                                                 |  |

|                | STA                                                                                                                           | TOPRI+UE                                                                                                     | 5 /                                                                                                                   |  |

|                |                                                                                                                               | MAINPRG                                                                                                      | ;I/O PORT SETUP COMPLETE, SO<br>; JUMP TO OPERATING SYSTEM OR<br>; TO MAIN PROGRAM                                    |  |

|                |                                                                                                                               |                                                                                                              | SERVICE ROUTINE                                                                                                       |  |

| XSTOR          | .EQU                                                                                                                          | 81                                                                                                           | ;SAVE X REGISTER<br>;SAVE RESULTS HERE<br>;6522'S CA1 INTERRUPT ROUTINE                                               |  |

| INTVEC         | .EQU<br>.EQU                                                                                                                  | 82<br>02E0                                                                                                   | ;SAVE RESULTS HERE<br>;6522'S CA1 INTERRUPT ROUTINE                                                                   |  |

|                | .ORG<br>;                                                                                                                     | INTVEC                                                                                                       |                                                                                                                       |  |

|                | BPL                                                                                                                           | NXTDIG                                                                                                       | ;GET DIGIT FROM 6522<br>;IF MSB=0, THIS IS NOT THE MOST<br>; SIGNIF DIGIT. SO CONTINUE                                |  |

|                | BIT                                                                                                                           | OVRBIT                                                                                                       | ; CHECK FOR OVERRANGE<br>; BRANCH TO ERROR ROUTINE                                                                    |  |

|                | BNE                                                                                                                           | OVRANG<br>#00                                                                                                | BRANCH TO ERROR ROUTINE                                                                                               |  |

|                | ;                                                                                                                             |                                                                                                              | ;SET THE DIGIT POINTER<br>; AND STORE                                                                                 |  |

| NXTDIG         | LDX<br>STA<br>INX                                                                                                             | XSTOR<br>DIGSTOR,                                                                                            | ;GET DIGIT POINTER<br>,X ;STORE DIGIT IN ZERO PAGE<br>; AND POINT TO                                                  |  |

|                |                                                                                                                               | XSTOR                                                                                                        | ; THE NEXT DIGIT                                                                                                      |  |

|                | CPX                                                                                                                           | #05<br>DONE                                                                                                  | ;5 DIGITS COMPLETES ONE SCAN<br>;CONVERSION COMPLETE, PROCESS<br>;OR DISPLAY DATA                                     |  |

|                | RTI                                                                                                                           |                                                                                                              | ;THE 'DONE' ROUTINE MUST END WITH 'RTI'<br>;RETURN IF NOT COMPLETE                                                    |  |

| OVRANG         | LDX                                                                                                                           | #01                                                                                                          | SET DIGIT COUNTER SO THAT DIGITS                                                                                      |  |

|                | STX<br>NOP                                                                                                                    | XSTOR                                                                                                        | ; WILL NOT OVERFLOW ZERO PAGE MEM<br>;IF REQUIRED, USER PROGRAM FOR                                                   |  |

|                | NOP                                                                                                                           |                                                                                                              | ; SERVICING OVERRANGE GOES HERE                                                                                       |  |

|                | RTI                                                                                                                           |                                                                                                              | ;AND RETURN                                                                                                           |  |

|                | ;                                                                                                                             |                                                                                                              |                                                                                                                       |  |

|                | .END                                                                                                                          |                                                                                                              |                                                                                                                       |  |

|                |                                                                                                                               |                                                                                                              |                                                                                                                       |  |

FIGURE 3: 6502 assembly language testing.

Once the 6522's interrupt has been recognized and vectored to location "INTVEC," a read of Port A loads the TC7135 data in to the 6502 accumulator. Reading Port A also sets the  $\mu$ P's status flags and resets the 6522's interrupt flag.

The  $\mu P$  now tests whether the accumulator contains the TC7135's most significant digit by testing for DS5 being high. Connecting DS5 to PA7 (MSB) of the I/O port allows testing DS5 with a single branch on plus instruction.

If DS5 is high, this data signals the beginning of a new display scan (i.e., an end of conversion has occurred). The  $\mu$ P zeros its X index register, which will be used both to count the digits and to provide an offset for storing each digit in zero page memory. Register X is also stored in zero page memory at location XSTOR, since its contents will probably be lost upon returning from interrupt.

An early indication of an overrange condition can be obtained at this time. A bit mask, stored in memory, is used to test for the TC7135's OVERRANGE input. If OR is high, the program branches to an error routine. An alternative for overrange testing is to wait until all digits have been scanned and then test bit 4 of any digit.

FIGURE 4: TC7135 to 6502µP interface program flow chart.

# AN16

If DS5 is not high, or after register X is zeroed, program execution proceeds to location "NXTDIG." The BCD data is stored in zero page memory, beginning at location "DIGSTOR" and indexed by register X. After each digit is stored, register X is incremented and compared to five. If register X equals five, the digit scan is complete and data can be processed or displayed. Register X less than five

indicates the digit scan is not complete, so an RTI instruction returns operation to the main program to await another digit strobe. Other programs can use memory location XSTOR as a "Data Valid" indication: If XSTOR = 5, then 5 consecutive memory locations beginning at DIGSTOR contain the results of the latest TC7135 conversion.

FIGURE 5: 6522 I/O port control register functions.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

### Trademarks

The Microchip name and logo, the Microchip logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, KEELOQ, SEEVAL, MPLAB and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, Filter-Lab, MXDEV, microID, *Flex*ROM, *fuzzy*LAB, MPASM, MPLINK, MPLIB, PICC, PICDEM, PICDEM.net, ICEPIC, Migratable Memory, FanSense, ECONOMONITOR, Select Mode and microPort are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2001, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL0Q® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# WORLDWIDE SALES AND SERVICE

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

**Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

Atlanta 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350

Tel: 770-640-0034 Fax: 770-640-0307 Austin - Analog

8303 MoPac Expressway North Suite A-201 Austin, TX 78759

Tel: 512-345-2030 Fax: 512-345-6085 Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

Boston - Analog Unit A-8-1 Millbrook Tarry Condominium 97 Lowell Road

Concord, MA 01742 Tel: 978-371-6400 Fax: 978-371-0050 Chicado

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

**Dayton** Two Prestige Place, Suite 130 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

Detroit Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

Los Angeles 18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

San Jose Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### **Toronto** 6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 **China - Beijing** Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915

New China Hong Kong Manhattan Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Rm. 531, North Building Fujian Foreign Trade Center Hotel 73 Wusi Road Fuzhou 350001, China Tel: 86-591-7557563 Fax: 86-591-7557572 **China - Shanghai**

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 India Microchip Technology Inc. India Liaison Office **Divyasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

EUROPE

Denmark Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Arizona Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Arizona Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Germany - Analog

Lochhamer Strasse 13 D-82152 Martinsried, Germany Tel: 49-89-895650-0 Fax: 49-89-895650-22 Italy Arizona Microchip Technology SRL

Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883 **United Kingdom** Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle

Winnersh Trangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

06/01/01