# AN1484

#### Recommended Usage of Microchip 23XX512/23XX1024 Serial SRAM Devices

Author: Martin Bowman Microchip Technology Inc.

#### INTRODUCTION

Many embedded systems require some amount of volatile storage for temporary data. This is increasingly true when enabling the "Internet of things". Because of their small footprint, low I/O pin requirement, low-power consumption and low cost, serial SRAMs are a popular choice for volatile storage. Microchip Technology has addressed this need by offering a line of serial SRAMs using the industry standard SPI-based communication. Serial SRAM devices are available in a number of density offerings, operational voltage ranges and packaging options. The serial SRAM products offer an alternative to the traditional parallel architecture that saves both board area and also I/O count on the MCU.

In order to achieve a highly robust application when utilizing serial SRAMs, the designer must consider more than just the data sheet specifications. There are a number of conditions which could potentially result in non-standard operation. The most important of them are discussed in this application note. This application note is written for the 23XX512/ 23XX1024 family of devices. For the 23XX256/ 23XX640 please refer to AN1245.

This application note provides assistance and guidance with the use of Microchip advanced serial SRAMs. These recommendations are not meant as requirements, however, their adoption will lead to a more robust overall design. This document should be used along with the device data sheet. The following topics are discussed:

- Input Considerations

- Power Supply

- SPI/SDI and SQI High-Speed Serial Connections

- MODE Register

- HOLD Operation

- · Operating Modes

- VBAT Operation

Not all of Microchip SRAM devices support all available features. The features supported by each device are summarized in the table below:

| Device    | Density    | Voltage Range | Hold Pin | SPI | SDI | SQI | Vват<br>Support | Pages      |

|-----------|------------|---------------|----------|-----|-----|-----|-----------------|------------|

| 23A512    | 512K Bits  | 1.7-2.2 V     | Yes      | Yes | Yes | Yes | No              | 32B x 2048 |

| 23LC512   | 512K Bits  | 2.5-5.5 V     | Yes      | Yes | Yes | Yes | No              | 32B x 2048 |

| 23LCV512  | 512K Bits  | 2.5-5.5 V     | No       | Yes | Yes | No  | Yes             | 32B x 2048 |

| 23A1024   | 1024K Bits | 1.7-2.2 V     | Yes      | Yes | Yes | Yes | No              | 32B x 4096 |

| 23LC1024  | 1024K Bits | 2.5-5.5 V     | Yes      | Yes | Yes | Yes | No              | 32B x 4096 |

| 23LCV1024 | 1024K Bits | 2.5-5.5 V     | No       | Yes | Yes | No  | Yes             | 32B x 4096 |

#### TABLE 1: DEVICE FEATURES

#### **RECOMMENDED CONNECTIONS**

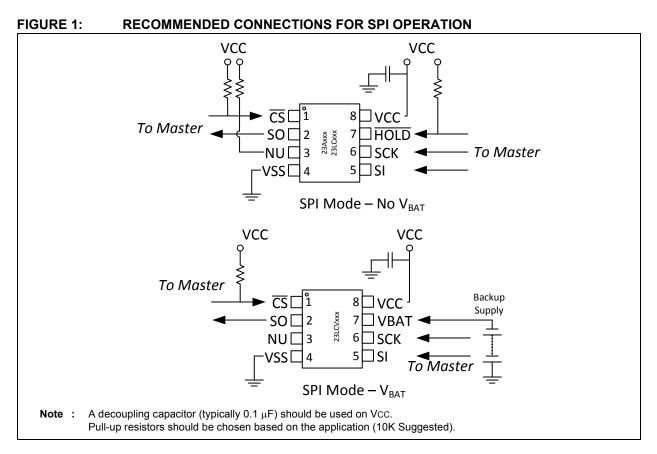

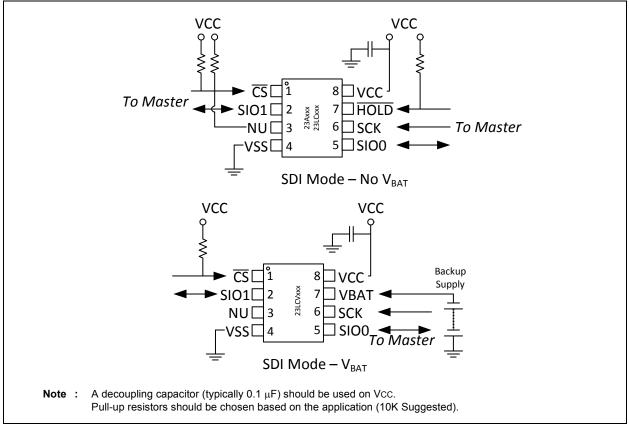

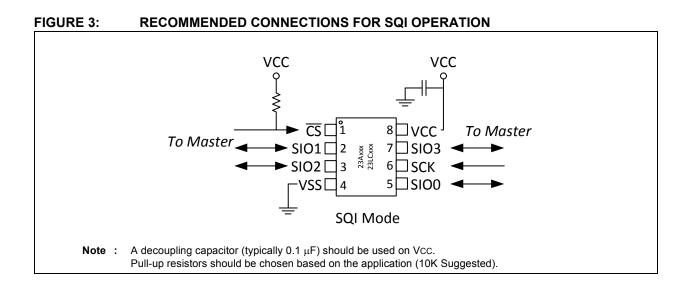

Figure 1 through Figure 3 show the recommended connections for the serial SRAM device when using SPI, SDI and SQI serial communications. The pin designated as NU in the schematics is not used in the referenced configuration and should be treated as shown in the schematic.

## AN1484

#### INPUT CONSIDERATIONS

It is never good practice to leave an input pin floating. This can cause high standby current as well as undesired functionality. If a pin is left floating, it can either float low or high. Which direction the signal goes is dependent upon a number of factors, including noise in the system and capacitive coupling. Because of this, the level seen by the input circuitry is relatively random and likely to change during operation.

Such unpredictable input levels can have devastating effects on device operation. For example, Microchip's SPI serial SRAMs feature a HOLD pin on some devices which allows the user to suspend the clock mid-stream. If this pin were to float low (active), the device would no longer react to any clock pulses received, communication would be disrupted and data potentially lost or corrupted.

Therefore, any unused input pins should always be tied to a proper level, such as high for an active-low input. Moreover, it is recommended that, if the microcontroller has extra, tri-state I/O pins available, connections be made to these unused inputs along with a pull-down/ pull-up resistor, as shown in Figure 1. This will allow for the inputs to be used at a later date simply by modifying firmware.

Although the  $\overline{CS}$  pin should always be driven by the microcontroller during normal operation, it has potential for floating during power-down/power-up. As such, this pin should also have a pull-up resistor to avoid undesired commands due to noise during these conditions.

#### POWER SUPPLY

Microchip SPI serial SRAMs feature a robust serial communication protocol that helps to prevent unintentional writes and data corruption while power is within normal operating levels. But, certain considerations should be made regarding power-up and power-down conditions to ensure the same level of protection during those times when power is not within normal operating levels.

As shown in Figure 1, a decoupling capacitor (typically 0.1  $\mu F)$  should be used to help filter out small ripples on Vcc.

#### **Power-Up**

On power-up, VCC should always begin at 0V and rise straight to its normal operating level to ensure a proper Power-on Reset. VCC should not remain at an ambiguous level (i.e., below the minimum operating voltage). However, if Vcc happens to fall below the minimum retention voltage of the device (see data sheet DC Characteristics), it is recommended that Vcc be brought down fully to 0V before returning to normal operating level. This will help to ensure that the device is reset properly.

Furthermore, if the microcontroller features a Brownout Reset with a threshold higher than that of the serial SRAM, bringing Vcc down to 0V will allow both devices to be reset together. Otherwise, the microcontroller may reset during communication while the SRAM is still in an operational condition.

#### **Power Failure During a Write**

During the time that data is being written to the SRAM VDD should remain above the minimum operating voltage. If at any time VDD drops below this minimum voltage but remains above the retention voltage, (as specified in the product data sheet) care should be taken to ensure that the data written to the device is free from errors.

#### **SPI OPERATION**

During normal SPI operation the following pins are used for device communication:

- CS Chip Select active low

- SO Data from the SRAM

- · SI Data to the SRAM

- SCK Serial data clock

Pin 3 – SIO2 (available on 23AXXX and 23LCXXX devices) is used for SQI mode of operation. As this is an input pin, this should not be left floating. This pin may be connected to either Vss or Vcc. It is recommended that this pin be connected to Vcc in the event that the device enters SQI mode, as this pin will need to be high to exit SQI.

For the 23LCVXXX devices, pin 3 is internally tied high, so can be treated as a true No Connect.

#### **SDI OPERATION**

SDI operation uses the same physical pins as SPI, however, both the SI and SO pins become SIO0 and SIO1.

Pin 3 – SIO2 (available on 23AXXX and 23LCXXX devices) is used for SQI mode of operation. As this is an input pin, it should not be left floating. It may be connected to either Vss or Vcc. It is recommended that this pin be connected to Vcc in the event that the device enters SQI mode, as this pin will need to be high to exit SQI mode. The following pins are used in SDI communication mode:

- CS Chip Select active low

- SIO0 Bidirectional data line (LSB)

- SIO1 Bidirectional data line (MSB)

- · SCK Serial data clock

To enter SDI mode of operation the EDIO command must be issued. Upon completion of this command, the device will be expecting data and commands to be issued in SDI mode. The device can return to SPI mode by issuing the RSTIO command.

In SDI mode data is sent to the SRAM on the rising edge of the clock, 2 bits per clock, with both the SIO0 and SIO1 pins being bidirectional. In this mode, the data rate to and from the serial SRAM is 2x SPI mode.

As there is a finite time for both the SIO0 and SIO1 lines to change from input to output when reading data from the device, there is a dummy byte inserted between the address and the first data byte clocked from the SRAM, as shown in the product data sheet.

#### **SQI OPERATION**

SQI mode operates on the same principle as SDI, however, there are four bidirectional data lines. Because of the extra data line, the  $\overline{HOLD}$  function is disabled and VBAT is not available when operating in SQI mode. The following pins are used in SQI communication mode:

- CS Chip Select active low

- SIO0 Bidirectional data line (LSB)

- SIO1 Bidirectional data line

- · SIO2 Bidirectional data line

- SIO3 Bidirectional data line (MSB)

- SCK Serial data clock

To enter SQI mode of operation the EQIO command must be issued. Upon completion of this command, the device will be expecting data and commands to be issued in SQI mode. The device can return to SPI mode by issuing the RSTIO command.

In SQI mode data is sent to the SRAM on the rising edge of the clock, 4 bits per clock, giving 4x the data throughput of standard SPI mode.

As there is a finite time for the bidirectional data lines to change from input to output when reading data from the device, there is a dummy byte inserted between the address and the first data byte clocked from the SRAM.

#### **MODE REGISTER**

Microchip SPI serial SRAMs feature a MODE register. The MODE register is used to control features of the device and is a read/write register. Bits within the MODE register are used to control the operating mode:

- Byte mode

- · Page mode

- Sequential mode

The MODE register is accessed through the Read Mode Register (RDMR) and Write Mode Register (WRMR) commands. Unused bits should always be written as '0'.

#### HOLD FEATURE

The HOLD feature is not available on devices with VBAT support (23LCVXXX) or when SQI mode is enabled.

#### **OPERATING MODES**

The Microchip serial SRAM has three operating modes.

#### **Byte Mode**

Byte mode is selected when bits <7:6> in the STATUS register are set to '00'. In this mode, all read and write operations are limited to the byte that is addressed, with the address clocked into the device after the instruction. The user can read or write to the same byte continuously until the  $\overline{CS}$  line is brought high, terminating the command. The internal Address Pointer is not incremented.

#### Page Mode

Page mode is selected when bits <7:6> in the STATUS register are set to '10'. In this mode, read and write operations are limited to the current page that is addressed, with the address following the instruction.

The serial SRAM has a page size of 32 bytes, with either 2048 pages (23XXX512) or 4096 pages (23XXX1024). In Page mode the user can either read data from or write data to the current page. As the internal Address Pointer is incremented, at the end of the page boundary it will roll over to the beginning of the current page. If a write is being executed, the data at the beginning of the page will be overwritten. The address sent after the instruction does not have to be aligned to a page boundary.

#### **Sequential Mode (Default)**

Sequential mode is selected when bits <7:6> in the STATUS register are set to '01'. In this mode, read and write operations can be performed on the whole array.

The address sent after the instruction is the first array location that will be read from or written to. With each subsequent data byte, the internal Address Pointer is incremented. At any point, the read or write sequence can be terminated by raising  $\overline{CS}$ . At the end of the SRAM array, the internal Address Pointer will roll-over to  $0 \times 00000$  (23XXX1024) or  $0 \times 0000$  (23XXX512).

#### **VBAT OPERATION**

This section details special considerations for using the VBAT mode of operation. The internal VBAT switch allows the data stored in the SRAM array to be retained when VCC is no longer available. Care should be taken to ensure that the VBAT voltage specification is not exceeded.

The SRAM array is powered from the external VBAT supply when the Vcc voltage drops below the VTRIP level (see data sheet specification). During this time the SRAM will not respond to any communications over the SPI/SDI bus.

The current required to maintain the SRAM contents is significantly lower than the Vcc current, allowing the use of a backup battery with a low capacity. Recommended backup supply examples are detailed below – this is not an exhaustive list as other options exist.

The recommended electrical connections for an external primary (non-rechargeable) battery are shown in Figure 1 and Figure 2 for both SPI and SDI operation. No additional components are required for VBAT operation with a primary battery such as a coin cell.

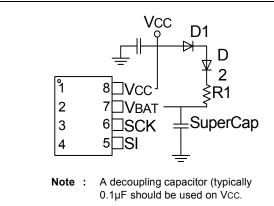

When using a backup supply based around a Super Cap, the following schematic shows the recommended external connections. D1 and D2 are used to both limit the maximum voltage to the Super Cap and the VBAT pin. R1 is used to limit the current to the Super Cap.

FIGURE 4: SUPER CAP SCHEMATIC

Additional care should be exercised when using a backup supply that is designed to be recharged, such as a NiCad backup battery. In this case, care must be taken to ensure that the battery cannot be over charged. The above circuit (Figure 4) can be used for a NiCad battery if the resistor R1 is chosen so that the charge current is within the allowable limits of the battery.

#### SUMMARY

This application note illustrates recommended techniques for increasing design robustness when using Microchip advanced SPI serial SRAMs. These recommendations fall directly in line with how Microchip designs, manufactures, qualifies and tests its serial SRAMs, and will allow the devices to operate within the data sheet parameters. It also serves to explain in detail some of the features of the device and makes the user aware of any potential pitfalls that they may fall into.

# AN1484

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620766880

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou Tel: 86-571-2819-3187

Fax: 86-571-2819-3189 China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820