### **Glitch-Free Design Using the Configurable Logic Cell (CLC)**

Author: Stephen Allen Microchip Technology Inc.

### INTRODUCTION

One of the challenges that digital designers run into frequently involves getting rid of glitches in their design. This is typically accounted for by ensuring there is adequate set-up and hold time when data is latched.

A 'glitch' is a signal which does not remain active for a full clock period. If a signal with a glitch feeds the clock line of numerous latches, some of the latches may get updated, while others may not. This is clearly a situation that designers want to avoid.

It should also be noted that propagation delay varies with temperature, therefore, a design which does not produce glitches during development may produce glitches under different conditions. The addition of the Configurable Logic Cell (CLC) to the Microchip set of peripherals allows end-users to essentially "design" a simple peripheral that can interface with the PIC<sup>®</sup> microcontroller. With the ability to drive signals into the PIC device that can cause interrupts and increment counters, it is necessary to provide some instruction so that stable designs can be created using the CLC peripheral.

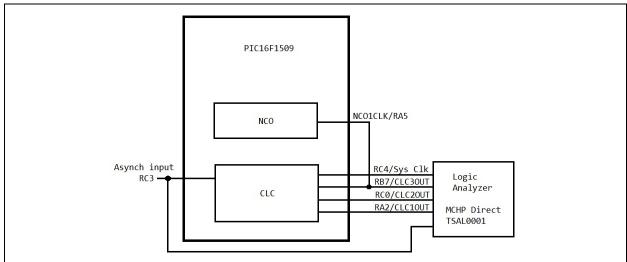

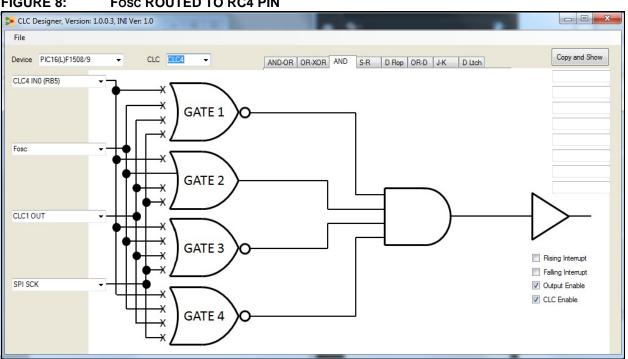

A PIC16F1509 was used for this example, and it uses three of the four available CLC modules. The 4th CLC module is being used to route the internal Fosc signal to the RC4 pin, so that it can be viewed with a logic analyzer. Other signals internal to the CLC (XOR output, latch output) have been brought out on external pins to provide greater visibility of how the application is functioning.

The block diagram (Figure 1) shows the asynchronous input signal on RC3, with the CLC outputs feeding the logic analyzer. The CLC3 signal is our glitch-free clock signal and is being fed into the NCO1CLK pad.

### FIGURE 1: GLITCH-FREE BLOCK DIAGRAM – BENCH SET-UP

In this example, we will create a high-speed counter which is used to increment the NCO register. The NCO will increment as long as an external pulse signal is high. This creates a high-resolution, long-duration counter, as the NCO counter is a 20-bit wide register. It will take approximately 16 instruction cycles (4  $\mu$ s with 16 MHz clock) for the data to be read and the counter to reset, so it is necessary to have at least 4  $\mu$ s of low time between pulses. A falling edge interrupt flag on CLC2 provides a signal that the pulse width measurement has been completed. While the NCO register has been designed to be resistant to glitches on the clock input, it is still good design practice to have clean signals feeding into the NCO clock line.

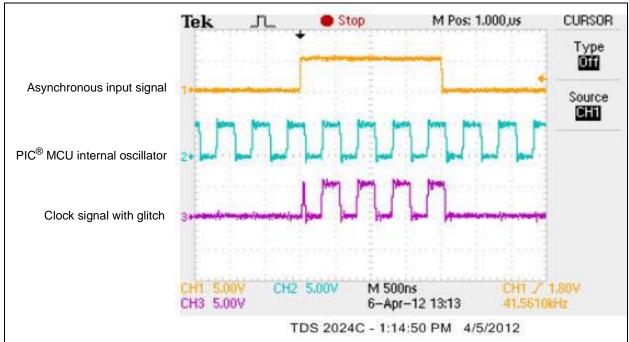

The first design for this circuit <u>does</u> allow glitches to pass in, and is a simple 'AND' of the pulse signal with the system clock. Note how a spike on the clock is created when the pulse signal rises shortly before the clock falls (Figure 2).

FIGURE 2: LOGICAL 'AND' OF ASYNCHRONOUS PULSE AND SYSTEM CLOCK

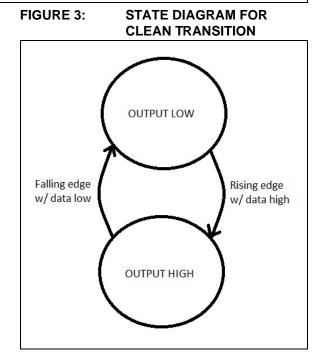

We want to use the 'AND' function to clock the NCO when the pulse is high, but we would like to get rid of the glitches on the clock signal. In order to do this, it would be ideal to create a pulse -> new signal that would only rise on the rising edge of the clock, and only fall on the falling edge of the clock. This new signal (CLC2OUT) can be AND'ed with the oscillator clock, and there will never be a glitch on the NCO clock signal. A simple state diagram (Figure 3) shows how this will work.

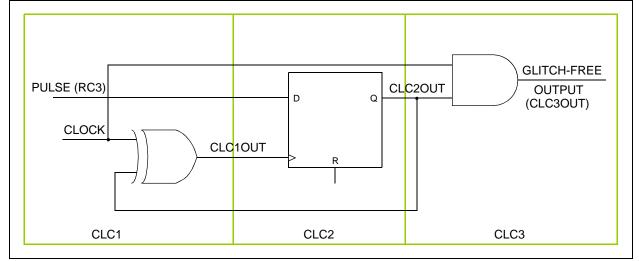

This state diagram can be implemented with a D flip-flop and an XOR gate. The XOR gate will have the function of taking feedback from the D flip-flop and inverting the clock, so that it will trigger on the falling edge once the flip-flop has been set. A schematic for this is shown below (Figure 4). This new signal (CLC2OUT) can be AND'ed with the oscillator clock, and there will never be a glitch on the NCO clock signal.

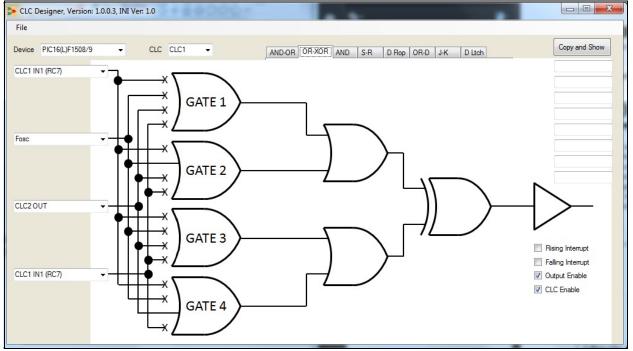

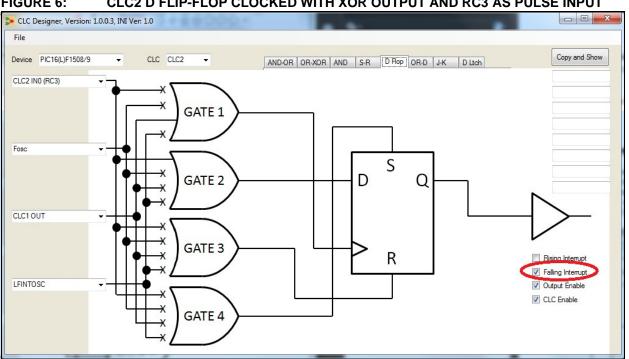

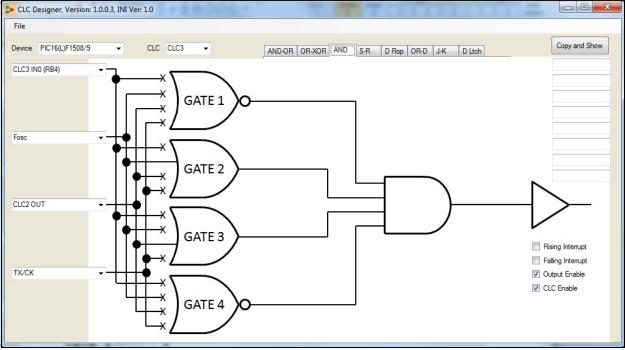

The schematic has been broken down so that each logic function will use one CLC module, and the following screenshots show how the schematic is implemented using the CLC tool -> CLC Designer tool (Figure 5, Figure 6, Figure 7 and Figure 8):

#### FIGURE 6: CLC2 D FLIP-FLOP CLOCKED WITH XOR OUTPUT AND RC3 AS PULSE INPUT

FIGURE 8: **Fosc ROUTED TO RC4 PIN**

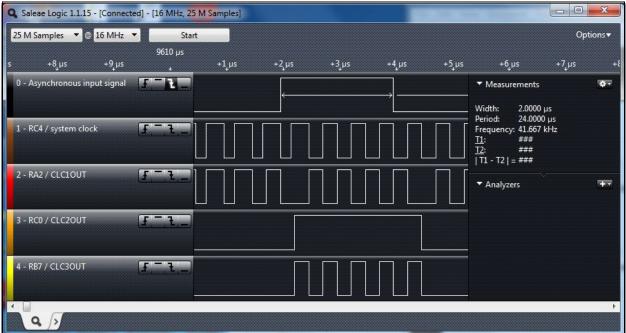

Once this logic has been implemented, we now have a glitch-free output to drive our NCO clock signal. The scope plot below (Figure 9) shows the Asynchronous input signal, Fosc system clock, XOR output

(CLC1OUT), latch output (CLC2OUT), and glitch-free output clock (CLC3OUT). The interrupt flag will be set on the falling edge of the CLC2OUT signal (when we are done measuring our pulse width).

#### FIGURE 9: **GLITCH-FREE CLOCK OUTPUT TO NCO**

### APPENDIX A: ASSEMBLY SOURCE CODE

### Software License Agreement

The software supplied herewith by Microchip Technology Incorporated (the "Company") is intended and supplied to you, the Company's customer, for use solely and exclusively with products manufactured by the Company.

The software is owned by the Company and/or its supplier, and is protected under applicable copyright laws. All rights are reserved. Any use in violation of the foregoing restrictions may subject the user to criminal sanctions under applicable laws, as well as to civil liability for the breach of the terms and conditions of this license.

THIS SOFTWARE IS PROVIDED IN AN "AS IS" CONDITION. NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATU-TORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICU-LAR PURPOSE APPLY TO THIS SOFTWARE. THE COMPANY SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

FileName: glitch\_free.asm Dependencies: Processor: PIC16F1509 Hardware: Compiler: MPASM 5.45 or later Company: Microchip Technology, Inc.

Copyright © 2007-2012 Microchip Technology Inc. All rights reserved.

You may use this software, and any derivatives, exclusively with Microchip's products. Microchip and its licensors retain all ownership and intellectual property rights in the accompanying software and in all derivatives hereto. This software and any accompanying information is for suggestion only. It does not modify Microchip's standard warranty for its products. You agree that you are solely responsible for testing the software and determining its suitability. Microchip has no obligation to modify, test, certify, or support the software.

THIS SOFTWARE IS SUPPLIED BY MICROCHIP "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE, ITS INTERACTION WITH MICROCHIP'S PRODUCTS, COMBINATION WITH ANY OTHER PRODUCTS, OR USE IN ANY APPLICATION.

IN NO EVENT, WILL MICROCHIP BE LIABLE, WHETHER IN CONTRACT, WARRANTY, TORT (INCLUDING NEGLIGENCE OR BREACH OF STATUTORY DUTY), STRICT LIABILITY, INDEMNITY, CONTRIBUTION, OR OTHERWISE, FOR ANY INDIRECT, SPECIAL, PUNITIVE, EXEMPLARY, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, FOR COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE SOFTWARE, HOWSOEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWABLE BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THIS SOFTWARE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THIS SOFTWARE.

MICROCHIP PROVIDES THIS SOFTWARE CONDITIONALLY UPON YOUR ACCEPTANCE OF THESE TERMS.

1 #include "p16f1509.inc" \_CONFIG \_CONFIG1, \_FOSC\_INTOSC & \_WDTE\_OFF & \_PWRTE\_OFF & \_CLKOUTEN\_OFF CONFIG CONFIG2, LVP OFF & STVREN ON errorlevel -302 ; suppress bank selection not zero warning result0 eau  $0 \times 20$ result1 equ 0x21 result2 equ 0x22 ORG 0x00 main BANKSEL ANSELA clrf ANSELA ; all digital pins clrf ANSELC clrf ANSELB

```

BANKSEL TRISB

bcf

TRISA,2

; RA2 (pin 17) output - CLC10UT

; RC0 (pin 16) output - CLC2OUT

bcf

TRISC,0

bcf

TRISB,7

; RB7 (pin 10) output - CLC3OUT

; RC4 (pin 6) output - CLC4OUT (used to show internal

bcf

TRISC,4

oscillator clock)

BANKSEL

OSCCON

movlw 0x78

movwf OSCCON

; go to 16 MHz clock

;; include file generated by CLC Designer Tool

#include "glitch_free_osc_out_clc2_int.inc"

BANKSEL

NCOlINCL

; bank with NCO registers

movlw 0x00

movwf NCOlINCH

movlw 0x01

movwf NCOlINCL

; set up increment value for NCOlINCH/L

movlw 0x03

movwf NCO1CLK

; set up NCO1CLK pad as the clock source

movlw 0xC0

movwf NCO1CON

; and run the NCO.

wait_initialize

BANKSEL

NCO1ACCL

; bank with NCO registers

movlw 0x00

movwf

NCO1ACCL

movwf NCO1ACCH

movwf NCO1ACCU

; clear accumulator

NCO1CON,N1EN ; turn on NCO

bsf

BANKSEL

PIR3

bcf

PIR3,CLC2IF

; clear interrupt flag.

wait_for_pulse

btfss PIR3,CLC2IF

; Has CLC2IF falling edge interrupt flag been set?

goto wait_for_pulse

; Yes - I am done measuring the pulse width.

BANKSEL

NCO1ACCL

; bank with NCO registers

NCO1CON,N1EN ; turn off NCO

bcf

movf NCO1ACCU,W

movwf result2

movf

NCO1ACCH,W

movwf

result1

movf

NCO1ACCL,W

movwf result0

; pulse width measurement is stored in resultx.

wait_initialize; so that we can do it again.

qoto

end

```

### APPENDIX B: CLC CONFIGURATION – ASSEMBLY LANGUAGE VERSION

### Software License Agreement

The software supplied herewith by Microchip Technology Incorporated (the "Company") is intended and supplied to you, the Company's customer, for use solely and exclusively with products manufactured by the Company.

The software is owned by the Company and/or its supplier, and is protected under applicable copyright laws. All rights are reserved. Any use in violation of the foregoing restrictions may subject the user to criminal sanctions under applicable laws, as well as to civil liability for the breach of the terms and conditions of this license.

THIS SOFTWARE IS PROVIDED IN AN "AS IS" CONDITION. NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATU-TORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICU-LAR PURPOSE APPLY TO THIS SOFTWARE. THE COMPANY SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

### CLC Configuration include files

CLC1 Configuration BANKSEL CLC1GLS0 movlw H'00' movwf CLC1GLS0 movlw H'08' movwf CLC1GLS1 movlw H'00' movwf CLC1GLS2 movlw H'20' movwf CLC1GLS3 movlw H'01' movwf CLC1SEL0 movlw Н'51' movwf CLC1SEL1 movlw H'00' movwf CLC1POL movlw H'Cl' movwf CLC1CON CLC2 Configuration BANKSEL CLC2GLS0 movlw H'20' movwf CLC2GLS0 movlw H'02' movwf CLC2GLS1 movlw H'00' movwf CLC2GLS2 movlw H'00' movwf CLC2GLS3 Н'ОО' movlw movwf CLC2SEL0 movlw Н'ОО' movwf CLC2SEL1 movlw H'00' movwf CLC2POL movlw H'CC' movwf CLC2CON

CLC3 Configuration BANKSEL CLC3GLS0 movlw H'00' movwf CLC3GLS0 movlw H'08' movwf CLC3GLS1 movlw H'20' movwf CLC3GLS2 movlw H'00' movwf CLC3GLS3 movlw H'00' movwf CLC3SEL0 movlw H'01' movwf CLC3SEL1 movlw H'09' movwf CLC3POL movlw H'C2' movwf CLC3CON CLC4 Configuration BANKSEL CLC4GLS0 movlw H'00' movwf CLC4GLS0 movlw H'08' movwf CLC4GLS1 movlw H'00' movwf CLC4GLS2 movlw H'00' movwf CLC4GLS3 movlw H'00' movwf CLC4SEL0 movlw Н'ОО' movwf CLC4SEL1

movlw H'OD'

movwf CLC4POL

movlw H'C2'

movwf CLC4CON

NOTES:

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### ISBN: 9781620764503

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820