# **AN1287**

# Using C18/HI-TECH C® Compiler to Interface Serial SRAM Devices to PIC16F/PIC18F Microcontrollers

Author: Deepak Kumar Rana

Microchip Technology Inc.

### INTRODUCTION

Microchip's serial SRAM product line represents a new way to add additional RAM to an application. With the small 8-pin packages and the SPI interface, these devices give designers added system flexibility. The 23XXXX series of serial SRAM devices from Microchip Technology support a half-duplex protocol that functions on a master-slave paradigm that is ideally suited to data stream applications.

The bus is controlled by the Microcontroller (master), which accesses the 23XXXX using the MSSP peripheral built into the MCU configured for SPI operation. The MSSP peripheral can support throughput up to 5 or 8 MHz depending upon the device family of PIC16/18 MCU Selected. Communication can be paused using the  $\overline{HOLD}$  pin.

This application note is part of a series that provide source code to help the user implement the protocol with minimal effort.

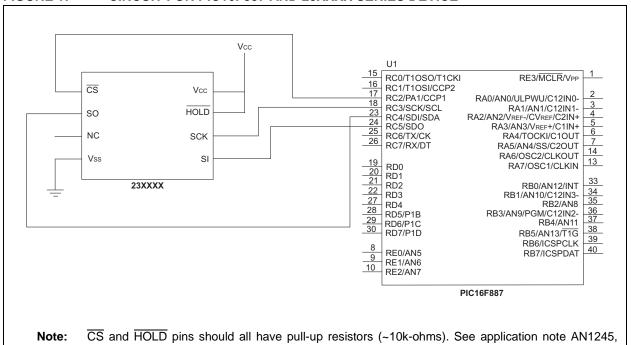

Figure 1 describes the hardware schematic for the interface between Microchip's 23XXXX series devices and the PIC16F/18F series of MCUs. The schematic shows the connections necessary between either controller and the serial SRAM as tested, and the software was written assuming these connections. The HOLD pin is tied to Vcc because this feature is not used in the examples provided.

FIGURE 1: CIRCUIT FOR PIC16F887 AND 23XXXX SERIES DEVICE

"Recommended Usage of Microchip SPI Serial SRAM Devices."

### FIRMWARE DESCRIPTION

The purpose of this application note is to offer the designer a set of examples for the read and write functions for using the Microchip SPI serial SRAM. Examples are included for the following modes: Byte, Page and Sequential Read and Writes. The code uses on-chip MSSP hardware peripheral to communicate with the serial SRAM.

The code was tested using the 23K256 SRAM mounted on the general purpose section of the PICDEM™ 2 Plus development board. The MSSP module is configured for SPI Master mode with a clock frequency of 5 MHz. The code is compatible with the PIC16F/18F families of MCUs with the MSSP module.

Oscilloscope screen shots are shown in this application note.

The following functions are provided to access the Serial SRAM.

- SRAMWriteStatusReg

- SRAMReadStatusReg

- SRAMWriteByte

- SRAMReadByte

- SRAMWritePage

- SRAMReadPage

- SRAMWriteSeq

- SRAMReadSeq

The above functions are defined in the driver files SRAM\_Driver.asm (for PIC16 assembly code and PIC18 C code) and SRAM\_Driver.c (for PIC16 HITECH), with a respective SRAM\_Driver.inc and SRAM\_Driver.h files.

The respective file pairs can be directly imported into the users application code. For the PIC18 C code we use the driver file in assembly ( $SRAM\_Driver.asm$ ) and call the assembly functions from C file  $Main\_Demo.c.$

Four Code examples accompanying the application note are:

- Assembly code example for PIC16 (MPASM™ assembler)

- HI-TECH C<sup>®</sup> code example for PIC16 (HI-TECH C compiler)

- C Code example for PIC18 (MPASM assembler and C18 compiler)

- C Code example for PIC18 (HI-TECH C compiler)

#### INITIALIZATION

Only one function needs to be called to initialize the SRAM. To communicate with the SRAM we need to configure the on-chip MSSP module of the MCU for SPI operation. The InitSRAM() function initializes the MSSP module for SPI (Master mode 1, CKP=0, CKE=1) functionality. Using the on-chip MSSP peripheral makes the communication easier than bit-banging the I/O port, reducing software overhead.

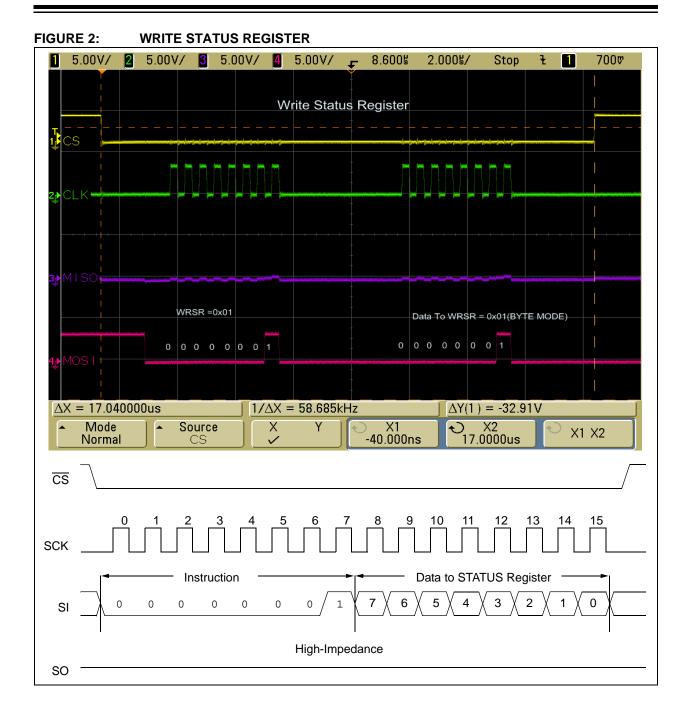

### WRITE STATUS REGISTER

The default mode of operation for the serial SRAM is Byte mode and the user must select the appropriate mode (Byte, Page, Sequential) before the read or write operation. The functions that are provided configure the SRAM for the correct mode of operation, for example if a SRAMWritePage command is called, then the appropriate operating mode is selected. The STATUS register also has provision for enabling the HOLD feature, but this is not used in these examples. Figure 2 shows an example of the Write Status Register command. Chip Select is brought low (active) and the opcode is sent out through the SPI port. The Write Status command is given followed by the data to be written, in this case, Byte mode is selected.

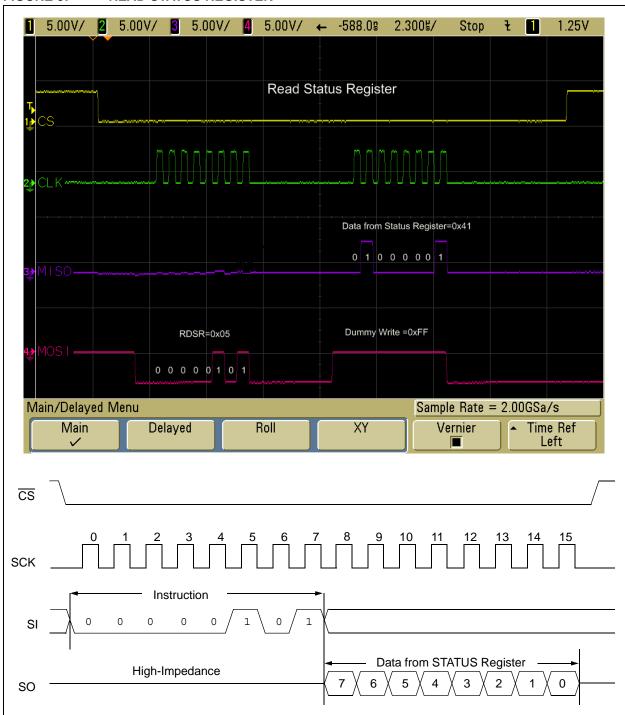

### **READ STATUS REGISTER**

Figure 3 shows an example of the Read Status Register command to check for the mode of operation and also the current status of the HOLD function.

FIGURE 3: READ STATUS REGISTER

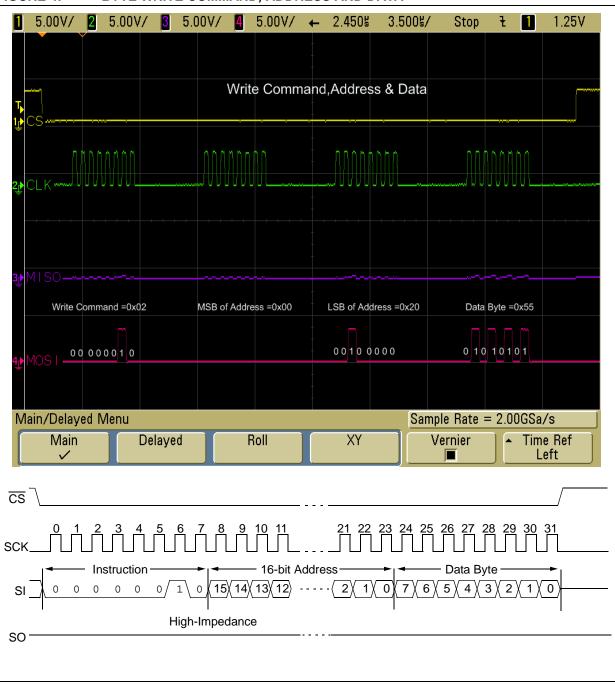

### **BYTE WRITE**

The byte write operation consists of the following sequence: The Write command followed by the word address and data byte. The serial SRAM uses a 16-bit address, so two bytes must be transmitted for the entire word address, with the Most Significant Byte (MSB) first.

Figure 4 shows an example of the Write command. For this, the device is selected and the opcode, 0x02, is sent. The High Address byte is given 0x00, followed by the Low Address byte, 0x20. Finally, the data is clocked in last, in this case, 0x55.

FIGURE 4: BYTE WRITE COMMAND, ADDRESS AND DATA

### **BYTE READ**

The byte read operation can be used to read data from the serial SRAM. The MCU/DSC sends the command byte followed by the word address. Figure 5 shows an example of the Read command, followed by the MSB and LSB address bytes, followed by the read byte.

FIGURE 5: BYTE READ (COMMAND BYTE, WORD ADDRESS AND READ BYTE) 5.00V/ 5.00V/5.00V/ 5.00V/ 2.450⊌ 3.500%/ ł 1 1.25V Stop Read Command, Address & Data Data Byte =0x55 0 1 0 1 0 1 0 1 Dummy Write =0xFF Read Command =0x03 MSB of Address =0x00 LSB of Address =0x20 00000011 00 10000 0 0000 0000 Main/Delayed Menu Sample Rate = 2.00GSa/s Delayed Roll XY Vernier Time Ref Main Left CS 15 \ 14 \ 13 \ 12 0 0 0 Data Out-High-Impedance 5 🛚 3 / 2 / SO -

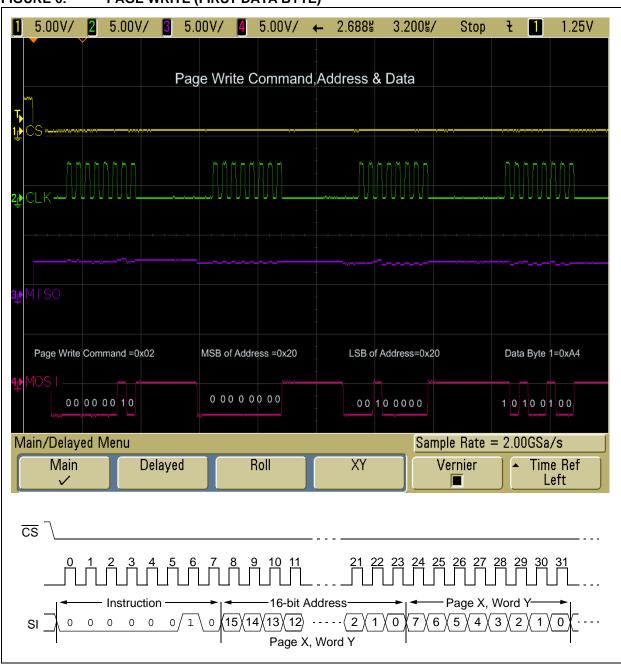

#### **PAGE WRITE**

Page write operations provide a technique for increasing throughput when writing large blocks of data. The Serial SRAM features a 32-byte page. By using the page write feature, up to 1 full page of data can be written consecutively. It is important to point out that page write operations are limited to writing bytes within a single physical page regardless of the number of bytes being written. Physical page boundaries start at

addresses that are integer multiples of the page size and end at addresses that are [integer multiples of the page size] – 1. Attempting to write across a page boundary results in the data being wrapped back to the beginning of the current page. Figure 6 shows Write command, address and data byte during a page write operation.

FIGURE 6: PAGE WRITE (FIRST DATA BYTE)

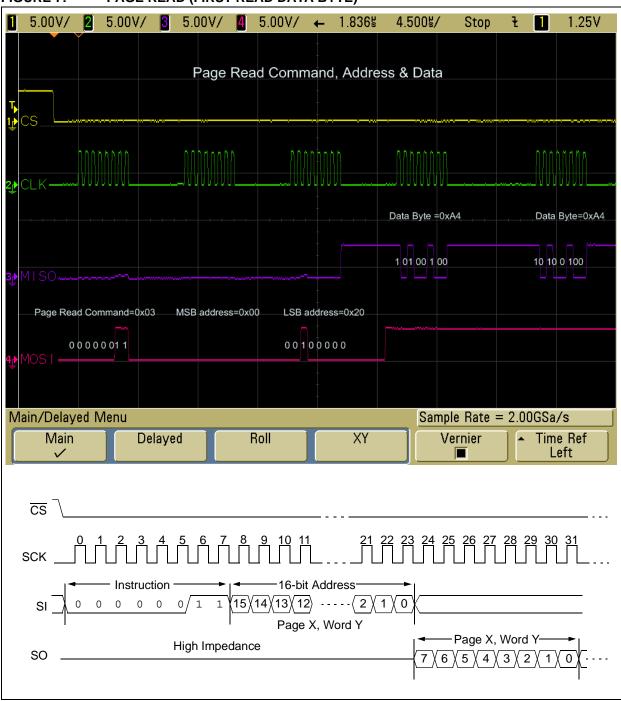

## **PAGE READ**

Page read operations read a complete string, starting with the specified address. The page read operation also works similar to a page write operation and thus a maximum of 32 bytes can be read consecutively. Figure 7 shows an example of the entire sequence of commands necessary to perform the page read operation. For clarity, only the first byte is shown.

FIGURE 7: PAGE READ (FIRST READ DATA BYTE)

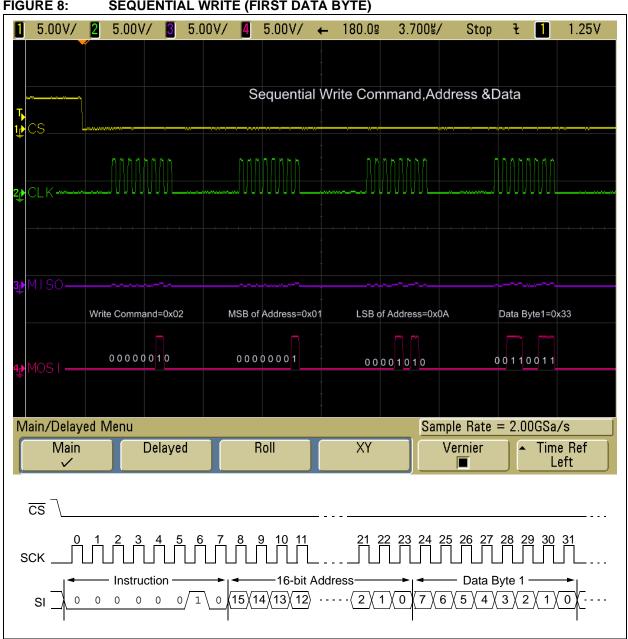

## **SEQUENTIAL WRITE**

This operation is very useful while writing a long string which is more than the page size (32 bytes). This operation needs Write command (0x02) to be sent followed by upper address byte and lower address byte. The SRAM keeps writing data as long as it receives clock and valid data. When the last location of memory is reached, the next location that is written is the first address (0x0000), that is, the internal address counter rolls over. Figure 8 depicts the entire sequence of commands necessary to perform the sequential write operation. For clarity, only the first byte is shown.

FIGURE 8: **SEQUENTIAL WRITE (FIRST DATA BYTE)**

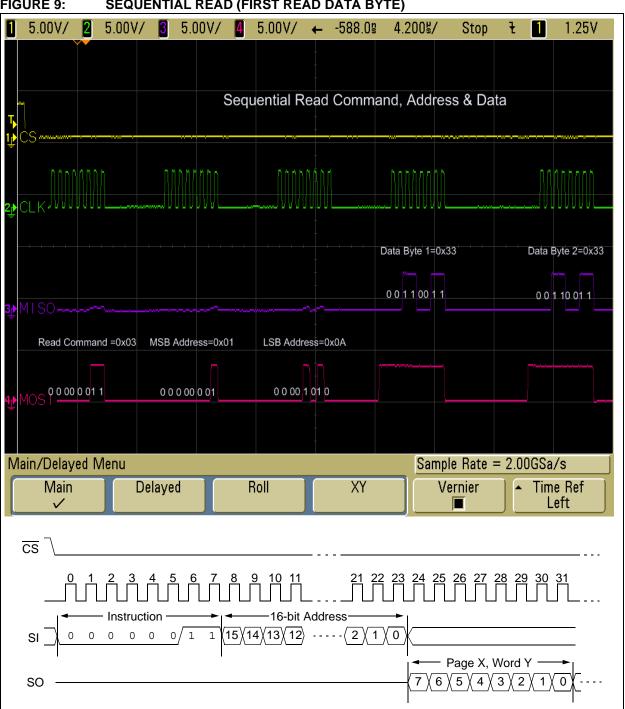

### SEQUENTIAL READ

Sequential read operation allows the entire array to be read from the SRAM. The internal address counter automatically increments and page boundaries are ignored. When the internal address counter reaches the end of the array, the address counter will roll over to 0x0000. Figure 9 shows an example of the sequence of commands necessary to perform a sequential read operation.

FIGURE 9: **SEQUENTIAL READ (FIRST READ DATA BYTE)**

# **AN1287**

# **CONCLUSION**

This application note offers designers a set of firmware routines to access SPI serial SRAM. The code demonstrates read and write operations for Byte, Page and Sequential modes. All the routines were written under the Microchip development environment MPLAB<sup>®</sup> IDE, using tools MPASM assembler, C18 and HI-TECH C compilers. The code was tested on Microchip's PICDEM™ 2 Plus development board with the connections shown in Figure 1 with the PIC16F887 and PIC18F45K20.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09