# AN1229

# Class B Safety Software Library for PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs

Authors: Veena Kudva & Adrian Aur Microchip Technology Inc.

# INTRODUCTION

This application note describes the Class B Safety Software Library routines that detect the occurrence of Faults in a single channel CPU. These routines have been developed in accordance with the IEC 60730 standard to support the Class B certification process. These routines can be directly integrated with the end user's application to test and verify the critical functionalities of a controller without affecting the end user's application.

This application note also describes the Application Programming Interface (API) functions that are available in the Class B Safety Software Library.

The Class B safety software routines can be called periodically at start-up or run time to test the following components:

- CPU Registers

- CPU Program Counter

- Invariable Memory

- Variable Memory

- Clock

- Interrupt Handling and Execution

This application note also outlines various techniques, which are not part of the Class B Safety Software Library, to test components such as external communication, timing, I/O periphery, analog I/O and analog multiplexer.

| Note: | The term 'IEC 60730 standard' used in    |  |

|-------|------------------------------------------|--|

|       | this document refers to the "IEC 60730-1 |  |

|       | ed.3.2" Copyright © 2007 IEC, Geneva,    |  |

|       | Switzerland. www.iec.ch.                 |  |

# OVERVIEW OF THE IEC 60730 STANDARD

Note: "The author thanks the International Electrotechnical Commission (IEC) for permission to reproduce information from its International Standard IEC 60730-1ed.3.2 (2007). All such extracts are copyright of IEC, Geneva, Switzerland. All rights reserved. Further information on the IEC is available from www.iec.ch. IEC has no responsibility for the placement and context in which the extracts and contents are reproduced by the author, nor is IEC in any way responsible for the other content or accuracy therein."

The IEC 60730 standard defines the test and diagnostic methods that ensure the safe operation of the controlled equipment used in household appliances. Annex H of the IEC 60730 standard classifies the software into the following categories (see **Appendix B: "IEC 60730-1 Table H.11.12.7**"):

- Class A

- Class B

- Class C

The Class B Safety Software Library implements the important test and diagnostic methods that fall into the Class B category. These methods use various measures to detect and respond to the software-related Faults and errors.

According to the IEC 60730 standard, the controls with functions that fall into the Class B category should have one of the following structures:

• Single Channel with Functional Test

In this structure, the Functional test is executed prior to the application firmware execution.

· Single Channel with Periodic Self-Test

In this structure, the Periodic tests are embedded within the firmware, and the self-test occurs periodically while the firmware is in Execution mode.

• Dual Channel without Comparison

In this structure, two independent methods execute the specified operations.

# SYSTEM REQUIREMENTS

The following system requirements are recommended to run the Class B Safety Software Library:

- For the tests that require the independent time slot monitoring, the system hardware must be provided with at least two independent clock sources (e.g., crystal oscillator and line frequency).

- The user application determines whether the interrupts need to be enabled or disabled during the execution of the Class B Safety Software Library.

If an interrupt occurs during the execution of the Class B Safety Software Library routine, an unexpected change may occur in any of the registers. Therefore, when the Interrupt Service Routine (ISR) executes, the contents of the register will not match the expected content, and the ISR will return an incorrect result.

# CLASS B SAFETY SOFTWARE LIBRARY

The Class B Safety Software Library, which applies to 8bit, 16-bit, and 32-bit devices, includes several APIs, which are intended to maximize application reliability through Fault detection. These APIs help meet the IEC 60730 standard compliance. The following tests can be implemented using this library:

- CPU Register Test

- Program Counter Test

- Variable Memory Test

- Invariable Memory (Flash/EEPROM) Test

- Interrupt Test

- Clock Test

In the following sections, the test description and the implementation details are discussed for each test. In addition, each section also lists the APIs that are required to execute the corresponding test for supported architectures.

# **CPU Register Test**

The CPU Register test implements the functional test H.2.16.5 defined by the IEC 60730 standard. It detects stuck-at Faults in the CPU registers. This ensures that the bits in the registers are not stuck at a value '0' or '1'; this is a non-destructive test.

This test performs the following major tasks:

- 1. The contents of the CPU registers to be tested are saved on the stack before executing the routine.

- The registers are tested by first successively writing the binary sequences (length is dependant upon architecture), 010101... followed by 101010... into the registers, and then reading the values from these registers for verification.

- 3. The test returns an error code if the returned values do not match.

Note: The interrupts should be disabled during the execution of the CPU Register test so that the register integrity is preserved at all times.

#### **API FUNCTIONS**

The following API functions implement the CPU Register test:

- SSL\_8bit\_CPU\_RegisterTest (PIC10/12/16)

- SSL\_8bitsFamily\_CPU\_RegisterTest (PIC18)

- SSL\_16bitsFamily\_CPU\_RegisterTest

- SSL\_32bitsFamily\_CPU\_RegisterTest

# Program Counter Test

The Program Counter (PC) test implements the functional test H.2.16.5 defined by the IEC 60730 standard. The PC holds the address of the next instruction to be executed.

The test performs the following major tasks:

- 1. The PC test invokes the functions that are located in the Flash memory at different addresses.

- 2. These functions return a unique value.

- 3. The returned value is verified using the PC test function.

- 4. If the values match, the PC branches to the correct location.

**Note 1:** The user application defines the address where the PC branches.

**2:** The size of the program memory varies by device. Refer to the specific device data sheet for more details.

# EXAMPLE 1: LINKER SCRIPT MODIFICATION

/\* The modified linker script \*/

The customized linker script defines the addresses where these functions reside in the Flash memory. The functions placed at these addresses return a unique value, which is the starting address of the called function. Example 1 shows how to modify the linker script to place a function in the Flash memory. The actual Flash address space is processor dependent. Please refer to the processor-specific linker script example provided.

# **API FUNCTIONS**

The following API functions implement the PC test:

- SSL\_8bit\_PCtest (PIC10/12/16)

- SSL\_8bitsFamily\_PCtest (PIC18)

- SSL\_16bitsFamily\_PCtest

- SSL\_32bitsFamily\_PCtest

SslTestSection1 0x900:

{

\*(.SslTestSection1);

} program

/\* The SSL\_TestFunction1 function\*/

long \_\_attribute\_\_((\_\_section\_\_(``.SslTestSection1"))) SSL\_TestFunction1()

{

return((long)&SSL\_TestFunction1);

}

# Invariable Memory (Flash/EEPROM) Test

The Invariable Memory (Flash/EEPROM) test implements the periodic modified checksum H.2.19.3.1 defined by the IEC 60730 standard. It detects the single bit Faults in the invariable memory. The invariable memory in a system, such as Flash and EEPROM memory, contains data that is not intended to vary during the program execution. The Flash/EEPROM Invariable Memory test computes the periodic checksum using the Cyclic Redundancy Check (CRC). Several standards are used today for the CRC calculation. The characteristics of the CRC divisor vary from 8 to 32 bits depending on the polynomial that is used. The width of a divisor determines its ability to detect the errors. Some commonly used CRC divisors are as follows:

- CRC-16 = 1 1000 0000 0000 0101 = 8005 (hex)

- CRC-CCITT = 1 0001 0000 0010 0001 = 1021 (hex)

- CRC-32 = 1 0000 0100 1100 0001 0001 1101 1011 0111 = 04C11DB7 (hex)

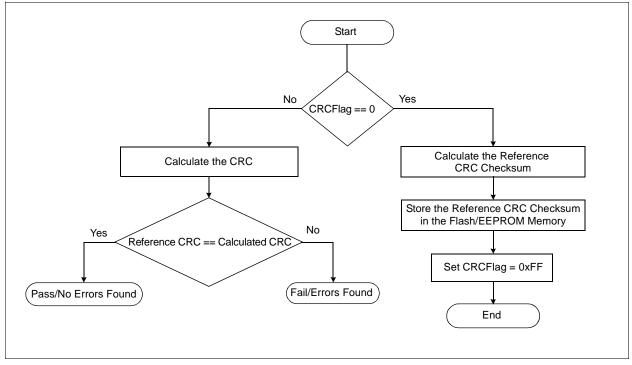

Figure 1 illustrates the flowchart for the Invariable Memory test.

The CRC16 calculation function returns the final CRC value that can be used to perform the following:

- 1. At the system start-up, the computed CRC checksum can be used as a reference checksum if the CRC\_Flag is set to 0x00.

- The reference checksum is stored in the Flash or EEPROM memory and the CRC flag is set to 0xFF.

- 3. The CRC16 calculation function can be called periodically if the CRC flag is set to 0xFF.

- 4. The checksum calculated from step 3 is compared with the reference checksum.

- 5. If both values match, a status bit can be set by the user application to indicate that the invariable memory has passed the test and no errors were found.

#### **API FUNCTIONS**

The following API functions implement the Invariable Memory test:

- SSL\_8bit\_EEPROMtest\_CRC16 (PIC10/12/16)

- SSL\_8bitsFamily\_EEPROMtest\_CRC16 (PIC18)

- SSL\_8bitsFamily\_Flashtest\_CRC16 (PIC18)

- SSL\_16bitsFamily\_Flashtest\_CRC16

- SSL\_16bitsFamily\_EEPROMtest\_CRC16

- SSL\_32bitsFamily\_Flashtest\_CRC16

Note: The 16-bit EEPROM test applies only to dsPIC30F devices.

# FIGURE 1: FLOWCHART FOR THE INVARIABLE MEMORY TEST

# **Variable Memory Test**

The Variable Memory test implements the Periodic Static Memory test H.2.19.6 defined by the IEC 60730 standard. It detects single bit Faults in variable memory. The variable memory contains data, which is intended to vary during program execution. The RAM Memory test is used to determine if any bit of the RAM memory is stuck at '1' or '0'. The March Memory test and Checkerboard test are some of the widely used static memory algorithms for checking the DC Faults.

The following tests can be implemented using the Class B Safety Software Library:

- March Test

- March C Test

- March C Minus Test

- March B Test

#### MARCH TEST

A March test performs a finite set of operations on every memory cell in a memory array. Each operation performs the following tasks:

- 1. Writes '0' to a memory cell (w0).

- 2. Writes '1' to a memory cell (w1).

- 3. Reads the expected value '0' from a memory cell (r0).

- 4. Reads the expected value '1' from a memory cell (r1).

#### March Test Notations

Figure 2 illustrates the notations that are used in the March test.

#### FIGURE 2: MARCH TEST NOTATIONS

- ↑: Arranges the address sequence in ascending order.

- I Arranges the address sequence in descending order.

- 1: Arranges the address sequence in either ascending or descending order.

- *r*<sub>0</sub>: Indicates a read operation (reads '0' from a memory cell).

- *r*<sub>1</sub>: Indicates a read operation (reads '1' from a memory cell).

- w0: Indicates a write operation (writes '0' to a memory cell).

- w1: Indicates a write operation (writes '1' to a memory cell).

**Note:** The March memory functions do not test the Stack area of the RAM. The following special functions are provided for the Stack area test:

SSL\_8bitsFamily\_RAM\_STACKtest\_MarchC (PIC18) SSL\_16bitsFamily\_RAM\_STACKtest\_MarchC SSL\_32bitsFamily\_RAM\_STACKtest\_MarchC

# MARCH C TEST

The March C test is used to detect the following types of Fault in the variable memory:

- Stuck-at Fault

- Addressing Fault

- Transition Fault

- Coupling Fault

The complexity of this test is 11n, where n indicates the number of bits in the memory. This test is a destructive test (i.e., memory contents are not preserved). Therefore, it is designed to run at the system start-up before initializing the memory and the run-time libraries.

Example 2 shows the pseudocode that demonstrates the implementation of the March C test.

# **API FUNCTIONS**

The following API functions implement the March C test:

- SSL\_8bit\_RAMtest\_MarchC (PIC10/12/16)

- SSL\_8bitsFamily\_RAMtest\_MarchC (PIC18)

- SSL\_8bitsFamily\_RAM\_STACKtest\_MarchC (PIC18)

- SSL\_16bitsFamily\_RAMtest\_MarchC

- SSL\_16bitsFamily\_RAM\_STACKtest\_MarchC

- SSL\_32bitsFamily\_RAMtest\_MarchC

- SSL\_32bitsFamily\_RAM\_STACKtest\_MarchC

Figure 3 illustrates a March C algorithm.

| FIGURE 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MARCH C ALGORITHM         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| MarchC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| Ĵ(w0); Ĵ(r0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | w1); 	Î( <i>r</i> 1, ₩0); |

| <b>(</b> <i>r</i> 0); <b>(</b> <i>r</i> 0, <b>(</b> <i>r</i> 0); <b>(</b> <i>r</i> | w1);↓(r1,w0);↑(r0)        |

| }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

# EXAMPLE 2: PSEUDOCODE FOR MARCH C TEST

```

for(i=0;i<=(n-1);i++)

x(i) = 0;

/*write background to zero*/

for(i=0;i<=(n-1);i++)</pre>

{

if (x(i)==0)

x(i) =1;

else

return fail;

}

for(i=0;i<=(n-1);i++)

{

if(x(i) == 1)

x(i)=0;

else

return fail;

}

for(i=(n-1);i>=0;i--)

{

if(x(i) == 0)

x(i)=1;

else

return fail;

for(i=(n-1);i>=0;i--)

{

if(x(i)==1)

x(i)=0;

else

return fail;

for(i=(n-1);i>=0;i--)

{

if(x(i)==0) {}

else

return fail

}

return pass;

```

#### MARCH C MINUS TEST

The March C Minus test is used to detect the following types of Fault in the variable memory:

- Stuck-at Fault

- Addressing Fault

- Transition Fault

- Coupling Fault

The complexity of this test is 10n, where n indicates the number of bits in the memory.

This test is a destructive test. Therefore, it is designed to run at the system start-up before initializing the memory and the run-time libraries.

#### **API FUNCTIONS**

API The following functions implement the March C Minus test:

- SSL\_8bit\_RAMtest\_MarchC\_Minus (PIC10/12/16)

- SSL\_8bitsFamily\_RAMtest\_MarchC\_Minus (PIC18)

- SSL\_16bitsFamily\_RAMtest\_MarchC\_Minus

- SSL\_32bitsFamily\_RAMtest\_MarchC\_Minus

Figure 4 illustrates a March C Minus algorithm.

#### FIGURE 4: MARCH C MINUS ALGORITHM

MarchCMinus

{

}

(w0); (r0, w1); (r1, w0);

$\Downarrow (r0, w1); \ \Downarrow (r1, w0); \ \Uparrow (r0);$

# MARCH B TEST

The March B is a non-redundant test that can detect the following types of Fault:

- Stuck-at

- Linked Idempotent Coupling

- Inversion Coupling

This test is of complexity 17n, where n indicates the number of bits in the memory.

Figure 5 illustrates a March B algorithm.

# FIGURE 5: MARCH B ALGORITHM

```

MarchB

{

(v0); \uparrow (r0, w1, r1, w0, r0, w1); \uparrow (r1, w0, w1);

\downarrow (r1, w0, w1, w0); \downarrow (r0, w1, w0);

```

Example 3 shows the pseudocode that demonstrates the implementation of the March B test.

# **API FUNCTIONS**

The following API functions implement the March B test:

- SSL\_8bit\_RAMtest\_MarchB (PIC10/12/16)

- SSL\_8bitsFamily\_RAMtest\_MarchB (PIC18)

- SSL\_16bitsFamily\_RAMtest\_MarchB

- SSL\_32bitsFamily\_RAMtest\_MarchB

- Note 1: The user application should allocate appropriate space for the stack before executing any of the March tests (see the details in the specific API function description). The stack must be allocated at an appropriate address so that it does not get overwritten during the test execution.

- 2: Depending on the architecture, it is recommended that the stack be placed at the beginning or at the end of the data memory. The user application should specify an address such that it does not overlap other statically allocated resources (e.g., the MPLAB<sup>®</sup> ICD 2 RAM space or other debugger used RAM space).

EXAMPLE 3: PSEUDOCODE FOR MARCH B TEST

```

for(i=0;i<=(n-1);i++)</pre>

x(i)=0;

/*write background to zero*/

for(i=0;i<=(n-1);i++)

{

if(x(i)=0)

x(i)=1;

else

return fail;

if(x(i)==1)

x(i)=0;

else

return fail;

if(x(i)==0)

x(i)=1;

else

return fail;

for(i=0;i<=(n-1);i++)</pre>

{

if(x(i)==1)

{

x(i)=0;

x(i)=1;

ļ

élse

return fail;

for(i=(n-1);i>=0;i--)

{

if(x(i)=1)

{

x(i)=0;

x(i)=1;

x(i)=0;

}

else

return fail;

for(i=(n-1);i>=0;i--)

{

if(x(i)==0)

x(i)=1;

x(i)=0;

}

élse

return fail;

}

return pass;

```

# CHECKERBOARD RAM TEST

The Checkerboard RAM test writes the checkerboard patterns to a sequence of adjacent memory locations. This test is performed in units (memory chunks) of architecture-specific sizes (2 bytes for 8-bit architecture, 4 bytes for 16-bit architecture, 64 bytes for 32-bit architecture). This is a non-destructive memory test.

This test performs the following major tasks:

- 1. Saves the contents of the memory locations to be tested in the CPU registers.

- 2. Writes the binary value (length is dependent upon architecture) 101010... to the memory location, 'N', and the inverted binary value, 010101..., to the memory location, 'N+1', and so on, until the whole memory chunk is filled.

- 3. Reads the contents of all the memory locations in the current chunk and verifies its contents. If the values match, the function continues; otherwise it stops and returns an error.

- 4. Step 2 and 3 are repeated by writing the inverted pattern to the same locations.

- 5. Once a memory chunk is completed the test of the next chunk is started until all of the requested memory area is tested.

#### **API FUNCTIONS**

The following API functions implement the Checkerboard RAM test:

- SSL\_8bit\_RAMtest\_CB (PIC10/12/16)

- SSL\_8bitsFamily\_RAM\_CB\_test (PIC18)

- SSL\_16bitsFamily\_RAMtest\_CheckerBoard

- SSL\_32bitsFamily\_RAMtest\_CheckerBoard

# Interrupt Test

The Interrupt test implements the independent time slot monitoring H.2.18.10.4 defined by the IEC 60730 standard. It checks whether the number of interrupts that occurred is within the predefined range.

The goal of the Interrupt test is to verify that interrupts occur regularly. The Interrupt test function can be invoked at specified time intervals. It is triggered by a timer or line frequency interrupt to monitor and verify the interrupt operation.

To keep track of the interrupts that occur frequently, a dedicated counter in each ISR can be decremented when an interrupt occurs. For example, if the Serial Peripheral Interface (SPI) is configured to generate an interrupt every 2 ms, the SPI will generate at least five interrupts in 10 ms. When a SPI interrupt occurs, the counter dedicated to keep track of the SPI interrupt is decremented. Thus, if the counter is initialized to five, the counter is decremented to zero in 10 ms. This is verified by the Interrupt test function that is triggered after every 10 ms.

To keep track of interrupts that occur rarely, a dedicated counter within the Interrupt test function is decremented if the specific interrupt did not occur during the last time interval. Refer to the example code, which is available for download from the Microchip web site (see **Appendix A: "Source Code"** for details.).

# **Clock Test**

According to the IEC 60730 standard, only harmonics and subharmonics of the clock need to be tested. The Clock test implements the independent time slot monitoring H.2.18.10.4 defined by the IEC 60730 standard. It verifies the reliability of the system clock (i.e., the system clock should be neither too fast nor too slow):

Depending on the choice of the reference clock, one of the following Clock tests can be used:

- Clock Test Using the Secondary Oscillator (Sosc)

- Clock Test Using the Line Frequency (50 Hz, 60 Hz)

#### **CLOCK TEST USING THE Sosc**

The Clock Test function is used to verify the proper operation of the CPU clock when the Sosc is used as a reference clock.

This test performs the following major tasks:

- 1. The LP secondary oscillator is used as an independent clock source or a reference clock source. This 32 kHz oscillator is used to clock the hardware Timer1.

- Usually, the Primary Oscillator (Posc) with Phase-Locked Loop (PLL) is the clock source to the CPU. The test uses a hardware timer that runs at the CPU clock frequency (Timer0 for 8bit architecture, Timer2 for 16-bit architecture and the CPU Core timer for 32-bit architecture).

- Timer1 is configured to overflow and generate an interrupt at specified time intervals (e.g., 1 ms).

- 4. The value of the hardware timer used to count the CPU clock counts is saved when Timer1 overflows. This value represents the number of CPU clock cycles elapsed in the 1 ms time period of the Sosc. If the number of clock cycles is outside a specified range, the function returns an error code.

#### **API FUNCTIONS**

The following API functions implement the Clock test:

- SSL\_8bitsFamily\_CLOCKtest (PIC18)

- SSL\_16bitsFamily\_CLOCKtest

- SSL\_32bitsFamily\_CLOCKtest

# CLOCK TEST USING THE LINE FREQUENCY (50 Hz, 60 Hz)

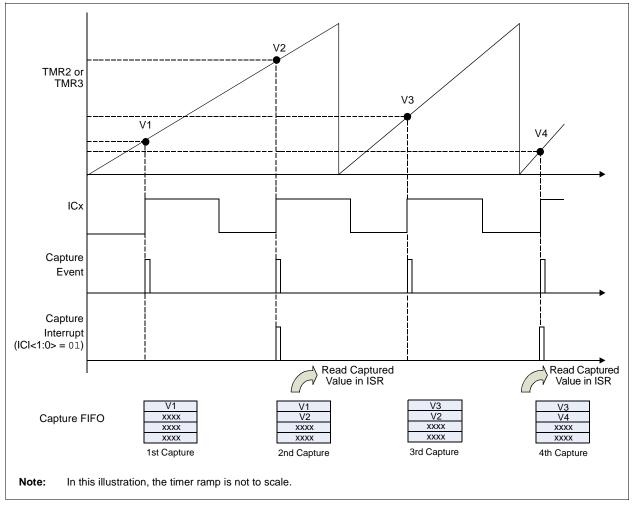

The Clock Test function is used to verify the proper operation of the CPU clock. The 50 Hz/60 Hz line frequency is used as an independent clock source or a reference clock source. The input capture module is used for the period measurement. The 50 Hz/60 Hz line frequency is fed to the Input Capture pin (IC1) of the respective device.

This test performs the following major tasks:

- 1. The IC1CON register is configured as follows:

- a) Hardware Timer2 is selected as the IC1 time base (Timer1 for PIC18).

- b) The capture operation is programmed to occur on every rising edge of the line frequency.

- c) A capture done event (interrupt) is programmed to occur on every second capture event

FIGURE 6: TIMER VALUE CAPTURE

- The Timer2 prescaler is configured so that the timer count does not time-out within 20 ms/ 16.66 ms (Timer1 for PIC18).

- 3. The capture is performed on every rising edge of line frequency. For period measurement, the capture done event (interrupt) is generated after taking two time-stamps (see Figure 6).

- The difference between the two time-stamps (V1 and V2) provides the timer period value. The number of CPU cycles in 20 ms/16.66 ms of the line frequency is computed as follows:

Number of Clock Cycles = ((V1 - V2) \* Timer2 Prescaler)

# **API FUNCTIONS**

The following API functions implement the Clock test:

- API Functions for 8-bit PIC MCUs (PIC18)

- SSL\_16bitsFamily\_CLOCKtest\_LineFreq

- SSL\_32bitsFamily\_CLOCKtest\_LineFreq

# Addressing of Variable and Invariable Memory and Internal Data Path

For single chip microcontrollers or digital signal controllers, such as PIC MCUs and dsPIC DSCs, the Periodic Static Memory test is used to test the variable memory, and the periodic checksum is used to test the invariable memory. These tests detect any stuck-at Fault in the internal address bus and internal data path.

# Addressing Wrong Address

This test is required only for microcontrollers with an external memory device.

# **External Communication**

The IEC 60730 Class B specifications suggest the following measures to ensure reliable communication between components:

# TRANSFER REDUNDANCY

The transfer redundancy is a Fault/error control technique that protects against coincidental and/or systematic errors in the input and output information. It is achieved by transferring the data between the transmitter and receiver. The data is transferred at least twice in succession and then compared.

# PROTOCOL TEST

The Protocol test is a Fault/error control technique in which the data is transferred to and from the computer components to detect errors in the internal communication protocol.

# CRC SINGLE WORD

A CRC polynomial is used to calculate the CRC checksum of the transmitted message. At the transmitting end, this CRC checksum is appended to the message before transmitting it. At the receiving end, the receiver uses the same CRC polynomial to compute the CRC checksum, and compares the computed value with the received value.

# Timing

The PIC MCUs and dsPIC DSCs have several dedicated communication interfaces, such as UART,  $I^2C^{TM}$  and SPI modules. The IEC 60730 Class B specifications suggest that these modules should use time slot monitoring to ensure that the communication occurs at the correct point in time.

# **Plausibility Check**

The plausibility checks on the I/O periphery, analog multiplexer and A/D convertor can be performed as follows:

#### **I/O PERIPHERY**

The plausibility check on an I/O pin can be performed by toggling the I/O and checking the state of the pin.

# ANALOG MULTIPLEXER

To verify the operation of the analog multiplexer, known voltage values are applied to all channels. These values are read and compared with the applied voltage for verification.

# A/D CONVERTER

To test the analog functions of the A/D converter, a known external voltage is applied to the analog inputs. The conversion results are then compared with the applied voltage.

# API FUNCTIONS FOR 8-BIT PIC MCUs (PIC10/12/16)

This section lists and describes the API functions that are available in the Class B Safety Software Library for 8-bit architecture (PIC10/12/16). The API functions are listed below followed by their individual detailed descriptions:

- SSL\_8bit\_CPU\_RegisterTest

- SSL\_8bit\_PCtest

- SSL\_8bit\_EEPROMtest\_CRC16

- SSL\_8bit\_RAMtest\_MarchC

- SSL\_8bit\_RAMtest\_MarchC\_Minus

- SSL\_8bit\_RAMtest\_MarchB

# SSL\_8bit\_CPU\_RegisterTest

# Description

This function implements the CPU Register test. The test successively writes the values 0x55 and 0xAA into the registers and then reads the values from these registers for verification. The function returns an error code if the values do not match. The contents of the register (W0) that returns the error code are not preserved. The contents of the CPU register to be tested is saved on a temporary register before executing the routine and is restored upon the completion of the test.

#### Include

None.

#### Prototype

int SSL\_8bit\_CPU\_RegisterTest(void);

# Arguments

None.

#### **Return Value**

| REGISTER_TEST_FAIL | Return value = 0 |

|--------------------|------------------|

| REGISTER_TEST_PASS | Return value = 1 |

# Remarks

None.

#### **Source File**

None.

#### TABLE 1: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory | 77 words     |

| Stack          | NONE         |

| Execution Time | 81 cycles    |

# SSL\_8bit\_PCtest

# Description

This function implements the PC test, which is a functional test of the PC. The test invokes the functions that are located in the Flash memory at different addresses. The *SSL\_ProgCounterTest.h* header file defines the addresses, where these functions reside in the Flash memory. The functions placed at these addresses return a unique value, which is the starting address of the called function. This returned value is verified using the *SSL\_Bbit\_PCtest* function.

#### Include

SSL\_ProgCounterTest.h

# Prototype

unsigned int SSL\_8bit\_PCtest(void);

# Arguments

None.

# **Return Value**

| PC_TEST_FAIL | Return value = 0 |

|--------------|------------------|

| PC_TEST_PASS | Return value = 1 |

#### Remarks

None.

# TABLE 2: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory | 107 words    |

| Stack          | 1 byte       |

| Execution Time | 92 cycles    |

#### SSL\_8bit\_EEPROMtest\_CRC16

# Description

This function implements the Invariable Memory test. It computes the CRC of the data located between the address, EEPROM\_STARTADDRESS, and the address, EEPROM\_ENDADDRESS. This function returns the final CRC value.

#### Include

SSL\_EEPROM\_CRC.h

# Prototype

unsigned int SSL\_8bits\_EEPROMtest\_CRC16(unsigned char startAddress, unsigned char endAddress)

# Arguments

| startAddress | Indicates the starting address of the data to be tested |

|--------------|---------------------------------------------------------|

| endAddress   | Indicates the ending address of the data to be tested   |

# **Return Value**

crc\_Result Holds the CRC result

#### Remarks

None.

#### Source File

None.

#### TABLE 3: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 149 words                  |

| Stack          | 1 byte                     |

| Execution Time | 1091 cycles <sup>(1)</sup> |

**Note 1:** The execution time specified here is for three EEPROM locations.

# SSL\_8bit\_RAMtest\_MarchC

# Description

This function implements the March C test. This test accesses an 8-bit word from the RAM memory. The address must be aligned to the data type and the length must be an integral multiple of the data width. This is a destructive test; therefore, this test can be executed at the system start-up before initializing the memory and the run-time libraries. The memory will be cleared when the control returns from the SSL\_8bit\_RAMtest\_MarchC function.

#### Include

SSL\_MarchCRamTest.h

# Prototype

unsigned char SSL\_8bit\_RAMtest\_MarchC(void);

#### Arguments

None.

#### **Return Value**

| MARCHC_RAM_TEST_FAIL | Return value = 0 |

|----------------------|------------------|

| MARCHC_RAM_TEST_PASS | Return value = 1 |

#### Remarks

None.

# Source File

SSL\_MarchCRamTest.c

#### TABLE 4: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 388 bytes                  |

| Stack          | 15 bytes                   |

| Execution Time | 3834 cycles <sup>(1)</sup> |

# SSL\_8bit\_RAMtest\_MarchC\_Minus

#### Description

This function implements the March C Minus test. This test accesses an 8-bit word from the RAM memory. The address must be aligned to the data type and the length must be an integral multiple of the data width. This is a destructive test; therefore, this test can be executed at the system start-up before initializing the memory and the run-time libraries. The memory will be cleared when the control returns from the SSL\_8bit\_RAMtest\_MarchCMinus function.

#### Include

SSL\_MarchCMInusRamTest.h

# Prototype

unsigned char SSL\_8bit\_RAMtest\_MarchCMinus(void);

#### Arguments

None.

#### **Return Value**

MARCHC\_RAM\_TEST\_FAIL Return value = 0

MARCHC\_RAM\_TEST\_PASS Return value = 1

#### Remarks

None.

# **Source File**

SSL\_MarchCMinusRamTest.c

#### TABLE 5: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 269 bytes                  |

| Stack          | 10 bytes                   |

| Execution Time | 3834 cycles <sup>(1)</sup> |

# SSL\_8bit\_RAMtest\_MarchB

# Description

This function implements the March B test. This test accesses a byte word from the RAM memory. The address must be properly aligned to the data type and the length must be an integral multiple of the data width. This is a destructive test; therefore, this test can be executed at system start-up before initializing the memory and the run-time library. The memory will be cleared when the control returns from the SSL\_8bit\_RAMtest\_MarchB function.

# Include

SSL\_MarchBRamTest.h

# Prototype

unsigned char SSL\_8bit\_RAMtest\_MarchB(void);

#### Arguments

None.

#### **Return Value**

| MARCHB_RAM_TEST_FAIL | Return value = 0 |

|----------------------|------------------|

| MARCHB_RAM_TEST_PASS | Return value = 1 |

# Source File

SSL\_MarchBRamTest.c

#### TABLE 6: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 453 bytes                  |

| Stack          |                            |

| Execution Time | 2761 cycles <sup>(1)</sup> |

# API FUNCTIONS FOR 8-BIT PIC MCUs (PIC18)

This section lists and describes the API functions that are available in the Class B Safety Software Library for the 8-bit architecture. The functions are listed below followed by their individual detailed descriptions:

- SSL\_8bitsFamily\_CPU\_RegisterTest

- SSL\_8bitsFamily\_PCtest

- SSL\_8bitsFamily\_Flashtest\_CRC16

- SSL\_8bitsFamily\_EEPROMtest\_CRC16

- SSL\_8bitsFamily\_RAM\_STACKtest\_MarchC

- SSL\_8bitsFamily\_RAMtest\_MarchC\_Minus

- SSL\_8bitsFamily\_RAMtest\_MarchB

- SSL\_8bitsFamily\_RAMtest\_CheckerBoard

- SSL\_8bitsFamily\_CLOCKtest

- SSL\_8bitsFamily\_CLOCKtest\_LineFreq

# SSL\_8bitsFamily\_CPU\_RegisterTest

# Description

This function implements the CPU Register test. The test successively writes the values 0x55 and 0xAA into the registers and then reads the values from these registers for verification. The function returns an error code if the values do not match. The contents of the register (W0) that returns the error code are not preserved. The contents of the CPU register to be tested is saved on a temporary register before executing the routine and is restored upon the completion of the test.

#### Include

None.

# Prototype

```

void SSL_8bitsFamily_CPU_RegisterTest(void);

```

# Arguments

None.

# **Return Value**

| REGISTER_TEST_FAIL | Return value = 0x86 |

|--------------------|---------------------|

| REGISTER_TEST_PASS | Return value = 0x00 |

# Remarks

None.

#### **Source File**

None.

#### TABLE 7: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory | 77 words     |

| Stack          | NONE         |

| Execution Time | 81 cycles    |

# SSL\_8bitsFamily\_PCtest

# Description

This function implements the PC test, which is a functional test of the PC. The test invokes the functions that are located in the Flash memory at different addresses. The *SSL\_PcTest.h* header file defines the addresses, where these functions reside in the Flash memory. The functions placed at these addresses return a unique value, which is the starting address of the called function. This returned value is verified using the *SSL\_8bitsFamily\_Pctest* function.

# Include

SSL\_PcTest.h

# Prototype

int SSL\_8bitsFamily\_PCtest(void);

# Arguments

None.

# **Return Value**

| PC_TEST_FAIL | Return value = 0 |

|--------------|------------------|

| PC_TEST_PASS | Return value = 1 |

# Remarks

None.

#### TABLE 8: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory | 107 words    |

| Stack          | 1 byte       |

| Execution Time | 92 cycles    |

# SSL\_8bitsFamily\_Flashtest\_CRC16

# Description

This function implements the Invariable Memory test. It computes the CRC of the data located between the address FLASH\_STARTADDRESS and the address FLASH\_ENDADDRESS. This function returns the final CRC value.

# Include

SSL\_Flash\_CRC.h

# Prototype

unsigned int SSL\_8bitsFamily\_Flashtest\_CRC16

(word32 startAddress,word32 endAddress, unsigned int crc\_Result);

#### ARGUMENTS

| startAddress | Indicates the starting address of the data to be tested |

|--------------|---------------------------------------------------------|

| endAddress   | Indicates the ending address of the data to be tested   |

| crc_Result   | Indicates the initial value of the CRC                  |

# **Return Value**

crc\_Result Holds the CRC result

#### Remarks

None.

#### TABLE 9: RESOURCE REQUIREMENTS

| Parameter      | Requirements              |

|----------------|---------------------------|

| Program Memory | 489 bytes                 |

| Stack          | 70 bytes                  |

| Execution Time | 446 cycles <sup>(1)</sup> |

# SSL\_8bitsFamily\_EEPROMtest\_CRC16

# Description

This function implements the Invariable Memory test. It computes the CRC of the data located between the address, EEPROM\_STARTADDRESS, and the address, EEPROM\_ENDADDRESS. This function returns the final CRC value.

#### Include

SSL\_EEPROM\_CRC.h

# Prototype

```

unsigned int SSL_8bitsFamily_EEPROMtest_CRC16(uReg32 startAddress, uReg32 endAddress,

unsigned int crc_Result);

```

# Arguments

| startAddress | Indicates the starting address of the data to be tested |

|--------------|---------------------------------------------------------|

| endAddress   | Indicates the ending address of the data to be tested   |

| crc_Result   | Indicates the initial value of the CRC                  |

# **Return Value**

crc\_Result Holds the CRC result

#### Remarks

None.

# Source File

None.

#### TABLE 10: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 149 words                  |

| Stack          | 1 byte                     |

| Execution Time | 1091 cycles <sup>(1)</sup> |

**Note 1:** The execution time specified here is for three EEPROM locations.

# SSL\_8bitsFamily\_RAMtest\_MarchC

# Description

This function implements the March C test. This test accesses an 8-bit word from the RAM memory. The address must be aligned to the data type and the length must be an integral multiple of the data width. This is a destructive test; therefore, this test can be executed at the system start-up before initializing the memory and the run-time libraries. The memory will be cleared when the control returns from the SSL\_8bitsFamily\_RAMtest\_MarchC function.

# Include

SSL\_MarchC.h

# Prototype

```

int SSL_8bitsFamily_RAMtest_MarchC(char * ramStartAddress,int ramSize);

```

# Arguments

ramStartAddressIndicates the starting address from where the March C algorithm starts reading the dataramSizeIndicates the number of bytes that are tested; the size must be an even number

# **Return Value**

| MARCHC_RAM_TEST_FAIL | Return value = 0 |

|----------------------|------------------|

| MARCHC_RAM_TEST_PASS | Return value = 1 |

#### Remarks

None.

# **Source File**

SSL\_MarchCRamTest.c

#### TABLE 11: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 388 bytes                  |

| Stack          | 15 bytes                   |

| Execution Time | 3834 cycles <sup>(1)</sup> |

# SSL\_8bitsFamily\_RAM\_STACKtest\_MarchC

# Description

This function implements the March C test on the RAM memory and stack. This test accesses an 8-bit word from the RAM memory. The address must be aligned to the data type and the length must be an integral multiple of the data width. It first tests the RAM memory and then the stack area by transferring the stack contents into the tested RAM area. After the stack is tested, it restores the contents of the stack. This is a destructive test; therefore, this test can be executed at system start-up before initializing the memory and the run-time libraries. The memory will be cleared when the control returns from the SSL\_8bitsFamily\_RAM\_STACKtest\_MarchC function.

#### Include

SSL\_MarchC\_RamAndStackTest.h

#### Prototype

```

int SSL_8bitsFamily_RAM_STACKtest_MarchC(char * ramStartAddress, unsigned int ramSize);

```

# Arguments

| ramStartAddress | Indicates the starting address from where the March C algorithm starts reading the data |

|-----------------|-----------------------------------------------------------------------------------------|

| ramSize         | Indicates the number of bytes that are tested; the size must be an even number          |

# **Return Value**

| MARCHC_RAM_ | _STACK_TEST_FAIL | Return value = 0 |

|-------------|------------------|------------------|

| MARCHC_RAM_ | _STACK_TEST_PASS | Return value = 1 |

#### Remarks

None.

#### Source File

SSL\_MarchCRamAndStackTest.c

#### TABLE 12: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 890 bytes                  |

| Stack          | 88 bytes                   |

| Execution Time | 1576 cycles <sup>(1)</sup> |

# SSL\_8bitsFamily\_RAMtest\_MarchC\_Minus

# Description

This function implements the March C test on the RAM memory and stack. This test accesses an 8-bit word from the RAM memory. The address must be aligned to the data type and the length must be an integral multiple of the data width. It first tests the RAM memory and then the stack area by transferring the stack contents into the tested RAM area. After the stack is tested, it restores the contents of the stack. This is a destructive test; therefore, this test can be executed at system start-up before initializing the memory and the run-time libraries. The memory will be cleared when the control returns from the SSL\_8bitsFamily\_RAM\_STACKtest\_MarchCMinus function.

# Include

SSL\_MarchC\_Minus.h

# Prototype

```

int SSL_8bitsFamily_RAMtest_MarchC_Minus(char * ramStartAddress, int ramSize);

```

# Arguments

| ramStartAddress | Indicates the starting address from where the March C algorithm starts reading the data |

|-----------------|-----------------------------------------------------------------------------------------|

| ramSize         | Indicates the number of bytes that are tested; the size must be an even number          |

# **Return Value**

| MARCHC_RAM_TEST_FAIL | Return value = 0 |

|----------------------|------------------|

| MARCHC_RAM_TEST_PASS | Return value = 1 |

# Remarks

None.

# **Source File**

SSL\_RamTest\_MarchCMinus.c

# TABLE 13: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory | 124 bytes    |

| Stack          | 15 bytes     |

| Execution Time | 1402 cycles  |

# SSL\_8bitsFamily\_RAMtest\_MarchB

#### Description

This function implements the March B test. This test accesses a byte word from the RAM memory. The address must be properly aligned to the data type and the length must be an integral multiple of the data width. This is a destructive test; therefore, this test can be executed at system start-up before initializing the memory and the run-time library. The memory will be cleared when the control returns from the SSL\_8bitsFamily\_RAMtest\_MarchB function.

#### Include

SSL\_MarchB.h

# Prototype

```

int SSL_8bitsFamily_RAMtest_MarchB(char * ramStartAddress, int ramSize);

```

#### Arguments

| ramStartAddress | Indicates the starting address from where the March B algorithm starts reading the data |

|-----------------|-----------------------------------------------------------------------------------------|

| ramSize         | Indicates the number of bytes that are tested; the size must be an even number          |

# **Return Value**

| MARCHB_TEST_FAIL | Return value = 0 |

|------------------|------------------|

| MARCHB_TEST_PASS | Return value = 1 |

# Source File

SSL\_MarchBRamTest.c

#### TABLE 14: RESOURCE REQUIREMENTS

| Parameter      | Requirements               |

|----------------|----------------------------|

| Program Memory | 453 bytes                  |

| Stack          |                            |

| Execution Time | 2761 cycles <sup>(1)</sup> |

# SSL\_8bitsFamily\_RAMtest\_CheckerBoard

# Description

This function implements the Checkerboard test on the RAM memory. The test is performed on the memory space specified by the variable, SIZE. The execution begins from the address defined by the variable, START\_RAM. The number of specified locations must be even.

# Include

SSL\_CheckerBoardTest.INC

# Prototype

unsigned char SSL\_8bitsFamily\_Ram\_CB\_test(void);

# Arguments

None.

# **Return Value**

| RAM_Test_Fail | Return value = 0x86 |

|---------------|---------------------|

| RAM_Test_Pass | Return value = 0x00 |

# Remarks

None.

# Source File

SSL\_CheckerBoard.asm

#### TABLE 15: RESOURCE REQUIREMENTS

| Parameter      | Requirements             |

|----------------|--------------------------|

| Program Memory | 321 bytes                |

| Stack          | 68 bytes                 |

| Execution Time | 43 cycles <sup>(1)</sup> |

#### SSL\_8bitsFamily\_CLOCKtest

# Description

This function implements the Clock test. It is used to verify the proper operation of the CPU clock. The TMR0 value of Timer0 is saved within the Timer1 interrupt handler. This value represents the number of CPU clock cycles elapsed in 1 ms time period of the Sosc. If the number of clock cycles is beyond the defined boundary, the function sets an error flag.

This test performs the following major tasks:

- 1. The LP secondary oscillator is used as an independent clock source or a reference clock source. This 32 kHz oscillator is used to clock Timer1.

- 2. The Posc with Phase-Locked Loop (PLL) is the clock source to the CPU. Timer0 runs at the CPU clock frequency.

- 3. Timer1 is configured to generate an interrupt at specified time intervals (e.g., 1 ms).

- 4. The TMR0 value of Timer0 is saved within the Timer1 interrupt handler. This value represents the number of CPU clock cycles elapsed in the 1 ms time period of the Sosc. If the number of clock cycles is beyond the defined boundary, the function sets an error flag.

For example, the following parameters are used to calculate the CLK\_MIN\_TIME and CLK\_MAX\_TIME values for a PIC18F device:

- Primary Oscillator: INTOSC

- FOSC: 8 MHz

- FCY: FOSC/4: (8 \* 10^6) / 4

- FCY: 2000000

- Secondary oscillator: 32 kHz

- Timer1 period: 31

Therefore, with 4% tolerance, the number of CPU clock cycles in 1ms (2000 cycles) are:

- CLK\_MIN\_TIME: 1920

- CLK\_MAX\_TIME: 2080

#### Include

SSL\_ClockTest.h

# Prototype

unsigned int SSL\_8bitsFamily\_CLOCKtest(void);

#### Arguments

None.

#### **Return Value**

| CLOCK_NO_ERROR | Return value = 1 |

|----------------|------------------|

| CLOCK_ERROR    | Return value = 0 |

# Remarks

None.

# SSL\_8bitsFamily\_CLOCKtest(Continued)

# Source File

SSL\_ClockTest.c

#### TABLE 16: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory |              |

| Stack          |              |

| Execution Time |              |

# SSL\_8bitsFamily\_CLOCKtest\_LineFreq

# Description

This function implements the line frequency Clock test. It is used to verify the proper operation of the CPU clock. It uses the following procedure to configure the IC1CON register:

- 1. The Timer1 module is selected as the IC1 time base.

- 2. An interrupt is generated on every second capture event.

- 3. The capture event is generated on every rising edge of the line frequency.

The IC1 pin generates an interrupt after every 20 ms if the line frequency is 50 Hz and after every 16.66 ms if the line frequency is 60 Hz. Timer1 is configured in such a way so that the timer count does not time-out within 20 ms/16.66 ms. The capture event is generated on every rising edge of the line frequency. For period measurement, the capture interrupt is generated twice and Timer1 count is stored in the 2nd interrupt routine.

If the number of clock cycles is beyond the defined boundary, the function sets an error flag.

For example, the following parameters are used to calculate CLK\_MIN\_TIME and CLK\_MAX\_TIME for a PIC18F device:

- Primary Oscillator: INTOSC

- FOSC: 8 MHz

- FCY: FOSC/4: (8 \* 10^6) / 4

- FCY: 2000000

The number of counts that will be counted in the 20ms is =  $0.02 \times 200000 = 40000$ . With a tolerance of 4%

- CLK\_MIN\_TIME: 38400

- CLK\_MAX\_TIME: 41600

#### Include

SSL\_ClockTest\_LineFreq.h

# Prototype

int SSL\_8bitsFamily\_CLOCKtest\_LineFreq(void);

# Arguments

None.

#### **Return Value**

| CLOCK_NO_ERROR | Return value = 1 |

|----------------|------------------|

| CLOCK_ERROR    | Return value = 0 |

#### Remarks

None.

#### **Source File**

SSL\_ClockTest\_LineFreq.c

#### TABLE 17: RESOURCE REQUIREMENTS

| Parameter      | Requirements |

|----------------|--------------|

| Program Memory |              |

| Stack          |              |

| Execution Time |              |

# API FUNCTIONS FOR 16-BIT PIC MCUs AND dsPIC DSCs

This section lists and describes the API functions that are available in the Class B Safety Software Library for 16-bit architecture. The API functions are listed below followed by their individual detailed descriptions:

- SSL\_16bitsFamily\_CPU\_RegisterTest

- SSL\_16bitsFamily\_PCtest

- SSL\_16bitsFamily\_Flashtest\_CRC16

- SSL\_16bitsFamily\_EEPROMtest\_CRC16

- SSL\_16bitsFamily\_RAMtest\_MarchC

- SSL\_16bitsFamily\_RAMtest\_MarchC\_Minus

- SSL\_16bitsFamily\_RAMtest\_MarchB

- SSL\_16bitsFamily\_RAMtest\_CheckerBoard

- SSL\_16bitsFamily\_CLOCKtest

- SSL\_16bitsFamily\_CLOCKtest\_LineFreq

# SSL\_16bitsFamily\_CPU\_RegisterTest

# Description