**AVIX Real Time Operating System**

# AVIX for PIC24-dsPIC Microchip MPLAB Port Guide

Product Version 5.0.0

© 2006-2012, AVIX-RT

All rights reserved. This document and the associated AVIX software are the sole property of AVIX-RT. Each contains proprietary information of AVIX-RT. Reproduction or duplication by any means of any portion of this document without the prior written consent of AVIX-RT is expressly forbidden.

AVIX-RT reserves the right to make changes to the specifications described herein at any time and without notice in order to improve design or reliability of AVIX. The information in this document has been carefully checked for accuracy; however, AVIX-RT makes no warranty pertaining to the correctness of this document.

#### Trademarks

AVIX, AVIX for PIC24-dsPIC, AVIX for PIC32MX and AVIX for CORTEX-M3 are trademarks of AVIX-RT. All other product and company names are trademarks or registered trademarks of their respective holders.

Warranty Limitations

AVIX-RT makes no warranty of any kind that the AVIX product will meet the USER's requirements, or will operate in the manner specified by the USER, or that the operation of the AVIX product will operate uninterrupted or error free, or that any defects that may exist in the AVIX product will be corrected after the warranty period. AVIX-RT makes no warranties of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose, with respect to the AVIX product. No oral or written information or advice given by AVIX-RT, its dealers, distributors, agents, or employees shall create any other warranty or in any way increase the scope of this warranty and licensee may not rely on any such information or advice.

AVIX-RT Maïsveld 84 5236 VC 's-Hertogenbosch The Netherlands

phone +31(0)6 15 28 51 77 e-mail info@avix-rt.com www www.avix-rt.com

Product Version 5.0.0 - II -

### **Table of Contents**

| <b>1</b><br>1.1                                                                       | Introduction                                                                                                                                                                                                                                                                                            |                                                                            |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2                                                                                     | Compiler selection and compatibility                                                                                                                                                                                                                                                                    | 2                                                                          |

| 3                                                                                     | Getting Started                                                                                                                                                                                                                                                                                         | 3                                                                          |

| <b>4</b><br>4.1                                                                       | How to Install AVIX<br>Directory structure and files                                                                                                                                                                                                                                                    |                                                                            |

| <b>5</b><br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.2.1<br>5.2.2<br>5.2.2<br>5.2.3 | Development Environment Settings<br>Settings for the MPLAB8x environment<br>Specify AVIX Include Path<br>Structure based function parameters<br>ELF object file type<br>Settings for the MPLABX environment<br>Specify AVIX Include Path<br>Structure based function parameters<br>ELF object file type | 8<br>9<br>10<br>11<br>11<br>12                                             |

| 6                                                                                     | Memory Model and Linking                                                                                                                                                                                                                                                                                | 14                                                                         |

| <b>7</b><br>7.1<br>7.2<br>7.3                                                         | Configuring AVIX<br>Configuration Parameters<br>Interrupt and Timer<br>Distributions                                                                                                                                                                                                                    | 15<br>20                                                                   |

| -                                                                                     |                                                                                                                                                                                                                                                                                                         | ~ 4                                                                        |

| 8                                                                                     | Stack usage and Interrupt Service Routines                                                                                                                                                                                                                                                              | 24                                                                         |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.3.1<br>9.3.2                                       | Stack usage and Interrupt Service Routines<br>Controller Specific Capabilities<br>Multi-Thread PSV/Extended Data Space usage<br>Table Page (TBLPAG) usage<br>DSP Functionality.<br>How to make AVIX DSP aware.<br>DSP Details.                                                                          | <b>26</b><br>26<br>27<br>27<br>28                                          |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.3.1                                                | Controller Specific Capabilities<br>Multi-Thread PSV/Extended Data Space usage<br>Table Page (TBLPAG) usage<br>DSP Functionality<br>How to make AVIX DSP aware                                                                                                                                          | 26<br>27<br>27<br>28<br>28<br>30<br>31<br>31                               |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.3.1<br>9.3.2<br><b>10</b><br>10.1<br>10.2          | Controller Specific Capabilities                                                                                                                                                                                                                                                                        | 26<br>27<br>27<br>28<br>28<br>30<br>31<br>31<br>32<br>34<br>34<br>34<br>35 |

# **Table of Figures**

| Figure 1: AVIX Main Setup Screen                      | 5 |

|-------------------------------------------------------|---|

| Figure 2: AVIX Directory Structure                    | 6 |

| Figure 3: Set AVIX Interface include path for MPLAB8x | 8 |

| Figure 4: Struct parameter project setting for MPLAB8x   | 9 |

|----------------------------------------------------------|---|

| Figure 5: ELF binary format project settings for MPLAB8x |   |

| Figure 6: Set AVIX Interface include path for MPLABX     |   |

| Figure 7: Struct parameter project setting for MPLABX    |   |

| Figure 8: ELF binary format project settings for MPLABX  |   |

| Figure 9: AVIX Sample Interrupt Controller Register Map  |   |

| Figure 10: AVIX based application memory layout          |   |

| ······································                   |   |

# **Table of Tables**

| Table 1: Project Setup Steps             | 3 |

|------------------------------------------|---|

| Table 2: Controller Family Header Files  |   |

| Table 3: AVIX Configuration Parameters   |   |

| Table 4: AVIX Distribution Capabilities  |   |

| Table 5: Registers (partly) used by AVIX |   |

# Table of Code Samples

| Code sample 1: Group AVIX Code Sections to prevent Linker Errors                 | 14 |

|----------------------------------------------------------------------------------|----|

| Code sample 2: How to declare an ISR using the compiler syntax                   | 24 |

| Code sample 3: How to declare an ISR using the AVIX software system stack syntax |    |

| Code sample 4: Using a memory pool in base or EDS memory                         |    |

| Code sample 5: Portable EDS pointer tagging                                      |    |

|                                                                                  |    |

# 1 Introduction

This document describes how to use AVIX with a controller belonging to one of the PIC24F, PIC24H, PIC24E, dsPIC30F, dsPIC33E or dsPIC33F families of microcontrollers using the MPLAB development environment combined with the C30/XC16 compiler suite.

This document forms an extension to the AVIX User Guide and Reference Guide and should be considered an indivisible part of it. Terms and abbreviations defined in the AVIX User Guide and Reference Guide are also applicable to this Port Guide.

The full name of the AVIX port described in this document is AVIX for PIC24-dsPIC. Whenever using the name AVIX throughout this document, this refers to AVIX for PIC24-dsPIC.

### 1.1 Reader Guidance

To find the information you are looking for as efficient as possible, here an overview is given of the different chapters this document contains.

The different chapters can be divided in three categories:

- 1. Chapter 2 contains background information on the compiler toolsuite AVIX can be used with.

- 2. **Chapter 3** contains a compact overview how to create an AVIX based application. When familiar with AVIX, this is all that is needed to get up and running.

- 3. Chapters 4, 5, 6 and 7 contain information how to; install AVIX, make required changes to the project settings, deal with linking large programs and configure AVIX. The information in these chapters is not pure background but essential to obtain a working project.

- 4. The remaining chapters can be considered to contain background information which is not essential to get up and running but do contain information about the way AVIX interacts with the application and with the underlying hardware. In more detail these are:

- Chapter 8, Stack usage and Interrupt Service Routines, provides a description of how to declare ISR's to make use of the AVIX system stack.

- **Chapter 9, Controller Specific Capabilities,** provides details about capabilities specific to the targeted controller families. Topics are use of the TBLPAG register for access to FLASH memory, use of the PSVPAG register for Program Space Visibility and use of DSP functionality<sup>1</sup>.

- Chapter 10, Using memory in the Extended Data Space, provides information how AVIX allows the memory in the Extended Data Space (EDS memory), to be used by your application.

- **Chapter 11, Power Management**, provides information how to use the power management capabilities offered by the controller and how this is supported by AVIX.

- **Chapter 12, Resource Usage**, description of the hardware resources used by AVIX and the rules to obey when these or related resources are required by the application.

<sup>&</sup>lt;sup>1</sup> DSP functionality is only available on controllers belonging to the dsPIC30F and dsPIC33F families of microcontrollers.

# 2 Compiler selection and compatibility

AVIX can be used with applications build using either the C30 or the newer XC16 compiler suite. Both compiler suites can be selected to be used from within the legacy MPLAB8x development environment or from the new MPLABX development environment.

Throughout this document a number of dialogs are shown as they are used by the MPLAB development environment to make specific project settings. These dialogs are based on the C30 compiler suite. When using the XC16 compiler suite, similar dialogs are presented by MPLAB8x in essence offering the exact same entry fields. Some of the content of the XC16 based dialogs may be a little different from those of the C30 based dialogs.

In case of using MPLAB8x, when switching between compiler toolsuites (either from C30 to XC16 or from XC16 to C30), a number of project settings are restored to their default values. Since AVIX depends on a number of custom project settings, after switching between compiler toolsuites, it is essential for these settings to be restored. For details on the applicable settings, see chapter 5.1

When using MPLABX, switching between compilers does not restore any other setting.

When referring to the compiler toolsuite in this document, use is made of the phrase C30/XC16 compiler suite to denote both compiler toolsuites may be used.

# **3 Getting Started**

This chapter contains a quick guide to get up and running with AVIX and the steps needed to create an AVIX based project.

AVIX can be used with the legacy Microchip development environment MPLAB8x and the new Microchip development environment MPLABX, both with the C30/XC16 compiler suite. Both environments require a number of mandatory project settings. These settings are mentioned in the steps described below referring §5 where the applicable settings are described in more detail.

AVIX virtually works out of the box and requires the following steps to be up and running with a new project:

| 1 | Install AVIX<br>See §4 for details. The names and relative order of directories created by the setup utility must<br>remain as specified since AVIX depends on this. The location where AVIX is installed is not<br>important but advised is to choose a project related location.                                                                                                                                                                                  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Create a new project<br>Create a new MPLAB project based on the C30/XC16 compiler suite. For MPLAB8x use<br><u><b>Project – Project Wizard</b></u> , for MPLABX use <b>File – New Project</b>                                                                                                                                                                                                                                                                       |

| 3 | Create the projects main source file and add to the project<br>Manually add a source file (.c) to the project containing function 'void avixMain(void)'. An<br>AVIX project does not contain a user provided function `main' which is implemented by AVIX.<br>The application must offer `avixMain' instead which is the entry point of an AVIX based<br>application.                                                                                               |

| 4 | Add AVIX configuration file (AVIXConfig.c) to the project<br>This AVIX file must be built as part of the project like any other project source file.                                                                                                                                                                                                                                                                                                                |

| 5 | Add AVIX library file (AVIX_PIC24-dsPIC_MICROCHIP_MPLAB_E_050000_FH.a <sup>2, 3</sup> ) to the project.<br>This AVIX file must be linked against the other project binaries                                                                                                                                                                                                                                                                                         |

| 6 | Add AVIX interface include path to project settings<br>The location of the AVIX 'Interface' directory must be added to the project settings. See §5.1.1<br>for details on the MPLAB8x environment and §5.2.1 for details on the MPLABX environment.                                                                                                                                                                                                                 |

| 7 | Allow the compiler to pass 'C' structs by value<br>AVIX is highly type safe, a feature requiring the compiler to pass 'C' structs by value. Change<br>the project settings to allow this by adding compiler flag –fno-pcc-struct-return. See §5.1.2 for<br>details on the MPLAB8x environment and §5.2.2 for details on the MPLABX environment.<br><i>This setting is highly important. An AVIX based application build without this setting will<br/>not work.</i> |

| 8 | Set the project to generate binary files according the ELF format<br>The AVIX library is distributed in the ELF format. For compatibility the project specific source<br>files must be build according the same binary format. See §5.1.3 for details on the MPLAB8x<br>environment and §5.2.3 for details on the MPLABX environment.                                                                                                                               |

#### Table 1: Project Setup Steps

<sup>&</sup>lt;sup>3</sup> Library AVIX\_PIC24-dsPIC\_MICROCHIP\_MPLAB\_E\_050000\_FH.a is for use with PIC24F, PIC24H, dsPIC30F and dsPIC33F controllers. When using PIC24E or dsPIC33E controllers, use library AVIX\_PIC24-dsPIC\_MICROCHIP\_MPLAB\_E\_050000\_EP.a instead.

Product Version 5.0.0

<sup>&</sup>lt;sup>2</sup> The capital E in the file name denotes the library of an Extended distribution. Depending on the type of distribution, the filename may be different.

The result of the above steps is a project that builds. At this point however, the application does not yet use any AVIX function resulting in the linker ignoring the AVIX library. This in turn results in the linker complaining function <code>`main'</code>, which is implemented in this library, cannot be found.

To solve this, AVIX functions must be called from application code, a step required anyway.

From this point on, application code will be added to the project in the form of threads, ISR's and DIH's. Threads are separate 'C' functions that are registered with AVIX so they will run as a thread. Thread functions are typically registered from 'avixMain' using function avixThread\_Create. See the AVIX User Guide and Reference Guide for details.

Function avixMain is executed with all interrupts disabled. For AVIX to work correctly it is essential during execution of avixMain interrupts remain disabled. Make sure not to enable interrupts during execution of avixMain, neither direct nor indirect by (third party) functions being called.

# 4 How to Install AVIX

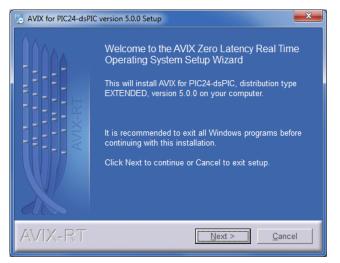

AVIX is distributed in the form a Windows based setup utility, the opening screen of which is shown in Figure 1. Note that the content of this screen may vary based on the type of distribution you have acquired.

Figure 1: AVIX Main Setup Screen

Installing AVIX is very straightforward and the only relevant information that is to be provided is the directory where AVIX is to be installed.

When pressing <u>N</u>ext, the install procedure will start. During the install process you will be asked a number of questions allowing you to install those parts of AVIX you need in the directory of your choice.

Note that the AVIX setup utility does not install any executables apart from an uninstall utility named uninstall.exe. This utility is installed in a directory named Uninstall which is created in the main installation directory that is selected as part of the install procedure. Besides this uninstall utility, directory Uninstall contains a number of additional files needed by the uninstall utility.

AVIX can be uninstalled by running this utility through "Add or Remove Programs" present in the Windows Control Panel or from the Windows Start Menu shortcut created as part of the install process. It is not possible to directly run uninstall.exe.

### 4.1 Directory structure and files

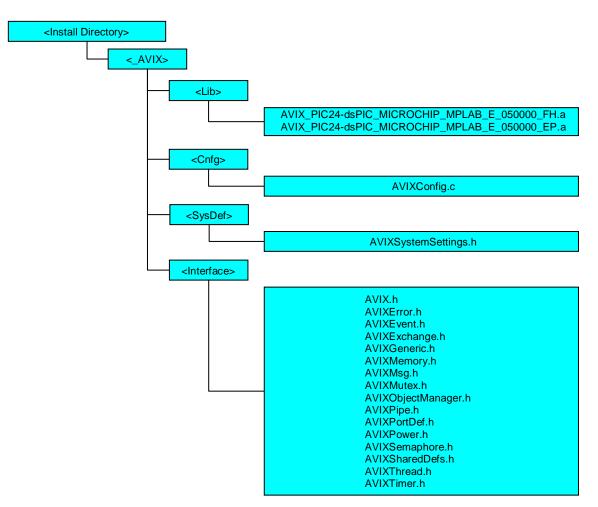

After installing AVIX, the following directory/file structure is created where the root, <Install Directory>, is the directory provided during the install procedure<sup>4</sup>:

Figure 2: AVIX Directory Structure

The names and relative order of directories 'Lib', 'Cnfg', 'SysDef' and 'Interface' must remain as shown in Figure 2 since the build process depends on this.

Below an overview is given of the installed files. Source files requiring AVIX functionality can include file AVIX.h. Optionally the specific header for the desired functionality can be included. For ease of use this is however not advised since AVIX.h in itself is always sufficient.

<sup>&</sup>lt;sup>4</sup> Depending on options offered during installation, additional directories may be created under the <Project Directory> containing for instance utility software. These additional directories and the files contained in them do not belong to the core of AVIX but are intended to be used with AVIX. When applicable, these files are documented in separate documents.

- AVIX\_PIC24-dsPIC\_MICROCHIP\_MPLAB\_E\_050000\_FH.a: Contains the AVIX code. This is a library file that must be linked in the project. The capital 'E' in this filename denotes an extended distribution. Depending on the type of distribution used, another character may be present in the filename. (FH) denotes this library is for the F and H parts (PIC24F, PIC24H, dsPIC30F and dsPIC33F). When using a PIC24E or dsPIC33E controller, use library AVIX\_PIC24-dsPIC\_MICROCHIP\_MPLAB\_E\_050000\_EP.a instead.

- AVIXSystemSettings.h: File containing the configuration settings as described in §7. *This file does never need to be explicitly included.*

- **AVIXConfig.c**: Source file needed for configuring AVIX through the settings in AVIXSystemSettings.h. *This file must be compiled and linked as part of the project under development.*

- AVIX.h: Header file including all other header files. Including this header file is sufficient to use all AVIX functions without including one of the specific header files.

- AVIXError.h: Header file to include when the error facility is used.

- **AVIXEvent.h**: Header file to include when event group functionality is used.

- **AVIXExchange.h:** Header file to include when exchange functionality is used.

- AVIXGeneric.h: Header containing generic definitions used from the other header files. *This file does never need to be explicitly included.*

- **AVIXMemory.h** Header containing definitions for memory pool functions.

- AVIXMsg.h: Header file to include when message functionality is used.

- **AVIXMutex.h**: Header file to include when mutex functionality is used.

- AVIXObjectManager.h: Header file containing generic definitions related to kernel object handling used for the other header files. This file does never need to be explicitly included.

- **AVIXPipe.h**: Header file to include when pipe functionality is used.

- AVIXPortDef.h: Header containing platform definitions, used by other headers. *This file does never need to be explicitly included.*

- AVIXPower.h: Header file to when power management functionality is used.

- **AVIXSemaphore.h**: Header file to include when semaphore functionality is used.

- AVIXSharedDefs.h: Header file with definitions shared between the configuration file and the AVIX library.

This file does never need to be explicitly included.

- **AVIXThread.h**: Header file to include when thread functionality is used.

- **AVIXTimer.h**: Header file to include when timer functionality is used.

# 5 Development Environment Settings

AVIX can be used with the legacy Microchip development environment MPLAB8x and the new MPLABX, both with the C30/XC16 compiler suite. A description of these environments falls outside the scope of this document. To use AVIX from within these environments, a number of AVIX specific project settings are however required which are described in this chapter.

### 5.1 Settings for the MPLAB8x environment

This chapter contains mandatory projects settings when using AVIX with the legacy Microchip development environment MPLAB8x.

### 5.1.1 Specify AVIX Include Path

An AVIX based project must have access to the directory containing the AVIX interface files, this location must be added to the MPLAB8x project settings.

Open the applicable dialog through <u>*Project - Build Options... - Project – Directories Tab.*</u> Select 'Include Search Path' from the 'Show Directories for:' dropdown control.

The dialog is shown in Figure 3.

The include path entered depends on the location where AVIX is installed. The value shown is based on AVIX being installed in the project directory.

|                             |   | Build Options For Pro                                                                                                                      | ject "AVIX16.m | sp"    | ? 🛛             |

|-----------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|-----------------|

|                             |   | MPLAB ASM30                                                                                                                                | MPL            | AB C30 | MPLAB LINK30    |

| Include Path to             | X | Directories                                                                                                                                | Custom Build   | Trace  | ASM30/C30 Suite |

| locate AVIX<br>Header Files |   | Directories and Sear<br>Show directories for<br>New<br>(\_AVIXVInterface<br>Build Directory Polic)<br>(> Assemble/Comp<br>(> Assemble/Comp | : Include Sea  | Down   |                 |

|                             |   | L L                                                                                                                                        | ОК             |        | Apply Help      |

Figure 3: Set AVIX Interface include path for MPLAB8x

### 5.1.2 Structure based function parameters

The functions offered on the AVIX API use 'C' structures. The C30/XC16 compiler suite allows for structures to be passed by value or by reference. To implement the high level of type safety the AVIX library is built based on passing structures by value. This implies that code using AVIX functions has to use the same mechanism in order to be compatible with the library.

This is accomplished by using compiler flag **-fno-pcc-struct-return**.

Open the applicable dialog through *Project - Build Options... - Project – MPLAB C30 Tab* and add the required flag according Figure 4.

It is essential to select checkbox 'Use Alternate Settings' in order for the setting to be used.

A consequence of using 'Alternate Settings' is that settings made through one of the dialogs (like for instance the compiler optimization level) have to be copied manually to the Alternate Settings field in order to be effective. When for instance changing the compiler optimization level to O3 through the applicable entry, this value will be entered in the default dialog field for settings. After making the setting, manually copy this to the field also used to enter –fno-pcc-struct-return.

Setting flag **-fno-pcc-struct-return** requires use of alternate settings (checkbox "Use Alternate Settings" in the dialog shown in Figure 4. Activating alternate settings implies that changes to the project settings made in the regular way have to be manually copied to the same field where flag – fno-pcc-struct-return is contained in, in order to be persistent when closing this dialog.

|                                                       | Build Options For Project "test.mcp"                                                                                                                                                                                                                             |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | Directories Custom Build Trace ASM30/C30 Suite<br>MPLAB ASM30 MPLAB C30 MPLAB LINK30                                                                                                                                                                             |

| Select to activate<br>manually added<br>compile flags | Categories: Categories: Additional warnings Generate Command Line Generate debugging information Gupport all ANSI-standard programs Make warnings into errors Guse 64-bit double Preprocessor Macros Add Remove Remove Remove All Inherit global settings g-Wall |

| Add flag to<br>pass C structs<br>by value.            | OK Cancel Apply Help                                                                                                                                                                                                                                             |

Figure 4: Struct parameter project setting for MPLAB8x

#### 5.1.3 ELF object file type

The AVIX library is distributed in the ELF format. For compatibility the project specific source files must be build according the same binary format. Selecting the ELF binary format is done through through the project settings dialog.

Open the applicable dialog through Project - Build Options ... - Project - ASM30/C30 Suite Tab and select the desired option according Figure 5.

|                                      | Build Options For Project "test.mcp"                                                                                                                                                                                                                                                               |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select<br>ELF/DWARF<br>binary format | MPLAB ASM30 MPLAB C30 MPLAB LINK30<br>Directories Custom Buld Trace ASM30/C30 Suite<br>Categories: [All Options]<br>Generate Command Line<br>Corp. CoFF<br>© ELF/DWARF<br>Target Type<br>© Build normal target (invoke LINK30)<br>© Build ibrary target (invoke LINK30)<br>© Build generic library |

|                                      |                                                                                                                                                                                                                                                                                                    |

|                                      | OK Cancel Apply Help                                                                                                                                                                                                                                                                               |

Figure 5: ELF binary format project settings for MPLAB8x

#### 5.2 Settings for the MPLABX environment

This chapter contains mandatory projects settings when using AVIX with the new Microchip development environment MPLABX.

#### 5.2.1 Specify AVIX Include Path

An AVIX based project must have access to the directory containing the AVIX interface files, this location must be added to the MPLABX project settings.

Open the applicable dialog by clicking the left mouse button on the project name and select entry Properties from the drop down menu.

The dialog is shown in Figure 6 where the selections to make in this dialog are highlighted.

The include path entered depends on the location where AVIX is installed. The value shown is based on AVIX being installed in the same directory where the MPLABX project files directory is located.

|               | K Project Properties - test                                |                                                        |                     |       |                                            |

|---------------|------------------------------------------------------------|--------------------------------------------------------|---------------------|-------|--------------------------------------------|

|               | Categories:<br>General<br>Onf: [default]<br>Onf: [default] | Options for xc16-gcc (v1.1<br>Option categories: Prepr |                     | leset | 2: Select<br>Preprocessing<br>and messages |

|               | ······································                     | C include dirs                                         | \_AVIX\Interface    |       |                                            |

|               | ····   Building                                            | Define C macros                                        |                     |       |                                            |

| 1: Select the |                                                            | ANSI-std C support                                     |                     |       | 3: Enter the                               |

| compiler      | vch-as<br>∞ xc16-gcc                                       | Errata                                                 |                     | _ =   | path to the                                |

|               |                                                            | Smart IO forwarding level                              | 1                   | · •   | AVIX interface                             |

|               |                                                            | Smart IO format string                                 | (N/A)               |       | directory                                  |

|               |                                                            | Make warns into errors                                 |                     |       | ,                                          |

|               |                                                            | Additional warnings                                    |                     |       |                                            |

|               |                                                            | Strict ANSI warnings                                   |                     | -     |                                            |

|               |                                                            | Additional options: -fno-p                             | occ-struct-return   |       |                                            |

|               |                                                            | Option Description Gene                                | erated Command Line |       |                                            |

|               |                                                            |                                                        |                     |       |                                            |

|               |                                                            |                                                        |                     |       |                                            |

|               |                                                            |                                                        |                     |       |                                            |

|               | Manage Configurations                                      | ]                                                      |                     |       |                                            |

|               | Manage Configurations                                      |                                                        |                     |       |                                            |

|               |                                                            |                                                        | OK Cancel Apply     | Help  |                                            |

Figure 6: Set AVIX Interface include path for MPLABX

### 5.2.2 Structure based function parameters

The functions offered on the AVIX API use 'C' structures. The C30/XC16 compiler suite allows for structures to be passed by value or by reference. To implement the high level of type safety the AVIX library is built based on passing structures by value. This implies that code using AVIX functions has to use the same mechanism in order to be compatible with the library.

This is accomplished by using compiler flag **-fno-pcc-struct-return**.

Open the applicable dialog by clicking the left mouse button on the project name and select entry *Properties* from the drop down menu.

The dialog is shown in Figure 7 where the selections to make in this dialog are highlighted.

|                        | 🔀 Project Properties - test                                                                                                                             |                                                                                                                                                                                                                        |                  | ×                                          |                                                    |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------|----------------------------------------------------|

|                        | Categories:                                                                                                                                             | Options for xc16-gcc (v1.10) Option categories. Preprocessing and messages Reset                                                                                                                                       |                  | 2: Select<br>Preprocessing<br>and messages |                                                    |

| 1: Select the compiler | <ul> <li>Real ICE</li> <li>Loading</li> <li>Libraries</li> <li>Building</li> <li>XC 16 (Global Options)</li> <li>xc 16-gcc</li> <li>xc 10-dd</li> </ul> | C include dirs<br>Define C macros<br>ANSI-std C support<br>Errata<br>Smart IO forwarding level<br>Smart IO format string<br>Make warns into errors<br>Additional warnings<br>Strict ANSI warnings<br>Additional option | LAVIX \Interface |                                            |                                                    |

|                        | Manage Configurations                                                                                                                                   |                                                                                                                                                                                                                        | Cancel Apply     | -fno-pcc-str                               | nter flag<br>uct-return to the<br>I options field. |

Figure 7: Struct parameter project setting for MPLABX

### 5.2.3 ELF object file type

The AVIX library is distributed in the ELF format. For compatibility the project specific source files must be build according the same binary format. Selecting the ELF binary format is done through through the project settings dialog.

Open the applicable dialog by clicking the left mouse button on the project name and select entry *Properties* from the drop down menu.

The dialog is shown in Figure 8 where the selections to make in this dialog are highlighted

|                                            | X Project Properties - test     Categories:                                                                    | Options for xc16-gcc (v1.10)<br>Option categories: Global option                                                                                | ns Reset          | 2: Select<br>Global options                 |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------|

| 1: Select the<br>compiler gobal<br>options | Real ICE     Loading     Libraries     Buildinn     XC16 (Global Options)     Xc16 us     xc16-gcc     xc16-ld | Output file format Define common macros Generic build Use legacy libc Fast floating-point math Additional options: Option Description Generated | ELF/DWARF (N/A)   | 3: Select the<br>ELF/DWARF<br>binary format |

|                                            | Manage Configurations                                                                                          |                                                                                                                                                 | Cancel Apply Help |                                             |

Figure 8: ELF binary format project settings for MPLABX

# 6 Memory Model and Linking

The content of this chapter is especially relevant when during building the application, the linker generates errors related to unreachable code suggesting the large code model.

PIC24-dsPIC family members are 16 bit controllers. Branch instructions allow code within 32Kb from the branch instruction to be reached. Other instructions are offered in multiple formats. Calling a function for instance can be done using the rcall instruction or the call instruction. Using rcall, the same limitation as with branch instructions exist. Using call, allows any location in memory to be reached.

When compiling, either a small or a large memory model can be used. Using the small model, the compiler will use relative branches and calls with a 32Kb range. Using the large model the compiler uses instructions allowing the entire program memory to be reached. Which model is used depends on the size of the application. The disadvantage of the large model is that the compiler generated code is larger and slower.

AVIX is distributed in the form of a binary library. The AVIX library is build using the small memory model. Doing so, the generated code is smaller and faster. This model is compatible with application code regardless the model used when compiling the application. Based on the selected memory model, the application will contain 'small' or 'large' calls to the AVIX functions.

Functions present in the AVIX library do also use each other and since AVIX is compiled using the small memory model, the different AVIX functions must be no further apart from each other than 32Kb. Here a potential issue exists. The AVIX library contains multiple object files and in principle these individual files can be placed anywhere in program memory. The linker can place AVIX object files such that functions calling each other are out of reach, resulting in a linker error.

A solution for this would be to build the AVIX library using the large model. Since this does generate larger and slower code a different solution for this potential issue is chosen.

All compiler generated code lives in sections which can be given a name. For AVIX code, the section name .\_avix\_code\_ is used. The linker allows all sections with the same name to be grouped. Since the total amount of AVIX code is something like 12Kb, when grouping all AVIX code sections together, all functions are guaranteed to be no further than 32Kb from each other, preventing the potential issue.

To accomplish this, the linker description file for the used controller must be added to the project. For every controller, such a linker description file exists (.gld file). Suggested is to copy the applicable file to the project directory and make the suggested changes to this file.

All linker description files contain a SECTION statement where directives can be added to control the application memory layout. To group all AVIX code together, the text shown in brown in Code sample 1 must be added to the linker description file SECTION statement.

Product Version 5.0.0

# 7 Configuring AVIX

AVIX is highly configurable. All configuration settings are made by manipulating the content of file AVIXSystemSettings.h. Details are provided in §7.1.

Besides the configuration settings, AVIXSystemSettings.h contains include statements for the global header files of the different controller families supported by this port. Based on the selected controller (see §5.1), the correct include file is automatically used. The applicable include files are shown in Table 2.

| Controller family | Controller family include file |

|-------------------|--------------------------------|

| PIC24F            | p24Fxxxx.h                     |

| PIC24E            | p24Exxxx.h                     |

| PIC24H            | p24Hxxxx.h                     |

| dsPIC30F          | p30Fxxxx.h                     |

| dsPIC33E          | p33Exxxx.h                     |

| dsPIC33F          | p33Fxxxx.h                     |

#### Table 2: Controller Family Header Files

When including one of the AVIX header files (preferably AVIX.h, see §4.1 for more details), AVIXSystemSettings.h is automatically included and as a result the applicable controller family include file is included. Therefore all definitions of the applicable controller family include file are available to the application and there is no need for the application to explicitly include one of these files.

### 7.1 Configuration Parameters

Configuring AVIX is done by manually editing the content of file AVIXSystemSettings.h. The following settings are present<sup>5</sup>:

#### avix\_DEVICE\_CLOCKhz

The controller's core speed and device speed are to be set by the application. Based on these settings, the speed at which the AVIX used hardware timer is running must be configured through this parameter. This parameter specifies the frequency in Hertz used for clocking the hardware timer configured through configuration parameter avix\_SYSTMR.

From this value the applicable timing related settings used by AVIX are derived. An incorrect value for this parameter will lead to imprecise timing of timers and round robin time slice duration.

The value specified here is related to configuration parameter avix\_TIMER\_CLK\_SECONDARY:

- When using an internal clock for the hardware timer, the value for avix\_DEVICE\_CLOCKhz must equal the instruction frequency the controller core is operating at.

- When using an external clock for the hardware timer, the value for avix\_DEVICE\_CLOCKhz must equal the frequency of this external clock which most of the time is 32,768Hz.

<sup>&</sup>lt;sup>5</sup> Depending on the type of distribution, some configuration parameters are fixed. The applicable parameters are clearly marked in AVIXSystemSettings.h. Details are found in Table 3.

#### avix\_TIMER\_CLK\_SECONDARY

Specify whether the hardware timer is clocked from an internal or an external clock.

- 0: Hardware timer is clocked from internal processor instruction clock.

- 1: Hardware timer is clocked from external clock.

When using AVIX power management, certain power reduction modes require the system timer to be clocked from an external clock in order for the AVIX timing functions to continue operating. For more details see §11.

#### avix\_ROUND\_ROBIN\_CYCLEus

The time in microseconds a thread is allowed to run before another thread at the same priority will be activated. A typical value for this parameter is 10,000 (10 ms).

The value for this parameter must be at least five (5) times the value you choose for avix SYS CLOCK TICKus.

Optionally this parameter can be given the value 0 effectively disabling round robin scheduling. When doing so and using multiple threads at the same priority, such a thread must explicitly call avixThread\_Relinquish to allow the next thread at the same priority to be activated.

#### avix\_SYS\_CLOCK\_TICKus

Hardware timer period in microseconds. This parameter specifies the period of the AVIX system tick.

This value must be at least five (5) times lower than the value chosen for avix ROUND ROBIN CYCLEus.

This parameter specifies the accuracy available for all timing related functionality. A typical value is between  $100\mu$ s and  $1000\mu$ s where the lower the number, the more accurate application timing can be obtained.

When using AVIX power management, to place the controller in SLEEP mode, the timer period configured through this parameter may need to be substantially longer than the times mentioned above. For more details see §11.

Based on the resolution of the clock used for the hardware timer, the actual period may differ from the period configured through this parameter. The actual hardware timer period is available through symbol AVIX\_SYS\_CLOCK\_ACTUAL\_PERIOD. When the application needs the hardware timer period, make sure to use this symbol i.s.o. avix SYS CLOCK TICKus.

#### avix\_MEM\_POOL\_COUNT

Maximum number of memory pools that can be created by the application.

For every memory pool that can be created, two bytes are reserved. As such the value of this parameter has a marginal effect on RAM usage.

#### avix\_MSG\_POOL\_NR\_MESSAGES

Number of messages in the message pool available to the application.

When this parameter is given a value of zero (0), no message pool is created.

Based on this parameter, during initialization, a memory pool is created from which messages are allocated. Make sure to configure this parameter to the lowest possible value for the lowest memory consumption.

#### avix\_MSG\_BODY\_NR\_BYTES

The message mechanism is based on messages with a fixed size of the message data section. This parameter specifies the size in bytes of a message data section.

A value of zero (0) is allowed meaning no data can be placed in messages and only the message type field can be used to differentiate between messages.

#### avix\_SYSTEM\_STACK\_SIZE

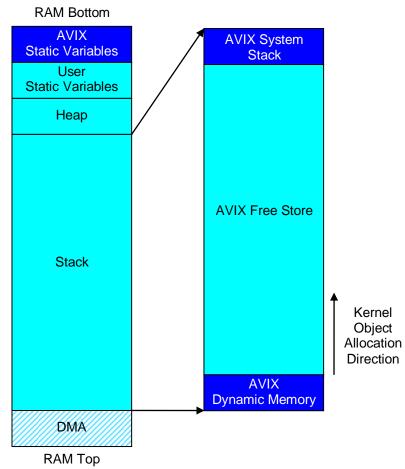

AVIX implements a system stack for use by Interrupt Service Routines. Using this system stack for interrupts means that stacks of individual threads can be smaller. This configuration parameter specifies the size in bytes allocated for the system stack. The configured size is scaled such that the stack size adheres to the stack alignment requirements for the applied microcontroller.

Besides ISR's, this system stack is used by some AVIX internal functions.

A typical value for this parameter is 200 to 400 bytes.

#### avix\_MAX\_PRIORITY

The maximum thread priority an application can use. A thread can be given any priority from 1 up to and including avix\_MAX\_PRIORITY.

The maximum value for this configuration parameter is 254.

Adapt the value of this parameter to the actual priorities used by the application. A lower value for this parameter has a positive effect on both memory usage and performance.

#### avix\_TRACING

Control Thread Activation Tracing. This parameter may have one of the following values:

0: Tracing **disabled**, trace code **executed**. On every context switch trace code is executed but no trace port assigned to any thread will be asserted. Instead of this a dummy memory location is asserted. This allows disabling tracing retaining the same performance as using value 1.

1: Tracing **enabled**, trace code **executed**. On every context switch, trace code is executed. For threads having a trace port assigned this port will be asserted. For threads not having a trace port assigned, a dummy memory location is asserted. This allows enabling tracing retaining the same performance as using value 0.

2: Tracing **disabled**, trace code **not executed**. Using this value, AVIX will not execute the trace code leading to optimal performance. Using this value AVIX executes a different instruction sequence than with either value 0 or 1.

Values 0 and 1 exist to allow having a build with or without tracing having the same performance. These modes are intended to be used during development where switching between these mode enable/disable tracing without influencing performance. This forms the basis of the non-intrusiveness of tracing. Regardless if value 0 or 1 is used, the exact same instruction sequence will be executed.

Regardless the value of this configuration parameter, trace ports can be assigned to a thread using function avixThread\_SetTracePort. The value of this configuration parameter only influences how these ports are used by AVIX.

#### avix\_EXTENDED\_MEMORY

Number of bytes in the Extended Data Space (EDS) to allocate AVIX memory pools in.

The value of this parameter must be in the range 0...65,532. More details can be found in §10.

Note when using memory pools allocated in EDS RAM from multiple threads, this implies multithreaded usage of the DSRPAG and DSWPAG registers. In this case these registers must be saved as part of the thread context and as a consequence flag <code>avix\_MULTI\_THREAD\_PSV</code> must be set.

#### avix\_MULTI\_THREAD\_PSV

Most controllers belonging to the PIC24-dsPIC families allow a FLASH page to be mapped to the upper data area (address 0x8000 to 0xffff) and contain a PSVPAG register to facilitate this. Some members of the PIC24F family and the PIC24E and dsPIC33E families support EDS RAM and allow either a FLASH page or a RAM page to be mapped to this upper data area. These controllers do not have a PSVPAG register but a pair of registers named DSRPAG and DSWPAG instead. AVIX is compatible with both types of controllers. Although the name of the configuration flag contains the term PSV, in practice this flag controls either PSVPAG or the DSRPAG/DSWPAG pair. When a controller is equipped with DSRPAG/DSWPAG, these registers are said to control EDS (Extended Data Space) pages.

Control usage of multiple PSV/EDS pages from multiple threads.

0: PSV/EDS usage from multiple threads is not allowed.

1: PSV/EDS usage from multiple threads is allowed

When using value 1, the PSVPAG register or the DSRPAG/DSWPAG register pair is saved as part of the thread context. As a consequence, two or four more bytes of stack space are used per thread and thread context switch time will be a few instructions longer. For this reason, when not using PSV/EDS pages from multiple threads it is advised to set this parameter to value 0.

For more details see §9.1.

Note when using EDS RAM based memory pools from multiple threads, this implies usage of the DSRPAG and DSWPAG registers and flag avix MULTI THREAD PSV must be set.

#### avix\_MULTI\_THREAD\_TBLPAG

Control usage of the table access instructions from multiple threads.

0: TBLPAG usage from multiple threads is not allowed.

1: TBLPAG usage from multiple threads is allowed

When using value 1, the TBLPAG register is saved as part of the thread context. As a consequence, two more bytes of stack space are used per thread and thread context switch time will be a few instructions longer. For this reason, when not using table page access from multiple threads it is advised to set this parameter to value 0.

For more details see §9.2.

#### avix\_DSP\_ENABLED

Control usage of DSP functionality.

- 0: DSP functionality may not be used

- 1: DSP functionality may be used by a single thread

When using value 1, an additional register is saved as part of the thread context. As a consequence, two more bytes stack space are used per thread and thread context switch time will be a few instructions longer. For this reason, when not using DSP functionality it is advised to set this parameter to value 0.

This parameter only has effect when using AVIX with a member of either the dsPIC30F, the dsPIC33E or the dsPIC33F family. When using controllers of the PIC24F, PIC24E or PIC24H families, this parameter is ignored.

For more details see §9.3.

#### avix\_SWI avix\_SWI\_IRQ\_REG avix\_SWI\_IRQ\_CTRREG avix\_SWI\_IRQ\_LVLREG

Specify the internal interrupt and related registers used by AVIX.

Any available interrupt can be chosen as long as it is not used by the application.

For more details, see §7.2

#### avix\_SYSTMR avix\_SYSTMR\_IRQ\_REG avix\_SYSTMR\_IRQ\_CTRREG avix\_SYSTMR\_IRQ\_LVLREG

Specify the hardware timer and the related interrupt registers used by AVIX.

Any available timer can be chosen as long as it is not needed by the application.

For more details, see §7.2

#### Table 3: AVIX Configuration Parameters

### 7.2 Interrupt and Timer

Special care must be taken when configuring the interrupt and hardware timer used by AVIX.

For the interrupt this concerns the following configuration parameters:

- avix\_SWI: The name of the selected interrupt.

- avix\_SWI\_IRQ\_REG: The interrupt register belonging to the selected interrupt.

- avix\_SWI\_IRQ\_CTRREG: The interrupt control register belonging to the selected interrupt.

- avix\_SWI\_LVLREG: The interrupt priority register belonging to the selected interrupt.

The hardware timer is configured by specifying its number. Internally the hardware timer is used on interrupt basis so for the hardware timer also the applicable interrupt registers must be configured. The following configuration parameters are applicable:

Product Version 5.0.0 20

- avix\_SYSTMR: The number of the selected hardware timer.

- avix SYSTMR IRQ REG: The interrupt register belonging to the selected timer.

- avix\_SYSTMR\_IRQ\_CTRREG: The interrupt control register belonging to the selected timer.

- avix\_SYSTMR\_LVLREG: The interrupt priority register belonging to the selected timer.

The PIC24-dsPIC interrupt structure is based on using three different registers for every interrupt:

- Interrupt register (IF): Register containing the actual interrupt flag.

- Interrupt control register (IE): Register containing a flag to enable or disable the related interrupt.

- Interrupt priority register (IP): Register containing a three bit value specifying the priority of the interrupt.

When selecting an interrupt for use by AVIX, first select the name of the desired interrupt and assign this name to configuration parameter avix\_SWI. Interrupt names can be found in the reference manual of the controller being used.

For example, using DMA2 as the interrupt this is done by the following entry in AVIXSystemSettings.h:

#define avix SWI

Next the three related configuration parameters must be given a value such that they represent the interrupt register name, the interrupt control register name and the interrupt priority register name

DMA2

This information can be found in the reference manual of the selected controller. Figure 9 shows this information for the dsPIC33FJ256GP710. Based on the selection of DMA2 as the interrupt to be used by AVIX, locate DMA2IF, DMA2IE and DMA2IP in the table which are the bit-fields belonging to the selected interrupts. In the table these values are marked red.

The registers to use for the configuration parameters are found in the leftmost column of this table in the row where the bit field is found. These register names are used for the three additional configuration parameters related to the selected interrupt. For DMA2IF, the register is IFS1, for DMA2IE the register is IEC1 and for DMA2IP, the register is IPC6.

This results in the following entries in AVIXSystemSettings.h:

#define avix\_SWI\_IRQ\_REG IFS1

#define avix\_SWI\_IRQ\_CTRREG IEC1

#define avix\_SWI\_IRQ\_LVLREG IPC6

for the selected interrupt, DMA2 in this example.

Specifying these four entries conclude configuring AVIX to use DMA2 as its internal interrupt.

The selected interrupt is for exclusive use by AVIX and may not be used by the application. The device belonging to the selected interrupt is not used by AVIX and thus available to the application. In this case however it is important to guarantee the device itself does not generate interrupts. Failure to do so leads to an instable application.

### AVIX for PIC24-dsPIC Port Guide

| TABLE       | 3-3:        | INTE              | RRUPT    | CONT       | ROLLER  | REGIST   | ER M        | AP            |                 |             |         |             |              |                      |             |            |         |               |

|-------------|-------------|-------------------|----------|------------|---------|----------|-------------|---------------|-----------------|-------------|---------|-------------|--------------|----------------------|-------------|------------|---------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15            | Bit 14   | Bit 13     | Bit 12  | Bit 11   | Bit 10      | Bit 9         | Bit 8           | Bit 7       | Bit 6   | Bit 5       | Bit 4        | Bit 3                | Bit 2       | Bit 1      | Bit 0   | All<br>Resets |

| INTCON1     | 0800        | NSTDIS            | OVAERR   | OVBERR     | COVAERR | COVBERR  | OVATE       | OVBTE         | COVTE           | SFTACERR    | DIV0ERR | DMACERR     | MATHERR      | ADDRERR              | STKERR      | OSCFAIL    |         | 0000          |

| INTCON2     | 0082        | ALTIVT            | DISI     | -          | -       |          |             |               | 100 <u></u> 000 |             |         |             | INT4EP       | INT3EP               | INT2EP      | INT1EP     | INT0EP  | 0000          |

| IFS0        | 0084        |                   | DMA1IF   | AD1IF      | U1TXIF  | U1RXIF   | SPI1IF      | SPI1EIF       | T3IF            | T2IF        | OC2IF   | IC2IF       | DMA0IF       | T1IF                 | OC1IF       | IC1IF      | INTOIF  | 0000          |

| IFS1        | 0086        | U2TXIF            | U2RXIF   | INT2IF     | T5IF    | T4IF     | OC4IF       | OC3IF         | DMA2IF          | IC8IF       | IC7IF   | AD2IF       | INT1IF       | CNIF                 |             | MI2C1IF    | SI2C1IF | 0000          |

| IFS2        | 8800        | T6IF              | DMA4IF   | -          | OC8IF   | OC7IF    | OC6IF       | OC5IF         | IC6IF           | IC5IF       | IC4IF   | IC3IF       | DMA3IF       | C1IF                 | C1RXIF      | SPI2IF     | SPI2EIF | 0000          |

| IFS3        | 008A        |                   |          | DMA5IF     | DCIIF   | DCIEIF   |             |               | C2IF            | C2RXIF      | INT4IF  | INT3IF      | T9IF         | T8IF                 | MI2C2IF     | SI2C2IF    | T7IF    | 0000          |

| IFS4        | 008C        |                   | —        |            | -       | -        |             |               |                 | C2TXIF      | C1TXIF  | DMA7IF      | DMA6IF       | _                    | U2EIF       | U1EIF      | _       | 0000          |

| IEC0        | 0094        |                   | DMA1IE   | AD1IE      | U1TXIE  | U1RXIE   | SPI1IE      | SPI1EIE       | T3IE            | T2IE        | OC2IE   | IC2IE       | DMA0IE       | T1IE                 | OC1IE       | IC1IE      | INTOIE  | 0000          |

| IEC1        | 0096        | U2TXIE            | U2RXIE   | INT2IE     | T5IE    | T4IE     | OC4IE       | OC3IE         | DMA2IE          | IC8IE       | IC7IE   | AD2IE       | INT1IE       | CNIE                 | —           | MI2C1IE    | SI2C1IE | 0000          |

| IEC2        | 0098        | T6IE              | DMA4IE   |            | OC8IE   | OC7IE    | OC6IE       | OC5IE         | IC6IE           | IC5IE       | IC4IE   | IC3IE       | DMA3IE       | C1IE                 | C1RXIE      | SPI2IE     | SPI2EIE | 0000          |

| IEC3        | 009A        |                   |          | DMA5IE     | DCIIE   | DCIEIE   |             |               | C2IE            | C2RXIE      | INT4IE  | INT3IE      | T9IE         | T8IE                 | MI2C2IE     | SI2C2IE    | T7IE    | 0000          |

| IEC4        | 009C        | 1111 <u></u> 1111 |          |            |         |          | <u></u>     |               | <u></u>         | C2TXIE      | C1TXIE  | DMA7IE      | DMA6IE       | <u>-</u>             | U2EIE       | U1EIE      |         | 0000          |

| IPC0        | 00A4        |                   |          | T1IP<2:0>  | >       |          | (           | )<br>C1IP<2:0 | )>              |             |         | IC1IP<2:0>  |              |                      | II          | NT0IP<2:0> |         | 4444          |

| IPC1        | 00A6        |                   |          | T2IP<2:0>  | >       |          | 0           | OC2IP<2:0     | )>              |             |         | IC2IP<2:0>  |              |                      | DMA0IP<2:0> |            | 4444    |               |

| IPC2        | 00A8        |                   | ι        | J1RXIP<2:  | 0>      |          | Ś           | SPI1IP<2:0    | )>              |             |         | SPI1EIP<2:0 | Þ            |                      |             | T3IP<2:0>  |         | 4444          |

| IPC3        | 00AA        |                   |          |            |         |          | D           | MA1IP<2       | :0>             |             |         | AD1IP<2:0>  | >            |                      | U           | 1TXIP<2:0  | >       | 4444          |

| IPC4        | 00AC        |                   |          | CNIP<2:0   | >       |          |             |               |                 |             |         | MI2C1IP<2:0 | )>           | 100 <del>2</del> 003 | S           | I2C1IP<2:0 | >       | 4444          |

| IPC5        | 00AE        |                   |          | IC8IP<2:0  | >       |          |             | IC7IP<2:0     | >               |             |         | AD2IP<2:0>  | >            | 100 <u>-</u> 000     | I           | NT1IP<2:0> |         | 4444          |

| IPC6        | 00B0        |                   |          | T4IP<2:0>  | >       |          | (           | OC4IP<2:0     | )>              |             |         | OC3IP<2:0:  | >            | 100 <del>-</del> 100 | D           | MA2IP<2:0  | >       | 4444          |

| IPC7        | 00B2        |                   | l        | U2TXIP<2:  | 0>      |          | U           | J2RXIP<2:     | 0>              |             |         | INT2IP<2:0  | >            |                      |             | T5IP<2:0>  |         | 4444          |

| IPC8        | 00B4        |                   |          | C1IP<2:0   | >       |          | C1RXIP<2:0> |               |                 | SPI2IP<2:0> |         | <u>-</u>    | SPI2EIP<2:0> |                      | >           | 4444       |         |               |

| IPC9        | 00B6        |                   |          | IC5IP<2:0  | >       |          | IC4IP<2:0>  |               |                 | IC3IP<2:0>  |         | _           | DMA3IP<2:0>  |                      | >           | 4444       |         |               |

| IPC10       | 00B8        |                   |          | OC7IP<2:0  | )>      |          | OC6IP<2:0>  |               |                 | OC5IP<2:0>  |         | _           | IC6IP<2:0>   |                      |             | 4444       |         |               |

| IPC11       | 00BA        |                   |          | T6IP<2:0>  | >       |          | D           | MA4IP<2       | :0>             |             |         |             | —            |                      | ç           | C8IP<2:0>  |         | 4444          |

| IPC12       | 00BC        |                   |          | T8IP<2:0>  | >       |          | M           | 12C2IP<2      | :0>             |             |         | SI2C2IP<2:0 | >            |                      |             | T7IP<2:0>  |         | 4444          |

| IPC13       | 00BE        | 101 <u></u> 111   | (        | C2RXIP<2:  | 0>      | <u> </u> | 1           | NT4IP<2:0     | )>              |             |         | INT3IP<2:0  | >            | <u></u>              |             | T9IP<2:0>  |         | 4444          |

| IPC14       | 00C0        |                   | 1        | DCIEIP<2:0 | )>      |          |             |               |                 |             |         |             |              |                      |             | C2IP<2:0>  |         | 4444          |

| IPC15       | 00C2        |                   |          |            |         | <u> </u> |             |               |                 |             |         | DMA5IP<2:0  | >            |                      | (           | OCIIP<2:0> |         | 4444          |

| IPC16       | 00C4        |                   | <u> </u> | _          | -       |          |             | U2EIP<2:0     | )>              |             |         | U1EIP<2:0>  | >            |                      |             |            |         | 4444          |

| IPC17       | 00C6        |                   | (        | C2TXIP<2:  | D>      | <u> </u> | 0           | C1TXIP<2:     | 0>              |             |         | DMA7IP<2:0  | >            |                      | D           | MA6IP<2:0  | >       | 4444          |

| INTTREG     | 00E0        |                   |          |            |         |          | ILR<        | 3:0>          |                 | -           |         |             | VE           | CNUM<6:0>            |             |            |         | 0000          |

Figure 9: AVIX Sample Interrupt Controller Register Map

The table shown in Figure 9 contains the registers for the dsPIC33FJ256GP710. Make sure to use the table belonging to the controller you are using since the applicable registers differ per controller type.

The same process must be followed for the hardware timer required by AVIX. First you choose the number of the desired timer and make this number the value of <code>#define avix\_SYSTMR</code>. *Note that this is just a number without a T*. When using timer 7, the configuration parameter looks like:

#define avix SYSTMR

For every timer, there is a TxIF, TxIE and TxIP register, respectively containing the interrupt register, the interrupt control register and the interrupt priority register for that timer. Since in this example timer 7 is used, locate T7IF, T7IE and T7IP in the Interrupt Controller Register table.

7

In the table above these entries are marked blue. Next the corresponding registers found in the leftmost column are entered in AVIXSystemSettings.h. This leads to:

| #define | avix SYSTMR | IRQ REG    | IFS3  |

|---------|-------------|------------|-------|

| #define | avix SYSTMR | IRQ CTRREG | IEC3  |

| #define | avix_SYSTMR | IRQ_LVLREG | IPC12 |

Correctly specifying these values is essential for AVIX to operate correctly. Make sure after editing the selected values in AVIXSystemSettings.h to check them once more.

### 7.3 Distributions

AVIX is available in three different retail distributions. These distributions differ in user configurable parameters and the number of kernel resources (thread, mutex, etc.) that can be used. Every distribution comes with an AVIXSystemsSettings.h file, containing all configuration parameters mentioned in §7. Based on the type of distribution, a configuration parameter is either fixed (as determined by the build process of that distribution) or user changeable. Fixed configuration parameters are clearly denoted as such in AVIXSystemsSettings.h.

Table 4 shows a summary of the fixed configuration parameters and their values together with the maximum number of kernel objects that can be used for each type of distribution.

| Distribution                       | BASIC        | STANDARD     | EXTENDED         |  |  |  |  |

|------------------------------------|--------------|--------------|------------------|--|--|--|--|

| Controller Type                    |              | Configurable |                  |  |  |  |  |

| Device Speed                       | Configurable |              |                  |  |  |  |  |

| Round Robin Cycle Time             |              | Configurable |                  |  |  |  |  |

| System Clock Period                |              | Configurable |                  |  |  |  |  |

| Internal Interrupt                 |              | Configurable |                  |  |  |  |  |

| Hardware Timer                     |              | Configurable |                  |  |  |  |  |

| System Stack size                  | 200          | 300          | Configurable     |  |  |  |  |

| Maximum Priority                   | 8            | 16           | Configurable     |  |  |  |  |

| Message Body Size                  | 4            | Configurable |                  |  |  |  |  |

| Nr. Messages in Message Pool       | 10           | Configurable |                  |  |  |  |  |

| Maximum number of Memory Pools     | 2            | 4            | Configurable     |  |  |  |  |

|                                    |              |              |                  |  |  |  |  |

| Maximum number of Threads          | 8            | 16           | Memory dependent |  |  |  |  |

| Maximum number of Mutexes          | 4            | 8            | Memory dependent |  |  |  |  |

| Maximum number of Semaphores       | 4            | 8            | Memory dependent |  |  |  |  |

| Maximum number of Event Groups     | 4            | 8            | Memory dependent |  |  |  |  |

| Maximum number of Pipes            | 4            | 8            | Memory dependent |  |  |  |  |

| Maximum number of Timers           | 4            | 8            | Memory dependent |  |  |  |  |

| Maximum number of Exchange Objects | 4            | 8            | Memory dependent |  |  |  |  |

Fixed configuration parameter. Value present in AVIXSystemSettings.h for reference purposes. Changing has no effect. Fixed value in Distribution Library code

Fixed value in Distribution Library code

#### Table 4: AVIX Distribution Capabilities

The retail version of AVIX is distributed as a binary library. This library is controller neutral and can be used with any controller of the families targeted by AVIX.

# 8 Stack usage and Interrupt Service Routines

Controllers belonging to the PIC24F, PIC24E, PIC24H, dsPIC30F, dsPIC33E and dsPIC33F families do not implement a hardware system stack for use by Interrupt Service Routines (ISR's).

To reduce memory usage, AVIX does implement a software system stack

ISR's can be declared using the standard compiler mechanism. Doing so however, the system stack is not used and interrupts use the stack of the then active thread.

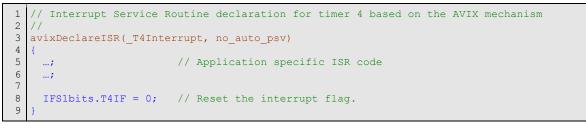

An example of a basic ISR declaration is shown in Code sample 2.

#### Code sample 2: How to declare an ISR using the compiler syntax

Alternatively ISR's can be declared using AVIX provided macros. ISR's using these macros make minimal use of the stack of the active thread and will mainly use the software system stack.

Using the software system stack for ISR's leads to a significant reduction of RAM usage, at the cost of five additional instruction cycles consumed by the ISR.

ISR's based on the regular compiler mechanism and ISR's based on the AVIX provided macros may be used together. So for every individual ISR a choice can be made whether reduction of RAM usage or ultimate performance is the most important.

The macros to declare an ISR using the AVIX system stack are shown below.

avixDeclareISR(isrName, psvUsage)