Analog Dialogue

## In This Issue

- **2** Editors' Notes; New Product Introductions

- **3** Detecting Human Falls with a 3-Axis Digital Accelerometer

- **10** Measuring Noise of Low-Fixed-Gain Differential Amplifiers

- **11** The Basics of Video Decoders in Supervision and Inspection

- 14 How to Apply Low-Dropout Regulators Successfully

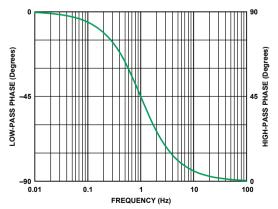

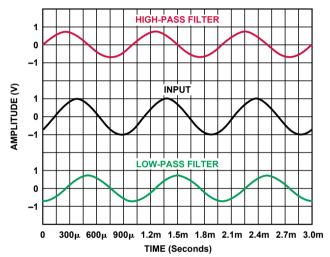

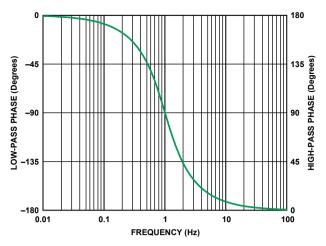

- **18** Phase Response in Active Filters, Part 2: Low-Pass and High-Pass Responses

- **22** Difference Amplifier Forms Heart of Precision Current Source

www.analog.com/analogdialogue

## **Editors' Notes**

#### IN THIS ISSUE

#### **Detecting Human Falls with a 3-Axis Digital Accelerometer**

Elderly individuals can suffer accidental falls due to weakness or dizziness. The initial injury can be further aggravated if treatment is not obtained within a short time. MEMS-based fall detectors can sense changes in body position by tracking acceleration, determine when an individual is falling, and issue an alert for assistance. This article describes the use of an ADXL345 three-axis digital accelerometer as a fall detector. Page 3.

#### **Measuring Noise of Low-Fixed-Gain Differential Amplifiers**

Measuring noise of low-gain differential amplifiers presents a challenge, as their integrated feedback and gain resistors preclude high-gain configurations, and a differential-tosingle-ended conversion is needed to match the spectrum analyzer. A second amplifier stage can provide gain and the differential-to-SE conversion, neatly solving both of these problems. Page 10.

#### The Basics of Video Decoders in Supervision and Inspection

Video cameras—which range from inexpensive, low-definition black-and-white closed-circuit television systems to stateof-the-art high-definition digital-video systems—are found in diverse applications including product inspection, traffic monitoring, and real-time face recognition. Dropping unneeded data and passing only the essential parts of the picture can simplify the video system—saving memory and computational cycles. Page 11.

#### How to Apply Low-Dropout Regulators Successfully

A low-dropout regulator (LDO) is capable of maintaining a specified output voltage over a wide range of load current and input voltage, down to a very small difference between input and output voltages. This difference, known as the dropout voltage or headroom requirement, can be as low as 80 mV at 2 A. Page 14.

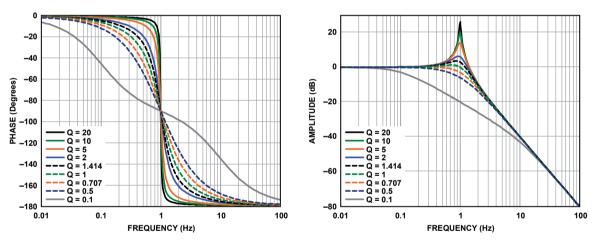

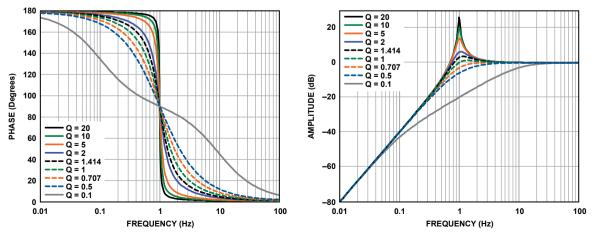

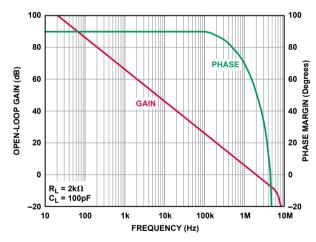

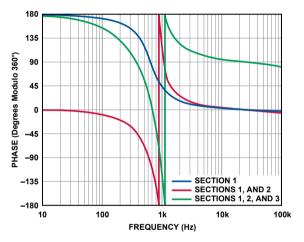

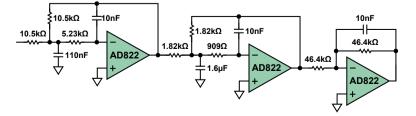

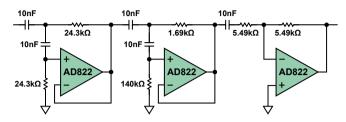

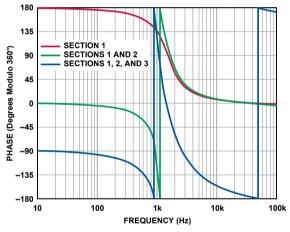

## Phase Response in Active Filters, Part 2: Low-Pass and High-Pass Responses

The transfer function of an active filter can be viewed as the cascaded response of the filter transfer function and an amplifier transfer function. This article examines the phase shift of the filter transfer function itself. While filters are designed primarily for their amplitude response, the phase response can be important in applications such as time delay simulation, cascaded filter stages, and especially processcontrol loops. Page 18.

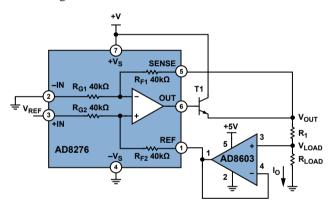

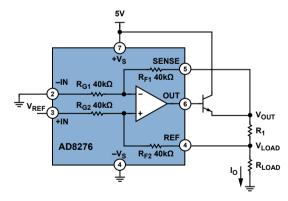

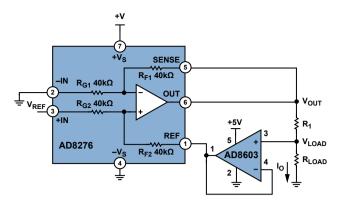

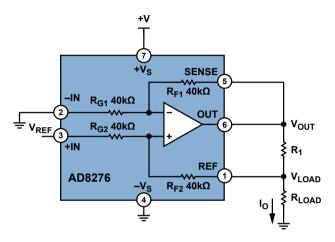

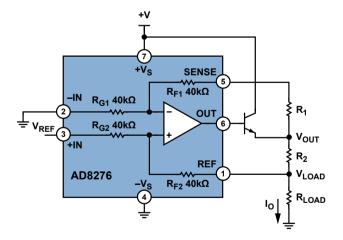

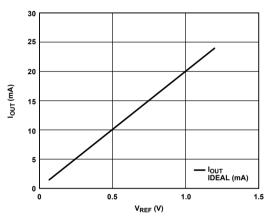

#### **Difference Amplifier Forms Heart of Precision Current Source**

Precision current sources are used to provide excitation for RTDs in process-control systems; to measure unknown elements in digital multimeters; and to drive 4-mA to 20-mA current loops, which are widely used to transmit information over long distances. This article shows how a difference amplifier can be used to implement a precision current source. Page 22.

Dan Sheingold [dan.sheingold@analog.com]

Scott Wayne [scott.wayne@analog.com]

#### **PRODUCT INTRODUCTIONS: VOLUME 43, NUMBER 3**

Data sheets for all ADI products can be found by entering the part number in the search box at www.analog.com.

#### July

| Accelerometer, digital, 3-axis, $\pm 2-g/\pm 4-g/\pm 8-g/\pm 16-g$ ADXL345 |

|----------------------------------------------------------------------------|

| Amplifier, instrumentation, rail-to-rail output AD8227                     |

| Driver, flash LED, dual, high power ADP1655                                |

| Driver, line, quad LVDS ADN4665                                            |

| Drivers, MOSFET, dual, 4-A, high-speed ADP3624/ADP3634                     |

| Isolators, digital, 4-channel, 500-mW dc-to-dc ADuM640x                    |

| Supervisor, voltage, 4-channel, OV/UV ADM2914                              |

| Supervisor, voltage, 4-channel, ±supplies ADM6339                          |

|                                                                            |

#### August

| 24-011 MDC3 ADuC/000/                 |         |

|---------------------------------------|---------|

| Mixer, balanced, 1200-MHz to 2500-MHz | ADL5355 |

| Receiver, line, quad LVDS             | ADN4666 |

#### September

| Accelerometers, 3-axis, low-power, low-profile AD | XL32x |

|---------------------------------------------------|-------|

| ADC, sigma-delta, 4-channel, 24-bit, 4.8-kHz A    | D7193 |

| ADCs, pipelined, dual,                            |       |

| 10-/12-/14-bit, 80 MSPS AD9204                                                                                             | 1/A D0231/A D0251 |

|----------------------------------------------------------------------------------------------------------------------------|-------------------|

| Amplifier, difference, dual, unity-gain                                                                                    |                   |

| Amplifier, difference, gain of ½ or 2                                                                                      |                   |

| Amplifier, operational, dual, micropower                                                                                   |                   |

| Amplifier, operational, dual, rail-to-rail                                                                                 |                   |

| Amplifier, operational, dual, rail-to-rail                                                                                 |                   |

| Amplifier, operational, JFET-input                                                                                         |                   |

| Amplifier, operational, quad, JFET-input                                                                                   |                   |

| Amplifier, operational, quad, rail-to-rail                                                                                 |                   |

| Amplifier, operational, zero crossover distortion                                                                          |                   |

| Buffer, clock fanout, 2-input, 8-output                                                                                    |                   |

| Buffer, clock fanout, 2-input, 10-output                                                                                   | ADCLK950          |

| Converter, dc-to-dc, step-down, 3-A                                                                                        | ADP2118           |

| Converter, dc-to-dc, step-down, dual, 2-A/4-A                                                                              | ADP2114           |

| DAC, voltage-output, quad, 16-bit                                                                                          |                   |

| DACs, voltage-output, single/quad, 12-bit                                                                                  |                   |

| Delay Line, video, triple skew-compensating                                                                                |                   |

| Demodulator, quadrature, 400-MHz to 6-GHz                                                                                  |                   |

| Digitizer, video/graphics, 12-bit, 170-MHz                                                                                 |                   |

| Driver, laser-diode, dual-loop, 50-Mbps to 3.3-Gbp                                                                         | os ADN2872        |

| Drivers, current/voltage, programmable A                                                                                   |                   |

| Drivers, MOSFET, dual 4-A AI                                                                                               |                   |

| Front Ends, analog, 8-channel                                                                                              | AD9276/AD9277     |

| Generator, clock, 2-output, PCI Express <sup>®</sup>                                                                       | AD95/3            |

| Generator, clock, 7-output, Fibre Channel/Etherne                                                                          |                   |

| Generator/Synchronizer, network clock, 4-input                                                                             |                   |

| Isolator, digital, bidirectional, USB                                                                                      |                   |

| Mixer, balanced, 500-MHz to 1700-MHz                                                                                       |                   |

| <b>Modulator</b> , sigma-delta, dual, 640 MSPS<br><b>Multiplexer</b> , CMOS, 8-channel, $4.5-\Omega$                       | ADC1609           |

|                                                                                                                            |                   |

| <b>Multiplexer</b> , CMOS, differential, 4-channel, $4.5-\Omega$<br><b>Multiplexer/Demultiplexer</b> , 6.5-Gbps, dual, 2:1 |                   |

| Receiver, HDMI, quad, Deep Color                                                                                           |                   |

|                                                                                                                            |                   |

|                                                                                                                            | ALIG-1634         |

| Switch, CMOS, quad SPDT, $4.5-\Omega$                                                                                      |                   |

| Switch, CMOS, quad SPD1, $4.5-\Omega$<br>Switch, CMOS, triple SPDT, $4.5-\Omega$<br>Transmitter, HDMI/DVI, CEC             | ADG1633           |

### Analog Dialogue

Analog Dialogue, www.analog.com/analogdialogue, the technical magazine of Analog Devices, discusses products, applications, technology, and techniques for analog, digital, and mixed-signal processing. Published continuously for 43 years—starting in 1967—it is currently available in two versions. Monthly editions offer technical articles; timely information including recent application notes, new-product briefs, pre-release products, webinars and tutorials, and published articles; and potpourri, a universe of links to important and relevant information on the Analog Devices website, www.analog.com. Printable quarterly issues feature collections of monthly articles. For history buffs, the *Analog Dialogue* archive includes all regular editions, starting with Volume 1, Number 1 (1967), and three special anniversary issues. If you wish to subscribe, please go to www.analog.com/analogdialogue/subscribe.html. Your comments are always welcome; please send messages to dialogue. editor@analog.com or to *Dan Sheingold*, Editor [dan.sheingold@analog.com] or *Scott Wayne*, Publisher and Managing Editor [scott.wayne@analog.com]

# **Detecting Human Falls with a 3-Axis Digital Accelerometer**

By Ning Jia

#### Foreword

For a human, experiencing a fall unobserved can be doubly dangerous. The obvious possibility of initial injury may be further aggravated by the possible consequences if treatment is not obtained within a short time. For example, many elderly individuals can suffer accidental falls due to weakness or dizziness—or, in general, their diminished self-care and self-protective ability. Since they tend to be fragile, these accidents may possibly have serious consequences if aid is not given in time. Statistics show that the majority of serious consequences are not the direct result of falling, but rather are due to a delay in assistance and treatment. Post-fall consequences can be greatly reduced if relief personnel can be alerted in time.

Besides senior citizens, there are many other conditions and activities for which an immediate alert to a possible fall, especially from substantial height, would be quite helpful—for example mountaineers, construction workers, window washers, painters, and roofers.

In light of this need to warn of falls, the development of devices for detection and prediction of all types of falls has become a hot topic. In recent years, technological advances in *microelectromechanical-system* (MEMS) acceleration sensors have made it possible to design fall detectors based on a 3-axis *integrated MEMS* (*i*MEMS<sup>®</sup>) accelerometer. The technique is based on the principle of detecting changes in motion and body position of an individual, wearing a sensor, by tracking acceleration changes in three orthogonal directions. The data is continuously analyzed algorithmically to determine whether the individual's body is falling or not. If an individual falls, the device can employ GPS and a wireless transmitter to determine the location and issue an alert in order to get assistance. The core element of fall detection is an effective, reliable detection principle and algorithm to judge the existence of an emergency fall situation.

This article, based on research into the principles of fall detection for an individual body, proposes a new solution for detection of fall situations utilizing the ADXL345,<sup>1</sup> a 3-axis accelerometer from Analog Devices.

#### The ADXL345 *i*MEMS Accelerometer

*i*MEMS semiconductor technology combines micromechanical structures and electrical circuits on a single silicon chip. Using this technology, *i*MEMS accelerometers sense acceleration on one, two, or even three axes, and provide analog or digital outputs. Depending on the application, the accelerometer may offer different ranges of detection, from several g to tens of g. Digital versions may even have multiple *interrupt* modes. These features offer the user convenient and flexible solutions.

The recently introduced ADXL345 is an *i*MEMS 3-axis accelerometer with digital output. It features a selectable  $\pm 2$ -g,  $\pm 4$ -g,  $\pm 8$ -g, or  $\pm 16$ -g measurement range; resolution of up to 13 bits; fixed 4-mg/LSB sensitivity; a tiny 3-mm  $\times$  5-mm  $\times$  1-mm package; ultralow power consumption (25  $\mu$ A to 130  $\mu$ A); standard I<sup>2</sup>C<sup>®</sup> and SPI serial digital interfacing; and 32-level FIFO storage. A variety of built-in features, including motion-status detection and flexible interrupts, greatly simplify implementation of the algorithm for fall

detection. As you will see, this combination of features makes the ADXL345 an ideal accelerometer for fall-detector applications.

The fall-detection solution proposed here takes full advantage of these internal functions, minimizing the complexity of the algorithm—with little requirement to access the actual acceleration values or perform any other computations.

#### **Interrupt System**

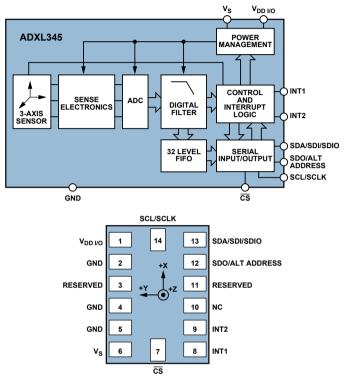

Figure 1 shows the system block diagram and pin definitions of the ADXL345.

Figure 1. ADXL345 system block diagram and pin designations.

The ADXL345 features two programmable interrupt pins—INT1 and INT2—with a total of eight interrupt functions available. Each interrupt can be enabled or disabled independently, with the option to map to either the INT1 or INT2 pin. All functions can be used simultaneously—the only limiting feature is that some functions may need to share interrupt pins. The eight functions are: DATA\_READY, SINGLE\_TAP, DOUBLE\_TAP, ACTIVITY, INACTIVITY, FREE\_FALL, WATERMARK, and OVERRUN. Interrupts are enabled by setting the appropriate bit in the **INT\_ENABLE** register and are mapped to either the INT1 or INT2 pins, based on the contents of the **INT\_MAP** register. The interrupt functions are defined as follows:

- 1. DATA\_READY is set when new data is available—and cleared when no new data is available.

- 2. SINGLE\_TAP is set when a single acceleration event that is greater than the value in the THRESH\_TAP register occurs for a shorter time than specified in the DUR register.

- 3. DOUBLE\_TAP is set when two acceleration events that are greater than the value in the THRESH\_TAP register occur and are shorter than the time specified in the DUR register, with the second tap starting after the time specified by the LATENT register and within the time specified in the WINDOW register.

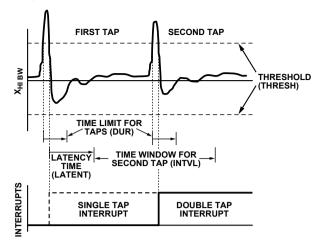

Figure 2 illustrates the valid SINGLE\_TAP and DOUBLE\_TAP interrupts.

Figure 2. SINGLE\_TAP and DOUBLE\_TAP interrupts.

- 4. ACTIVITY is set when acceleration greater than the value stored in the THRESH\_ACT register is experienced.

- 5. INACTIVITY is set when acceleration of less than the value stored in the THRESH\_INACT register is experienced for longer than the time specified in the TIME\_INACT register. The maximum value for TIME\_INACT is 255 s.

Note: With ACTIVITY and INACTIVITY interrupts, the user can enable or disable each axis individually. For example, the ACTIVITY interrupt for the X-axis can be enabled while disabling the interrupts for the Y-axis and Z-axis.

Furthermore, the user can select between dc-coupled or ac-coupled operation mode for the ACTIVITY and INACTIVITY interrupts. In dc-coupled operation, the current acceleration is compared with THRESH\_ACT and THRESH\_ INACT directly to determine whether ACTIVITY or INACTIVITY is detected. In ac-coupled operation for activity detection, the acceleration value at the start of activity detection is taken as a reference value. New samples of acceleration are then compared to this reference value; if the magnitude of the difference exceeds THRESH\_ACT, the device will trigger an ACTIVITY interrupt. In ac-coupled operation for inactivity detection, a reference value is used for comparison and is updated whenever the device exceeds the inactivity threshold. Once the reference value is selected, the device compares the magnitude of the difference between the reference value and the current acceleration with THRESH\_INACT. If the difference is below THRESH\_INACT for a total of TIME\_INACT, the device is considered inactive and the INACTIVITY interrupt is triggered.

- 6. FREE\_FALL is set when acceleration of less than the value stored in the THRESH\_FF register is experienced for longer than the time specified in the TIME\_FF register. FREE\_FALL interrupt is mainly used in detection of free-falling motion. As a result, the FREE\_FALL interrupt differs from the INACTIVITY interrupt in that all axes always participate, the timer period is much shorter (1.28 s maximum), and it is always dc-coupled.

- 7. WATERMARK is set when the number of samples in the FIFO has filled up to the value stored in the SAMPLES register. It is cleared automatically when the FIFO is read

and its content emptied below the value stored in the SAMPLES register.

Note: the FIFO register in the ADXL345 has four operation modes: Bypass, FIFO, Stream, and Trigger; and can store up to 32 samples (X-, Y-, and Z-axis). The FIFO function is an important and very useful feature; *however, the proposed solution does not use the FIFO function*, so it will not be further discussed.

8. OVERRUN is set when new data has replaced unread data. The precise operation of OVERRUN depends on the operation mode of FIFO. In bypass mode, OVERRUN is set when new data replaces unread data in the DATAX, DATAY, and DATAZ registers. In all other modes, OVERRUN is set when the FIFO is filled with 32 samples. OVERRUN is cleared by reading the FIFO contents and is automatically cleared when the data is read.

#### **Acceleration-Change Characteristics While Falling**

The main research on the principles of fall detection focuses on the changes in acceleration that occur when a human is falling.

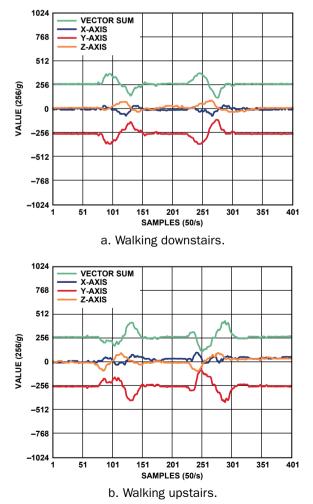

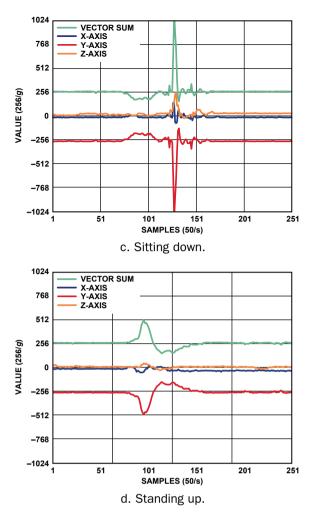

Figure 3 illustrates changes in acceleration that occur when (a) walking downstairs, (b) walking upstairs, (c) sitting down, and (d) standing up from a chair. The fall detector is mounted to a belt on the individual's body. The red trace is the Y-axis (vertical) acceleration; it is -1 g at equilibrium. The black and yellow traces are the respective X-axis (forward) and Z-axis (sideways) accelerations. They are both 0 g at equilibrium. The green trace is the vector sum magnitude, 1 g at equilibrium.

Figure 3. Accelerometer responses to different types of motion.

Because the movement of elderly people is comparatively slow, the acceleration change will not be very conspicuous during the walking motions. The most pronounced acceleration is a 3-g spike in Y (and the vector sum) at the instant of sitting down.

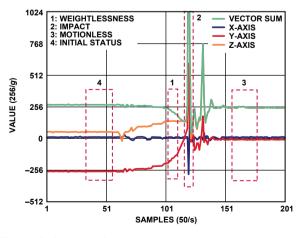

The accelerations during falling are completely different. Figure 4 shows the acceleration changes during an accidental fall. By comparing Figure 4 with Figure 3, we can see four critical differences characteristic of a falling event that can serve as the criteria for fall detection. They are marked in the red boxes and explained in detail as follows:

Figure 4. Acceleration change curves during the process of falling.

- 1. Start of the fall: The phenomenon of weightlessness will always occur at the start of a fall. It will become more significant during free fall, and the vector sum of acceleration will tend toward 0 g; the duration of that condition will depend on the height of freefall. Even though weightlessness during an ordinary fall is not as significant as that during a freefall, the vector sum of acceleration will still be substantially less than 1 g (while it is generally greater than 1 g under normal conditions). Therefore, this is the first basis for determining the fall status that could be detected by the ADXL345's FREE\_FALL interrupt.

- 2. *Impact*: After experiencing weightlessness, the human body will impact the ground or other objects; the acceleration curve shows this as a large shock. This shock is detected by the ACTIVITY interrupt of ADXL345. Therefore, the second basis for determining a fall is the ACTIVITY interrupt right after the FREE\_FALL interrupt.

- 3. *Aftermath*: Generally speaking, the human body, after falling and making impact, can not rise immediately; rather it remains in a motionless position for a short period (or longer as a possible sign of unconsciousness). On the acceleration curve, this presents as an interval of flat line, and is detected by the INACTIVITY interrupt of ADXL345. Therefore, the third basis for determining a fall situation is the INACTIVITY interrupt after the ACTIVITY interrupt.

- 4. Comparing before and after: After a fall, the individual's body will be in a different orientation than before, so the static acceleration in three axes will be different from the initial status before the fall (Figure 4). Suppose that the fall detector is belt-wired on the individual's body, to provide the entire history of acceleration, including the initial status. We can read the acceleration data in all three axes after the INACTIVITY interrupt and compare those sampling data with the initial status. In Figure 4, it is evident that the body fell on its side, since the static acceleration has changed from -1 g on the Y axis to +1 g on the Z-axis. So the fourth basis for determining a fall is if the difference between sampling data and initial status exceeds a certain threshold, for example, 0.7 g.

The combination of these qualifications forms the entire falldetection algorithm, which, when exercised, can cause the system to raise an appropriate alert that a fall has occurred. Of course, the time interval between interrupts has to be within a reasonable range. Normally, the time interval between FREE\_FALL interrupt (weightlessness) and ACTIVITY interrupt (impact) is not very long unless one is falling from the top of a very high building! Similarly, the time interval between ACTIVITY interrupt (impact) and INACTIVITY interrupt (essentially motionless) should not be very long. A practical example will be given in the next section with a set of reasonable values. The related interrupt detection threshold and time parameters can be flexibly set as needed.

If a fall results in serious consequences, such as unconsciousness, the human body will remain motionless for an even longer period of time, a status that can still be detected by the INACTIVITY interrupt, so a second critical alert could be sent out if the inactive state was detected to continue for a defined long period of time after a fall.

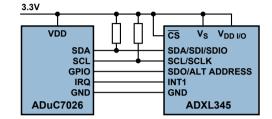

#### **Typical Circuit Connection**

The circuit connection between the ADXL345 and a microcontroller is very simple. For this article, the test platform uses the ADXL345 and an ADuC7026 analog microcontroller—which features 12-bit

analog I/O and an ARM7TDMI<sup>®</sup> MCU. Figure 5 shows the typical connection between ADXL345 and ADuC7026.<sup>2</sup> With the  $\overline{CS}$  pin of ADXL345 tied high, the ADXL345 works in I<sup>2</sup>C mode. The SDA and SCL, the data and clock of the I<sup>2</sup>C bus, are connected to the corresponding pins of ADuC7026. A GPIO of ADuC7026 is connected to the ADXL345's ALT pin to select the I<sup>2</sup>C address of the ADXL345, and the INT1 pin of ADXL345 is connected to an IRQ input of the ADuC7026 to generate the interrupt signal.

Other MCU or processor types could be used to access the ADXL345, with similar circuit connections to Figure 5, but the ADuC7026 also provides a data-acquisition facility including

multichannel analog-to-digital and digital-to-analog conversion. The ADXL345 data sheet describes SPI-mode applications to achieve higher data rates.

#### Using the ADXL345 to Simplify Fall Detection

Table 1, Figure 5, and the Appendix (Page 8) define the realization of the algorithm for the solution mentioned above. The function of each register is included in the table, and the values used in the present algorithm are as indicated. Please refer to the ADXL345 data sheet for the detailed definition of each register bit.

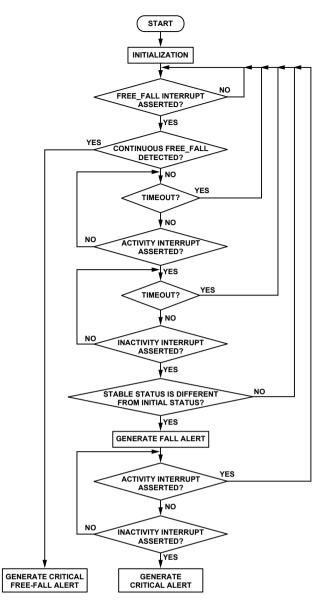

Some of the registers in Table 1 will have two values. This indicates that the algorithm switches between these values for different aspects of detection. Figure 6 is an algorithm flow chart.

Figure 5. Typical circuit connection between the ADXL345 and microcontroller.

| Hex<br>Address | Register Name  | Туре                                  | Reset<br>Value | Description                                 | Settings in<br>Algorithm | Function of the Settings in Algorithm                                                                                                 |

|----------------|----------------|---------------------------------------|----------------|---------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0              | DEVID          | Read-only                             | 0xE5           | Device ID                                   | Read-only                | <u> </u>                                                                                                                              |

| 1-1C           | Reserved       | , , , , , , , , , , , , , , , , , , , |                | Reserved, do not access                     | Reserved                 |                                                                                                                                       |

| 1D             | THRESH TAP     | Read/write                            | 0x00           | Tap threshold                               | Not used                 |                                                                                                                                       |

| 1E             | OFSX           | Read/write                            | 0x00           | X-axis offset                               | 0x06                     | X-axis, offset compensation get from initialization calibration                                                                       |

| 1F             | OFSY           | Read/write                            | 0x00           | Y-axis offset                               | 0xF9                     | Y-axis offset compensation, get from initialization calibration                                                                       |

| 20             | OFSZ           | Read/write                            | 0x00           | Z-axis offset                               | 0xFC                     | Z-axis offset compensation, get from initialization calibration                                                                       |

| 21             | DUR            | Read/write                            | 0x00           | Tap duration                                | Not used                 |                                                                                                                                       |

| 22             | LATENT         | Read/write                            | 0x00           | Tap latency                                 | Not used                 |                                                                                                                                       |

| 23             | WINDOW         | Read/write                            | 0x00           | Tap window                                  | Not used                 |                                                                                                                                       |

| 24             | THRESH_ACT     | Read/write                            | 0x00           | Activity threshold                          | 0x20/0x08                | Set activity threshold as 2 g/0.5 g                                                                                                   |

| 25             | THRESH_INACT   | Read/write                            | 0x00           | Inactivity threshold                        | 0x03                     | Set inactivity threshold as 0.1875 g                                                                                                  |

| 26             | TIME_INACT     | Read/write                            | 0x00           | Inactivity time                             | 0x02/0x0A                | Set inactivity time as 2 s or 10 s                                                                                                    |

| 27             | ACT_INACT_CTL  | Read/write                            | 0x00           | Axis enable control for activity/inactivity | 0x7F/0xFF                | Enable activity and inactivity of X-, Y-, Z-axis,<br>wherein inactivity is ac-coupled mode, activity is<br>dc-coupled/ac-coupled mode |

| 28             | THRESH_FF      | Read/write                            | 0x00           | Free-fall threshold                         | 0x0C                     | Set free-fall threshold as 0.75 g                                                                                                     |

| 29             | TIME_FF        | Read/write                            | 0x00           | Free-fall time                              | 0x06                     | Set free-fall time as 30 ms                                                                                                           |

| 2A             | TAP_AXES       | Read/write                            | 0x00           | Axis control for tap/<br>double tap         | Not used                 |                                                                                                                                       |

| 2B             | ACT_TAP_STATUS | Read-only                             | 0x00           | Source of activity/tap                      | Read-only                |                                                                                                                                       |

| 2C             | BW_RATE        | Read/write                            | 0x0A           | Data rate and power mode control            | 0x0A                     | Set sample rate as 100 Hz                                                                                                             |

| 2D             | POWER_CTL      | Read/write                            | 0x00           | Power save features control                 | 0x00                     | Set as normal working mode                                                                                                            |

| 2E             | INT_ENABLE     | Read/write                            | 0x00           | Interrupt enable control                    | 0x1C                     | Enable activity, inactivity, free-fall interrupts                                                                                     |

| 2F             | INT_MAP        | Read/write                            | 0x00           | Interrupt mapping control                   | 0x00                     | Map all interrupts to Int1 pin                                                                                                        |

| 30             | INT_SOURCE     | Read-only                             | 0x00           | Source of interrupts                        | Read-only                |                                                                                                                                       |

| 31             | DATA_FORMAT    | Read/write                            | 0x00           | Data format control                         | 0x0B                     | Set as $\pm 16 g$ measurement range, 13-bit right<br>alignment, high level interrupt trigger, I <sup>2</sup> C interface              |

| 32             | DATAX0         | Read-only                             | 0x00           | X-axis data                                 | Read-only                |                                                                                                                                       |

| 33             | DATAX1         | Read-only                             | 0x00           | 1                                           | Read-only                |                                                                                                                                       |

| 34             | DATAY0         | Read-only                             | 0x00           | Y-axis data                                 | Read-only                |                                                                                                                                       |

| 35             | DATAY1         | Read-only                             | 0x00           | 7                                           | Read-only                |                                                                                                                                       |

| 36             | DATAZ0         | Read-only                             | 0x00           | Z-axis data                                 | Read-only                |                                                                                                                                       |

| 37             | DATAZ1         | Read-only                             | 0x00           | 1                                           | Read-only                |                                                                                                                                       |

| 38             | FIFO_CTL       | Read/write                            | 0x00           | FIFO control                                | Not used                 |                                                                                                                                       |

| 39             | FIFO_STATUS    | Read/write                            | 0x00           | FIFO status                                 | Not used                 |                                                                                                                                       |

Figure 6. Algorithm flow chart.

Each interrupt threshold, and the related time parameter in the algorithm, is as described below.

- 1. After initialization, the system waits for the FREE\_FALL interrupt (weightlessness). Here THRESH\_FF is set to 0.75 g and TIME\_FF is set to 30 ms.

- 2. After FREE\_FALL interrupt is asserted, the system begins

waiting for the ACTIVITY interrupt (impact). THRESH\_ACT is set to 2 g and the ACTIVITY interrupt is in dc-coupled mode.

- 3. Time interval between FREE\_FALL interrupt (weightlessness) and ACTIVITY interrupt (impact) is set to 200 ms. If the time between these two interrupts is greater than 200 ms, the status is not valid. The 200-ms counter is realized through the MCU timer.

- 4. After the ACTIVITY interrupt is asserted, the system begins waiting for the INACTIVITY interrupt (motionless after impact). THRESH\_INACT is set to 0.1875 g and TIME\_INACT is set to 2 s. INACTIVITY interrupt works in ac-coupled mode.

- 5. The INACTIVITY interrupt (motionless after impact) should be asserted within 3.5 s after the ACTIVITY interrupt (impact). Otherwise, the result is invalid. The 3.5-s counter is realized through the MCU timer.

- 6. If the acceleration difference between stable status and initial status exceeds the 0.7-*g* threshold, a valid fall is detected, and the system will raise a fall alert.

- 7. After detecting a fall, the ACTIVITY interrupt and INACTIVITY interrupt have to be continuously monitored to determine if there is a long period of motionlessness after the fall. The THRESH\_ACT is set to 0.5 g and the ACTIVITY interrupt is running in the ac-coupled mode. THRESH\_INACT is set to 0.1875 g, TIME\_INACT is set to 10 s, and the INACTIVITY interrupt is working in ac-coupled mode. In other words, if the subject's body remains motionless for 10 s the INACTIVITY interrupt will be asserted and the system raises a critical alert. Once the subject's body moves, the ACTIVITY interrupt will be generated to complete the entire sequence.

- 8. The algorithm can also detect if the individual's body freefalls from a high place. Here, we consider that the two FREE\_FALL interrupts are continuous if the interval between them is shorter than 100 ms. A critical freefall alert will be raised if the FREE\_FALL interrupt (weightlessness) is continuously asserted for 300 ms

$$S = \frac{1}{2}gt^2 = \frac{1}{2} \times 10 \times 0.3^2 = 0.45 \text{ m}.$$

This algorithm is developed in C language to be executed on the ADuC7026 microcontroller (See Appendix, Page 8). A test case is also presented with the proposed solution to verify the algorithm. Each position, including falling forward, falling backward, falling to the left, and falling to the right is tested 10 times. Table 2 presents the test results. Check marks ( $\checkmark$ ) indicate each condition that is satisfied.

|                      | Table 2. Test Results                        |              |              |              |              |              |              |              |              |              |              |

|----------------------|----------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Falling Position     | Prolonged Motionless<br>Period after Falling | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           |

| Falling Forward      | No                                           | $\checkmark$ |

|                      | Yes                                          | ✓*           | √*           | ✓*           | ✓*           | ✓*           | √*           | ✓*           | ✓*           | ✓*           | ✓*           |

| Falling Backward     | No                                           | $\checkmark$ |

|                      | Yes                                          | ✓*           | √*           | ✓*           | ✓*           | ✓*           | √*           | ✓*           | ✓*           | ✓*           | ✓*           |

| Falling to the Left  | No                                           | $\checkmark$ |

|                      | Yes                                          | ✓*           | √*           | ✓*           | ✓*           | ✓*           | √*           | ✓*           | ✓*           | ✓*           | ✓*           |

| Falling to the Right | No                                           | $\checkmark$ |

|                      | Yes                                          | ✓*           | √*           | ✓*           | √*           | ✓*           | √*           | √*           | ✓*           | ✓*           | ✓*           |

Table 2. Test Results

Note: The  $\checkmark$  symbol indicates a detected fall; the \* symbol indicates a detected prolonged motionless period after falling.

This experiment shows that falling status can be effectively detected with the proposed solution, based on the ADXL345. This is only a simple experiment. More comprehensive, effective, and long-term experimentation will be required to verify the reliability of the proposed solution.

#### Conclusion

The ADXL345 is a powerful and full-featured accelerometer. We have described a proposed new solution for the fall-detection problem that takes advantage of the various built-in motion-status detection features and flexible interrupts. Tests have shown that it combines low algorithm complexity and high detection accuracy.

#### Appendix—An Example of the Code

This section presents an example of C code for the proposed solution, based on the ADXL345 and ADuC7026 platform. There are four .h files and one .c file in the project, compiled by Keil UV3. The .c file code is listed below.

#### Author

#### Ning Jia [ning.jia@analog.com], a

field applications engineer, has been a member of the Analog Devices China Applications Support Team for two years. He is responsible for the technical support of a broad range of analog products across China. He graduated in 2007 from Beijing University of Posts and Telecommunications with a master's degree in signal and information processing.

#### References

- <sup>1</sup>Information on all ADI components can be found at www.analog.com.

- <sup>2</sup>www.analog.com/en/analog-microcontrollers/ADuC7026/ products/product.html.

// Include header files #include "FallDetection.h" void IRQ\_Handler() \_\_irq // IRQ interrupt unsigned char i; if((IRQSTA & GP\_TIMER\_BIT)==GP\_TIMER\_BIT)//TIMER1 Interrupt, interval 20ms  $T_{1CLRI} = 0;$ // Clear Timer1 interrupt

// Strike after weightlessness is detected, waiting for stable if (DetectionStatus==0xF2) TimerWaitForStable++;

if(TimerWaitForStable>=STABLE\_WINDOW)// Time out, restart IRQCLR = GP\_TIMER\_BIT;// Disable ADuC7026's Timer1 interrupt IRQCLR = 0r ------DetectionStatus=0xT0; putchar(DetectionStatus); ADXL345Registers[XL345\_THRESH\_TNACT]=STRIKE\_THRESHOLD; ADXL345Registers[XL345\_THRESH\_TNACT]=NOMOVEMENT\_THRESHOLD; ADXL345Registers[XL345\_TINACT\_CTL]=NACT\_STRESHOLD; ADXL345Registers[XL345\_ACT\_INACT\_CTL]=XL345\_INACT\_Z\_ENABLE | XL345\_INACT\_Y\_ENABLE | XL345\_INACT\_AC | XL345\_ACT\_Z\_ENABLE | XL345\_ACT\_V\_ENABLE | XL345\_ACT\_V\_ENABLE | XL345\_ACT\_V\_ENABLE | XL345\_ACT\_DC; x1345Write(4, XL345 THRESH ACT, &ADXL345Registers[XL345 THRESH ACT]); , else if(DetectionStatus==0xF1)// Weightlessness is detected, waiting for strike TimerWaitForStrike++; if(TimerWaitForStrike>=STRIKE\_WINDOW)// Time out, restart I IRQCLR = GP\_TIMES\_\_\_\_\_ DetectionStatus=0xF0; putchar(DetectionStatus); ADXL345Registers[XL345\_THRESH\_ACT]=STRIKE\_THRESHOLD; ADXL345Registers[XL345\_THRESH\_TNACT]=NOMOVEMENT\_THRESHOLD; ADXL345Registers[XL345\_THME\_INACT]=STABLE\_TIME; ADXL345Registers[XL345\_ACT\_INACT\_CTL]=XI345\_INACT\_Z\_ENABLE | XL345\_INACT\_Y\_ENABLE | XL345\_ACT\_Y\_ENABLE | XL345\_ACT\_Y\_ENABLE | XL345\_ACT\_Y\_ENABLE | XL345\_ACT\_Y\_ENABLE | XL345\_ACT\_DC; XL345\_ACT\_X\_ENABLE | XL345\_ACT\_DC; IRQCLR = GP TIMER BIT;// Disable ADuC7026's Timerl interrupt x1345Write(4, XL345 THRESH ACT, &ADXL345Registers[XL345 THRESH ACT]); } ; if((IRQSTA&SPM4\_IO\_BIT)==SPM4\_IO\_BIT)// External interrupt form ADXL345 INTO IRQCER = SPM4 IO BIT; // Disable ADuc7026's external interrupt x1345Read(1, XL345 INT SOURCE, &ADXL345Registers[XL345 INT SOURCE]); if(ADXL345Registers[XL345\_INT\_SOURCE]&XL345\_ACTIVITY]==XL345\_ACTIVITY]// Activity interrupt asserted xl345Write(4, XL345\_THRESH\_ACT, &ADXL345Registers[XL345\_THRESH\_ACT]); IRQEN|=GP\_TIMER\_BIT;// Enable ADuC7026's Timerl interrupt TimerMaitForstable=0; else if(DetectionStatus==0xF4)// Waiting for long time motionless, but a movement is detected x1345Write(4, XL345 THRESH ACT, &ADXL345Registers[XL345 THRESH ACT]); , else if((ADXL345Registers[XL345\_INT\_SOURCE]&XL345\_INACTIVITY)==XL345\_INACTIVITY) // Inactivity interrupt asserted // Waiting for stable, and now stable is detected if(DetectionStatus==0xF2) DetectionStatus=0xF3;// Go to Status "F3" IRQCLR = GP\_TIMER\_BIT; putchar(DetectionStatus); x1345Read(6, XL345\_DATAX0, &ADXL345Registers[XL345\_DATAX0]); DeltaVectorSum=0; for(i=0;i<3; i++)</pre> Acceleration[i]=ADXL345Registers[XL345\_DATAX1+i\*2]&0x1F; Acceleration[i]=(Acceleration[i]<<8)|ADXL345Registers[XL345\_DATAX0+i\*2];</pre>

```

if(Acceleration[i]<0x1000)

Acceleration[i]=Acceleration[i]+0x1000;

else //if(Acceleration[i]>=4096)

Acceleration[i]=Acceleration[i]-0x1000:

3

if(Acceleration[i]>InitialStatus[i])

DeltaAcceleration[i]=Acceleration[i]-InitialStatus[i];

else

DeltaAcceleration[i]=InitialStatus[i]-Acceleration[i];

}

DeltaVectorSum=DeltaVectorSum+DeltaAcceleration[i]*DeltaAcceleration[i];

if(DeltaVectorSum>DELTA_VECTOR_SUM_THRESHOLD) // The stable status is different from the initial status

DetectionStatus=0xF4; // Valid fall detection

putchar(DetectionStatus);

-

ADXL345Registers[XL345 THRESH ACT]=STABLE THRESHOLD;

ADXL345Registers[XL345 THRESH INACT]=NOMOVEMENT THRESHOLD;

ADXL345Registers[XL345 THRESH INACT]=NOMOVEMENT THRE;

ADXL345Registers[XL345 ACT INACT_CTL]=XL345 INACT_Z_ENABLE | XL345_INACT_Y_ENABLE

| XL345_INACT_X_ENABLE | XL345_INACT_AC

| XL345_ACT_Z_ENABLE | XL345_ACT_Y_ENABLE

| XL345_ACT_X_ENABLE | XL345_ACT_AC;

xL345Write(4, XL345_THRESH_ACT, &ADXL345Registers[XL345_THRESH_ACT]);

}

else

// Delta vector sum is not exceed the threshold

| XL345_ACT_Z_ENABLE | XL345_ACT_Y_ENABLE

| XL345_ACT_X_ENABLE | XL345_ACT_DC;

| XL345_ACT_X_ENABLE | XL345_ACT_DC;

| Xl345Write(4, XL345_THRESH_ACT, &ADXL345Registers[XL345_THRESH_ACT]);

else if(DetectionStatus==0xF4) // Wait for long time motionless and now it is detected

DetectionStatus=0xF5; // Valid critical fall detection

putchar(DetectionStatus);

ADXL345Registers[XL345_THRESH_ACT]=STRIKE_THRESHOLD;

ADXL345Registers[XL345_THRESH_INACT]=NOMOVTMENT_THRESHOLD;

ADXL345Registers[XL345_TTIME_ITACT]=STABLE_TIME;

ADXL345Registers[XL345_TTINACT_CTL]=XL345_INACT_Z_ENABLE | XL345_INACT_Y_ENABLE

| XL345_INACT_X_ENABLE | XL345_INACT_AC

| XL345 ACT Z ENABLE | XL345 ACT Y ENABLE

| XL345_ACT_X_ENABLE | XL345 ACT_DC;

x1345Mrite(4, XL345 THRESH_ACT, &ADXL345Registers[XL345 THRESH_ACT]);

DetectionStatus=0xF0; // Go to Status "F0", restart

putchar(DetectionStatus);

'se if((ADXL345Registers[XL345_INT_SOURCE]&XL345_FREEFALL) ==XL345_FREEFALL) // Free Fall interrupt asserted

if(DetectionStatus==0xF0)

// Waiting for weightless, and now it is detected

{

DetectionStatus=0xFl; // Go to Status "Fl"

putchar(DetectionStatus;);

ADXL345Registers(XL345_THRESH_ACT]=STRIKE_THRESHOLD;

ADXL345Registers(XL345_THRESH_TIACT]=NOMOVEMENT_THRESHOLD;

ADXL345Registers(XL345_TIME_INACT_I=NOMOVEMENT_THRESHOLD;

ADXL345Registers(XL345_TIME_INACT_CL]=NABLE TIME;

ADXL345Registers(XL345_TIME_TACT_CL]=XL345_INACT_Z_ENABLE | XL345_INACT_Y_ENABLE

| XL345_INACT_X_ENABLE | XL345_INACT_AC

| XL345 ACT Z ENABLE | XL345 ACT Y ENABLE

| XL345_ACT_X_ENABLE | XL345_ACT_DC;

x1345write(4, XL345_THRESH_ACT, &ADXL345Registers[XL345_THRESH_ACT]);

IRQEN|=GP_TIMER_BIT; //Tenable_ADuC7026's Timer1 interrupt

TimerWaitForStrIke=0;

TimerFreeFall=0;

/ else if(DetectionStatus==0xFl) // Waiting for strike after weightless, and now a new free fall is detected

if(TimerWaitForStrike<FREE_FALL_INTERVAL) // if the Free Fall interrupt is continuously assert within the time of

"FREE_FALL_INTERVAL",

// then it is consider as a continuous free fall

TimerFreeFall=TimerFreeFall+TimerWaitForStrike;

{

élse

/ Not a continuous free fall

TimerFreeFall=0;

}

TimerWaitForStrike=0;

if(TimerFreeFall>=FREE_FALL_OVERTIME)

// if the continuous time of free fall is longer than

"FREE_FALL_OVERTIME"

// consider that a free fall from high place is detected

DetectionStatus=0xFF:

{

DetectionStatus=0xFF;

putchar(DetectionStatus);

ADKL345Registers[XL345_THRESH ACT]=STRIKE THRESHOLD;

ADXL345Registers[XL345_THRESH INACT]=NOMOVEMENT_THRESHOLD;

ADXL345Registers[XL345_TIME_INACT]=NOMOVEMENT_THRESHOLD;

ADXL345Registers[XL345_TIME_INACT]=STABLE TIME;

ADXL345Registers[XL345_ACT_INACT_CTL]=XL345_INACT_Z_ENABLE | XL345_INACT_Y_ENABLE

| XL345_INACT_X_ENABLE | XL345_INACT_AC

| XL345_ACT_Z_ENABLE | XL345_ACT_Y_ENABLE

}

else

TimerFreeFall=0;

}

IRQEN |=SPM4 IO BIT;

// Enable ADuC7026's external interrupt

}

}

void main(void)

ADuC7026 Initiate();

ADXL345 Initiate();

DetectionStatus=0xF0;

InitialStatus[0]=0x1000;

InitialStatus[1]=0x1000;

InitialStatus[2]=0x1000;

// ADuC7026 initialization

// ADXL345 initialization

// Clear detection status, Start

// X axis=0g, unsigned short int, 13 bit resolution, 0x1000 = 4096 = 0g, +/-0xFF = +/-256 = +/-1g

// Y axis=-1g

// Z axis=0g

// Enable ADuC7026's external interrupt, to receive the interrupt from ADXL345 INTO

righter the interrupt from ADXL345 INTO

IRQEN =SPM4 IO BIT;

while(1)// Endless loop, wait for interrupts

;

}

```

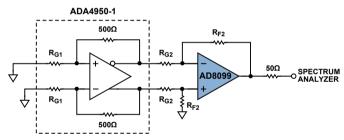

## Measuring Noise of Low-Fixed-Gain Differential Amplifiers

#### By Angel Caballero

Noise, composed of small, random voltages, can be difficult to measure. Lab instruments add their own noise, further complicating the measurement. Special techniques are often used when measuring noise. For example, amplifiers are typically configured with high closed-loop gains, multiplying their input noise to make it easier to measure. Low-fixed-gain differential amplifiers present a greater challenge, however, as their integrated feedback and gain resistors preclude the use of a high-gain configuration. Additionally, differential-to-singleended conversion is needed to interface with available spectrum analyzers. A second amplifier stage can provide gain and the differential-to-single-ended conversion, neatly solving both of these problems.

Figure 1 shows an ADA4950-1<sup>1</sup> selectable-gain (1, 2, or 3) differential amplifier followed by an AD8099<sup>2</sup> low-noise, low-distortion op amp. The AD8099, configured for a gain of 10, converts the differential output into a single-ended signal. Its  $1-nV/\sqrt{Hz}$  input-referred voltage noise is negligible compared to that of the ADA4950-1. The output of the ADA4950-1 is multiplied by 10, making its noise proportionately larger as well. With a 0.5-pF compensation capacitor and gain of 10, the AD8099 has enough bandwidth to measure the noise of the ADA4950-1 up to 10 MHz before the system's frequency response starts to roll off.

Figure 1. The AD8099 low-noise, low-distortion op-amp is used to measure the noise of the ADA4950-1 selectable-gain differential amplifier.

The output voltage of the AD8099 is simply:

$$V_{OUT} = V_{OUT, DIFF} \times \frac{R_{F2}}{R_{G2}}$$

(1)

The noise contribution of the AD8099, measured with inputs grounded, is treated as the noise floor of the measurement system. The total output noise including the ADA4950-1 was then measured, with the contribution from the AD8099 subtracted using root-sum-square math, as shown in Equation 2, where  $V_{n1}$  is the output noise of the ADA4950-1 and  $V_{n2}$  is the output noise of the AD8099.

Total output noise:

$$V_{total}^{2} = \left(V_{n1} \times \frac{R_{F2}}{R_{G2}}\right)^{2} + V_{n2}^{2}$$

(2)

A few other techniques were implemented to accurately measure the system noise:

• When measuring the noise of the AD8099, its inputs were grounded with SMA connectors that had their

center conductor shorted to the ground pins of the connector. Additionally, the SMA connectors were soldered together, creating a shared electrical connection to ground directly at the connectors, instead of through the board.

- An analog-controlled power supply was used for the AD8099 and the ADA4950-1. Compared to digitally controlled power supplies, analog-controlled power supplies are better at rejecting 60-Hz noise and harmonics that couple in from the power line.

- All nearby instruments were turned off unless they were being used for the measurement. This minimized oscillations generated by the instruments to control their digital circuitry. These oscillations can couple through the air and into the amplifiers. For the same reason, 4-ft cables were used to connect the circuit boards to the spectrum analyzer, which was picking up the refresh frequency of the display and affecting the output of the AD8099.

- Low-value resistors ( $R_F = 250 \Omega$ ;  $R_G = 25 \Omega$ ) were used to configure the AD8099's gain in order to keep their noise contribution small. Lower values caused the AD8099 to oscillate. When the ADA4950-1 was connected to the AD8099 with a short cable, an oscillation was observed at 250 MHz. When a 1-ft cable was used, the oscillations went away.

The AD8099 itself contributed only a small amount of noise:

$$v_{OUT}^{2} = \left[ \left( 1 + \frac{R_{F2}}{R_{G2}} \right) v_{n} \right]^{2} + R_{F2}^{2} \left( n_{i+}^{2} + n_{i-}^{2} \right) + 2 \left( n_{RG2} \times \frac{R_{F2}}{R_{G2}} \right)^{2} + 2n_{RF2}^{2} + n_{50}^{2}$$

(3)

where  $v_n$  is the input voltage noise; and  $n_{i+}$  and  $n_{i-}$  are the input current noise of the AD8099.

Measuring the ADA4950-1's current noise is impossible because a large feedback resistor is needed to amplify the noise, but the value of the internal feedback resistor cannot be changed.

The Stanford Research Systems SR785 was used to measure noise up to 100 kHz, while the Agilent E4440 PSA spectrum analyzer was used for noise beyond 100 kHz.

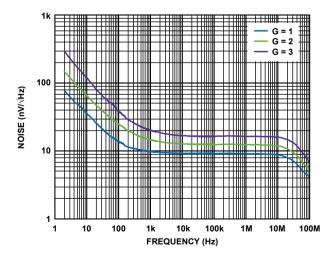

Figure 2. Test results.

#### References

- <sup>1</sup> www.analog.com/en/amplifiers-and-comparators/differentialamplifiers/ada4950-1/products/product.html.

- <sup>2</sup> www.analog.com/en/amplifiers-and-comparators/operationalamplifiers-op-amps/ad8099/products/product.html.

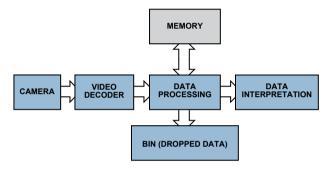

# The Basics of Video Decoders in Supervision and Inspection

#### By Witold Kaczurba

Video inspection<sup>1</sup> systems are used in many commercial and industrial processes. Cameras—which range from those in inexpensive, low-definition black-and-white closed-circuit television (CCTV) systems to those in state-of-the-art high-definition digital-video systems—are used in diverse applications ranging from product inspection to traffic monitoring to real-time face recognition.

Video inherently carries a lot of data, which can complicate signal-processing and data-storage tasks. Video inspection can often be simplified by cropping useless information and passing only the essential parts of the picture, which saves both memory and computational cycles. Figure 1 shows the elements of a typical system.

Figure 1. Simplified video-inspection data flow.

This article shows a few examples of how extracting useful data can minimize processing, memory size, and DSP usage—and illustrates how special features of Analog Devices video decoders<sup>2</sup> can simplify video algorithms and speed up development of video inspection systems.

#### **Example 1. Counting and Inspecting Objects**

Imagine a wide conveyor belt containing many rapidly moving products. The large number of products makes manual counting difficult. In addition to automating the counting task, a camera can be used to monitor product quality. This can be accomplished by modifying the simple count algorithm to focus on particular details and artifacts.

Storing all of the video data requires a huge amount of memory, and processing a large amount of data will cost a lot in terms of hardware and power. Instead of collecting whole pictures in memory, the system can find interesting details in the pile of data and drop as much useless data as possible when inspecting the products on the conveyor belt.

In most cases, gray-scale pictures can carry enough information. So chrominance information can be dropped by converting RGB signals to Y (luminance only). The resulting monochromatic picture can then be examined for content by using *edge detection* to find products on the belt and compare their shapes with a template to determine whether the product is misshapen.

Edge detection algorithms—which require only a few lines of active video and a small amount of memory—find discontinuities in the brightness of adjacent pixels by calculating the first and second derivatives of active pictures, as described in *Digital Image Processing* by Bernd Jähne.<sup>3</sup> Edge detection can be implemented in

practice by extracting information using matrix calculations, such as the Sobel<sup>4</sup> matrix operator. In an FPGA (field-programmable gate-array) implementation, doing this on a pixel basis gives satisfying results. A simple FPGA implementation is shown in *A Proposed FPGA Based Architecture for Sobel Edge Detection Operator* by Tanvir A. Abbasi and Mohm. Usaid Abbasi.<sup>5</sup> Noise can be removed by adding a Gaussian 2D filter, as described in *Hardware Acceleration of Edge Detection Algorithm on FPGAs* by Mathukumar Venkatesan and Daggu Venkateshwar Rao,<sup>6</sup> which describes a successful implementation of a detector similar to the Canny edge detector.<sup>7</sup>

Several other optimization algorithms can enhance the picture quality, but all occupy significant space on the FPGA design. However, some integrated-circuit (IC) video decoders are already equipped with useful preprocessing algorithms or filters; so choosing one of these would save space in the FPGA. For example, the ADV7802 video decoder<sup>8</sup> includes both *luma transient improvement* (LTI) and *chroma transient improvement* (CTI) blocks. These blocks, which enhance the resulting picture by improving the steepness of luma and chroma transitions, use adaptive peaking and nonlinear methods—without increasing noise or introducing artifacts—and can be very useful in the process of edge detection. In addition, luma-shaping and other built-in input filters can remove high-frequency noise from the source—focusing on the signal and ignoring incidental noise.

Figure 2. LTI/CTI operation diagram.

Edge detection provides information on an object's edge transitions instead of a full picture of the object. This reduction, from  $3 \times 8$  bits per pixel (bpp) to 1 bpp, saves a lot of memory:

- •640 pixels × 480 pixels = 307,200 bits at 1 bpp •800 pixels × 600 pixels = 480,000 bits at 1 bpp

- $\sim 800 \text{ pixels} \times 600 \text{ pixels} = 480,000 \text{ bits at 1 opp}$

- •1024 pixels × 768 pixels = 786,432 bits at 1 bpp •1280 pixels × 720 pixels = 921,600 bits at 1 bpp

By converting RGB to Y, storing just a few lines of active video in memory, and using FPGA algorithms, we can detect objects and see their shapes. Once their locations on the moving belt are known, we can estimate their movement and collect color or other information from the next frames with the assurance that a minimum amount of memory is being used. The process involves

- 1. Edge detection

- 2. Storing information

- 3. Predicting the next position  $x_{n+1}$

- 4. Extracting information in areas where product is supposed to be

#### **Example 2. Detecting Motion and Quality**

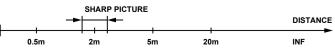

A robot is looking for items at a particular distance and within a limited range. Ultrasound can be used in some applications; but if the surface absorbs ultrasound or the items are behind glass, video can be used. The camera is set to focus on nearby objects. Items within a narrow range will have sharp edges, but background items—which are outside that range—have fuzzy edges (Figure 3).

Figure 3. Focus—narrow depth of field.

Edge detection can be used to distinguish the items within the target range, as these are the only ones with sharp edges. Items in the background will be fuzzy enough to fail an edge detection test. Processing yields a binary bitmap where a 1 means that an edge was detected and a 0 means that no edge was detected. The position (x, y) of each detected edge pixel can be used to approximate the middle of an isolated object using Equation 1:

ъr

Ĵ

$$x_{average} = \frac{\sum_{n=1}^{N} x_n}{N} ; \quad y_{average} = \frac{\sum_{n=1}^{N} y_n}{N}$$

(1)

Where  $x_n$  is the x-position of edge pixel, n;  $y_n$  is the y-position of edge pixel, n; and N is the number of edge pixels detected.

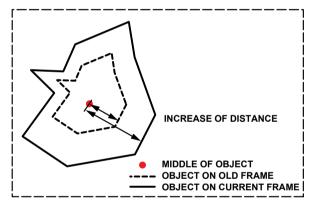

Once the position of the object and its edges are known, we can try to trace it. The key is to extract exactly one object from the picture, transforming its edges to an outline that can be used to determine if the item is moving toward the camera by checking the average distance of pixels from the middle of the object to see if the size of object is changing, as shown in Equation 2 (below).

N is the number of edge pixels in FRAME; M is the number of edge pixels in FRAME-1.

Focusing on the horizontal axis leads to Equation 3 (below).

The value of this equation will be positive when the object is moving toward the camera (pixels are spreading from the middle of object). A negative value means that the object is moving away from the camera, as shown in Figure 4.

Figure 4. Frame change of moving object.

Note that the object has to be within the camera's range of focus. By modifying the algorithm, we can actively change the focus<sup>9</sup> to scan a wider area. Once the objects are detected, they can be segmented, processed, and tracked.

$$\frac{1}{N} \sum_{n}^{N} \left( \sqrt{\left( x_{n}^{FRAME} - x_{average}^{FRAME} \right)^{2} + \left( y_{n}^{FRAME} - y_{average}^{FRAME} \right)^{2}} \right) - \frac{1}{M} \sum_{m}^{M} \left( \sqrt{\left( x_{m}^{FRAME-1} - x_{average}^{FRAME-1} \right)^{2} + \left( y_{m}^{FRAME-1} - y_{average}^{FRAME-1} \right)^{2}} \right)$$

$$\frac{1}{N}\sum_{n}^{N}\left(x_{i}^{FRAME}-x_{average}^{FRAME}\right)-\frac{1}{M}\sum_{n}^{M}\left(x_{i}^{FRAME-1}-x_{average}^{FRAME-1}\right)$$

(3)

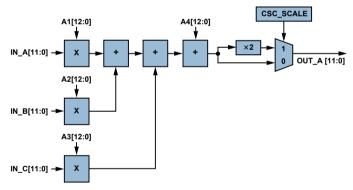

$$\begin{bmatrix} Channel\_A\_out\\ Channel\_B\_out\\ Channel\_C\_out \end{bmatrix} = \begin{bmatrix} A1 & A2 & A3\\ B3 & B1 & B2\\ C2 & C3 & C1 \end{bmatrix} \begin{bmatrix} Channel\_A\_in\\ Channel\_B\_in\\ Channel\_C\_in \end{bmatrix} + \begin{bmatrix} A4\\ B4\\ C4 \end{bmatrix}$$

(4)

Tracking objects becomes more difficult as video complexity increases, especially with textured objects and objects that lose sharpness because they move quickly. Some tracking algorithms are shown in *Good Features to Track* by Jianbo Shi.<sup>10</sup> As objects lose sharpness, edge detection fails. Tracking can still be done by using complex correlation techniques such as block matching—used to estimate motion—or other methods detailed in *Video Processing and Communications* by Yao Wang, Jörn Ostermann, and Ya-Qin Zhang.<sup>11</sup>

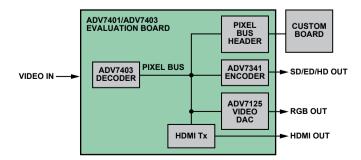

Thanks to continuous data flow from the camera, an object can be tracked to determine its acceleration and other parameters. However, a high-quality video sequence must be used in order to obtain good video analysis results. When detecting edges by analyzing adjacent pixels, the resolution will be better if progressivescan video is used instead of low-quality interlaced PAL or NTSC signals. The ADV7401 and ADV7403 video decoders<sup>12</sup> accept a variety of video standards, including progressive modes. Capable of digitizing video signals up to 140 MHz, they can handle SD, ED, and HD component signals, CVBS, and graphics. In addition, they support nonstandard video modes, allowing the use of lesspopular standards, such as STANAG. The flexible pixel output bus allows data processing in 4:2:2, 4:4:4 YCrCb, or 4:4:4 RGB formats. Nonstandard video formats can be oversampled or undersampled to get a given horizontal width, as described in AN-0978 Application Note, Component Processor Nonstandard Video Formats.<sup>13</sup>

The built-in *color-space converter* (CSC), shown in Figure 5, transforms the color space to suit user requirements (Equation 4 below, where A1... A4, B1... B4, C1... C4 are adjustable CSC parameters). YPrPb or RGB input signals can be converted to other formats using configurable matrix conversion. For instance, converting RGB to YCrCb allows chroma information (Cb, Cr) to be dropped, simplifying edge detection with a monochrome picture.

Figure 5. Single CSC channel (ADV7403).

(2)

The CSC is very useful. With an RGB or YCrCb input, color information can be simply transformed using a color-space matrix. Figure 6 shows a YUV color space that is similar to YCrCb.

PRODUCT IS NOT FRESH

Figure 6. YUV color space in product-quality evaluation can be used to detect (for example) when a product is burned or moldy. Y (luma) is constant.

As Figure 6 shows, the color (or YPrPb value), can help to detect the quality of the product, for example, whether it is burned or moldy. Color-space conversion is necessary in video processing and for interfacing to ICs that use other standards. The ADV7401/ADV7403 include an input multiplexer that enables easy switching of video sources, a useful feature when switching from a stopped conveyor belt to a working one.

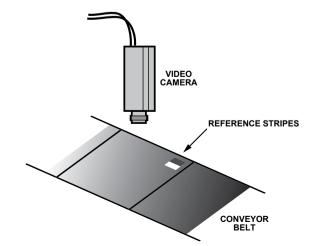

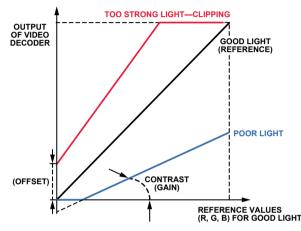

#### Example 3. Adjusting White and Color Balance for Video Inspection

Significant effort is required to develop a video system that extracts objects from a picture, as simple changes in light angle or intensity can affect the inspection results. Video engineers can use the ADV7401/ADV7403 gain and offset adjustments to adjust the brightness and contrast by adding two small reference stripes (one dark, one bright) to the conveyor belt. The offset and gain of the ADV7401/ADV7403 are adjusted to get comparable values, thus allowing the system to compensate for changes in light, color, angle, and intensity.

Figure 7. Small reference stripes are added to the visible area.

The algorithm for adjusting proper white balance<sup>14</sup> can be very simple. First, get reference RGB (or YCrCb) values for the stripes. Then, to compensate for light, simply change the offset and gain to get the same values as the reference. This algorithm can be used:

- 1. Get RGB (or YCrCb) values of the dark stripe.

- 2. Adjust offset to match desired RGB (or YCrCb) value of dark stripe.

- 3. Get RGB (or YCrCb) values of the light stripe

- 4. Adjust gain to match desired RGB (or YCrCb) value of light stripe.

- 5. To improve accuracy, repeat steps 2 and 4.

This procedure is especially useful during system development, as it provides the correct offset (brightness) and gain (contrast)—even when the light is too strong or too weak, as shown in Figure 8. The offset and gain registers are available via the  $I^2C$  bus, allowing quick adaptation.

Figure 8. The offset and gain are adjusted to compensate for changes in ambient lighting.

Colors can also be used for the reference stripes. This compensation is similar to white balance, which is widely used, but while white balance matches a human's perception, the color correction is to compensate for changes due to different lighting. Although the algorithm is similar, an additional offset causes dark colors to look unnatural. The ADV7401/ADV7403 colorspace conversion, flexible output pixel port, and offset and gain adjustment registers allow engineers to quickly develop algorithms using data that is already prepared for processing. As discussed earlier, it is important to reduce the amount of data required for video processing and to avoid advanced algorithms if they're not needed for simple video. An evaluation board for the ADV7401/ ADV7403 with an easily accessible pixel port is available to speed up the start of new design. It's a matter of simply plugging a video-capture board into the pixel port of the evaluation board and capturing the video-data (Figure 9).

Figure 9. Pixel bus on ADV7401/ADV7403 evaluation board.

# How to Apply Low-Dropout Regulators Successfully

#### By Ken Marasco

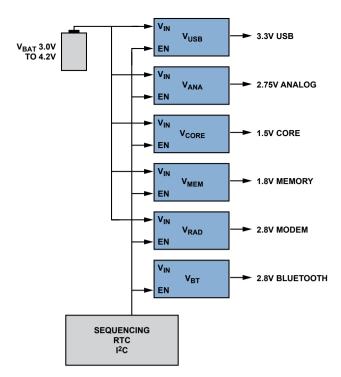

A low-dropout regulator (LDO) is capable of maintaining its specified output voltage over a wide range of load current and input voltage, down to a very small difference between input and output voltages. This difference, known as the dropout voltage or headroom requirement, can be as low as 80 mV at 2 A. The adjustable-output low-dropout regulator<sup>1</sup> first came to public attention in 1977. Nowadays, portable devices often require up to 20 low-dropout linear regulators. Many of the LDOs in today's portable devices are integrated into multifunction power-management ICs<sup>2</sup> (PMICs)—highly integrated systems with 20 or more power domains for audio, battery charging, housekeeping, lighting, communications, and other functions.

As portable systems rapidly evolve, however, the integrated PMIC cannot keep up with peripheral power requirements. Dedicated LDOs must be added in the later stages of system development to power such optional items as camera modules, Bluetooth, Wi-Fi, and other bolt-on modules. LDOs have also been used as band-aids for noise reduction, to solve voltage-regulation problems caused by electromagnetic interference (EMI) and printed-circuit board (PCB) routing, and to improve system efficiency by switching off unneeded functions.

This article reviews the basic LDO topology, explains key specifications, and shows the application of low-dropout voltage regulators in systems. Examples will be given using design characteristics of Analog Devices LDO families.<sup>3</sup>

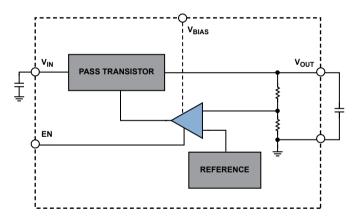

Figure 1. An LDO regulates the output voltage with a low dropout voltage (the difference between  $V_{\text{OUT}}$  and the lowest specified value of  $V_{\text{IN}}$  at the rated load current).

**Basic LDO Architecture.**<sup>4</sup> An LDO consists of a voltage reference, an error amplifier, a feedback voltage divider, and a pass transistor, as shown in Figure 1. Output current is delivered via the pass device. Its gate voltage is controlled by the error amplifier—which compares the reference voltage with the feedback voltage, amplifying the difference so as to reduce the error voltage. If the feedback voltage is lower than the reference voltage, the gate of the pass transistor is pulled lower, allowing more current to pass and increasing

the output voltage. If the feedback voltage is higher than the reference voltage, the gate of the pass transistor is pulled higher, restricting the current flow and decreasing the output voltage.

The dynamics of this closed-loop system are based on two main poles—the internal pole formed by the error amplifier/pass transistor and the external pole formed by the amplifier's output impedance and the output capacitor's equivalent series resistance (ESR). The output capacitance and its ESR affect the loop stability and the response to transient changes in load current. An ESR of 1  $\Omega$  or less is recommended to ensure stability. Also, LDOs require input and output capacitors to filter noise and control load transients. Larger values improve the transient response of the LDO but increase the startup time. Analog Devices LDOs are designed to be stable over the specified operating conditions when the specified capacitors are used.

**LDO Efficiency.** Increased efficiency is a constant demand from the design engineer. This translates into a reduction of the quiescent current  $(I_Q)$  and forward voltage drop.

$$LDO efficiency = \left(\frac{V_{OUT} I_{OUT}}{V_{IN} (I_{OUT} + I_Q)}\right) \times 100\%$$

(1)

With  $I_Q$  in the denominator, it is evident that the higher  $I_Q$ , the lower the efficiency. Today's LDOs have reasonably low  $I_Q$ , and for simplicity,  $I_Q$  can be neglected in efficiency calculations if  $I_Q$  is very small compared to the load current,  $I_{\rm OUT}$ . Then LDO efficiency is simply  $(V_{\rm OUT}/V_{\rm IN}) \times 100\%$ . Because the LDO has no way to store significant amounts of unused energy, power not delivered to the load is dissipated as heat within the LDO.

Power dissipated

$$(P_D) = (V_{IN} - V_{OUT}) \times I_{IN}$$

(2)

Providing a stable power supply voltage independent of load and line variations, changes in ambient temperature, and the passage of time, LDOs are most efficient with small differences between supply voltage and load voltage. For example, as a lithium-ion battery drops from 4.2 V (fully charged) to 3.0 V (discharged), a 2.8-V LDO connected to the battery will maintain a constant 2.8 V at the load (dropout voltage less than 200 mV), but its efficiency would increase from 67% with the fully charged battery to 93% with the discharged battery.

To improve efficiency, LDOs can be connected to an intermediate voltage rail generated by a high-efficiency switching regulator. With a 3.3-V switching regulator, for example, the LDO efficiency would be constant at 85%, and the overall system efficiency would be 81%, assuming 95% efficiency for the switching regulator.

**Circuit Features Enhance LDO Performance.** An enable input permits external control of LDO turn-on and turn-off, allowing supplies to be sequenced in proper order in multirail systems. Soft-start limits inrush current and controls output-voltage rise time during power-up. A sleep state minimizes power drain, especially useful in battery-based systems, while allowing fast turn-on. Thermal shutdown turns the LDO off if its temperature exceeds the specified value. Overcurrent protection limits the LDO's output current and power dissipation. Undervoltage lockout disables the output when the supply voltage is below the specified minimum value. Figure 2 shows a simplified typical power system for portable designs.

Figure 2. Typical power domains in a portable system.

#### **Understanding Linear Regulator Requirements**

**LDOs for Digital Loads.** Digital linear regulators, such as the ADP170 and ADP1706, are designed to support the main digital requirements of a system, usually microprocessor cores and system input/output (I/O) circuitry. LDOs for DSPs and microcontrollers have to work with good efficiency and handle high and rapidly varying currents. Newer application requirements put tremendous strain on the digital LDO because processor cores often change clock speed to save energy. The clock-speed variation, in response to software-induced loading, translates into a demanding need for LDO load-regulation capability.

The important characteristics for digital loads are line- and load regulation and transient under- and overshoot. When powering low-voltage microprocessor cores, accurate output-control is very important at all times; inadequate regulation can allow the core to latch up. The above parameters are not always featured in data sheets, and graphs of transient response may show optimistic rise and fall speed in response to transient signals. Line and load regulation is stated in two ways: percent deviation of output voltage with load change, actual V/I values, or both, at a specific load current.

To save energy, digital LDOs are designed with low  $I_Q$  to increase battery life, and portable systems have long periods of low-power operation when the software is idling. During periods of inactivity, systems will go to sleep—requiring the LDO to shut down and consume less than 1  $\mu$ A. While the LDO is in sleep mode, all of the circuits—including the band-gap reference—are switched off. When the system returns to active mode, fast turn-on times are required—during which the digital supply voltage must not overshoot excessively. Excessive overshoot can result in system latch up, sometimes requiring the removal of the battery or activation of the master reset button to correct the problem and restart the system.

**LDOs for Analog and RF Loads.** Low noise and high power supply rejection (PSR), as found in the ADP121 and ADP130, are important for LDOs used in the analog environment because analog devices are more sensitive to noise than digital devices.

Analog LDO requisites are mainly driven by the wireless interface requirements: "Do no harm to the receiver or transmitter, and create no pop or hum in the audio system." The wireless connection is highly susceptible to noise, and the receiver's effectiveness can be reduced if the noise interferes with the signal. When considering an analog linear regulator, it is important for the device to suppress noise from upstream sources and downstream loads, while not adding further noise itself.