A forum for the exchange of circuits, systems, and software for real-world signal processing

FLOATING-POINT DSP: TOPS IN MEMORY, INTERCONNECTIVITY, PERFORMANCE (page 3)

Fast, low-distortion voltage-feedback op amps offer accurate clamping (page 6) Simple techniques to protect amplifiers from input overvoltage (page 13)

Complete contents on page 3

# SHAG

2-126 < N < 1.111...x 2127

**ANALOG**DEVICES

Volume 28, Number 3, 1994

#### **Editor's Notes**

#### A BRIEF REPORT TO READERS

Two years ago, we started to ask specific feedback questions on the domestic "bingo" inquiry card. The first questionnaires were multiple-choice and rather lengthy; nevertheless a large percentage of you responded to the questions. More recently, the feedback questions have become simpler, unaided-recall types, at the bottom

of the card: "Which articles did you like? Dislike? What would you like to see?" There were a heartening number of responses, including many suggestions. Most-of the readers of 28-1 who responded liked Oli Josefsson's first article on  $\Sigma$ - $\Delta$  converters and Walt Jung's article on voltage references. Early returns from 28-2 indicate that these two are again in high-scoring territory with  $\Sigma$ - $\Delta$  Part 2 and microphone preamps.

The "would like to see" responses were relatively flat across about 20 topical classifications, but audio, video, converters, DSP, motor control, tutorials, and "more!" rose somewhat above the surrounding terrain.

When we switched to self-mailers to save postage costs and get the environmental goodies from conserving plastic or paper envelopes, there was concern about the integrity of the "book" as received. So we added a question on the condition received. Only a few—1% of cards—reported "damaged, send replacement copy"; but that would still be several hundred if it were representative of the entire mailing. However, the damaged number has to be a lot less, because most recipients of damaged copies would return the card (which is well-protected at the centerfold) requesting a fresh copy. So the assumption is that those few cards represent most of the damaged copies. If we're wrong, and there are a couple of hundred of you out there gritting your teeth at the mangling of the *Dialogue*, please let us know! There were also about 5% in "fair" condition. If you don't like to have a "fair" copy, let us know and we'll replace yours, too.

#### **GOOD LUCK, BILL**

Bill Schweber, who has been a Senior Technical Marketing Engineer at Analog Devices and Contributing Editor to *Analog Dialogue* since 1987, has recently left us to join *EDN* magazine as Analog Editor, a job for which he is—alas!—eminently suited.

During this era, besides contributing counsel and articles to this publication, Bill has worked with engineers at all levels and locations within Analog Devices, with editors of trade publications, and with a wide range of technical people elsewhere in the world to develop interesting and useful stories about designs, technologies, and

applications of Analog Devices products. His writing will not be totally new to *EDN* readers, since he has had a hand in many of their analog articles, whether authored by Analog Devices people or by *EDN* staffers.

In the course of his work, he has played a role in one of the most important aspects of professional development—encouraging, stimulating, and helping engineers to overcome their reticence to write technical articles (and to seek the rewards of authorship, especially professional visibility among their peers).

Bill's interest in writing has actually propelled his career development from systems engineer and design engineer to product manager, marketing engineer, and now, technical editor—with increasing visibility along the way. He has written numberless articles (for a current one, see page 3), and has authored three textbooks. The most recent is *Electronic Communication Systems—A complete course*, published by Prentice Hall (1991).

Bill has been fun to work with, an intellectually challenging colleague, an insatiable reader, an enthusiastic communicator, yet eminently practical, with a skepticism born of an intuitive feel for the downside (soft underbelly) of brilliant-sounding ideas (naturally, he is a "Dilbert" fan). We will miss him. Good luck, Bill!

Dan. Sheingold@analog.com

#### THE AUTHORS

Rupert Baines (page 8) provides marketing and marketing-communications support to Analog Devices's Communications Division. He has a BSEE from the University of Hull (United Kingdom) and an MBA from IESE in Barcelona (Spain), and has had experience in electronic design and international

marketing communications. He has authored articles for the U.K. trade press on op amps, DSP, and RISC  $\mu Ps$ .

Joe Buxton (pp. 13-16), a Senior Product Marketing Engineer at Analog Devices, Santa Clara, has worked extensively on the development of SPICE op amp models. He writes application notes and articles for publication and is currently involved with business development and strategic marketing for linear products. In 1988, Joe received a

BSEE from the University of California, Berkeley. In his leisure time, he enjoys bicycling, hiking, skiing, and listening to music.

(Biographies of **Steve Cox** (p.4) and **Doug Garde** (p.5) will appear in the next issue.

**Cover:** The cover illustration was designed and executed by **Shelley Miles**, of *Design Encounters*, Hingham MA.

#### Analog Dialogue

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Published by Analog Devices, Inc. and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and DSP circuits and systems. Correpondence is welcome and should be addressed to Editor, Analog Dialogue, at the above address. Analog Devices, Inc., has representatives, sales offices, and distributors throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-937-1428, 1-800-262-5643 (U.S.A. only) or fax 617-821-4273.

#### Floating-Point DSP Leads in Memory, Interconnectivity, Performance

### For single- and multiple processor applications, SHARC also provides upward compatibility.

by Bill Schweber

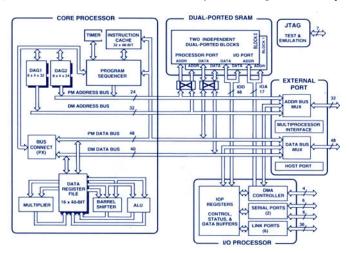

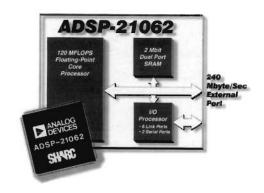

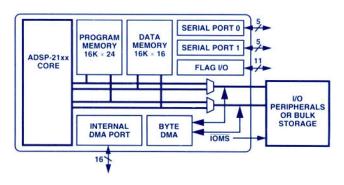

The ADSP-21060 and ADSP-21062 are the industry's first DSPs in the class of Super Harvard ARchitecture Computer (SHARC<sup>TM</sup>).\* They integrate on a single chip: the industry's fastest general-purpose floating-point core, based on the ADSP-21020 (Analog Dialogue 25-2, 1991); a dual-ported 4- or 2-megabit SRAM; widebandwidth communication ports; and a sophisticated DMA (direct memory-access) controller—plus a crossbar switch to interconnect them (see block diagram below). Applications for SHARCs, in various configurations, are shown in the Table.

#### SHARC APPLICATIONS

|                      | 2-Mbit memory<br>ADSP-21062                                                                 | 4-Mbit memory<br>ADSP-21060                                          |

|----------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| SINGLE<br>PROCESSOR  | •Low-cost color imaging<br>(printers & scanners)<br>•Low-end graphics<br>(PC plug-in cards) | •Medical imaging                                                     |

| MULTI-<br>PROCESSING | Call processing Digital cellular base stations Data acquisition Instrumentation             | •Accelerator boards •Graphics boards •Image processing •Radar •Sonar |

Featuring a processing speed of 40 MIPS (million instructions per second) and 120 MFLOPS (million floating-point operations per second), the ADSP-21060 SHARC combines the industry's highest-performance 32-bit floating-point DSP core—based on the ADSP-21020—with the largest on-chip memory of any processor—RISC, CISC, or DSP. Peripherals integrated on-chip

<sup>\*</sup>For technical data, use the reply card. Circle 1

for high-speed I/O processing include: 10 simultaneous DMA channels; highly efficient host system/interconnect bus interfaces; external communication ports (6 link ports, 2 serial ports); and scalable multi-processing hooks. The ADSP-21060 and other processors in the SHARC family offer designers a single chip with clear advantages in performance, bandwidth, size and power over traditional DSPs and processors—and at a much lower system cost than designs based on standard DSP and embedded RISC-based chipsets.

Specific features of the ADSP-2060 SHARC include:

- 32-bit single-precision (or 40-bit extended precision) IEEE floating-point DSP core—with 3 independent, parallel computational units: ALU, multiplier, and shifter—featuring 40-MIPS performance, with 120 MFLOPS (millions of floating-point operations per second) peak, 80 MFLOPS sustained.

- On-chip, configurable memory banks—dual-ported 4-megabit internal SRAM—with fast, independent local memory access to DSP core, DMA controller, and I/O processor. The two banks support dual-operand fetch. (The ADSP-21062, with an identical processor, has 2 megabits of SRAM).

- I/O processor with DMA controller, memory mapper, and communications. Ten DMA channels, used with the dual-ported SRAM, handle background transfers between internal and external memory, peripherals, host, serial/link ports—without affecting performance of the DSP core. Two serial ports and 6 point-to-point links facilitate glueless multi-processor systems.

- Interface to off-chip memory, supporting programmable wait states and page-mode DRAM.

#### IN THIS ISSUE

Volume 28, Number 3, 1994, 24 Pages

| Editor's Notes                                                                |

|-------------------------------------------------------------------------------|

| Floating-point DSP leads in memory, interconnectivity, performance (SHARC) 3  |

| Fast, low-distortion V-feedback op amps with clamping (AD9631/2,AD8036/7) . 6 |

| New high-speed A/D converters for communications (AD9022/23/26/27) 8          |

| New 8-bit, 16-channel voltage-output D/A converter (AD8600) 9                 |

| 16-bit DAC for comms, imaging & displays updates (a 30 MHz (AD768) 10         |

| 12-bit dual DAC: Serial, single-supply, saves space in SO-14 (AD8522) 11      |

| 16-bit fixed point DSP: 80 Kbytes of RAM reduce system cost (ADSP-2181) 12    |

| Simple techniques protect amplifiers from high-voltage inputs                 |

| New-Product Briefs:                                                           |

| What's new in amplifiers: VCAs, transimpedance, isolation, upower 17          |

| What's new in interfaces: RS-232, RGB-to-NTSC/PAL                             |

| What's new in A/D and D/A converters                                          |

| What's new in switches, voltage references, motion control 20                 |

| What's new in digital audio: ASRC, personal sound, codec 21                   |

| Worth Reading                                                                 |

| Potpourri                                                                     |

- System bus crossbar, providing flexible interconnections between 16/32-bit host CPU, DMA device controller, external memory, peripherals, optional boot EPROM.

- On-chip hooks for "glueless" scalable parallel-bus cluster multiprocessing with up to six ADSP-2106x's for very high speed number crunching (see sidebar "Cluster multiprocessing").

The SHARC, like all Analog Devices DSPs, uses a "Harvard" architecture with two separately accessible address spaces (see Analog Dialogue 20-1 (1986) and 24-1 (1990). In its simplest configuration, one memory space is used for data, the other for program instructions. In contrast, the more familiar architecture used in conventional microprocessors (proposed by John von Neumann in 1948) uses a single stored program area, shared by both data and program. The hardware and interconnections for the von Neumann architecture are simpler, but its information bottleneck makes it less efficient at executing the highly repetitive algorithms of signal processing than the Harvard approach.

#### **SHARC TOOLS**

The tool set features the industry's first Numerical C implementation on a DSP processor. The ADSP-21000 Family G21K C Compiler supports Numerical C for vector and matrix operations, used extensively in DSP algorithms; this provides greater code efficiency and a more natural syntax for developing DSP applications, using fewer lines of code. Analog Devices' Numerical C has been adopted by the Free Software Foundation in version 2.4 of the standard GNU C Compiler.

The Simulator reflects all core changes of the ADSP-2106x processor, including the interrupt table, instruction set, register set and memory configuration. The Simulator also supports windowed access to DMA and SPORT (serial port) control and data registers, including simulated file I/O to serial ports. In addition, the Simulator supports DMA operation to/from an external device and DMA operation to/from external memory. External devices are supported using file I/O. Memory access may be tracked in two ways: either by a "memory window", displaying a specified range of memory, or by tracking the "data fetch" address. In addition, the ADSP-2106x Simulator and EZ-ICE Emulator both feature a graphical user interface with the same intuitive menu layout. All are integrated with the CBUG™ C Source-Level Debugger.

The ADSP-2106x EZ-ICE™ In-Circuit Emulator, with its easy-to-use Microsoft Windows® interface, allows non-intrusive access to the internal processor registers through a JTAG serial boundary-scan interface. Consisting of a PC plug-in card and a small attached probe, it supports full-speed operation, multiprocessor debugging, up to 30 software breakpoints, nine hardware break ranges, single-step execution, register Modify and Read, and program- and data memory upload/download.

The ADSP-21062 EZ-LAB is a PC plug-in development system that includes an ADSP-21062, with connectors for at least four more. It has a connector for analog front end cards and includes an AD1847 sound-codec card. Software is included for program debugging. The ADSP2106x-EZ-KIT package includes the EZ-LAB plus development software (assembler, linker, simulator, PROM splitter, C compiler with Numerical C support, C source-level debugger, and C runtime library). EZ-LAB is priced at \$1,495 and EZ-KIT at \$1,995.

Both SHARCs are housed in 240-lead PQFP packages with enhanced thermal conduction. The 2-megabit ADSP-21062 for

5-V supply is sampling now, with full production by March 1995; the 4-megabit ADSP-21060 will be sampling in March 1995 and in full production by June. They are priced at \$296 for the ADSP-21060 and \$196 for the ADSP-21062 (1000s).

#### CLUSTER MULTIPROCESSING DSP Communication through Shared On-Chip Memory

by Steve Cox

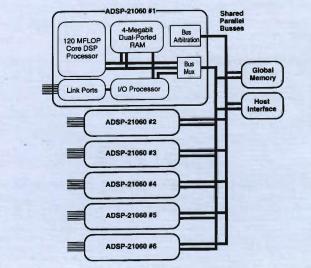

Multiprocessor systems typically use two schemes to communicate between processor nodes. One approach uses dedicated point-to-point communication channels. In the other, nodes communicate through a single shared global memory via a parallel bus. The ADSP-2106x SHARC supports both, implementing point-to-point communication through its six Link Ports, and realizing an enhanced version of shared parallel bus communication called *cluster multiprocessing*.

Cluster multiprocessing is embodied with up to six nodes on a parallel bus that allows internode access to on-chip memory, to a shared global memory, and to a host processor interface. The cluster configuration allows the ADSP-2106x to have a very fast node-to-node data-transfer rate. It also allows for a simple, efficient communication model. For instance, all the required setup for a DMA transfer can be done by a node on one side of the data transfer. The other node is not interrupted until the data transfer is complete. Each processor can directly read from and write to another processor's internal memory. This distributed-memory multiprocessing system also simplifies the software communication model.

The figure shows a cluster of such DSPs. Up to six processors and a host can vie for the bus without any additional external logic. Bus requests are made implicitly whenever a processor accesses external address space. Because each processor monitors all bus requests and applies the same priority logic to the requests, each can independently determine who will be the next bus master. The on-chip arbitration logic allows transitions in bus ownership to use only one cycle of overhead. Once a processor gains ownership of the bus, it has access not only to external memory but also to all the other processors' internal memory and I/O registers. Thus, a processor can directly transfer data with another processor or set up a DMA channel to transfer the data. Memory-to-memory transfers can occur at a 40-MHz, 240-megabyte-per-second rate.

To identify the address space of each processor within the unified address space of the cluster, each processor has its own unique ID. The I/O registers, internal memory and external memory are all part of the unified address space.

The DSP's internal memory is designed to complement the I/O needs of multiprocessor systems. The on-chip dual-ported RAM allows full-speed interprocessor transfers; at the same time, it supports dual accesses by the floating-point DSP core. No extra cycles are ever required from the DSP core; thus the processor's full 40-MIPS, 120-MFLOPS performance is easily achieved.

A bottleneck may exist within a cluster, because only two nodes can communicate on the shared bus each cycle. Other nodes are held off until the bus is released. Since the ADSP-2106x also supports Link Port communication within a cluster, this bottleneck can be eliminated, because all 6 ports can communicate simultaneously. However, individual transfers occur at 40 Mbyte/s; a lower rate than that allowed on the parallel bus. Since the Link Port data path is narrower than the node's native word size, the transfer of each word requires multiple clock cycles. Link Ports may also require more software overhead and complexity because they must be set up on both sides of the channel before they are used.

#### ON-CHIP SRAM DESIGN CONSIDERATIONS Designer challenges and user opportunities in a DSP with on-chip mega-memory

By Doug Garde

Integration of a processor with substantial amounts of memory allows a chip designer to use SRAM in new and creative ways. No longer is the memory a non-optimal fixed function over which the designer has no control; instead, one can take advantage of many synergies that exist in defining its operation and interfacing it with the processor. To understand these differences, we need to review some issues associated with interfacing to external SRAM.

Considerations for interfacing to external SRAM: In high speed systems (i.e., 25-ns cycle time or less), the most significant challenge in accessing external memory is meeting the time budgets. In each cycle, the processor must drive the address off-chip, and then wait for the external memory to access the data and drive it back to the processor. In addition, the processor must provide accurately timed read and write strobes to the memory. Furthermore, the data and address buses typically have 50 to 100 pF of capacitive loading, which adds to the bus charging time.

Unless wait states are used, expensive, fast-access memories are needed. In a 25-ns cycle for instance, the external memory might typically require a 10-ns read-access time (17 ns in SHARC). These requirements make the SRAM very expensive and power-consuming.

In addition, because of the fast transition times required on each signal, ringing and large ground and power supply transients occur, producing a large amount of noise that reduces signal integrity. Considerable design skill and expensive printed circuit boards are needed to overcome these noise problems. Power dissipation also increases, due to the large number of address and data lines being charged and discharged. Package pin-count usually increases, because two sets of buses (for two external memories) are needed per cycle in Harvard and Super-Harvard architectures.

The principal benefits of off-chip memory are that memory size can be customized to the application, and the processor chip—without memory real-estate—is smaller and cheaper.

Considerations for the Design of Internal memory: The designer of an on-chip memory can customize both the memory and the interface to achieve performance and functionality that could not be attained with external off-the-shelf memory. First, the interface between the processor and memory can be simplified because both are run by the same clock. Synchronous, or clocked, memory can operate faster than asynchronous or unclocked memory, but most commercial SRAMs are

asynchronous because of the way they have evolved in the commercial marketplace. Since they are standardized, their prices are lower than for speciality SRAMs.

With the address and data buses internal, far less time is wasted driving large off-chip drivers and external buses; this allows more of the time budget to be available for the memory access. Performance is further improved by the use of address and data latches at the memory and of clocked sense amplifiers (no address-transition detection circuits are needed). Since both memory and processor are part of the same silicon, the process and temperature variations track, eliminating the need for excessive best-case/worst-case tolerances.

In fact, the memory access requirements are eased so much that two accesses per cycle are possible on-chip, whereas even one access is a challenge for off-chip memory. Dual internal accesses per cycle are used in the ADSP-21060 SHARC family. This produces improved processor performance, or alternatively allows an I/O operation, such as DMA, that is independent of the processor access.

On-chip memory also makes it easier for many buses to be multiplexed for flexible access to multiple memory blocks. For example, each of two memory blocks could be easily accessed by either the program sequencer, either one of two address generators, or an I/O processor. This flexibility means that only one external memory is needed to supply data or programs, and therefore only one set of external buses is needed. Data and programs can be transferred as a background operation using an internal DMA controller. Furthermore, because this is usually not time-critical, the external memory, can often be inexpensive page-mode DRAM with wait states.

Yet another benefit of on-chip memory is the ease of designing a memory that allows access to either larger or smaller memory words in a single block. For example, on the ADSP-21060 SHARC, a normal data word is 32 bits, a short word is 16 bits and a long word for instruction or extended precision is 48 bits. All these word types can be intermixed in a single block of on-chip memory by designing columns to be 16 bits wide. By decoding the column addresses in groups of 1, 2 or 3 columns, corresponding to 16, 32 and 48 bits, the memory space can include each data type while still providing full memory utilization. This allows the use of internal memory to be customized to fit the application.

#### Fast, Low-Distortion V-Feedback Op Amps Offer Optional Accurate Clamping

### With 175/180-MHz large-signal BW, AD9631/9632 have ultralow distortion; AD8036/8037 have voltage-variable clamped output

The AD9631, AD9632, AD8036, and AD8037\* voltage-feedback op amps, manufactured on the Analog Devices XFCB (eXtra-Fast Complementary Bipolar) process, provide outstanding performance at low cost. The **AD9631** & **AD8036** are unity-gain stable ( $G \ge +1$ ); and the **AD9632** & **AD8037** excel for applications with voltage gain magnitudes  $\ge +2$  V/V or -1 V/V. Performance of both families is fairly similar, except that the **AD8036** & **AD8037** have an additional pair of voltage inputs,  $V_H$  and  $V_L$ , that provide simple, fast, flat, accurate clamps on the output for input voltages  $\ge V_H$  or  $\le V_L$ , when operated in the noninverting connection.

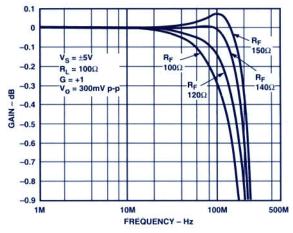

When connected for gain of +1, the AD9631 has small-signal bandwidth (-3-dB) of 320 MHz (220 minimum) and large-signal (4 V p-p) BW of 175 MHz (150 min). Corresponding BWs for the AD9632, with a gain of +2, are 250 (180) MHz and 180 (155) MHz. All of these devices typically have flat response (<0.1 dB) to 130 MHz (Figure 1). Performance characteristics for all four types are compared in the table. They are available for the -40 to +85°C temperature range, housed in SOIC and miniDIP packages. Prices start at \$4.12 in 1000s.

#### Typical (min/max) performance characteristics

$[\pm V_S = \pm 5 \text{ V}, R_L = 100 \Omega, \text{ unless noted otherwise}]$

|                                               | <b>AD9631</b> [G=+1] | AD9632<br> G=+2] | AD8036<br>[G=+1] | AD8037<br>[G=+2] |

|-----------------------------------------------|----------------------|------------------|------------------|------------------|

| Bandwidth, MHz, small signal                  | 320(220)             | 250(180)         | 240(150)         | 270(200)         |

| Large signal, [unclamped]                     | 175(150)             | 180(155)         | 195(160)         | 190(160)         |

| 0.1-dB flatness                               | 130                  | 130              | 130              | 130              |

| Slew rate, V/µs, average ±, 4-V step          | 1300(1000)           | 1500(1200)       | 1200(900)        | 1500(1100)       |

| Settling time to 0.1%, ns, 2-V step           | 11                   | 11               | 10               | 10               |

| Distortion, dBc, 2nd har. $R_L$ =500 $\Omega$ | -72(-65)             | -72(-65)         | -66(-59)         | -72(-65)         |

| Voltage noise, nV/√Hz, 1-200MHz               | 7 .                  | 4.3              | 6.7              | 4.5              |

| Differential gain error,%, 3.58 MHz           | 0.03(0.06)           | 0.02(0.04)       | 0.05(0.09)       | 0.02(0.04)       |

| Differential phase error, °,3.58 MHz          | 0.02(0.04)           | 0.02(0.04)       | 0.02(0.04)       | 0.02(0.04)       |

| Phase nonlinearity,°,DC-100 MHz               | 1.1                  | 1.1              | 1.1              | 1.1              |

| Voltage drift, μV/°C, -40 to +85°C            | ±10                  | ±10              | ±10              | ±10              |

| Bias current, µA, -40 to +85°C                | 2(7)                 | 2(7)             | 4(10)            | 2(7)             |

| Output voltage range, V, R <sub>L</sub> =150Ω | ±3.9(3.2)            | ±3.9(3.2)        | ±3.9(3.2)        | $\pm 3.9(3.2)$   |

| Output current, mA                            | 70                   | 70               | 70               | 70               |

| Supply voltage range, V                       | ±3-±6                | ±3-±6            | ±3-±6            | ±3-±6            |

| Quiescent supply current, mA                  | 17(18)               | 16(17)           | 20.5(21.5)       | 18.5(19.5)       |

| Clamp voltage range, V [VH or VL]             |                      |                  | ±3.9(3.3)        | ±3.9(3.3)        |

| Clamp accuracy, mV (2× overdrive)             |                      |                  | ±3(5)            | ±3(5)            |

| Clamp input bandwidth, MHz [-3 dB             | ]                    |                  | 240(100)         | 240(100)         |

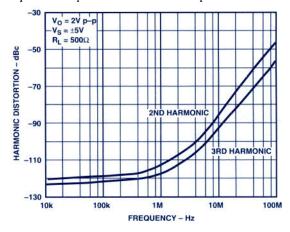

As Figure 2 shows, response is exceptionally clean, with SFDR† well below -110 dBc at frequencies up to 1 MHz, increasing to only -95 dBc at 5 MHz, and a maximum of -65 dB 2nd harmonic

Figure 1. AD9631AN small-signal 0.1-dB flatness. (For AD9631AR, add 20  $\Omega$  to  $R_{\text{F}}$ )

at 20 MHz (AD9631 with 500- $\Omega$  load). Distortion figures are comparable for the AD9632, taking into account the doubled gain: 2nd harmonic distortion is only –95 dB at 1 MHz and a guaranteed maximum of –65 dBc at 20 MHz. The AD8036 and AD8037 have similar performance, –100 and –95 dBc typical at 1 MHz, and –59/–65 dBc guaranteed for AD8036/37 at 20 MHz.

With their voltage-feedback architecture, these wideband, low-distortion, fast-settling operational amplifiers meet the requirements of many applications which were typically in the province of current-feedback types. They bring the improved predictability of a classical op-amp architecture to buffer circuits for A/D converters, video line drivers, and active filters. Many types of filter circuits benefit by the flexibility obtainable with the balanced high-impedance input circuits of these amplifiers.

Figure 2. AD9631 harmonic distortion vs. frequency, G = +1 V/V,  $R_L$  = 500  $\Omega$ .

<sup>†</sup>Spurious-Free Dynamic Range, the dB difference between the rms amplitude of a single-tone signal and the largest spurious peak (usually the 2nd harmonic) within the bandwidth of interest.

<sup>\*</sup>Use the reply card for technical data. Circle 2

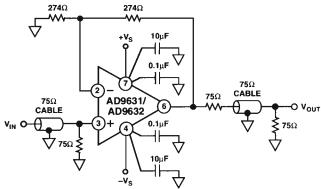

Figure 3 shows a circuit for applying the AD9631/AD9632 as a line driver for a back-terminated  $75-\Omega$  video cable. Many details that must be considered in the use of op amps in designing line drivers in general, and video line drivers in particular, can be found in *Analog Dialogue* 26-2, "Op amps in line-driver and receiver circuits", by Walt Jung.

Figure 3. AD9631/AD9632 as video line driver.

#### **ABOUT CLAMP AMPLIFIERS**

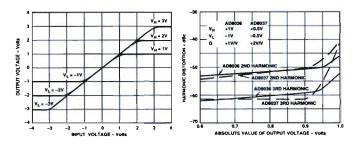

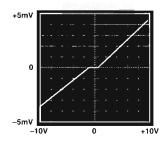

A clamp amplifier is a limiting or bounding circuit. For input voltages between two levels,  $V_H$  and  $V_L$ , the output is proportional to the input. For inputs greater than  $V_H$  or less than  $V_L$ , the output ideally remains constant, bounded at  $V_{CH}$  or  $V_{CL}$  ( $V_H$  or  $V_L \times$  the amplifier gain,  $A_V$ ), irrespective of the input, as shown in Figure 4a. The threshold voltages,  $V_H$  and  $V_L$ , may be fixed or variable. If the amplifier can handle positive and negative input/output voltages,  $V_H$  and  $V_L$  can have any plus or minus values within the specified range, as long as  $V_H > V_L$ .

Clamp amplifiers may clamp the output voltage (OCL) or the input voltage (ICL). The AD8036/37 use CLAMPIN®, a highly precise ICL design: comparators quickly and accurately steer to the actual plus input of the amplifier the lesser of  $V_{\rm IN}$  and  $V_{\rm H}$ , and the greater of  $V_{\rm IN}$  and  $V_{\rm L}$ . The amplifier gain amplifies  $V^+$ .

When controlled by external voltages, a clamp amplifier circuit is characterized by linearity (low distortion) in the unclamped range, flatness in the clamped range, accuracy of setting of the clamp voltages, and sharpness of the transition. Dynamically, when driven rapidly (i.e., stepped) into the clamped zone, it must have low overshoot and quick recovery. If  $V_H$  and  $V_L$  are variable control voltages, bandwidth must be adequate to handle them.

The AD8036 and AD8037 perform the clamp function with better performance than any available IC alternatives. Specifications include a clamp-voltage range of  $\pm 3.9 \text{ V}$  (3.3 V min), clamp ac-

Figure 4. (a) Clamp amplifier performance, for representative clamp values,  $V_H$  and  $V_L$ , showing flatness and small "knee" area. (b) Harmonic distortion as output amplitude approaches clamp voltage.  $V_0=2$  Vp-p,  $R_L=100~\Omega$ , f=20 MHz

curacy/flatness to within  $\pm 3$  mV (5 mV max), a "knee" region of 100 mV. Maximum overshoot is 5% max in response to a 2× step overdrive, with recovery within 1.5 ns. The clamp input responds with a -3-dB bandwidth of 240 MHz, a useful feature when the clamp inputs are used to modulate an r-f signal.

To demonstrate how "clean" the clipping is, Figure 4b plots 2nd-and 3rd-harmonic distortion as a function of sine-wave amplitude as it approaches a  $\pm 1$ -V output clamp setting. The approach to the clamped region contributes no additional distortion for a >90% swing; and even at the clamp threshold, the worst distortion seen is only 1% (-40 dB).

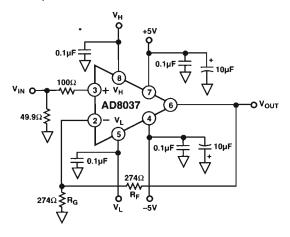

**Applications:** Figure 5 shows a basic circuit for clamping with gain; here, the gain is 2 V/V, and the resulting output clamp levels are  $2 \text{ V}_H$  and  $2 \text{ V}_L$ . In this configuration, with the  $0.1\text{-}\mu\text{F}$  bypass capacitors,  $\text{V}_H$  and  $\text{V}_L$  are assumed to be fixed or slowly varying. The clamp-level signal sources must be able to supply dc bias currents of  $70 \mu\text{A}$  max without error.

Figure 5. Basic clamp amplifier circuit for gain of +2 V/V.

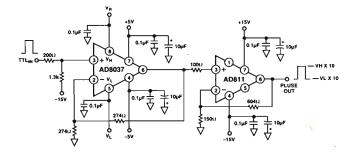

Clamp amplifiers are useful as protective buffers for A/D inputs, as programmable flat-pulse-forming amplifiers, and as amplitude modulators. Because  $V_H$  and  $V_L$  clip in the input stage and have input bandwidths comparable to the signal inputs, they can also be used in simple circuitry to generate the positive or negative absolute value of input signals (i.e., full-wave rectify them). Figure 6 shows a TTL-based programmable pulse generator.

These amplifiers were designed by Roy Gosser at our facility in Greensboro, NC.

Figure 6. Programmable flat- pulse generator application with TTL input and up to 24 V p-p output with 2500-V/ $\mu$ s slew rate.

# New High-Speed A/D Converters for Communications

### 12-Bit AD9022/23/26/27 offer sampling at up to 31 MSPS with SFDRs up to 76 dB

by Rupert Baines

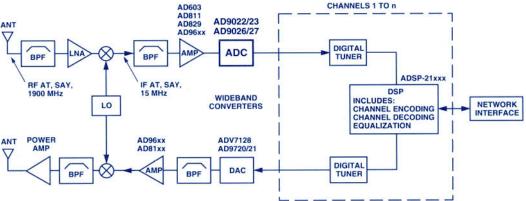

Four new 12-bit analog-to-digital converters, the TTL-compatible AD9022 and AD9026 and the ECL-compatible AD9023 and AD9027, combine high sampling rates (as high as 31 MSPS) with extremely low distortion (SFDR as high as 80 dB). They are intended for applications in wideband communications systems or instrumentation where high-frequency signals must be accurately captured and digitized.

Typical applications for these devices include systems for detecting high-frequency signals in the midst of a welter of other signals. Analog input-bandwidths as high as 200 MHz (extending well beyond Nyquist) mean that signals can be captured using undersampling. Instead of a local oscillator and mixer, the converter's sample rate is used to alias a signal down to baseband. If such an application is truly to detect weak signals, a wide dynamic range is required; this implies high resolution with low distortion and noise.

The AD9026 and AD9027\* are optimized for communications applications, while the AD9022\* and AD9023\* are intended for applications where low distortion at low cost is more important than getting the very highest speed. With sampling rates of 20 MSPS they can capture a 9.6-MHz bandwidth with SFDRs of 74 and 72 dB.

The 31-MSPS specifications of the AD9026B and AD9027B are significant because the US cellular communications industry (both analog and the TDMA digital standard) uses a 30-kHz channel; a 31-MSPS sampling rate allows 1024× oversampling (30.72 MSPS = 10-24 × 30 kHz). A traditional cellular system has a narrowband receiver for each channel—up to 60 receivers in a typical base station. In contrast, it is possible to use a wideband receiver based on the AD9027 to digitize the entire cellular bandwidth (12.5 MHz), with resolution high enough for DSP techniques to be be used to extract any of the desired channels

digitally. A single wideband receiver can thus replace as many as 60 narrowband front ends (see Figure 1). Because the tuning is done in software (by the DSP), it is possible to change between standards (e.g., from AMPS to TDMA) merely by loading a new program.

With the ability to digitize a 15-MHz portion of the spectrum directly, the AD9026/27 make possible a range of new communications products in which RF and IF signals will be handled digitally in much the same way that audio and video signals are today. Besides cellular infrastructure, the first applications are likely to be advanced instrumentation, such as spectrum analyzers, ultrasonic imaging devices and communications test-sets.

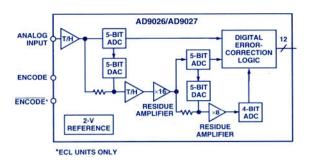

#### INTERNAL STRUCTURE

The devices use a three-pass subranging architecture (Figure 2). Two track-and-hold amplifiers (T/H), three flash ADCs, two DACs and two residue amplifiers produce a 14-bit digital word that, digitally error-corrected, results in a 12-bit-accurate output. The input T/H amplifier is the most critical block, because it must sample a  $\pm 1.024$ -V signal to better than 12-bit accuracy; errors introduced at this stage can't be corrected later.

Unlike many wideband ADCs, the dc performance of these devices needs no apology. No-missing-code operation is guaranteed, while differential & integral non-linearity are a maximum of 1 and 3 bits, respectively. All three specifications are guaranteed over

Figure 2. Block diagram of 3-pass subranging architecture.

the entire operating temperature range of -25°C to +85°C (case temperature). The specified power-supply is +5.0 V, -5.2 V, and dissipations are 1.4-1.6 W. All four types are available in 28-pin ceramic DIPs; and the AD9022 and AD9023 are also available for surface mount. Prices (1000s) start at \$140 for the AD9022/23 and \$238 for the AD9027/28.

These converters were designed by Frank Murden and Dana Zipperer, of ADI's Communications Division, in Greensboro, NC.

Figure 1. Cellular infrastructure system block diagram.

<sup>\*</sup>Use the reply card for technical data. Circle 3

## New 8-Bit, 16-Channel Voltage-Output D/A Converters

### AD8600 has 16 multiplying DACs with double buffering and readback, $\pm 1\text{-LSB}$ total unadjusted error, and 2- $\mu s$ settling time

The AD8600\* combines 16 high-performance multiplying, 8-bit D/A converters in a single monolithic IC. A parallel-input device, with double buffering, it can accept data clocked in at speeds up to 12.5 MHz, a combination of speed and high channel-count unmatched in the industry. It is specified to operate on a single +5-volt supply or dual  $\pm 5$ -V supplies, has a total unadjusted error within  $\pm 1$  LSB, settles to within  $\pm 1$  LSB of final value within 2  $\mu$ s of reference voltage changes or data updates, and consumes only 175 mW max in single-supply applications.

With its ability to furnish up to 16 independent voltages simultaneously, it is useful in multichannel instrumentation and test systems requiring speed and 8-bit accuracy. Typical applications include multichannel instrumentation systems, automatic test equipment, phased-array ultrasound gain adjustment, setting threshold levels for 16-channel logic analyzers, and PC-compatible programmable data-acquisition and control cards.

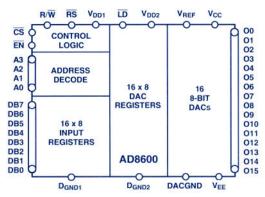

Figure 1 shows the device's functional organization and connections. An 8-bit parallel data input, four address pins, and  $\overline{CS}$ ,  $\overline{LD}$ ,  $\overline{EN}$ ,  $R/\overline{W}$ , and  $\overline{RS}$  provide the digital interface. The DACs all share a common external reference voltage, which sets the full-scale output. The device is housed in a 44-lead PLCC and is specified for operation from -40 to +85°C. The AD8600AP is priced at \$25.28 in 1000s.

Figure 1. Functional block diagram.

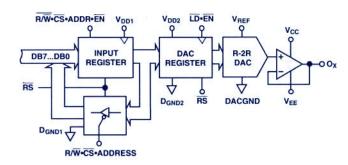

The signal flow in each DAC channel, including readback, is shown in Figure 2. Data appearing on the 8-bit parallel bus is clocked into each input register, then all DAC registers are updated simultaneously, producing buffered output voltages that can range from 0 to  $(V_{CC} - 1 \ V)$ . At system power-up, or during fault recovery, the reset  $(\overline{RS})$  pin forces all DAC registers into the zero state, which places 0 V at all DAC outputs.

Figure 2. Equivalent DAC channel, showing double-buffering of the digital inputs, digital readback, and output voltage buffering.

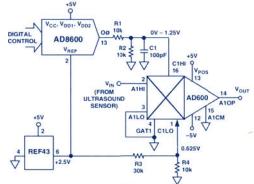

Application: Time-dependent variable-gain amplifier. The AD8600 is useful in phased arrays for ultrasound imaging as a gain-control signal for an exponential amplifier, such as the AD600 X-AMP® (Analog Dialogue 26-2, 1992). X-AMPs are variable-gain amplifiers for which equal increments of control voltage increase the signal gain in equal dB steps. For example, the control voltage increment corresponding to a 6-dB step increase results in a doubling of voltage gain.

In medical ultrasound, bursts of ultrasound are applied to the subject, then a set of transducers picks up the reflected sounds at various locations. The timing and strength of echoes from structures within the subject produce a picture of the internal situation.

However, because the ultrasound energy is absorbed as well as reflected, the deeper the source of the echo, the smaller the signal that is returned. To resolve far objects accurately, the gain on the returned signal must be greater than for near objects. Since the propagation speed and absorptivity of the medium are knowable, the rate of exponential attenuation can be predicted. This information can be used correspondingly to increase the gain of an X-AMP associated with a given transducer so as to make possible accurate estimates of the strength of the reflected signal, irrespective of depth.

D/A converters can be used to apply the required programmed control voltages to the X-AMP associated with each transducer. The AD8600 is especially useful in this application because it can be used compactly and at low cost to control the gains of an array of transducer channels with the required speed and accuracy. Figure 3 shows a scheme of digital exponential gain adjustment applied to one channel of an array.

The AD8600 was designed by Derek Bowers and Carol Flores at our Santa Clara, CA facility.

Figure 3. Ultrasound amplifier with digitally controlled variable gain.

<sup>\*</sup>Use the reply card for technical data. Circle 4

# Low-Cost 16-Bit DAC for Communications, Imaging, & Displays Updates at 30 MHz

### Current-output AD768 has on-chip reference, low quantization noise, 14-bit linearity, 83-dBc SFDR

The AD768\*, a wideband high-resolution D/A converter, is designed to fill the performance requirements of arbitrary waveform generation in direct digital synthesis (DDS), waveform reconstruction in communications systems, and wide-range, high-speed A/D converter design.

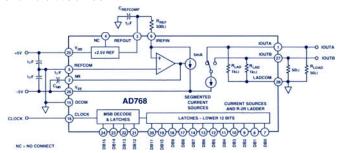

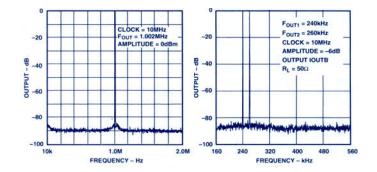

Supporting update rates up to 40 MSPS, the AD768 offers 16-bit resolution with 1/2-LSB differential and 1-LSB integral nonlinearity at the 14-bit level, and low 35 pV-s glitch. On-chip features include edge-triggered CMOS latches for the digital interface and a 2.5-V reference (an external reference may be used). Complementary outputs can be used individually or differentially, to provide a 20-mA-full-scale current that settles to 0.025% within 25 ns. AC specified, the part will provide 1-MHz output with 83-dBc spurious-free dynamic range (SFDR).

The AD768 operates on  $\pm 5\text{-V}$  supplies, typically consuming 465 mW of power. It is available in a 28-pin SOIC package and is specified for operation from -40 to +85°C. An evaluation board is available. Prices are \$24.95 for the AD768AR in 100s and \$150 for an evaluation board.

Figure 1. Functional block diagram of the AD768 and basic hookup.

#### A TYPICAL APPLICATION

Multitone transmitters (for ADSL): Communication applications frequently require aspects of component performance that differ significantly from the simple single-tone signals used in typical tests. This is especially true for spread-spectrum and frequency-division-multiplexed (FDM) signals, where information is contained in a number of small signal components spread across the frequency band. Such applications require a combination of wide dynamic range, good fine-scale linearity, and low intermodulation distortion (Figure 2). Full-scale SNR and THD performance alone may not reliably indicate how a device will perform in multitone applications.

\*Use the reply card for technical data. Circle 5

Figure 2. SFDR and 2-tone intermodulation distortion with 10-MHz clock:

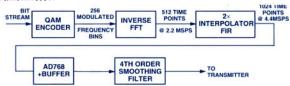

The discrete multitone (DMT) asymmetrical digital subscriber line (ADSL) communication system standard, currently under consideration by ANSI, is a case in point. Figure 3 is a block diagram of a transmitter function. A set of discrete tones in the frequency domain are quadrature amplitude-modulated (QAM) digitally, and a 512-point inverse FFT transforms them into a time-domain signal at 2.2 MSPS. An FIR interpolation filter upsamples—in this case, to 4.4 MSPS, and a D/A converter (the AD768) converts to analog; the signal is smoothed and goes on to the transmitter.

Figure 3. Typical discrete multitone ADSL Transmit chain.

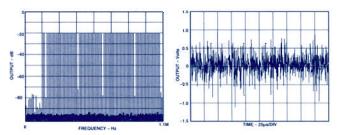

Figure 4 shows a frequency-domain representation of a test vector run through the system and the corresponding time-domain representation (which looks a lot like noise). The signal-to-noise-and-distortion (SINAD) ratio of each 4-kHz component is a function of noise (wideband and quantization) and distortion (simple harmonic and intermodulation) in the DAC and filter. The AD768's combination of 16-bit dynamic range and 14-bit linearity provides excellent performance for the DMT signal. The tables below show the signal-to-noise ratio obtained at the output of the filter for various frequency bins in the ADSL application.

| Frequency | SNR     | Frequency        | THD     |

|-----------|---------|------------------|---------|

| 151 kHz   | 63.5 dB | 160 kHz          | -60 dBc |

| 349 kHz   | 65 dB   | 418 k <b>H</b> z | -53 dBc |

| 500 kHz   | 64.8 dB | 640 kHz          | −57 dBc |

| 1 MHz     | 61.9 dB | 893 kHz          | −57 dBc |

The AD768 was designed by Doug Mercer, of ADI's Standard Linear Products Division, at our Wilmington, MA facility.

Figure 4. Output spectrum of ADSL test vector, and timedomain output signal.

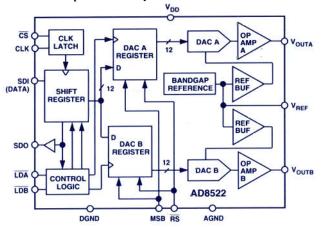

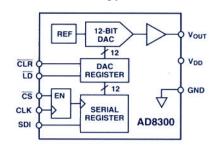

#### 12-Bit Dual DAC: Serial, Single Supply, Saves Space (SO-14)

#### +5-V-supply AD8522 includes 2.5-V reference and buffered voltage outputs. Surface-mount package is only 1.5 mm high

The AD8522\* is a complete (Figure 1) dual 12-bit digital-to-analog converter (DAC). Low in cost and easy to use, it is available in a space-saving 1.5-mm-high 14-pin surface-mount (SO-14) package—as well as a 14-lead epoxy DIP—and requires no external components for operation.

Figure 1. Functional block diagram.

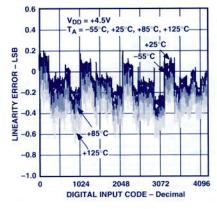

Requiring only 5 mW of power quiescently (and 25 mW maximum, with TTL input levels) from a single +5-volt  $\pm 10\%$  supply, it has monotonic output and a maximum integral nonlinearity (relative error) specification of  $\pm 1.5$  LSB ( $\pm 0.037\%$  FSR) over its temperature range of -40 to  $+85^{\circ}$ C (Figure 2), with a  $\pm 1$ -LSB match between the two channels. The AD8522 was designed for use in fixed and portable applications in equipment for digitally controlled calibration, and in dc setpoint applications for communications and process control. It is priced at \$8.36 in 1000s.

Figure 2. Typical linearity error plotted as a function of digital code and temperature.

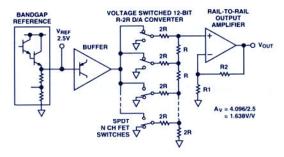

The AD8522 includes a serial digital interface, an on-board 2.5-V bandgap reference, and buffered voltage outputs capable of driving  $\pm 5$  mA at half-scale. Full-scale output is 4.096 V, set by laser-trimming (4.095 V for an input code of FFF<sub>H</sub>), an easy-to-use 1.0 mV/LSB. Serial data can be clocked in at 14 MHz and more.

Figure 3. Equivalent schematic of analog portion of AD8522.

Figure 3 shows the analog portion of the AD8522, including the curvature-corrected bandgap reference—which can provide  $\pm 2.5 \text{ V}$  at up to  $\pm 5 \text{ mA}$  externally (0.5% regulation); the voltage-switched R-2R ladder, and the rail-to-rail output amplifier, with gain factory-set for the specified output range. DC specifications over temperature include  $\pm 1 \text{ LSB}$  differential nonlinearity (monotonic), full scale voltage error  $\pm 16 \text{ mV}$  (including the error of the internal voltage reference), with a tempco of  $\pm 15 \text{ ppm/}^{\circ}\text{C}$ .

The device's output can drive a 500-pF load without oscillation; output settling time is 16  $\mu$ s to +FS  $\pm$  1 LSB, and to 0 + 6 LSB. Digital feedthrough is 2 nV-s, DAC glitch is 13 nV-s, and crosstalk is -38 dB while changing Load Enable in the opposite DAC.

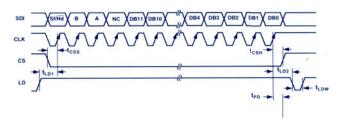

Hardware and software modes: The AD8522 has a 16-bit serial input register that accepts clocked-in data when the CS pin is active low. The DAC registers are updated by the Load Enable  $(\overline{LDA}$  and  $\overline{LDB}$  pins). Data can be loaded into the DACs in either a hardware or a software mode.

Hardware load directs the data currently clocked into the serial shift register into the DAC A register, the DAC B register, or both, depending on the active-low strobing choice for the  $\overline{LDA}$  and  $\overline{LDB}$  pins. Software-hardware serial data-register bit, Sf/ $\overline{Hd}$ , must be low for this mode to be in effect (Figure 4).

Software load permits the number of control lines to the AD8522 to be minimized. In this mode of operation, with bit  $Sf/\overline{Hd}$  high, the  $\overline{LDA}$  and  $\overline{LDB}$  pins act as one control input, taking the present contents of the serial input register and transferring the 12 bits of data into the decoded address determined by the address bits, A and B, in the serial input register.

The AD8522 was designed by Derek Bowers and Carol Flores at our Santa Clara, CA facility.

Figure 4. Timing diagram, showing software-control bits  $(Sf/\overline{Hd}, A, and B)$ .

<sup>\*</sup>Use the reply card for technical data. Circle 6 (for sample—circle 47 and mention model no.)

# 16-Bit Fixed-Point DSP with 80 KBytes of RAM Reduces System Cost

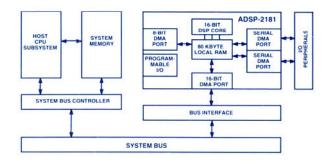

### ADSP-2181 eases design of reprogrammable systems, has 2 serial ports, plus 8-bit & 16-bit parallel DMA ports

The ADSP-2181\* is a 16-bit fixed-point reprogrammable digital signal processor (DSP) with 80 Kbytes of on-chip random-access memory (RAM), significantly more than is available on any other general-purpose fixed-point DSP. The fully integrated RAM and on-chip peripherals maximize on-chip performance, eliminating the need for external SRAM. This greatly reduces cost (the extra memory is essentially free in this competitively priced processor) and increases speed, since the additional lags inherent in using external buses are eliminated when communicating with on-chip memory.

Many complete applications can fit in the on-chip RAM, for example, high-speed data communications (V.32bis modems), spectrum analysis, speech compression (GSM, VSELP), or music synthesis. Because of download-ability, system-level designs requiring larger amounts of memory can use slower, low-cost bytewide read-only memory (ROM) and host-system dynamic RAM instead of high-speed, expensive SRAM (Figure 1).

Figure 1. Typical system configuration.

In embedded systems, the 8-bit parallel direct memory-access (DMA) port allows simple interfacing to low-cost, byte-wide PROMs, EPROMs, and ROMs, for storage of large data tables and program overlays. In host-based, or multiple-processor systems, the 16-bit parallel DMA port provides a high-speed communications port to system buses, allowing the host—or other processor—to directly access the ADSP-2181's on-chip RAM. This capability facilitates on-the-fly configuration of the DSP for multiple applications.

With its combination of high performance and multiple data-I/O ports (Figure 2), the ADSP-2181 can be easily reconfigured to suit a variety of systems and applications—for example, in integrating audio, video, and communications software into the PC

environment. The key performance benchmarks shown below illustrate the ADSP-2181's capabilities in PC-based sound and communications applications; they compare quite favorably with the best performance of any general-purpose fixed-point DSP. The benchmarks are executed from on-chip memory; other DSPs require external high-speed SRAM, which typically hogs a large portion of the DSP subsystem cost and time budgets.

#### FFT:

| 1-K point, complex, radix 4, DIF, FF I | 1.07 ms |

|----------------------------------------|---------|

| 4-K point, complex, radix-4, DIT, FFT  | 5.5 ms  |

| Voice, Data:                           |         |

| 20-voice synthesis                     | 20 MIPS |

| 11-voice emulation                     | 16 MIPS |

| V.32bis (14.4 kbps)                    | 16 MIPS |

| V.34 (28.8 kbps)                       | 32 MIPS |

The ADSP-2181 also provides a number of hardware- and software power-down modes, which allow the DSP to be placed in a "sleep" mode or in a reduced-power operating mode, to prolong battery life in portable applications.

For space-critical applications, such as portable communications and PCMCIA cards, the ADSP-2181 is available in a 128-lead PQFP (plastic quad flatpack) and a TQFP (thin quad flatpack)—which is just 1.4 mm thick. The device operates at 33 MIPS from a +5-V supply (3.3-V operation is also in the offing). As with all Analog Devices DSPs, there is a full suite of software and hardware tools for support. The ADSP-2181 in PQFP is priced at \$51 in 1000s.

The ADSP-2181 was designed by a team led by Greg Koker at our Norwood MA facility.

Figure 2. Block diagram of the ADSP-2181

ADSP-2181

48 KBYTE

PROGRAM RAM

32 KBYTE

DATA RAM

DMA

<sup>\*</sup>Use the reply card for technical data. Circle 7

# Simple Techniques Protect Amplifiers from Input Overvoltage

#### First, understand how the amplifier behaves under fault conditions

by Joe Buxton

Common-mode overvoltage on the inputs is a potential problem in any analog measurement system that interfaces to the "outside" world. Op amps and instrumentation amplifiers often have the difficult job of interfacing to external signal sources, such as sensors or other electronics, which may expose the system to voltages that exceed the parts' absolute maximum ratings. For example, a fault condition, such as an accidental short to other circuitry or equipment, could cause the sensor and wires to contact high voltages and apply them to the sensor amplifier. Natural phenomena, such as thunderstorms, can also induce overvoltages.

Regardless of the cause, whenever the input voltage exceeds an op amp's ratings, it could be damaged, whether the device's power supplies are on or off. In fact, with power off, even small fault voltages can damage the device. For example, when an op amp operates on  $\pm 15$ -V supplies, the input's magnitude must exceed either  $\pm 15$  V or  $\pm 15$  V before damage can occur. But with the supplies turned off, voltages as small as  $\pm 0.7$  V can cause damage. A typical instance where this kind of fault may occur is when interconnected circuits are powered separately—and one is turned on while the other is off. The live circuit can easily apply sufficient voltage to damage the ICs in the circuit that is off.

The best way to avoid damaging an amplifier is to eliminate all overvoltage conditions. However, predicting all possible fault conditions is a well nigh impossible task. Once an IC is damaged, it must be replaced (as well as any other devices that its failure caused to fail), a costly procedure when possible; But more often than not, the IC will be damaged in the field, resulting in costly re-working of the equipment (if it is recoverable). Thus, routinely designing to protect amplifiers from damage is an imperative for long-term reliability and low maintenance costs.

The first step in protecting an amplifier from overvoltages is to understand how it behaves when subjected to fault conditions. Once the failure mode has been determined, appropriate protection needs to be applied to the circuit—often as simple as adding a series input resistor or providing external clamping. Using fairly simple techniques, a designer can protect a circuit from overvoltages from a few volts to hundreds of volts, avoiding headaches and expense. But when external elements are added, their effects on the overall circuit performance must be considered.

#### Overvoltage can destroy an amplifier (gradually)

Given a high enough input voltage of the appropriate polarity, any op amp will conduct current to either the positive rail or the negative rail. While all op amps and instrumentation amplifiers are susceptible, the actual threshold for significant current flow

This article is based on an article originally published in SENSORS magazine, May, 1994, copyrighted by Helmers Publishing, Inc., Peterborough, NH, with permission.

differs appreciably for different devices. A typical conduction voltage can be as low as a diode drop of 0.6 V or as high as a process breakdown voltage of 50 V or more. The threshold for a particular amplifier depends on its input-stage architecture, as we will see.

Though popular opinion and most data sheet specs skirt this point, forward conduction of itself during an overvoltage is not inherently damaging to an IC unless accompanied by substantial current flow. Currents of 100 mA and more can quickly cause the input traces to burn out, resulting in a damaged part. But, if the current is limited to microamperes, or even a few milliamps, most amplifiers will be safe, even with continuous overvoltage. In fact, a simple resistor will generally protect an amplifier under almost all overvoltage conditions. But its presence degrades performance, so most amplifiers do not have inherent current limiting in their input stages. In those cases, when overvoltage does occur, unlimited current can flow and destroy the part.

The actual value of current that can damage an amplifier is a function of input stage construction, particularly, the width of the metal traces in the IC's input stage. A phenomenon known as *metal migration* occurs whenever the current density within a metal trace exceeds a certain level—about 1 mA per 1 µm of width for a typical 1-µm-thick trace. Thus, for a 5-µm-wide metal trace, the maximum safe current is about 5 mA. Beyond this level, atoms of the metal begin to move. In time, enough metal can migrate to cause an open circuit in the trace (and a bulge elsewhere), rendering the part inoperable. Input trace widths do differ from amplifier to amplifier, usually in the 5-to-10-µm range. There are exceptions, but for most bipolar parts, limiting the input current to less than 5 mA protects the device. This assumption is maintained in the following discussion.

An IC can often be subjected to more than 5 mA and still appear to function normally. But this does not guarantee that the part is free from damage. Metal migration is a *cumulative* effect; it may take a long time to cause a failure. But the damage will build up, eventually resulting in an open trace here or a short-circuit there. Such failures due to repeated overvoltage are difficult to detect in the early stages. The more current that flows during an overvoltage, the more the migration accelerates, and the sooner an open trace results. So, even though an amplifier may appear to withstand overvoltage currents well above 5 mA for a short time, it is important to observe the 5 mA limit to improve the prospect of long-term reliability.

Factors affecting amplifier overvoltage characteristics: Two methods of conduction occur in overvoltage conditions: forward biasing of PN junctions inherent in the structure of the input stage and—given enough voltage—reverse-bias junction breakdown. The only danger of forward biasing a PN-junction is that excessive current would flow and damage the part. As long as the current is limited no damage should occur. However, when the conduction is due to the reverse bias breakdown of a PN junction, the problem can be more serious, depending on the junction in question. For the case of a base-emitter junction breaking down, even small amounts of current can cause a large degradation in the forward beta of the transistor. After a breakdown occurs, the input parameters of the op amp, such as offset and bias current, may degrade well beyond the specified values. External diode

<sup>1</sup>Analog Integrated Circuits, Paul R. Gray and Robert G. Meyer, J. Wiley and Sons, 1984, page 28.

protection (to be discussed) is needed to limit voltage to prevent base-emitter junction breakdown.

The structure of the input stage affects the overvoltage characteristics of an amplifier. Many paths may exist in an amplifier to form a diode to either the positive or negative supply. For example, many bipolar devices are built on a substrate made of p-type silicon, which is electrically connected to the negative supply. This p-type material forms "substrate" diodes in conjunction with various n-type structures in the IC's circuitry. When the input goes below the negative supply, a substrate diode may clamp the input to within 0.7 V of the negative supply. The substrate diodes typically have low resistance, so virtually unlimited amounts of current can flow until the part is destroyed. The next section describes in detail a few of these structures that lead to PN junctions energizing during an overvoltage condition.

The overvoltage characteristics of an amplifier are not often apparent just from the data sheet. Input stages differ widely resulting in a variety of overvoltage characteristics. The simplified schematics in data sheets can sometimes suggest paths of forward biasing PN junctions. More often, though, there is not enough information to determine the overvoltage characteristics. Indeed, a full schematic with the process cross section is needed, and it should be interpreted by one wise to the ways of IC circuitry. Even then, possible conduction paths are not always apparent. In cases

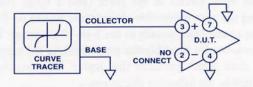

Figure 1. A curve tracer can be used to quickly determine the overvoltage characteristic of an amplifier.

where no obvious path exists, or the schematic does not contain enough detail, (and perhaps as a general rule) one's best route is to measure an amplifier's characteristics in the lab.

A curve tracer can be quickly configured to measure the overvoltage characteristics of any amplifier, as shown in Figure 1. The curve tracer ramps a dc voltage on the input and measures the current flowing into or out of the input stage. For most amplifiers, having symmetrical inputs, this measurement yields the same results, independently of which input is measured. Current feedback amplifiers are an exception to this rule; their positive and negative inputs have different characteristics. If a curve tracer is not available, similar results can be obtained in a short time using a dc voltage source and a multimeter; connect the source to the input through a 10-k $\Omega$  resistor, and measure the current as a function of the input voltage.

The supply voltages can be configured as desired; for simplicity, all the measurements in this article were made with both supplies connected to ground. The state of the other input is an important consideration in determining the characteristics. Many amplifiers have input protection diodes connected across the differential input pair to prevent large differential voltages from damaging the input transistors by reverse biasing their base-emitter junctions; but they do not protect against large common-mode voltages. When measuring the overvoltage characteristics, the other input should be left floating to ensure that the input diodes do not conduct,

thus concealing the characteristics of interest.

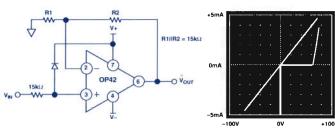

As noted above, amplifiers exhibit two basic types of overvoltage characteristics; recognizing the difference between the two on a curve tracer is important in understanding how to protect an amplifier. The forward biasing of PN junctions is evident because, as the input voltage rises above the supplies, distinct break points are encountered when internal diodes turn on. In most cases, this characteristic occurs within one or two diode drops of either supply. With forward conduction, simple current-limiting protects the amplifier. On the other hand, reverse-junction breakdown typically occurs only when the input rises at least 5 V above the positive supply or below the negative supply. The actual voltage for breakdown varies widely [in the OP42 example (Figure 3), it can be 50 V and more]. In such cases, an external diode clamp should be used to prevent breakdown.

Two examples of overvoltage characteristics: Two amplifiers' overvoltage characteristics are shown here to illustrate how overvoltage characteristics can occur. This is certainly not an exhaustive cross section of amplifiers. Any different amplifier architectures should be checked individually.

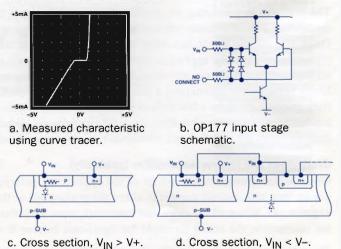

Figure 2a shows the overvoltage characteristic of an OP177 precision amplifier. Because of its low offset and drift characteristics, the OP177 is commonly used to amplify low level sensor outputs. Thus, the OP177 could easily find itself in a circuit (especially with remote sensors) where overvoltage is likely. The curve tracer plot in Figure 2a shows that conduction is visible when the input exceeds the positive supply by about 0.6 V or goes below the negative supply by the same amount. Notice that in the positive direction the current quickly exceeds the 5-mA limit. However, in the negative direction, the current appears to be limited by a linear resistance. The reason can be seen when the input stage circuitry is examined in detail.

The input stage schematic in Figure 2b reveals a  $500-\Omega$  resistor in series with each input; this explains the current limiting in the negative direction. In fact, the curve shows a 4-mA change in input current for a 2-V change in input voltage, resulting in the expected  $500-\Omega$  slope. But, what happened to the resistor for positive overvoltages? The unlimited current flow rules out a series resistor. Also, where can we find the forward-biased diodes implied by the plot? To understand this, we need to examine the cross section of the process for the input devices. The input resistors are diffused

Figure 2. OP177 and overvoltage.

p-type material in a reverse biased n well, and the n well is electrically connected to V+, as shown in Figure 2c. When the input rises above V+, the junction between the p-type resistor and the n well forward biases, (dashed-line diode). Because the p-type material forward biases, the resistor is bypassed. In this case, essentially unlimited current can flow to the positive supply, causing the input stage to be damaged.

The conduction path in the negative direction is a little more complicated, but it can be identified by examining the cross section of the input devices. Figure 2d shows the same diffused resistor in series with one of the input protection diodes. For simplicity, the cross section of only one of the differential protection diodes (2b) is shown in (2d). As shown, these diodes are actually fabricated from NPN transistors, with the base-collector junctions tied together by a metal trace. The substrate of the entire chip is made of p-type silicon that is electrically connected to the negative supply. When the input drops below the negative supply, the input resistor and protection diode are pulled down. At 0.6 V below V-, the substrate to "collector" junction forms a diode, shown by the dashed line. The anode is the p-type substrate and the cathode the n well of the input protection diode. In this case, the p-type diffused resistor does not forward bias, so the resistance remains in series with the input to limit the current. Because only PN junctions forward bias when the input exceeds either supply of the OP177, the input current needs only to be limited to less than 5 mA to protect the device, and no external clamping is required.

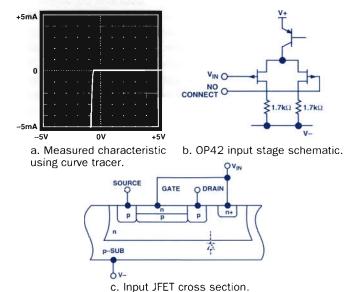

Figure 3 describes another typical input stage using a p-channel JFET differential pair. The OP42 is used as an example, but other JFET input devices behave in the same way. The curve-tracer response in Figure 3a shows an overvoltage characteristic very different from that of Figure 2a. For positive overvoltage, there doesn't seem to be a conduction path, but if higher voltage is applied, the input stage of the OP42 eventually breaks down at about 50 V. However, negative overvoltage quickly forward-biases an internal diode that can conduct large amounts of current. The input-stage schematic (3b) shows the differential p-channel JFET with no input series resistance or protection diodes but provides no clues as to how conduction occurs. Again, one can find the conduction paths in the input cross-section.

Figure 3. OP42 and overvoltage.

The p-channel JFET is an ion-implanted device built in n epi material, as shown in Figure 3c. The n-type gate and the n epi material are connected directly to the input. When the input voltage drops below the substrate potential (connected to V-), the substrate-to-n-well junction forward biases, forming a diode from the negative supply directly to the input. Because the silicon has low resistivity and no series resistor exists, essentially unlimited current flows. However, when a positive overvoltage is applied to the inputs, the n well and n gate are pulled above V+. Thus, the PN junctions (formed by the gate to drain and n well to substrate) in the input stage are reverse-biased and no conduction occurs-until eventually the input junctions break down if the input voltage is increased sufficiently—to about 50 V for the process on which the OP42 is fabricated. This breakdown, unlike base-emitter breakdown, is not inherently damaging to the JFETs if the input current is limited to <5 mA. However, as additional insurance, external clamping using a diode is recommended if the input voltage is likely to approach the breakdown region.

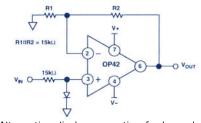

Externally protecting an amplifier: Op amps used in environments where overvoltages are expected require protection. Most amplifier types (except for the few with internal protection) require external resistors and, in some cases, diodes. For amplifiers with internal PN junctions that forward-bias whenever the input voltage exceeds the rail, the only protection needed is an external series resistor to limit the current to 5 mA. When reverse-bias junction breakdown is involved, external diodes are needed. Usually, the breakdown involves just one of the supplies, so only one diode is needed, with its current-limiting series resistor. When in doubt about an amplifier type's failure modes, check it out on a curve tracer. A simple 5-minute measurement can avoid the headaches of replacing failed amplifiers in the field.

Figure 4 shows the OP177's breakdown with added protection; it compares with the unprotected case in Figure 2a, where the current quickly exceeds 5 mA with an input only 1 V above the positive supply. With a 2-k $\Omega$  resistor in series with the input, the current is now limited to 5 mA for input voltages up to 10 V beyond the supply voltages. The equation for picking the value of series resistance is very simple. Just divide the magnitude of maximum expected overvoltage (positive or negative) by 5 mA. In this test, the op amp's positive input is the only one connected to the outside world, so no protection is needed for the negative input. However, in cases where both inputs may be subjected to overvoltage—as in differential configurations or instrumentation amplifiers—both inputs require protection.

Whenever components are added, the circuit needs to be analyzed to determine the effects of adding them. Here, the series protection resistor adds to the offset and noise of the circuit. The offset is simply the product of the bias current and resistance; in

Figure 4. OP-177 input current, using protective resistor.

balanced amplifiers, the offset can be minimized by equalizing resistances seen by both inputs. The thermal noise contributed by the resistor, and the voltage developed by the amplifier's current noise flowing through that resistor, combine with the voltage noise of the op amp as root-sum-of-the squares (rss). If either of these error contributions is unacceptably large, a possible alternative is to add clamping diodes from the input to both supplies. If the diodes can handle currents >5 mA, the series resistance can be reduced. The diodes and resistor should be selected such that the external diode turns on at <0.6 V for the maximum overvoltage, to avoid turning on the internal diodes. However, external diodes may in some cases cause problems of their own, as will be seen below.

When the overvoltage characteristic of an amplifier shows breakdown occurring, external clamp diodes should be added to prevent the amplifier's input voltage from ever reaching that breakdown voltage. Often, breakdown occurs in only one direction and requires only one external diode for adequate protection. This helps keep the parts count down and minimize the diode's parasitic effects. In either case, a series resistor is still needed to limit the current through the amplifier. The OP42, with its 50-V positive breakdown, is used as an example in Figure 5a. Here, a diode has its anode connected to the input and its cathode to the positive supply. When the input exceeds the positive supply by approximately 0.6 V, the diode forward-biases and limits the input voltage to well below the breakdown voltage, whether or not the part is powered on. A series resistor is included to limit the currents through the diode and the amplifier for negative overvoltages. In this example, for a maximum input voltage of  $\pm 75$  V, a 15-k $\Omega$  resistor is required to limit the current to 5 mA. As the curve tracer shows in 5b, the clamp diode turns on when the input exceeds V+ by 0.6V, and the series resistor limits current in both directions.

a. Reversed diode connected to V+.

c. Alternative diode connection for lower leakage.

Figure 5. Diode protection of OP42.

In high-impedance applications, the choice of diode is critical because it adds to leakage current. The diode chosen will depend on the maximum leakage-current requirement. A common 1N914 or 1N4148 diode typically has 10 nA of leakage. This is certainly not a very good choice to use with a JFET amplifier in a low-bias-

current application, but may be adequate for less demanding applications. A good intermediate choice for a protection diode is the base-collector junction of a 2N3906 transistor. The transistor is a low-cost part with leakage currents of the order of 10 pA. For the most demanding applications, low leakage FETs may be required. Such parts as the 2N4117A and PAD1, from Siliconix, provide protection with leakage currents under 1 pA. However, when JFET protection diodes are used for their low leakage, the temperature effects must also be considered. JFETs typically exhibit a doubling of leakage current for every 10°C temperature rise. This rise must be compared to the op amp's bias current characteristic over the full operating temperature range of the circuit. With a JFET input amplifier, which has similar temperature behavior, the diode's leakage may still be less than the amplifier's; in some cases, the 2N3906 may be the better choice.

In applications where small negative (and even smaller positive) voltages must be measured at high impedance, Figure 5c shows an alternative configuration for connecting the diode. Here, the anode is connected to the input, so that the diode conducts for positive input voltages, but the configuration offers especially low leakage for small negative input voltages, because the reverse bias voltage on the diode is only  $-V_{IN}$ , instead of  $-V_{IN} + V^{+}$ . This configuration may also be useful for high-impedance measurement of small positive voltages (well below 50 mV). However, if the input goes more than 50 mV above ground during normal operation, the diode slowly starts to forward bias, the leakage goes up, and response to large inputs becomes nonlinear. The choice between protection schemes depends entirely upon the application and the expected voltages.

The amplifiers discussed above do not have internal overvoltage protection, except possibly for differential-input protection. However, there exists a small group of amplifiers that are designed to handle input voltages that exceed the supplies.\* Such amplifiers often use thin-film resistors in series with both inputs to limit fault current. They, unlike diffused resistors, are isolated from the silicon by silicon dioxide, do not form a diode to either supply, and thus can limit current like external resistors. For example, the OP90, with 4-k $\Omega$  thin-film resistors, is guaranteed to handle voltages of magnitude up to 20 V greater than either supply. Another method is to use protection JFETs in the input stage; they turn on during an overvoltage condition and shunt current to the supplies. The AMP-02 instrumentation amplifier, using this scheme, allows its inputs to reach 60 V without damage. The designer should check a part's Absolute Maximum rating to determine its capabilities. For most amplifiers, that rating will read: "±V<sub>S</sub>". To maximize the performance in benign environments, such amplifiers do not have protection on-chip, so external protection is needed. But the ability of amplifiers with protection to handle higher voltages is specified on the data sheet.

**Summary:** Input overvoltage, a common problem, requires careful design practice to avoid damaging amplifiers. Consider the environment that a particular amplifier is required to operate in and identify any possible overvoltage modes. Once the voltage levels are established, the op amp must be investigated to see how it behaves under these stress levels. Then the appropriate protection, if required, must be included. An ounce of prevention at the design stage will forestall headaches in the field.

<sup>\*</sup>Examples: Operational amplifiers such as the AD820, AD822, OP90, OP290, OP291, OP490—and instrumentation amplifiers, such as the AD524, AD626, and AMP02. For technical data on these amplifiers, Circle 8

#### Amplifiers: Transimpedance, Isolation, $\mu$ Power, VCAs

### Quad VCA for Audio SSM2164 has 0.02% THD, -100 dB \le Gain \le +20 dB

The SSM2164 has four independent channels of voltage-controlled current gain with an adjustment range of 120 dB and a gain sensitivity of -33 mV/dB for each channel. The channels are matched to within 0.07 dB at unity gain, with a low 0.02% 2nd and 3rd-harmonic distortion (0.1% max). A single resistor establishes Class A or Class AB operation.