# Dialogue Analog

A forum for the exchange of circuits, stems, and software for real-world signal processing

ADSP-21020 FLOATING-POINT DEP CHIP FOR HIGH-SPEED SIGNAL PROCESSING (page 3)

Single-supply instrumentation amp for automotive environments (page 9) SPICE macromodels—3 powerful tool for designers (page 19)

Complete contents on page 3

00000003937

ADSP-21020

ADSP-21020

3-937E-9

2.998E10

FLOATING POINT

# Editor's Notes

# AVAILABILITY - DISTRIBUTION

In our welcome to Precision Monolithics (PMI) as a new Division of Analog Devices (Analog Dialogue 24-3, 1990), we noted that in the North American market their products were sold through distributors. We predicted that the ease of purchasing in any quantity, and the benefits of distributor inventory that this brings to both small- and large-quantity users would be poten-

tially available in the future for many Analog Devices parts in the U.S.A. and Canada. It has already come to pass. Now the Analog Devices line of standard ICs is available through the many branch locations of these distributors: Alliance Electronics, Allied Electronics, Anthem Electronics, Bell Industries, Future Electronics, Hall-Mark Electronics, Newark Electronics, Pioneer Standard Electronics, Pioneer Technologies Group, and Zentronics.

# **BOB ADAMS: AES FELLOW**

We are pleased to note that Robert W. Adams has been named a Fellow of the Audio Engineering Society (AES) "for his significant influence on the theory and practical realization of high-precision oversampling analog-to-digital and digital-to-analog converters and their measurement." According to Dr. Marshall Buck, President of

the Audio Engineering Society, "Bob's AES Fellowship is a tribute to his creative, state-of-the-art approach to design of the key component in digital audio engineering, the a/d converter."

Adds Dennis Buss, Analog Devices' Vice President of Technology Development, "Since joining Analog Devices, Bob has undertaken the lead role in developing technically advanced sigma-delta analog-to-digital converters, including the AD1879, which established a new performance benchmark for audio recording applications. Bob continues to define innovative circuit architectures, many presently in development, which promise to further increase digital audio fidelity, and he continues to be an active participant at technical conferences."

Bob Adams joined Analog Devices in 1989 as a Senior Design Engineer for digital audio converter products at Analog Devices Semiconductor Division, Wilmington MA. He works on a diverse range of consumer- and professional audio ICs, including a/d and d/a converters and other high-performance signal-processing devices. The AD1879, an 18-bit sigma-delta ADC for stereo, was described in a paper presented at the 1991 AES Convention in Paris, France.

Adams was born in Syracuse NY and received his BSEE in 1976 from Tufts University, Medford MA. After a brief career as a professional musician, he worked at ADS, Inc., a manufacturer of automotive audio electronics and loudspeakers. In 1977, he joined dbx, Inc., designing oversampling a/d converters for digital audio,

and later became Director of Research. Products that his work led to include an early recording system that employed companded delta modulation—and later a 20-bit stand-alone a/d converter using sigma-delta technology.

Bob has published many papers under the auspices of AES and IEEE<sup>1</sup> and holds several circuit patents. He is a Sustaining Member of AES and a Member of IEEE.

Dan Sheingold D

Several of his papers are included in the book, Oversampling Delta-Sigma Data Converters, edited by Candy and Temes. New York: IEEE Press, 1992.

### THE AUTHORS

Pete Predella (pages 12 and 15) is a Technical Publicity Associate at Analog Devices, in Norwood MA. Since joining ADI, in 1979, he has also been a Technician for the Component Test Systems and Memory Devices Divisions. Peter is a graduate of GTE Sylvania Technical School and is currently pursuing a BSET from Northeast-

ern University. His interests include reading, salt-water fishing, and golf.

Joe Buxton (page 19), a Senior Application Engineer for the PMI Division of Analog Devices, has worked extensively on the development of SPICE op amp models; he writes application notes and articles for publication and also helps customers resolve their circuit and design problems. In 1988, Joe received a BSEE from

the University of California, Berkeley. In his leisure time, he enjoys bicycling, hiking, skiing, and listening to music.

Bill Schweber (page 3) is a Senior Technical Marketing Engineer and Contributing Editor to Analog Dialogue. His photo and a biographical sketch appeared in the last issue of Analog Dialogue, 25-1

James Bryant (page 24) is European Applications Manager for ADI, based in Newbury, England. His photo and a biographical sketch appeared in the last issue of *Analog Dialogue*, 25-1.

### **COVER DESIGN**

The cover illustration symbolizes the compact representation of numbers in a floating-point format. Designed and executed by Shelley Cohane, of Design Encounters, Hingham MA, it incorporates a graphic design copyrighted by Digital Art/Westlight.

# Analog Dialogue

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Published by Analog Devices, Inc. and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and DSP circuits and systems. Correspondence is welcome and should be addressed to Editor, Analog Dialogue, at the above address. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577, Telex 174059, or cable ANALOGNORWOODMASS.

# Floating-Point DSP for High-Speed Signal Processing

A fast, easy-to-use descendant of the popular ADSP-2100 fixed-point family, the ADSP-21020 inaugurates a new generation

by Bill Schweber

The recently announced ADSP-21020\* expands Analog Devices' family of digital signal processing (DSP) ICs to encompass floating-point operation. Like the well-established fixed-point ADSP-2100A microprocessor and ADSP-2101 microcomputer families,† this device—first of a series of floating-point DSPs—has an architecture optimized for signal processing. It thus combines high attainable performance with ease of use.

### PERFORMANCE

The critical measure of a processor for real-time signal-processing applications is achievable performance. If a DSP lacks the speed to implement an algorithm in real time, either the processor or the algorithm must be replaced. This contrasts with processors that accelerate computer performance in essentially off-line numerical computations; for these applications, while "faster is better," displaying the answer a little slower than desired (e.g., 4.72 s vs. 4.25 s) is inconvenient but not critical.

There are many ways to specify the performance in terms of device parameters—for example, cycle time, MFLOPS (rillions of floating-point operations per second), and clock speed—but these alone aren't especially useful to the system design engineer. Algorithm-performance benchmarks are much more meaningful for signal processing, since they are examples of performance achieved in actual real-time computations.

The 1024-point complex fast Fourier transform (FFT) is often used as a primary figure of merit in signal-processing benchmarks. Table 1 records the ADSP-21020's submillisecond benchmark performance for this algorithm, as well as other common signal processing applications and basic operations.

Table 1. ADSP-21020 Benchmark Performance

| ADSP-21020 Grade:                            | -100 | -80  | -60   |       |

|----------------------------------------------|------|------|-------|-------|

| Operations                                   |      |      |       | Units |

| Instruction cycle                            | 40   | 50   | 60    | ns    |

| Complex FFT, 1024-point                      |      |      |       |       |

| Radix 2 with bit-reverse                     | 0.77 | 0.96 | 1.155 | ms    |

| N-tap FIR filter (per tap)                   | 40   | 50   | 60    | ns    |

| Y/ X (floating point divide)                 | 320  | 400  | 480   | DS    |

| $1/\sqrt{X}$ (floating pt. sq. root inverse) | 520  | 650  | 780   | пs    |

| Matrix multiply (pipelined)                  |      |      |       |       |

| $[3 \times 3] \bullet [3 \times 1]$          | 360  | 450  | 540   | ns    |

| $[4 \times 4] \bullet [4 \times 1]$          | 640  | 800  | 975   | ns    |

| IIR Filter (per biquad)                      | 200  | 250  | 300   | BS    |

\*Use the reply card for technical data. Circle 1 †Use the reply card for technical data. Circle 2

## **OVERVIEW**

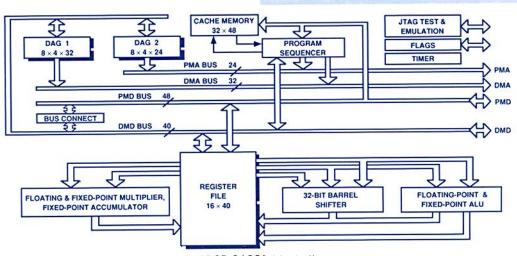

Like the fixed-point DSPs, the ADSP-21020 (Figure 1) supports the five prime requirements for digital signal processors<sup>1</sup>:

• fast, flexible arithmetic units: the ADSP-21020 executes all instructions in a single cycle

"Application decides optimal DSP architecture," by Bob Fine and David Fair, Analog Dialogue 24-1 (1990), pp. 9-11.

# IN THIS ISSUE

Volume 25, Number 2, 1991, 28 Pages

| Editor's Notes, Authors                                                  |

|--------------------------------------------------------------------------|

| ADSP-21020 Floating-Point DSP:                                           |

| Floating-point DSP chip for high-speed signal processing                 |

| Numerical C speeds code development and execution                        |

| Development tools and third-party support for floating-point DSP         |

| Single-supply in-amp for automotive applications (AD22050)               |

| Disk-drive ICs for read-channel and servoloop control (AD897, AD7774) 10 |

| 3 new single- and multichannel S/H chips (AD9100, AD682, SMP-18) 12      |

| Monolithic 10-bit, 18-MSPS sampling ADC with on-chip T/H (AD773) 14      |

| Complete 16-bit SOIC DACPORT includes on-chip 10-V ref (AD669) 15        |

| New-Product Briefs:                                                      |

| Serial DACPORTs™ in 12-bit DIPs and SOICs (AD7233/7243) 16               |

| 8 12-bit MDACs on a chip with serial input, +5-V supply (AD7568) 16      |

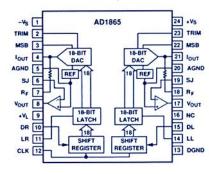

| Dual 18-bit audio DAC: 107-dB SNR, 16× oversampling (AD1865) 16          |

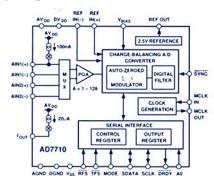

| Single-chip 21-bit Σ-Δ data acquisition family (AD7710/7711/7712) 17     |

| 16 × 16 analog crosspoint switch-array IC (AD75019) 17                   |

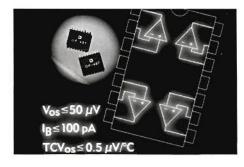

| Quad op amp with industry's highest precision (OP-497) 17                |

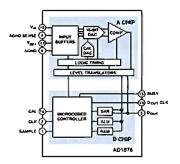

| Sampling ADC: 16-bit 100-kSPS, serial, autocalibrated (AD1876) 18        |

| 12-bit 750-kSPS sampling ADC dissipates <350 mW (AD7886) 18              |

| Flexible 12-bit, 8-10-µs ADCs:                                           |

| Improved performance for '574 sockets (AD774B)                           |

| Low cost, low power, small package (ADC-912A)                            |

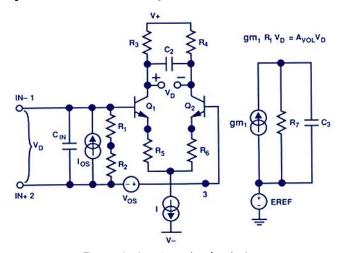

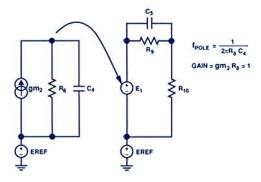

| Advanced SPICE op-amp macromodel: a powerful tool for designers 19       |

| Analog Devices names two new Fellows: Derek Bowers and Wyn Palmer . 23   |

| Ask the Applications Engineer - 10: When is a wire not a wire? 24        |

| Worth Reading                                                            |

| Potpourri (Last Issue, Errata, Product Notes, Updates, Patents) 27       |

| Advertisement                                                            |

- unconstrained data flow to and from the computation units: the Harvard architecture is supported by a 10-port register file. In every cycle: two operands can be read or written off-chip to or from the register file; two operands can be supplied to the ALU; two operands can be supplied to the multiplier; and two results can be received from the ALU and the multiplier (three, if the ALU operation is a combined addition/subtraction)

- extended precision and dynamic range in the computation units: the

processor uses IEEE-standard floating-point format (user-chosen

32- or 40-bit), and all extended-precision results are carried

throughout its computation units, to avoid overflows and limit

intermediate data-truncation errors.

- dual address generators for program and data memories: they provide both immediate and indirect (pre- and post-modify) addressing; they also support modulus and bit-reverse operations vital to effective execution of algorithms such as the FFT.

- efficient, zero-overhead program sequencing and control: in addition to zero-overhead loops, the ADSP-21020 supports single-cycle setup and exit for loops; loops can be nested (up to six levels in hardware) and interrupted.

The ADSP-21020 extends these features as necessary for a floating-point version (see adjacent box) and easier system development. The enhancements embodied in the ADSP-21020 are primarily in four categories: high-level language support, JTAG serial scan-path access, IEEE-standard floating-point operation, and open memory architecture. These features distinguish the ADSP-21020 from other floating-point DSPs (or fast microprocessors) available today.

High-level languages (HLLs) have the potential to provide many benefits to the system designer and programmer via more-structured code, fewer bugs, use of available algorithms, and even use of the same code on processors from several vendors. Their disadvantages have been that HLLs usually compile inefficiently, producing cumbersome machine code that takes more time and occupies more memory than well-tuned assembly language.

To overcome these disadvantages by supporting compact compiled HLLs and fast execution, the ADSP-21020 family architecture features:

- general-purpose data- and address register files, which can be flexibly used by the compiled code.

- 32-bit native data types [e.g., integer, floating-point, etc.], so that internal number format is consistent and efficient.

- large address spaces: 16 megawords for program memory,

6 gigawords for data memory.

- pre- and post-modify addressing formats

- · unconstrained placement of the circular buffer in data memory

- on-chip program, loop, and interrupt stacks.

In addition, the ADSP-210XX family is designed to support Numerical C, an extension of ANSI C. Numerical C is a compiled language; it supports vector data types and operators for numeric and signal-processing applications.

JTAG serial scan-path access implements an IEEE standard method for serially scanning the I/O status of each component in a system. Besides allowing the manufacturer to test ICs more easily, quickly, and thoroughly, JTAG has major impact on emulation (see development tools, page 7).

Floating-point support: Any processor, whether fixed- or floatingpoint, can produce results with sufficient resolution via careful

### WHICH FLOATING POINT?

Floating point is simple in concept; but its actual implementation for practical computation with binary words of fixed length is not. The many special cases and exceptions that must be handled include: truncation, roundoff, overflows, underflows, divide-by-zero, etc. An IEEE Standard (IEEE 754/854) for floating-point numerical processing fully defines how numbers are to be formatted and handled, including rules for handling exceptions.

The ADSP-21020 implements the IEEE standard in 32- and 40-bit floating-point formats. It also implements 32-bit fixed-point and fractional formats. The MAC's accumulator has a fixed-point format (which is a subset of the floating-point standard) with an 80-bit capacity to allow for significant overflows in true 32-bit fixed-point computations.

Support of the IEEE standard has a significant benefit for the ADSP-21020 user: algorithms can be ported between various platforms. For example, an algorithm can be developed, finetuned, and validated on a workstation, then ported to a system. The identical results will occur if the system platform and software also support the standard. On the other hand, results can differ significantly when one or the other platform does not support the standard; biased rounding and differences in exception handling can build up errors through repeated executions of arithmetic operations.

Figure 1: ADSP-21020 block diagram.

algorithm structure, manipulation of the numbers, and numerical analysis. For example, an 8-digit, fixed-point calculator can produce results with more than 8 significant figures if the user breaks the calculation into parts, performs scaling and descaling, etc. Though usable, fixed-point format can result in inefficient coding and execution. Thus, as users employ higher-speed- and -resolution a/d converters, a fixed-point DSP becomes more difficult to program effectively for real-time applications.

Floating-point processors are easier to use in equipment design, allowing a quicker time-to-market than processors that do not support the format. In fixed-point operation, the programmer (or compiler) must carefully scale, observe range restraints, and be alert for the inevitable scaling and ranging errors. Some estimates indicate that fixed-point scaling, ranging, error handling, and debugging can take 30% of the programmer's time.

Floating-point data formats easily extend the precision and dynamic range of DSP and permit a wider range of algorithms to be used. Many algorithms (such as those used in compression and decompression of digitized analog signals, or for speech recognition) were originally developed to operate on well-behaved signals bounded by many constraints. The present trend toward increased flexibility, with fewer constraints on the behavior and dynamic range of the intermediate results of the algorithm, necessitates floating-point operation. Examples include adaptive filtering, image processing, and more general voice-related applications. Other applications with low signal-to-noise ratios, such as radar and sonar, need wide dynamic range to process accurately the many computational steps required to extract signals from noise without accumulating excessive error.

But fixed-point DSPs are by no means dead. They are inherently less expensive and consume less power—and are well-suited for applications needing less precision or with properly bounded signals, as in modems and other voice-band applications.

Open memory architecture: The ADSP-21020 is designed to handle large amounts of memory off chip. This is done to avoid the constraints that limited on-chip memory imposes on the development and upgrade of floating-point algorithms for signal processing. It also facilitates the use of high-level languages and multitasking operating systems. An on-chip high-performance cache, operating with two data-address generators, enables parallel access to two off-chip memory spaces on every cycle.

## **ARCHITECTURE**

There are three independent computation units (Figure 1): an arithmetic-and-logic unit (ALU), a multiplier with fixed-point accumulator (MAC), and a shifter. The units are connected in parallel (not serially) and the output of any unit on one cycle can be the input of any unit on the next cycle. A 10-port register file is used for transferring data among computation units and data buses, and for storing intermediate results.

The ADSP-21020, like the fixed-point ADSP-2100 family, has a Harvard architecture, which provides for two independent memories—one for data, the other for program instructions and data. Within the DSP there are two independent address generators; one supplies a 32-bit address for data-memory data; the other provides a 24-bit address for program-memory data. A program sequencer with a 32-word instruction cache allows the ADSP-21020 to access data from both data memory and program-memory and fetch an instruction—in the same cycle, without any delay.

There are five external hardware interrupts, eight software interrupts, and nine internally generated interrupts. Interrupt service requests can be nested up to four deep. Many of the registers in the ADSP-21020 have alternate registers (shadows) which hold duplicate data; they retain the existing data during interrupt servicing when context is switched. A programmable timer provides periodic interrupts, counting down from a 32-bit count register (automatically reloaded).

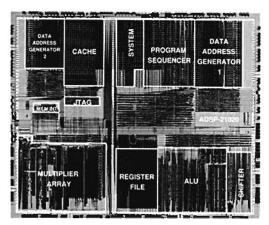

The ADSP-21020 is built on a 200  $\times$  200-mil die with 300,000 transistors (Figure 2) and is housed in a 223-lead plastic pin-grid array package. Two grades are available: -80 (50-ns instruction cycle) and -60 (60-ns); and a third, -100 (40-ns) is now available in sample quantity. Prices for -80 and -60 (1s) are \$265 and \$195.

The ADSP-21020 was designed by a team headed by Doug Garde, at Analog Devices' Norwood, MA, DSP facility.

Figure 2: ADSP-21020 chip microphotograph.

# ADSP-21020 vs. PIPELINED PROCESSORS

For repetitive computations, pipelined architectures can increase overall performance by allowing one instruction to be executed, while the next instruction (or instructions, depending on the length of the pipeline) is fetched and decoded. Similarly, data is pipelined to increase throughput.

For applications with predictable program flows, such as digital filtering, pipelines give the benefits of higher effective throughput without proportional speedup in processor cycle time. Other applications include many-step, deterministic numerical algorithms common in equation-solving.

But pipelines can have the opposite effect in many signalprocessing applications. Every time the program diverts from a normal linear flow—such as at the end of a loop (or nested loops), or when an exception or out-of-bound condition occurs—the program must jump to a new code sequence. To do this, the now-incorrect numbers that resulted from previous instructions must be "flushed out" of the pipeline.

This latency wastes processor cycles and negates any benefit the pipeline may have provided. It's especially apparent in such applications as matrix inversion, which has a regular computational structure but often generates exceptions (overflow, underflow). Pipelines also make programming more difficult, since data flow within the processor must be carefully tracked.

The ADSP-21020 achieves its performance without the use of an internal arithmetic pipeline; all *numeric* operations are completely executed within a cycle, leaving no intermediate data. Instructions require three steps (fetch/decode/execute) and can be pipelined.

# Numerical C Speeds Code Development and Execution

# High-level language is tailored for vector and matrix arithmetic, critical in signal processing

The major reasons for a system designer to use a high-level, standardized programming language are ease-of-use, portability between platforms, maintainability (ease of modifying a program), and time-to-market for the user's end product. Three variations of the popular C high-level programming language are attracting the attention of DSP systems engineers—"standard" C, Numerical C, and C++. ANSI Numerical C, a language that addresses the implementation of signal and numerical processing, is the most interesting, since it efficiently handles vector and matrix data, frequent subjects of signal-processing algorithms. Analog Devices has named its Numerical C compiler DSP/C<sup>TM</sup>.

### THE C PROGRAMMING LANGUAGE

C was created in the 1970s at AT&T's Bell Labs. Its generality, and the easy portability of C programs between hardware and operating system platforms, caused its popularity to grow for diverse applications on many machines and embedded systems.

Compared to many other HLLs, C is fairly "low-level" in that it understands a small set of basic objects (integer and floating-point data types) and manipulates them with an equally basic set of logical and arithmetic operations. As a result, it is relatively "small" and provides a solid foundation upon which more-complex objects and more-powerful operations may be built. It provides facilities, such as structure definitions, unions, arrays, etc., for defining objects beyond the basic set; and ramified operations may be implemented in functions defined by the user or contained in libraries.

During the 1980s, because of the growing popularity of C and the virtues of standardization, ANSI (American National Standards Institute) formed the X3J11 committee to prepare a draft standard for the C language. Besides the language itself, the committee proposed a set of standard library functions that provide the programmer with higher-level functions for performing input/output, storage allocation, control, and mathematical operations (such as sine and cosine). Many of today's C compilers come with libraries of these "standard" functions; other libraries provide functions for special purpose applications such as graphics, serial communications, and DSP.

### NUMERICAL C

Numerical C, an upwardly compatible superset of Standard C, is currently being drafted as an ANSI Standard, X3J11.1, slated to be published for comment in 1992. It will aid software developers for signal-and numerical processing by adding vector data types and vector operator extensions to the C language.

Numerical C allows vector and matrix algorithms to be expressed

in a natural way and efficiently compiled to match the vector capability of a processor. This language is especially effective if the target processor is a DSP that contains hardware support for both fast arithmetic and vector addressing & manipulation—like the ADSP-21020. With the Analog Devices DSP/C compiler, which supports Numerical C on the ADSP-21020, the HLL compiles directly to the processor instruction set. The result is optimal treatment of looping, pipelining, parallelism, and array addressing. It also incorporates DSP data types such as complex numbers (a + bj), and fractional numbers (1.31, for example).

It can simplify programming in such new functional areas as unary vector-sum and vector-product, and binary dot-product & autocorrelation. These functions permit operations such as matrix multiplication to be specified with a single line of code instead of a series of nested loops. Table 1 gives an example comparing C and Numerical C. The availability of additional data types such as complex and fract also simplifies coding of DSP algorithms.

Table 2 shows an example of DSP/C and the resulting compiled ADSP-21020 assembly language. Other extensions to ANSI Standard C included in Numerical C will allow compilers to perform optimizations as effective as those achieved with optimizing Fortran compilers. All major DSP vendors are developing Numerical C links to their chips; Analog's DSP/C, scheduled for production release in early 1992, is one of the first.

The Numerical C development team at Analog Devices is headed by Kevin Leary.

# DSP/C solution:

```

mvmultiply()

{

y[;] = \(\lambda[;](;) * \(\xi[;]);

}

```

# ANSI C solution:

```

mvmultiply()

{

int i, j;

int sum, inca;

for (i = 0; i< nrA; i++) /* column */

{

inca = i * ncA;

sum = 0.0;

for (j= 0; j < ncA; ++) /* row */

sum += A(inca + j) * x(j);

y(i] = sum;

}

}</pre>

```

Table 1. DSP/C™ and ANSI C source code compared: matrix vector multiplication example.

## DSP/C program statement:

```

float delay[N], *circ delay_ptr, c[N];

fir_filter()

{

output=aum(delay_ptr(;)*c[;]);

}

```

# Compiler-generated assembly code

```

FirFilter:

Array selection operator determines

i0=coef; starm addresses, stride, and loop count

f9=0.0;

f1=0,f4=fm(i0,m0),f5=pm(i8,m8); "do" instruction sets up do

lcntr=4, do lll until lce; loop for no-overhead (unplug

lll: f1=f1+f9,f9=f4*f5,f4=dm(i0,m0),f5=pm(i8,m8);

f1=f1+f9;

DAG automatically updates freg and

performs modulo operation

```

Table 2. DSP/C and ADSP-21020 assembly code generated by compiler: FIR filter example. Note similarity of assembly code to mathematical operations to be performed.

# Development Tools and Third-Party Support for Floating-Point DSP

Industry-wide support for ADSP-21020 includes hardware, software, and algorithm development

Successful development of a processor-based product requires more than just the processor and its data sheet or User Manual. Effective development tools and third-party software and hardware support are critical, especially in the algorithm-intensive applications of digital signal-processing.

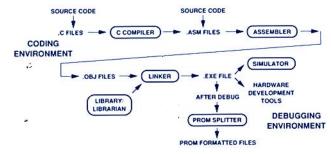

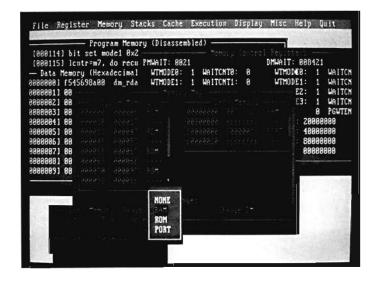

The available development tools for the ADSP-21020 are similar to those for the fixed-point family, but extended as required for floating-point. The software tools for the coding and debugging environment (Figure 1) are available in a PC-based development software package, the ADDS-210XX-DSW-PC. A Sun-platform version will be available soon.

The Macro assembler creates object files from the processor's assembly source code in the form of relocatable COFF (Common Object File Format) files. It accepts conditional assembly directives, as well as macro and listing directives, as part of the source file. The algebraic syntax (similar to that for the fixed-point ADSP-2100 family) facilitates coding of DSP algorithms.

The Linker processes separately assembled object files to create a single executable program. It assigns memory locations to code and data in accordance with a user-defined architecture file that describes the memory and I/O configuration of the target system. Input to the Linker consists of one or more object files in COFF format produced by the ADSP-210XX family Assembler and/or Library files. The Librarian allows the user to group frequently used object files into a single library file for input to the Linker.

The Simulator executes an ADSP-21020 program in software in the same way that an ADSP-21020 processor would in hardware. It provides a window-oriented graphical user interface (GUI), an extension of the one used by the improved ADSP-2100-family simulators. Most commands are accessed from pull-down menus with a mouse. Input to the Simulator consists of an executable file produced by the Linker—and an architecture file, to simulate a specified memory and I/O configuration.

Figure 1: Programming environment.

The PROM Splitter reformats an executable program into files that can be read by a PROM programmer. PROMs can then be programmed for use in the user's ADSP-21020 system.

The Development Software package, bundled with the optimizing C Compiler and Runtime Library (ADDS-210XX-BUN-PC) includes the Assembler, Librarian, Linker, Simulator, and PROM Splitter described above. It also includes an ANSI C compiler, which complies with the ANSI specification—as verified with the Perennial and industry-recognized Plum-Hall validation suites. Offering a variety of options for optimization and runtime support, it takes advantage of the ADSP-21020 high-level-language-compatible architectural features. It also comes with a runtime library of over 100 standard and DSP-specific functions.

Hardware support: The EZ-ICE™ Emulator (ADDS-21020-EZ-ICE) provides the DSP system developer with a low-cost software debug environment that allows non-intrusive access to the internal ADSP-21020 registers via a JTAG interface (see box). The use of on-chip emulation features allows the EZ-ICE to emulate any target system reliably.

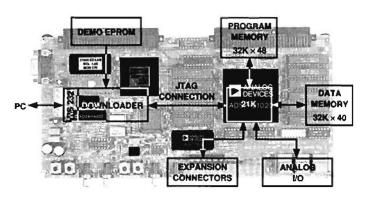

The EZ-LAB<sup>14</sup> Evaluation Board (ADDS-21020-EZ-LAB) (Figure 2) is a complete, general-purpose, stand-alone ADSP-21020 system with program and data memory. It also features analog I/O via codecs—A/D and D/A converters, to provide a complete analog-to-DSP-to-analog signal processing system. The download path from the PC enables the user to download and run user-developed and other programs directly on the EZ-LAB<sup>14</sup>. When used in conjunction with the EZ-ICE Emulator, it forms a powerful software debugger.

Figure 2: Block diagram of EZ-LAB.

7

### THIRD-PARTY SUPPORT

No single DSP vendor can provide the variety of software and hardware support to meet the needs of all users. To help satisfy the diverse and specialized needs of ADSP-21020 users, Analog Devices has worked with various third party vendors to provide additional tools. § Here are some examples:

# Spectron Microsystem: SPOX Operating System

The SPOX real-time DSP operating system provides a real-time kernel and libraries that enable software developers to work with objects relevant to signal processing such as vectors, filters, and streams. In addition, SPOX addresses the broader needs of real-time system designers through general-purpose features such as device-independent I/O, interrupt management, and multitasking support.

Spectron's recently announced OSPA—an Open Signal Processing Architecture— defines a robust set of CISC or RISC-to-DSP communications protocols, which will standardize the bost-to-DSP interactions in applications ranging from imaging and audio to multimedia workstations.

Combined with powerful high-level languages, like ANSI's Standard C and Numerical C, Spectron's products provide for portability of DSP application software across a wide variety of processors and hardware platforms. Simplifying applications development, they also preserve a user's investment in code development.

## Comdisco: Signal-Processing Workstation

The Signal Processing Worksystem, for development of signal processing applications at the systems level, is an environment that provides integrated and interactive design, simulation, and implementation for the development of DSP and communications systems.

Comdisco's Code-Generation System can generate C code linked with efficient assembly-language routines targeted for the ADSP-21020. Using the Signal-Processing Workstation, designers can move quickly from high-level system design to actual, in-place code on the DSP processor.

# • LSI/SSP: PC plug-in System Board

8

This IBM PC plug-in board from Loughborough Sound Images/ Spectrum Signal Processing includes an ADSP-21020 and up to 640 K words of both program and data memory. Like other Loughborough products, the System Board has a DSP-Link expansion port and two channels of 16-bit analog I/O. The software interface to the board is through a user-friendly Windows 3.0 debug monitor.

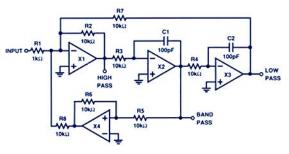

# Momentum Data Systems: FDAS Filter Design and Analysis System

FDAS combines a filter-design package with system analysis software. IIR filter designs include Butterworth, Chebyshev, and Bessel characteristics. FIR filter designs include window functions. The system-analysis features allow transfer function characteristics to be determined, including: magnitude, phase, group delay, log magnitude, impulse response, and pole/zero locations. The FDAS system is available with source code generation for the ADSP-2100 and -2101 fixed-point DSPs, and ADSP-21020 floating-point DSP; it generates files to interface to the Spectrum/ Loughborough system boards supporting these processors.

§For information on how to get in touch with these vendors, call Analog Devices DSP Applications, at (617) 461-3672. Or circle 3

# • Hyperception: Hypersignal Workstation.

This is an integrated DSP software package for filter design, simulation, and real-time analysis, generating source code for the ADSP-2100, -2101, and -21020. Processing and analysis software includes FIR/IIR filter design, math functions & signal arithmetic, and FFT processing. Hypersignal-Workstation works with the Loughborough/Spectrum system boards to create real-time functions and PC-based instrumentation—including a dual-channel digital oscilloscope & spectrum analyzer with continuous data acquisition.

The single-user price for ADDS-210XX-DSW-PC development software for the PC is \$995; ADDS-210XX-BUN-PC with C compiler is \$2195; the EZ-ICE™ Emulator is \$2995 (Spring, 1992); and the EZ-LAB™ Evaluation Board is \$995.

EZ-ICE Emulator efforts were led by Russ Rivin and Chris Russell; EZ-LAB Evaluation Board design was led by Steve Cox and Kapriel Karagozyan; Development Software by Dave Lannigan and Michael Allen; C compiler by Steve Kafka and Marc Hoffman; Runtime Library by Gordon Sterling and Josh Kablotsky; Development-Tool Engineering is led by Kevin Leary.

# **JTAG AND EMULATION**

IEEE Standard 1149.1 is a boundary-scan technique developed by the Joint Test Action Group (JTAG). The primary purpose of this standard is to make it easier to test systems—both high-density PC boards and ICs—via a "probeless" technique. The basic test bus comprises just four signals: Test Data In, Test Data Out, Test Mode Select, and Test Clock; the Standard also defines additional optional lines.

In the ADSP-21020, JTAG circuitry within the IC is accessed for emulator support via a connector from the IC to the edge of the EZ-ICE™ Emulator's PC board. The JTAG feature—significant among floating-point DSPs—permits the emulator to access all registers and states of the ADSP-21020, to write to and read from external memories, and—not just performing passive monitoring—to take control of the IC, with no degradation of target timing. Thus JTAG builds inherent emulation into the DSP IC, simplifying the design of EZ-ICE, which need not be a large, complex add-on emulator.

Contrast this with a conventional plug-in emulator:

- the plug-in emulator is electrically intrusive: it affects critical timing, loading, capacitance

- full-speed emulation requires fast memory to avoid wait states (by the way, emulators for the fixed-point ADSP-21XX series are indeed full-speed)

- its mechanical structure is often unreliable or awkward

- it is relatively costly.

Though a trace function is not available, the benefits of JTAG emulation in capability, fidelity, reliability, and cost are significant for processor users who must emulate as part of the debug cycle.

# References:

"Adding testability also aids debugging," EDN, August 2, 1990. IEEE Standard 1149.1 Designer's Reference, High-Performance Systems, August 1989.

# Single-Supply In-Amp for Automotive Applications

# Rugged AD22050 has wide common-mode range, meets automotive supply-voltage range and protection specs

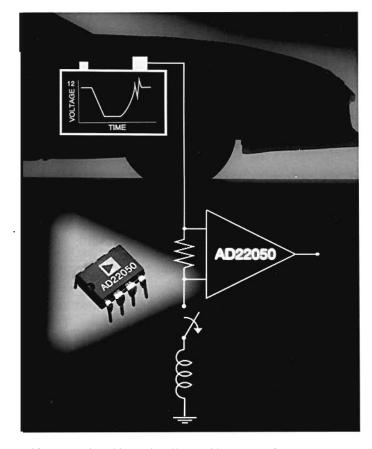

The AD22050\* monolithic instrumentation amplifier is one in a series of products designed to survive and maintain precision despite the environmental rigors of automotive applications. In the last issue, we described the AD22001† "bulbwatcher," which senses lamp and indicator failures; our next issue will feature a unique surface-micromachined accelerometer IC with precision on-chip signal conditioning and test facilities.

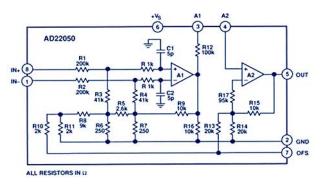

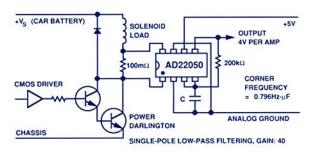

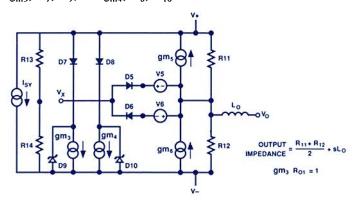

The AD22050 (Figure 1) is a single-supply differential amplifier with an accurate factory-programmed gain of 20 V/V. Its midscale ("zero") point can be set accurately via an Offset terminal—a necessity for bipolar signals in single-supply circuitry. In automotive applications, the device is useful for sensing current (via voltage across low-resistance shunts) in motors, solenoids, and valves—as well as for interfacing and conditioning output signals from pressure transducers, position indicators, strain gages, and other low-level signal sources.

Consisting of a subtractor with gain of 10 V/V and a follower with gain of 2, its accurately preset overall gain is 20 V/V. The gain can be modified with external circuitry to provide any gain in the range from 1 to 160 V/V. Besides its internal transient-spike protection and RFI filtering, the user can readily provide up to 3 poles worth of low-pass filtering with simple external circuitry.

Figure 2 shows a typical application circuit, in which the AD22050 measures the average current through a solenoid, which is pulsed on and off. The average input voltage across the measuring shunt is of the order of 100 mV, while the common-mode voltage ranges from about 1 V above ground—when the transistor is saturated—to about 1.5 V above the battery voltage, when the transistor is cut off and the diode conducts. If the battery voltage spikes up to +20 V, the common-mode voltage can be as high as 21.5 V, which can be readily handled by the AD22050, even with a +5-volt supply.

To measure current with floating shunts, an instrumentation am-

Figure 1. Simplified schematic diagram.

plister must be able to handle a wide range of common-mode voltage (CMV) with high common-mode rejection (CMR) and low drift. The AD22050 has a common-mode range of from below ground to  $6 \times (V_S - 1.0 \text{ V})$ , with performance specified for a  $\pm 24$ -volt minimum (and  $\pm 1.0$ -V maximum) CMV range with a  $\pm 5$ -V supply. CMR is a minimum of 80 dB for low frequencies and 60 dB at 10 kHz. Offset voltage, referred to the input, is a maximum of  $\pm 1$  mV at  $\pm 25$ °C—and  $\pm 3$  mV over the specified  $\pm 40$  to  $\pm 125$ ° operating temperature range. Default gain is  $\pm 10$  V/V  $\pm 10.5$ % at  $\pm 25$ °C, and  $\pm 1$ % over temperature.

An amplifier for automotive applications must be capable of operating (or at least surviving) over a wide range of supply-voltage variation. The AD22050 will operate at supply voltages from +3 V to +36 V and will survive a reverse supply voltage of -34 V. Its output can be indefinitely shorted to ground, and the device will survive a peak input voltage of 60 V for 40 ms. It is packaged in 8-pin plastic DIPs and SOICs and can be stored at temperatures from -65°C to +150°C. Price begins at \$3.90 in 100s, and is typically \$1.80 in automotive quantities.

The AD22050 was designed by Analog Devices Fellow Barrie Gilbert for ADIIs Automotive/Sensors Group in Wilmington MA.

Figure 2. Typical application—current-sensor interface.

<sup>\*</sup>For technical data, use the reply card. Circle 4 †For technical data, use the reply card. Circle 5

# Disk-Drive ICs— Optimized for Read-Channel and Servo Loop Control

Read channel: AD897 integrates peak detector, data synchronizer.

Servo loop: Single-chip AD7774 provides multichannel analog L/O

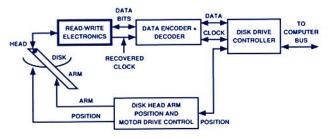

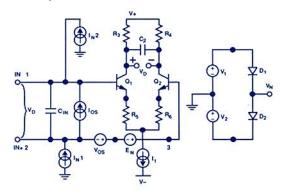

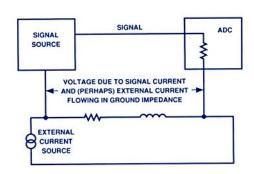

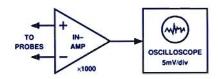

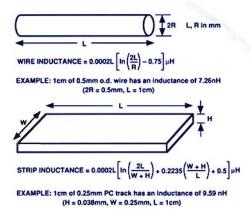

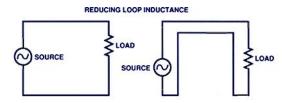

Hard-drive head circuitry has two major analog paths (Figure 1): the head-positioning control-servo loop and the read/write signal path (called the read channel, because most of its circuitry is for recovery of data from the disk). Two new monolithic IC chips are designed to meet these needs. The AD897 provides many of the functions of the read/write path; and the AD7774 Analog I/O Port contains a combination of analog/digital and digital/analog converters designed to meet the needs of the servo control path.

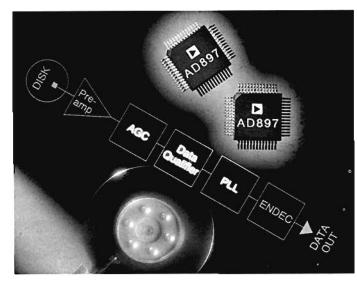

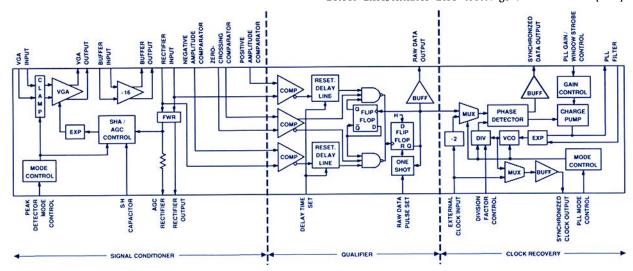

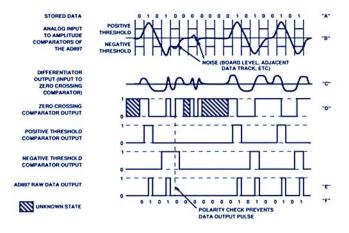

### **READ CHANNEL: THE AD897**

The AD897\* (Figure 2) is the newest descendant of the AD890 & AD891 (Analog Dialogue 22-1, 1988). The read channel, a sophisticated signal recovery-and-detection path, must amplify a low-level, noise-corrupted signal with widely varying amplitude and noise level (due to the mechanics of the disk). The recovered

Figure 1: Block diagram of a disk-drive system.

signal must then be qualified as valid data using a variety of criteria and a suitable clock (recovered from the data bits).

For an input signal from the head preamplifier, the AD897 provides signal conditioning, data qualification, and data synchronization at rates up to 40 megabits per second. It provides a 24-dB-gain buffer, a variable-gain amplifier (VGA) with up to 30 dB of gain—automatically set by an automatic gain-control loop (AGC) having 40 dB of gain range and programmable attack and decay times. The device provides three levels of data bit qualification—and a phase-locked-loop (PLL) for extracting bit timing from the data bits. The IC provides for external filters, configured by the user to match the data rate, media characteristics and other system requirements.

The AD897 qualifies data by amplitude threshold, time above amplitude threshold, and data polarity to ensure minimum bit error rate, a key system-level spec for drive read channels.

Amplitude (level) qualification is performed in level-comparators by comparing the normalized signal with a user-set threshold. Each comparator then drives a resettable delay line, to effect the "time above threshold" qualifier. After the recovered signal has been validated by these first two criteria, a comparator is used to detect differentiator zero crossings and clock a flip-flop if the

Figure 2: AD897 functional block diagram.

<sup>\*</sup>For technical data, use the reply card. Circle 6 †For technical data, use the reply card. Circle 7

signal has the correct polarity. The validated data event triggers a one-shot to produce the final, validated, timed data pulse—of width set by an external resistor. Figure 3 shows the operation of the qualifier for RLL 1,7 code (the most demanding); the AD897 also handles standard codes such as MFM and RLL 2,7.

Figure 3: AD897 Operation.

A key feature of the AD897 is the dead-zone-free data synchronizer PLL; it has four modes of operation: external clock, lock-to-data-preamble (frequency lock), lock to data (phase lock), and a three-state (coast) mode which holds the loop's filtered error voltage with low droop and avoids transients during mode switching. The three-state mode is useful when the read head is jumping across areas of the disk and there is no data to lock onto.

Performance: Besides its 40-Mb/s data transfer rate capability, the AD897 features 500-ps maximum additional pulse pairing and 0.1-dB/ms gain drift in the *coast* mode. The PLL has  $\pm 1$ -ns maximum window uncertainty, and no VCO startup phase error. The AD897, packaged in a 52-pin quad flat pack, will operate at temperatures from 0 to  $\pm 70$ °C. Its high-volume price is \$7.50.

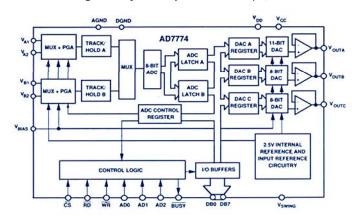

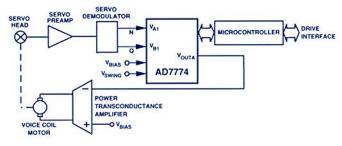

### SERVOLOOP: AD7774

The monolithic AD7774† combines (Figure 4) multiple channels of a/d and d/a conversion, output amplifiers, internal reference circuitry, and microprocessor interface. Though optimized for servo-control in hard-disk drives, it can be used generally in closed loop position-control. Included are a 4-channel 8-bit ADC (sharing two track-holds) and three d/a converters (two 8-bit and one 11-bit). Inputs can be sampled either independently or in simultaneous pairs.

External voltages independently set three key parameters: the

Figure 4: AD7774 Block diagram.

midpoint of the ADC transfer function (offset, or bias in disk-drive parlance), the input voltage swing of the ADCs (span), and the midpoint output voltage of the DACs (offset). Adjusting the offset and span matches the converters to the application; for example, the input and output voltages may be referenced to a point other than analog ground in single-supply applications.

Disk-drive applications: In disk drives with a dedicated servo track (Figure 5), the servo demodulator produces two positive voltages (N and Q, for normal and quadrature), with amplitudes of ( $V_{BIAS} \pm V_{SPAN}$ ), from the data patterns read from the surface. Using the AD7774's simultaneous sampling, they are converted—without introducing significant phase delay errors—to provide the servo microcontroller with position—and track-crossing information, from which velocity can be derived.

The four channels of the AD7774 can be used for processing signals from two demodulators, or two channels can be used for a single demodulator while the other a/d conversion channels are used for measuring current, temperature, calibration, etc.

To position the head assembly in drives, a voice coil motor is generally used. One d/a converter, with resolution of up to 11 bits, is usually sufficient for both modes: seek (going to a new track) and track (following an acquired track position). In the AD7774, the high-resolution DAC is used for the voice coil while the lower-resolution DACs are used for programmable control of the loop filter—or other functions calling for programmable gain.

The AD7774 operates from +5-V and +12-V supplies. Fabricated in LC<sup>2</sup>MOS, which combines precision bipolar circuitry with low-power CMOS logic, it is available in a 28-pin DIP and 28-terminal PLCC. Price is well below \$18 in large volumes.

The AD897 was designed by Wyn Palmer and Janos Kovacs at Analog Devices in Wilmington, MA. The AD7774 was designed by a design team consisting of Philip Quinlan (Lead Designer), Hooman Reyhani, and Hiro Yamaguchi, with chip layout by Edel McMahon and Stuart Meakins, at Analog Devices' facility in Limerick, Ireland.

Figure 5: Typical dedicated servo loop.

# 3 New S/H Chips for Fast, Accurate Data Acquisition, and 8-Channel Distribution

AD9100 has a 30-MSPS encode rate; the AD682 dual guarantees 12-bit dynamic performance; SMP-18 multiplexes 8 channels

by Peter Predella

Analog Devices has introduced three important new sample/trackand-hold (S/H and T/H) amplifiers. Two are well-equipped for the demanding task of capturing signals that vary too quickly to be properly digitized by an a/d converter alone, and the third serves in multi-channel data distribution. Applications include r-f sampling, direct digital synthesis, ATE, and data acquisition.

Why a track/hold (T/H)? There are many reasons: an ADC may need it to catch a rapidly varying signal and maintain a constant input value during conversion, or to establish precisely the time associated with the converted data, or to obtain a train of regularly spaced data points for digital-signal-processing. In d/a conversion, a sample-hold is used to minimize glitches and as an accessory to non-double-buffered DACs for handling rapidly varying data; also, multiple sample-holds may be a low-cost alternative to multiple DACs for distributing data from the output port of a digital system to two or more analog channels.

If a signal changes by more than one-half of a least-significant bit (LSB) during a conversion, the converted value may no longer accurately represent the input existing at the time the conversion command was received. Performance can be improved by using a faster converter or one having an internal track-hold,\* or—with a given converter—using an external T/H to acquire the signal and hold it during the conversion. The maximum sine-wave frequency  $(f_{max})$  that can be converted with n-bit resolution without introducing more than 1/2-LSB error is related to the conversion-time uncertainty (T) thus:

$$f_{max} = 2^{-(n+1)} / T \pi$$

For example, a 12-bit converter that completes a conversion in 1  $\mu$ s may have significant error at frequencies above 39 Hz! If a track-hold with an aperture uncertainty of 1 ns (and an acquisition time in microseconds) is introduced ahead of this converter, the maximum frequency will increase to 39 kHz.

Dynamic performance: In high-speed applications, dynamic errors in converting high-frequency sine-wave signals are associated with noise and distortion—and reduced signal-to-noise ratio [SNR, sometimes known as S/(N+D)]. Since distortion of sine-wave (or sum-of-sine-wave) signals adds Fourier components, the spectrum of a distorted converted signal contains spurious peaks signifying harmonics, aliases of the higher harmonics (as well as

†Use the reply card for data. Circle 8

intermodulation sum-and-difference products and their aliases)—and random noise (including components caused by aperture jitter). A properly designed- and employed T/H amplifier will greatly reduce both spurious signals due to distortion and random noise caused by the original jitter.

# **VIDEO SPEED, 12-BIT PERFORMANCE**

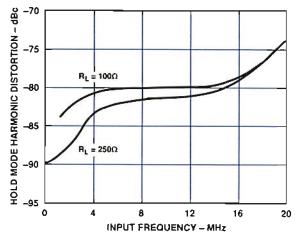

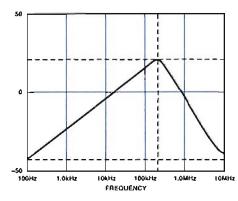

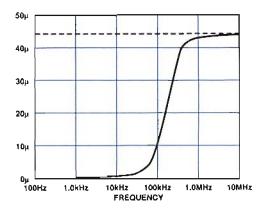

The AD9100† is the industry's fastest T/H amplifier with true 12-bit performance. At 30 megasamples per second (MSPS), its timing characteristics and dynamic performance are unmatched (see Table 1). Using a new (patented) closed-loop architecture built on a high-speed complementary-bipolar (CB) IC process, the AD9100 offers low distortion, yet maintains the slew rate specs of traditional open-loop designs. Maximum acquisition time of a 2-V signal to within 0.01% is 23 ns (16 ns typical). With an encode rate of 30 MSPS, hold-mode distortion is specified for input frequencies up to 20 MHz (Figure 1).

Table 1. Comparative Key Specifications

| Model:               | AD9100                                             | AD682           | SMP-18       | Units   |

|----------------------|----------------------------------------------------|-----------------|--------------|---------|

| Sample Rate          | >30                                                | 0.5             | 0.2          | MSPS    |

| Track Mode Dynamics  |                                                    |                 |              |         |

| Bandwidth (-3 dB)    | 250 (160 min)                                      | 4 (1-FP)        |              | MHz     |

| Slew Rate            | 850 (550 min)                                      |                 | 6            | V/µs    |

| Hold Settling Time   | 0.011                                              | 0.5             | 1            | μs, max |

| Aperture Delay       | +800                                               | <b>-25</b> ± 10 |              | ps      |

| Aperture Jitter      | <l< td=""><td>75 max</td><td></td><td>ps</td></l<> | 75 max          |              | ps      |

| Acquisition Time     |                                                    |                 |              |         |

| to 0.01% (2 V step)  | 16 (23 max)                                        |                 |              | ns      |

| to 0.1% (6 V step)   |                                                    |                 | 2.5          | μς      |

| to 0.01% (10 V stcp) |                                                    | 0.7             |              | μs, max |

| Droop Rate           | l (6 max)/μs                                       | 1/ms max        | 2 (40 max)/s | mV/(t)  |

| Hold offset          | ±1 (±5 max)                                        | -1 (+3, -4 max) | 4 (6 max)    | mV      |

| Output Drive         | ±60 (±40 min)                                      | ±5              | 10           | mA      |

| Power Dissipation    | 1.25 max                                           | 0.32 max        | 0.05         | W       |

| Pricing, 100s        | \$69                                               | \$12            | \$6.95       | US      |

|                      |                                                    |                 |              |         |

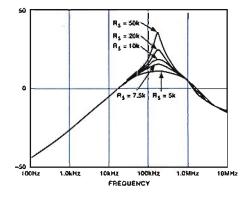

Figure 1. AD9100's Hold-mode distortion as a function of frequency.

The AD9100 can extend the dynamic range of 8- and 10-bit flash converters, as well as higher-resolution moderate-speed data-acquisition converters, to encode signals at up to 30 MSPS. Its applications include direct RF/IF sampling, imaging systems, peak detection, spectral analysis, and buffering of high-speed converter inputs. The encode clock drive for its patented switching circuitry is differential-input ECL; jitter is less than 1 picosecond. The analog inputs are internally clamped to prevent damage from voltage transients.

<sup>\*</sup>Examples of sampling a/d converters include the AD773, AD1876, and AD7886, introduced in this issue, or the AD1674, introduced in issue 25-1.

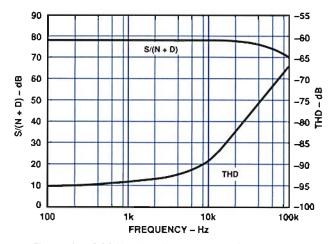

Figure 2. AD682's signal-to-noise performance.

Packaged in a 20-pin ceramic DIP and powered from +5-V and -5.2-V supplies, the AD9100 includes a hold capacitor and decoupling capacitors for the switch's power supply. Grades are available specified for the commercial (0 to +70°C), industrial (-25°C to +85°C), and military (-55 to +125°C) temperature ranges. An LCC package is available for surface-mount users.

## **DUAL S/H WITH 12-BIT DYNAMIC SPECS**

If your next high-speed multichannel application requires two channels of sample/hold with 12-bit dynamic performance, the AD682§ is a highly cost-effective choice. At a 500-ksps sampling rate, guaranteed maximum THD (see Figure 2) and minimum signal-to-noise plus distortion (S/N + D) at input frequencies up to 10 kHz are -80 dB and 72 dB, respectively. For higher frequencies—50 kHz and 100 kHz—the respective THD values are -73 and -68 dB, and for SNR, 73 dB and 67 dB. The AD682's 2nd- and 3rd-order IMD products are -77 and -78 dB.

Like its single- and quad-channel versions (AD781 and AD684), the AD682's combination of frequency- and time-domain (ac and dc) specs make it a first choice for traditional data-acquisition applications as well as sampled-data systems. Consider for example its acquisition time and hold-mode performance: full-scale

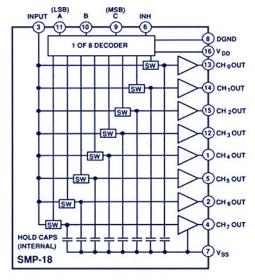

Figure 3. Block diagram of the 8-channel SMP-18.

§Use the reply card for technical data. Circle 9

‡Use the reply card for technical data on the SMP-18 or Application Note AN-204 on the SMP-04/08/18. Circle 10 for data, 11 for app. note

steps of 10-V can be acquired to within 0.1% (10 bits) in less than 600 ns and to 0.01% (12 bits) in less than 700 ns; aperture delay and jitter are  $-25 \pm 10$  ns and 75 ps max; and hold settling time to 1 mV is just 500 ns. Isolation between channels is 90 dB max; and worst-case interchannel mismatch specs are 1.5-mV for voltage offset and 300 ps for aperture time.

Both channels include on-chip capacitors and are configured for unity gain. The AD682 operates from ±12-V supplies and has an input range of ±5-volts. Both commercial (J-grade) and industrial (A-grade) devices are available packaged in a 14-pin DIP. MIL-temp range (S-grade) devices, specified from -55°C to +125°C, are packaged in 14-pin cerdips.

### **DRIVING MULTIPLE ANALOG CHANNELS**

The SMP-18‡, a new octuple S/H amplifier combines an input multiplexer and eight output buffer amplifiers, each with its own hold capacitor, in a single 16-pin DIP or SOIC (Figure 3). When used with an 8-bit, 10-volt-full-scale d/a converter, its 10-mV max buffer offset (20 mV over temperature) is less than 1/2 LSB. The SMP-18 has low nonlinearity (0.01% typical), fast acquisition time (2.5 µs), low droop rate (40 mV/s max, 2 typ), low dissipation, and high immunity to latch-up. Pin-compatible with the SMP-08 (Analog Dialogue 24-3), the SMP-18 provides the same function with nearly tripled speed. Working with a low-cost 8- or 10-bit d/a converter, the SMP-18 readily brings multichannel output to microprocessor-based systems.

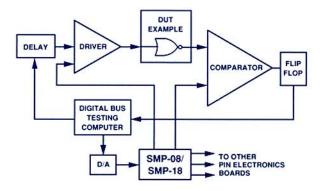

In multichannel applications, including per-pin IC automatic test systems (Figure 4), the SMP-18 is useful for level-setting and scaling circuitry, calibration and de-skew networks, and for manipulating system parameters. Other applications, including multipoint data-acquisition systems and general-purpose memory programmers, can benefit from the SMP-18's compactness. Compared to discrete designs and devices with lesser degrees of integration, the SMP-18 significantly reduces size and cost.

The SMP-18 is TTL/CMOS compatible and operates from either a single +12-V supply or bipolar  $\pm5\text{-V}$  supplies. No external logic components are required for direct interfacing to DACs, since break-before-make switching and decoder logic are included on-chip. The SMP-18 is specified for operation over the extended industrial temperature range, -40 to  $+85^{\circ}\text{C}$ .

The AD9100 was designed by Roy Gosser at ADI's Computer Labs Division in Greensboro, NC; the AD682 was designed by Chris O'Connor at our Wilmington, MA Semiconductor Division; The SMP-18 was designed by Paul Collanton at the PMI Division in Santa Clara, CA.

Figure 4. Typical multi-channel-output application of the SMP-18 in ATE.

# Monolithic 10-Bit, 18 MSPS Sampling A/D Converter with on-Chip Track-Hold

AD773 has a 100-MHz signal bandwidth, -66-dB THD at 1 MHz, only 1.2-W dissipation; is lowest-cost 10-bit video ADC

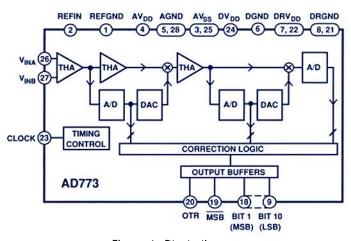

The AD773\* is a monolithic sampling analog-to-digital converter with 10-bit resolution. Combining an input track-and-hold amplifier (THA) and a digitally corrected subranging a/d converter, it is capable of converting video-bandwidth signals, sampling at rates up to 18 megasamples per second (MSPS). The THA's wide frequency range (typically 100 MHz, full-power) is ideal for wideband input signals and in undersampled applications.

For high performance and ease of use, the track-and-hold analog input has high input impedance and a choice of differential- or single-ended operation (Figure 1). This eliminates external buffers and sample-holds, saving power and board space. The reference input is also at high impedance; it will operate with standard 2.5-volt references such as the AD680, AD580, and REF-43. The AD773's dissipation, 1.5 W max (1.2 typical), is among the lowest for 10-bit video a/d converters; and—packaged in a convenient 28-pin ceramic DIP—its price is the lowest: \$55 in 100s (AD773JD).

Figure 1. Block diagram

Applications abound in a gamut of fields. Examples include: high-performance composite and component video—including post-production equipment, video tape recorders, and HDTV; imaging systems—including ultrasound, infrared, and radar; as well as communications and high-speed instrumentation.

The AD773 employs three 4-bit flash a/d converters in a three-stage pipelined architecture, with digital correction logic. This multistage architecture reduces power dissipation and die size—compared to full flash conversion—by greatly reducing the number of comparators. Output data is available in a choice of binary or twos-complement form. The AD773 will flag an out-of-

range signal when the analog input exceeds the full-scale range (nominally 1 V p-p) by 1/2 LSB; though generally useful, this feature is especially desirable in recursively controlled programmable-gain signal conditioning.

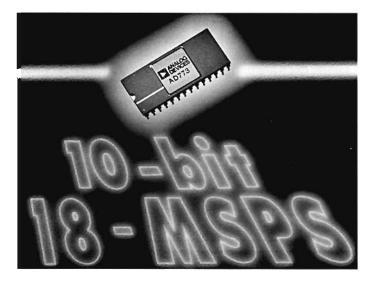

Dynamic performance of the AD773K, sampled at 18 MSPS with 1 and 8.1-MHz sine-wave inputs, includes signal to noise-plus-distortion [S/(N+D)] of 56 dB and 53 dB (typical). Total harmonic distortion for 1 and 8.1-MHz sine waves is typically -66 and -58 dB. Spurious-free dynamic range (SFDR) for 1-MHz input is typically 67 dB, and 2nd and 3rd-order intermodulation products (1.0 and 1.05 MHz inputs) are typically -69 and -61 dB. Figure 2 is a typical FFT response plot. Full-power bandwidth is typically 100 MHz, with settling time of less than one clock cycle for a full-scale swing. Differential phase and gain are 0.2° and 0.4%. Linearity is good over the temperature range: ±2-LSB max integral nonlinearity and ±1 LSB max differential nonlinearity, with no missing codes guaranteed.

Nominal power supply voltages are  $\pm 5$  V; and the AD773 is TTL/CMOS-compatible. Grades now available are J and K, for 0 to +70°C; military temperature-range versions will also be available. For an evaluation board, call your local sales office.

The AD773 design team was led by Peter Real and Dave Robertson at Analog Devices Semiconductor Division's Converter Group, Wilmington, MA.

Figure 2. FFT plot of output for 18-MSPS clock and 8.5-MHz input signal. -60-dB "spikes" are aliases of 2nd and 3rd harmonics.

# Complete 16-Bit DACPORT in SOIC Package Includes on-Chip 10-V Reference

Low-cost AD669's output span is programmable. 16-bit double-buffered latches eliminate glue logic and simplify  $\mu P$  interface

by Peter Predella

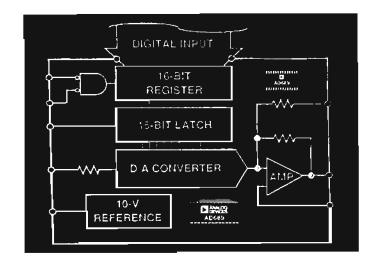

The AD669\* DACPORT™, a complete monolithic 16-bit digital-to-analog converter (DAC), includes a buried-Zener reference, span-programmable output amplifier and double-buffered latches. With it, a 16-bit computer bus can be interfaced to the analog world with a minimum of external circuitry. Applications for the DACPORT include multipoint industrial and laboratory automation and control systems, precision analog signal generation systems, and simultaneous sampling instrumentation. The AD669 can also simplify the upgrade path from 12- and 14-bit interfaces, reducing system design effort and costs.

Guaranteed and tested ac and dc characteristics include monotonicity over temperature to 15 bits, maximum  $\pm 1\text{-LSB}$  integral and differential nonlinearity (B grade), maximum 0.009% THD+N (full scale) and 84-dB SNR. Other key performance specifications include a 30-ns data setup access time and 40-ns write time (to handle a wide range of processors), 15-nVs glitch energy (impulse). For a full-scale input step and a bipolar output swing, the output settles to within  $\pm 0.0008\%$  in just 13  $\mu$ s, with 2-k $\Omega$  output load.

When required by the system, data is loaded into the AD669's first rank of latches in a standard parallel 16-bit format; then the data can be asynchronously transferred to the DAC latches whenever the analog data needs to be updated The double-buffered latches eliminate data skew errors and facilitate multichannel and

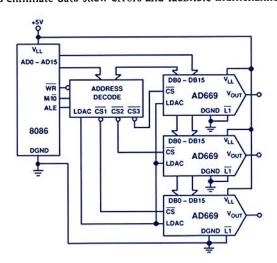

Figure 1. Interfacing the AD669 to an 8086 16-bit micro-processor in a multi-DAC environment—logic connections.

simultaneous sampling applications without the need for external glue logic to microprocessors. Just three control signals compatible with TTL, LSTTL, or 5-V CMOS are needed to control the latches. Figure 1 shows a scheme for interfacing several DACs to an 8086 16-bit microprocessor. The  $\mu P$  can write to each AD669 individually; and all outputs can be updated simultaneously. Processors with speeds up to 10 MHz can be interfaced without wait states.

An internal low-noise buried-Zener-diode circuit provides a stable reference, trimmed for absolute accuracy to within 0.2%. Buffered to drive external circuitry, it can act as a system reference, providing at least 2 mA (and more with external buffering).

The d/a converter portion uses an array of bipolar current sources with MOS current-steering switches to develop a current between 0 and 2 mA, proportional to the applied digital word. The four MSBs are decoded to sum up to 15 equal (1/16-full-scale) current sources; the other 12 bits are scaled with an R-2R ladder, then summed with the MSBs at the buffer amplifier's summing node.

The output amplifier is pin-programmable for unipolar or bipolar span. An on-chip resistor can be externally wired to either the DAC's output for a span of 0 to +10 V, or to the reference input to provide a full-scale -10 V to +10 V range.

Packaging options include 28-pin SOICs (the industry's smallest footprint available among 16-bit DACs), cerdips, and plastic DIPs. Operating temperatures range from -40 to +85°C, and -55 to +125°C. '883 versions will be available. Prices start at \$16 (100s).

The AD669 was designed by Michael Coln at Analog Devices Semiconductor, Wilmington, MA.

Table 1. AD669 Key Specifications

| Grades:              | AN/AR      | AQ/SQ | BN/BQ/BR  | Units      |

|----------------------|------------|-------|-----------|------------|

| Resolution           | 16         | 16    | 16        | Bits, min  |

| INL                  | ±2         | ±2    | ± 1       | LSB, max   |

| DNL                  | ±2         | ±2    | <b>±1</b> | LSB, max   |

| Gain error           | $\pm 0.15$ | ±0.1  | $\pm 0.1$ | % FSR, max |

| Reference error      | $\pm 0.2$  | ±0.2  | ±0.2      | %, max     |

| Unipolar offset      | ±5         | ±5    | ±2.5      | mV, max    |

| Bipolar zero error   | ±15        | ±15   | ±10       | mV, max    |

| Output settling time | 13         | 13    | 13        | μs, max    |

| THD + N              | 0.009      | 0.009 | 0.009     | %, max     |

| Signal-to-noise      | 84         | 84    | 84        | dB, min    |

| Power Dissipation    | 365        | 365   | 365       | mW         |

15

<sup>\*</sup>Use the reply card for data. Circle 13

# **New-Product Briefs**

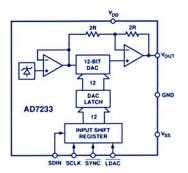

# SERIAL DACS In 12-Bit DIPs & SOICs: AD7233/43 DACPORTs

The AD7233/AD7243\*, industry's smallest complete serial-input 12-bit DACs, are 12-bit DACPORTs<sup>™</sup>—complete, ready-to-interface single-chip voltage-output d/a converters. Using a simple 3-wire interface to most DSP processors and microcontrollers, they can be clocked at up to 5 MHz, for a 300-kHz update rate. Full accuracy is maintained to beyond 100 kHz, since the DACs' maximum full-scale settling time is 10 μs to ±1/2 LSB.

Both devices, fabricated in ADI's linearcompatible CMOS (LC<sup>2</sup>MOS) process, include on-chip buried Zener references and output amplifiers—and have similar performance specs. They differ in pinout, input format, output range, reference connections, controls, and package choices.

Over temperature, both devices have ±0.9-LSB max differential nonlinearity ±1/2-LSB max relative accuracy error (B grade), and are guaranteed monotonic. They dissipate 100 mW. Prices (100s) start at \$7 for both.

AD7233 accepts digital twos-complement input, has an internally referenced -5 V to + 5 V output, and is packaged in an 8-pin mini-DIP. It is available in A and B grades for the -40 to +85°C temperature range.

AD7243 is available in 16-pin plastic DIP, cerdip, and small-outline (SOIC) packaging. Its output is pin-programmable for unipolar (0 to +5 or +10 V) or bipolar (-5 to +5 V: offset binary or twos complement). A CLR input resets the output to zero on command. The reference is jumpered externally, so the AD7243 can can either accept or serve as a reference for external circuitry.

\*DACPORT is a trade mark of Analog Devices, Inc.

Use the reply card for information. Circle 14

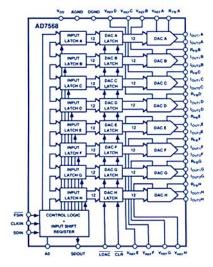

# **EIGHT 12-BIT M-DACS ON A CHIP**

# Serial-input monolithic AD7568: first-in-industry, single +5-V supply, separate reference inputs

The serial-input AD7568† contains an octet of 12-bit current-output 4-quadrant multiplying d/a converters on a monolithic CMOS chip, housed in a 44-pin PQFP. It is powered by a single +5-volt supply and dissipates only 1 mW. Each independently addressable DAC has its reference terminal and feedback-resistor—and both of its current outputs—available for connection; thus each DAC can be configured and operated independently; yet all DACs can be simultaneously updated or reset to zero.

The AD7568 is useful for fixed- and variable-reference applications requiring more than four 12-bit DACs with a common serial digital source. Examples include multipoint automatic testing, process-control systems, audio mixing, battery-powered remote instrumentation

Guaranteed monotonic over temperature, it combines excellent linearity (±1/2-LSB max relative-accuracy error, ±0.9-LSB max

differential nonlinearity) and fast settling (500 ns to 0.01% FSR with the AD843 as output amplifier). It is available in a top-grade "B" version (-40 to +85°C). Price is \$28 in 100s—about \$3.50 per channel.

†Use the reply card for technical data. Circle 15

# **DUAL 18-BIT AUDIO DAC**

# AD1865 has 107-dB min SNR, $16 \times$ oversampling Improved performance over AD1864, same price

The AD1865† is a monolithic dual-18-bit serial-input, voltage-output DAC for digital audio. Complete on a single chip and housed in a 24-pin plastic DIP or 28-pin SOIC package, its two conversion channels include pairs of references, DACs, latches, amplifiers, and scaling resistors; no external components are required.

Salient specifications include: signal-to-noise—SNR (from 20 Hz to 30 kHz) 107 dB min; total harmonic distortion plus noise—THD+N (at 0 dB, 990.5 Hz) 0.006% max; 110-dB minimum channel separation; 0.3% typical interchannel gain matching; 1% max gain error; and 88-dB min D-range. A premium "J"-version, with 0.004% max THD+N, is also available.

Applications include such consumer digital audio entities as compact-disc players, digital audiotape players and recorders, and automotive audio systems; multivoice keyboard instruments and other electronic musical in-

struments; digital mixing consoles for professional studio, recording, and broadcast equipment; and multimedia workstations.

The availability of two complete signal channels on-chip results in cophased voltage or current output signals and eliminates the need for output demultiplexing circuitry. The AD1865 is physically and electrically compatible with, but features improved performance over the earlier AD1864, at the same price. Prices start at \$20.45 in 100s.

# **SINGLE-CHIP DATA ACQUISITION**

# AD771X $\Sigma$ - $\Delta$ family has PGA, 21-bit A/Ds, Direct transducer interface, digital filter

Designed as complete analog front ends for low-frequency measurement applications with transducers—such as strain gages, RTDs, and thermocouples—the AD771X\* family of small, low-cost, monolithic data-acquisition chips performs a/d conversions with 21-bit resolution. Nonlinearity is ±0.0015% maximum with no missing codes; each device includes a software-programmable-gain amplifier (PGA) with a gain range from 1 to 128 V/V. Interfacing is via a bidirectional serial port.

The PGA and  $\Sigma$ - $\Delta$  architecture reduce the need for preamplifiers or front-end signal conditioning. In addition, the device has excellent 50/60-Hz rejection (100 dB min), digital low-pass filtering (software-programmable cutoff frequency), and both internal- and user-writeable self-calibration.

The AD7710\* is designed for low-level signal sources, e.g., strain gages. It has two differential inputs plus a differential reference input that can be used for calibration.

For RTDs, the AD7711† provides two 200µA current sources for excitation, a differential input, and a differential reference input. For handling signals with a wider range of input voltage, the AD7712§ provides attenuation as well as gain.

Dissipation is 25 mW (50-μW power-down); packaging is in 0.3" DIPs and 24-lead SOICs. Prices (AD7712 in 1000s) start at \$11.90

\*†§Use the reply card for technical data. Circle 17 (AD7110), 18 (AD7111), 19 (AD7112)

# QUAD OP AMP

# **OP-497 has industry's** highest precision

The OP-497¶ comprises four op amps combining high open-loop gain, low offset voltage and drift, and low bias current. It is a quad version of the dual OP-297 and single OP-97, well suited for designs needing a number of precision amplifiers, small space, and low power consumption. Typical applications include instrumentation-amplifier designs, photodiode preamplifiers, and amplifiers for thermocouples and strain gages.

Guaranteed specifications include 50  $\mu$ V maximum offset voltage at 25°C, drift of 0.5  $\mu$ V/°C, maximum bias current of 100 pA at 25°C—rising to only 450 pA at 125°C, 2 × 10<sup>6</sup> open-loop gain, and 625  $\mu$ A maximum supply current per channel.

Low offset voltage and high gain eliminate offset trims and additional gain stages in many designs. Battery-powered systems benefit from the OP-497's low supply current, ability to operate from any supply voltage between ±2 V and ±20 V, and 120-dB power-supply rejection. CMR is guaranteed at 120 dB min, with a common-mode range to within 1 V of the supply rails.

The OP-497's superbeta input stages with bias-current cancellation circuitry maintain subnanoampere bias current over the full operating temperature range. This contrasts with FET-input amplifiers; their initially low bias current doubles with each 10°C increase in temperature. Low I<sub>bias</sub> is useful in low-leakage, wide-temperature-range applications such as sample-holds, peak detectors, and log amplifiers.

The OP-497 is available for -40 to +85°C and -55 to +125°C, and in SOIC, LCC, and 14-pin plastic and cerdip packages. Prices start at \$4.75 (100s).

¶Use the reply card for technical data. Circle 21

# $16 \times 16$ ANALOG IC SWITCH ARRAY

# AD75019 crosspoint switch handles up to 24 V p-p Cell-based design allows custom extensions

The AD75019‡, a bidirectional CMOS analog switch housed in a 44-contact PLCC, connects up to 16 inputs to any or all of 16 outputs (256 points). TTL/CMOS-compatible address data is clocked serially—from 20 kHz to 5 MHz—into a 256-bit shift register, then to 256 on-chip latches. Applications exist in test, medical, audio, etc.

With a supply-voltage span of from 9 V to 24 V (unipolar or split as required), the AD75019 is specified at  $\pm 12$  V and  $\pm 5$  V; it will handle signal voltages up to the supply rails. With  $\pm 12$ -volt supplies, it draws a maximum quiescent current of  $\pm 400~\mu$ A; with  $\pm 12$ -V signals, max On resistance is 300  $\Omega$  (150 typical). Leakage current is 2 nA, 10 max ( $\pm 10$ -V signals); and interchannel isolation is 92 dB min for 2-V p-p signals at 1 kHz. Its price is \$15 in 100s.

The number of switches can be increased by cascading AD75019s, connecting SOUT of

one device to SIN of the next. Moreover, the array is a customizable linear system macro (LSM); its cells are all from Analog Devices' BiMOS II standard-cell library. The basic architecture can be adapted using other library cells at much less cost than that to design a custom ASIC. For example, we might add input or output signal buffers or provide a parallel control interface. For information about customized ICs in quantity, call an Analog Devices Sales Engineer.

‡For technical data, use the reply card. Circle 20

# **New-Product Briefs**

# **SAMPLING ADC** 16-bit, 100-ksps, serial, autocalibrated AD1876

The AD1876\* is a 16-bit serial-output sampling a/d converter capable of sampling at rates from 1 to 100 ksps (total conversion time 10 µs, aperture jitter 100-pVs). Designed with a switched-capacitor/charge-redistribution architecture, embodied in 2 chips employing compound monolithic integration (CMI), it is housed in a 0.3" ("skinny") 16-pin plastic DIP. Price is only \$25 (1000s).

The AD1876 has an input voltage reference range of from 3 to more than 7 volts and a full-power bandwidth of 1 MHz. Dynamic specifications include S/(N+D) of 83-dB minimum, 87 typical (48-kHz bandwidth), total harmonic distortion of -88 dB max (0.004%), -95 dB (0.002%) typical. Other ac specs include -89 dB max (-99 dB typical) peak spurious or peak harmonics, 92-dB D-range (-60 dB, A-weighted).

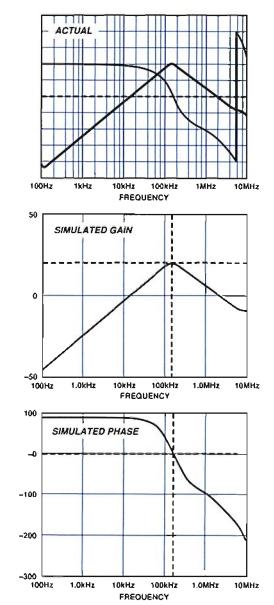

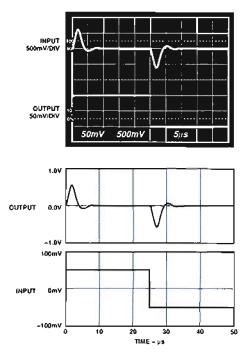

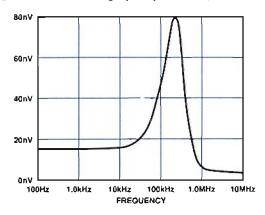

AC performance is also specified for -20-dB and -60-dB input levels. Typical intermodulation products are -102 dB second-order and -98 dB third order.