### **Editor's Notes**

### WHAT IS "APPLICATION-SPECIFIC"?

To a casual reader of the trade press it must seem that the world has gone ASIC-happy. Certainly the ability to develop libraries of standard functional blocks and interconnect them on monolithic IC chips with a few swift strokes at the keyboard and a couple of passes with a mouse is an exciting

prospect; it warrants a great deal of enthusiasm over potential savings of cost and space for both producers and customers. In fact, we at Analog Devices are looking forward to a major role in the high-performance application-specific IC market.

However, before a designer gets carried away with the idea that everything should be done this way and that you aren't really up with the state of the art unless designing a chip that will "do it all," it may be useful to consider what "application-specific" really means and the implications for the designer.

"Application," like "system," is an overused universal word that means different things to different people. To a user, an application-specific circuit is a purchased device or assembled collection of devices that can be used to maximize performance/cost for a given job; it may involve a home-grown kludge, a standard IC, a custom IC, a hybrid circuit, or even a module. In general, to a device manufacturer, an application-specific circuit can be a custom project for one user, a device intended for a specific role in a specific market (e.g., disk-drive data-recovery circuit), or a specialized device distinguished by function or performance—like a log amp or rms-to-de converter.

Standard-cell-based custom ASICs have made their greatest inroads in digital circuitry, where low cost and turnaround time have become the norm. They are beginning to enter wide usage in some aspects of analog circuitry, typically in very-high-volume circuits with low-to-moderate performance and sophistication.

But high-performance analog and mixed-signal custom devices require something more: the same kinds of processes, test capability, and design and applications expertise and experience that are needed to make high-performance general-purpose and application-specific ICs for the merchant market.

Required processing capabilities include as a minimum the ability reliably to make low-drift references and high-input-impedance junction FETs; a combined bipolar-CMOS process to facilitate digital and analog signals on the same chip; a complementary-bipolar process to make possible high-speed analog circuits with excellent de characteristics; and the ability to deposit precision resistors and laser-trim them. Also required are the design know-how to avoid the many pitfalls in predicting circuit behavior by simulation—and the experience in characterizing and testing linear ICs to insure the integrity of the product's performance.

There aren't many manufacturers of high-performance analog and interface ICs who have all of these capabilities, and there are even fewer who have manifested a serious interest in entering this market. That's why we're smiling.

Dan Sheingold

#### THE AUTHORS

Wyn Palmer (page 3 and page 8) is the engineering manager for diskdrive and video products at Analog Devices Semiconductor (ADS), which he joined in 1984. Earlier he had worked in the area of disk-drive design at DEC and Data General. He is a graduate of the University of Leeds, and the University of Southampton, in

England. His accomplishments at ADS include the AD840 highspeed op-amp family, as well as the disk-drive and rms circuits described in these pages. He enjoys gardening and hi-fi.

Phil Carrier (page 3) is a Product Marketing manager in the Linear Operations Group at ADS, working with analog signal-processing and temperature-transducer ICs. Earlier he had worked in applications and sales at ADI's Component Test Systems Division. Phil has a BSEE from the University of Massachusetts at Amherst. His

hobbies include fresh-water fishing and woodworking.

Charles Kitchin (page 8) is a technical writer in the Amplifier and Analog Signal Processing Group at ADS, producing data sheets, technical articles, and sales-support literature. Chuck was graduated with an ASET from Wentworth Institute in Boston and has been studying Electrical Engineering at the University of Lowell's

Evening Division. His hobbies include astronomy, wine tasting, and restoring WWII military radios.

Will Drachler (page 8) is a Product Marketing Engineer in the Linear Group at ADS, working with analog signal-processing and transducer products. He holds a BS in Electrical Engineering from the Rochester Institute of Technology, with a concentration in Economics. When not working, he enjoys athletics and refinishing furniture.

(More Authors on Page 33)

## analog dialogue

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Published by Analog Devices, Inc. and available at no charge to engineers and scientists who use of think about L.C. or discrete analog, conversion, data hardling and display circuits and systems. Correspondence is welcome and should be addressed to Editor, Analog Diulogue, at the above address Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577, Telex 174059, or cable ANALOGNORWOODMASS.

## DISK-READ ICs CONDITION AND DELIVER BITS AT 50 MBITS/s

## AD890 Provides AGC Over Wide Range of Input Amplitudes AD891's Precise Comparators and One-Shot Pinpoint Output Signal

by Wyn Palmer and Phil Carrier

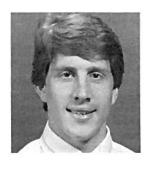

The AD890 Precision Wideband Channel Processing Element\* and AD891 Rigid-Disk Data Qualifier\* are a pair of application-specific integrated circuits (ASICs) designed for use between the head readback preamplifier and data decoder of high-performance disk drives. Starting with the noise-corrupted and distorted signal from the disk head, these monolithic components produce error-free digital bits at rates up to and beyond 50 megabits/second (Mbits/s). With low-cost, user-provided reliable passive filters to shape the signal, the response of the read-channel circuitry can be matched to the data rate, the medium, and drive-mechanism characteristics.

The AD890 and AD891 remove a major impediment to realizing the potential of high performance drives in computer systems: the rate at which data bits can be recovered from the disk platter and passed on to the computer system. Increases in performance and capacity have been achieved by decreasing the track-to-track spacing, increasing the bit density within tracks, and using runlength-limited codes<sup>1</sup> that increase the amount of data represented by each group of flux reversals on the disk.

Until now, disk-read electronics, using either IC or discrete component designs, could accept data from the disk surface and reliably decode it into the original bits at maximum rates limited to 10-25 Mbit/s. However, with proper design, the interface between the drive and the computer bus is capable of much faster rates than the rate at which bits can be retrieved from the disk surface itself. The bus interface design is selected to match the disk capabilities and system needs, which range from lower-speed asynchronous designs to high speed, fully synchronous circuits. Any substantial improvement in overall data transfer speed has required significant improvements in the disk-read electronics, to avoid underutilizing the larger disk's capacity.

Extracting this data requires a combination of analog signal processing and digital circuitry. It is ironic that the original data bits were essentially ideal digital signals, and were stored to be used again as digital signals—but they must be recovered in the much more complex world of analog circuitry because of the non-ideal nature of the disk mechanism and magnetic data storage.

Though the physical distance between disk and head is small, the technical situation is analogous to a long-distance communications system that transfers data by radio or satellite from one continent to another, subject to varying noise and signal fading. Interestingly, the precision automatic gain control (AGC) developed for the AD890 can also be used in non-disk-drive applications, such as the front ends of communications receivers.

The disk-data-recovery circuitry needs to handle low-level, highrate signals in a very unfavorable and noisy environment, and maximize the data transfer with acceptably low error rates. Uncorrected, raw bit error rates (BER) must typically be 1 in 10<sup>11</sup> or

\*Use the reply card for technical data on these devices.

\*EDN, Mar. 31, 1987, "Run-Length-Limited Coding Increases Disk-Drive Capacity,"

### IN THIS ISSUE

Volume 22, Number 1, 1988-36 Pages

| Editor's Notes, Authors                                                       |                                         |

|-------------------------------------------------------------------------------|-----------------------------------------|

| Disk-Read ICs Condition and Deliver Bits at 50 Mbits/second (AD890, AD891).   |                                         |

| Precision Bipolar Op Amp Has Lowest Offset, Drift (AD707)                     |                                         |

| Low-Cost True-RMS Chips Also Compute AC-Average Response (AD736/7)            |                                         |

| True 18-Bit DAC in Hybrid Package Has Small Size, Low Cost (AD1139)           |                                         |

| 12-Bit A/D Converters for DSP Provide Complete Interface (AD1332/1334)        |                                         |

| Monolithic Digitally Programmable Delay - 8-bits-to-Time Converter (AD9500) . |                                         |

| 15 New CMOS Switches and Multiplexers in Convenient Variety (ADG Series).     |                                         |

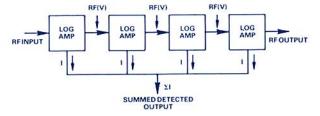

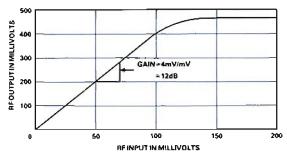

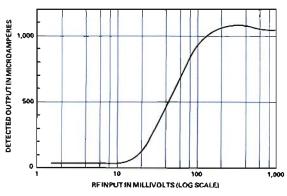

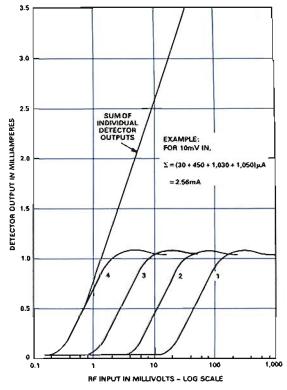

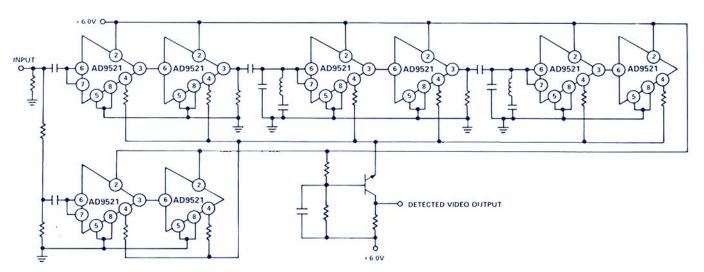

| Fast Monolithic Log Amp with Better Than 250-MHz Bandwidth (AD9521)           |                                         |

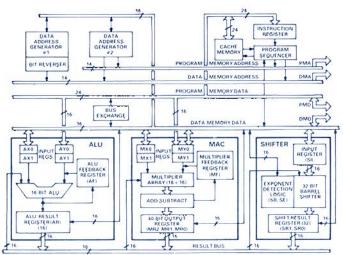

| Faster DSP Microprocessor: 1,024-Point Radix-4 FFT in 3.0 ms (ADSP-2100A)     |                                         |

| CMOS Video DACs Provide Memory, Interface, and 3 Outputs (ADV471/478).        |                                         |

| Monolithic 12-Bit Quad Voltage-Output Readback DAC (AD664)                    |                                         |

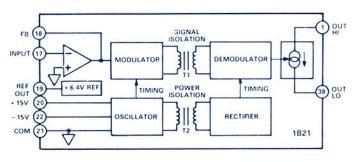

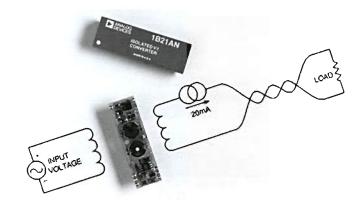

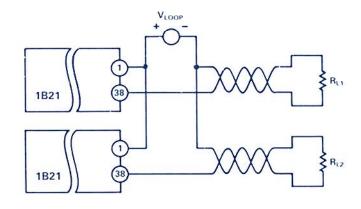

| Voltage-to-Current Isolator with High Accuracy (IB21)                         |                                         |

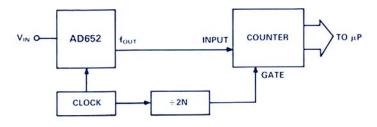

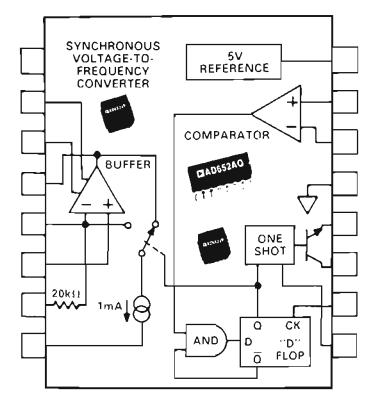

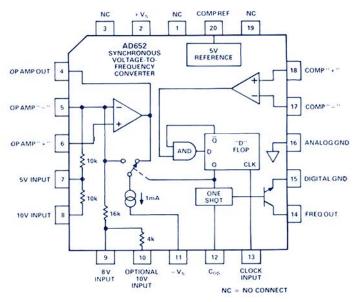

| AD652: Improved Monolithic Synchronous V/F Converter                          |                                         |

| 12-Bit Monolithic CMOS ADC Guarantees 3-us Conversion Time (AD7672)           |                                         |

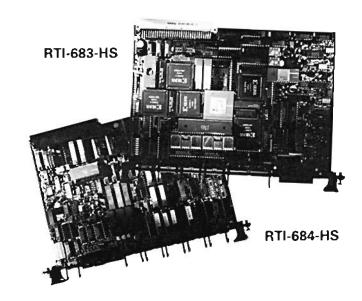

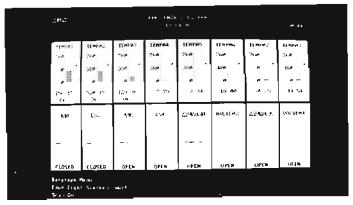

| VMEbus Video Digitizer Boards to Match Your Source (RTI-683/684-HS)           |                                         |

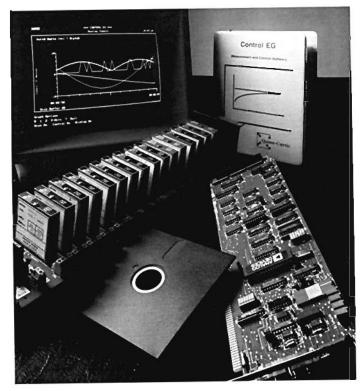

| Data-Acquisition and Control Software for PC Plug-Ins (Control EG-AC1904) .   |                                         |

| New Benchtop-Tester Enhancements Include High-Accuracy Op-Amp Board           |                                         |

| New-Product Briefs:                                                           |                                         |

| 8-MIPS Multibus II Array Processor Based on ADSP-2100 (RTI-980)               | 2                                       |

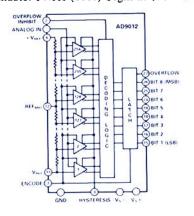

| 100-MHz 8-Bit Flash Converter is TTL-Compatible (AD9012)                      |                                         |

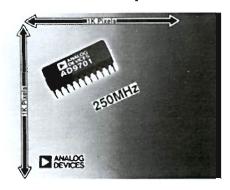

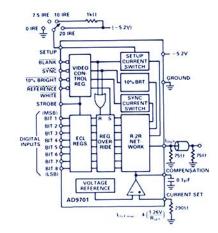

| Monolithic 8-Bit Video DAC has 250-MHz Update Rate (AD9701)                   |                                         |

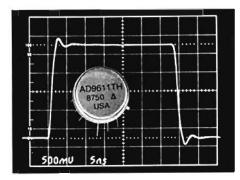

| The AD9611 280-MHz Op Amp: 7-ns 1% Settling, Low Distortion                   | 3                                       |

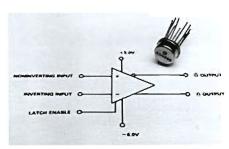

| High-Speed TTL Comparator Has 7-ns Propagation Delay (AD9686)                 |                                         |

| Lowest-Cost Complete Voltage-Out 8-Bit DACPORT, +5-V Supply (ADS              |                                         |

| Isolated, Linearized Thermocouple Input Module: J, K, T, E, R, S, B (5)       | 111111111111111111111111111111111111111 |

| 12-Bit, 1-MHz Tracking ADC in a DIP: NMC Over Temp (AD9003)                   |                                         |

| Complete 15-µs 12-Bit ADC, Pin Compatible with AD574A (AD674A) .              |                                         |

| Analog Devices Names 3 New Fellows: Jody Lapham, Bob Tsang, Mike Tuth         |                                         |

| More Authors                                                                  |                                         |

| Worth Reading                                                                 |                                         |

| Potpourri                                                                     |                                         |

| Advertisement                                                                 |                                         |

better despite these challenges:

- The signal from the disk head is small and noisy. Amplification boosts signal levels but can do nothing to improve the signalto-noise ratio—may even make it worse.

- The signal level varies considerably (as much as 40 dB), depending on the instantaneous distance between the head and disk surface. This distance is continuously changing by small but significant amounts, as a result of mechanical tolerances and variations as the disk rotates.

- The shape of the signal from the Read head is not optimum for data recovery; it may change, depending on many factors. High-frequency spectral components are attenuated, and the signal spreads out in time, resulting in overlap with adjacent pulses (1's) or pulse-absences (0's).

- Temperature variations in the drive cabinet can cause circuit performance to drift.

- The timing of the data signals is not exact; minute variations in drive speed and mechanical eccentricities introduce jitter.

- At rates greater than 20 Mbits/s, recovering data bits reliably is always a challenge to the circuit designer, even when the data bits are relatively noise-free and stable. Propagation delays and phase shifts alone seriously affect performance; with temperature or time instabilities, the difficulties are compounded.

### FUNCTIONS IN A DATA-RECOVERY SYSTEM

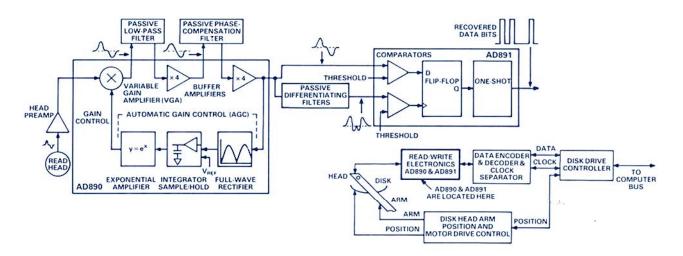

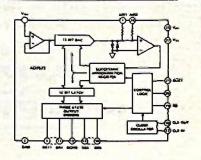

The functional blocks of the AD890 and AD891 are shown in Figure 1, along with typical signal waveforms at key points. Encoded binary signals are recorded as magnetic flux reversals; they occur at specific points in the medium. The output of the Read head is a band-limited voltage proportional to the derivative of the flux. The low-level signal from the Read head is amplified by an external preamplifier, located close to the head.

The preamp output goes to a critical element, a variable-gain amplifier (VGA). This amplifier provides continuously variable gain or attenuation over a wide range of 40 dB, depending on the signal level, controlled to produce an output at precisely the level required for optimum operation of the subsequent filters and comparators that make the 1-or-0 data-bit decision. The control

signal for the VGA comes from an automatic gain control (AGC) circuit, a feedback loop that measures the output, compares it with the desired level, and continously adjusts the gain of the VGA to maintain the desired output level.

An amplified and properly leveled signal from the Read head is not yet ready to be decoded into error-free 1's and 0's. Accordingly, the *read*-head signal from the VGA goes through filtering and gain stages, including gain-of-4 buffers. The purpose of low-pass filtering and equalization is to shape the signal amplitude and phase spectra to compensate for distortion, phase shifts, and nonlinearities in the data -writing and -reading processes (e.g., head coil inductance, mechanical arm resonances).

The design of these intermediate filters is quite critical to the specific application and must be done by the drive manufacturer based on the characteristics of the particular disk technology and head design employed. This represents, in effect, the value that must be added by the manufacturer to achieve low error rates through proper equalization-filter design<sup>2</sup>.

The signal from the buffer and filter stages is used in two ways: it goes to the AGC circuit as part of the closed-loop level control, and it continues through the signal processing chain for extraction of the actual binary data.

The AGC circuit has a full-wave rectifier to measure the output of the VGA and derive an output proportional to the average deviation. The rectifier output is subtracted from a reference—or amplitude set-point—and integrated; the result is applied to an exponential function, then multiplied by the input to control the VGA gain. The integrator provides filtering and insures zero average error in the steady state, and the exponential factor is used so that steady-state integrator output increments correspond to equal percentage changes of input rather than to the actual wideranging magnitude of change.

The attack and decay rates at which the AGC changes gain in response to signal amplitude changes must be matched to the application to keep the response from being either too slow (inadequate gain tracking) or too fast (instability and gain "pumping"); this is accomplished with an external capacitor that adjusts the integration time constant.

Figure 1. Disk output bit-recovery system. Simplified diagram shows chip functions, auxiliary filter circuitry, and waveforms at key points.

<sup>&</sup>lt;sup>2</sup>Heselett-Packard Journal, January, 1984, "Second-Generation Disc Read/Write Electronics."

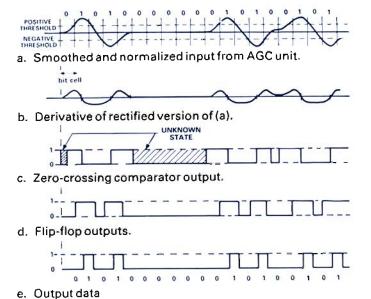

After the filtering and equalization, the data is ready to be extracted. The signal is differentiated to locate the peaks (zero crossings of the derivative); when the derivative of the signal is at zero, the signal waveform should be compared to the "valid signal" threshold (Figure 2a - 2c). Both the original signal and the differentiated signal are passed to threshold comparators.

The threshold level is set low enough to qualify valid pulses, but high enough to ignore noise. The amplitude comparator output goes to a D-type flip-flop clocked by the derivative comparator; a flip-flop output transition corresponds to a data bit; (a one-shot resets the flip flop shortly thereafter). The flip-flop transition drives a one-shot that finally produces data output pulses of precise width. These pulses are accurate counterparts of the data bits originally recorded on the disk surface; they can be decoded and error-corrected using standard high-speed digital circuitry. The one-shot's stability is critical at these high rates since even slight drift or jitter can look like false bits and lead to errors in the decoder and timing-recovery circuitry of the disk controller.

A useful data recovery circuit needs some additional features. To avoid saturation by the high-level Write fields, an input clamp is applied to the read circuit when writing to the disk by reducing the impedance of the input stage to a very low value; at the same time, the integrator can be switched to a hold mode to preserve the value of gain. This minimizes disturbance to the AGC and VGA and assists in producing a rapid recovery after writelread switching. The ability to externally set VGA gain is also useful in test and for specific application modes.

### **DESIGN AND PERFORMANCE OF THE AD890**

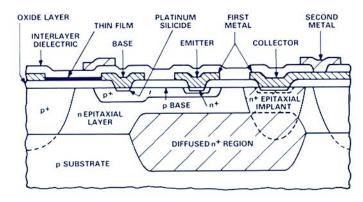

The key to the design and performance of the AD890 Precision, Wideband, Channel Processing Element is a 4-GHz FLASH bipolar process that uses double-level metallization and lascr-trimmed thin-film resistors (Figure 3). This combination provides stable and predictable currents in bias circuits, and the ability to compensate for temperature variations in gain and comparator offset. Bandgap voltage references provide the required stability. When operating at 50 Mbits/s and higher rates, achieving high performance depends as much on stability, predictability, and low jitter as on such traditional parameters as noise, bandwidth, and

Figure 2. Data qualifier examines signal level at time of waveform peak to determine if valid bits are present.

Analog Dialogue 22-1 1988

maximum slew rates.

The AD890 is essentially a precise 100-MHz AGC with up to 40 dB of gain-control range (+30, -10). The r-f path is fully differential for optimal high-frequency performance and minimal distortion. Three gain cells are provided: a 30-dB (nominal maximum) variable-gain block, and two 12.75-dB buffers. The two buffer stages simplify the low-pass filter and equalizer design.

The outputs of the gain stages are emitter followers capable of driving 200-ohm differential networks. The variable-gain amplifier's full-scale gain setting is trimmed to 30 dB ±0.6 dB and remains within 0.25 dB of nominal over the full operating temperature range. Wideband gain is maintained to within 1 dB of nominal at 50 MHz, at gains up to 26 dB below full-scale gain setting. Together, these three gain cells offer the best performance available in monolithic designs for this application.

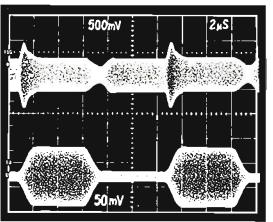

As an AGC, the AD890's essentially single-time-constant feed-back loop provides highly predictable attack and decay characteristics in response to input steps. With an external integrating capacitance of 1,000 pF connected, attack and decay times are about 1µs. The low-to-high and high-to-low gain transients are essentially identical, and independent of the initial gain setting, thus providing a nearly ideal AGC action (Figure 4). The single pole also ensures no overshoot or ringing. The AGC characteristics are gain-compensated so as to make the settling time essentially independent of transient magnitude.

Figure 3. Cross section of FLASH-process die showing twolevel metallization and laser-trimmed thin-film resistors.

In the AGC gain-setting section, the full-wave rectifier has 100-MHz bandwidth; for accouracy, its de offset is trimmed to less than 10 mV in manufacturing. The full-wave rectifier design allows easy, accurate amplitude detection of signals intended to provide servo positioning information to the disk arm. A single external capacitor can adjust the peak-to-average ratio of the full-wave rectifier. The rectifier output and a precision reference voltage are differenced in an averaging, high gain integrator-sample/ hold circuit for accurate AGC operation. A second full-wave rectifier in the AD890 can be used to generate a threshold output used for creating a data qualification level.

The gain acquired during AGC can be "held" (set via control lines) to minimize signal degradation during data regions. When in hold mode, the decay rate for the AGC is about 0.2 dB per ms, or about 0.02 dB for an average 100-µs sector length, a gain change of less than 0.2%. As an alternative approach—and for test purposes—the AD890 can be used in a mode selected by the control lines, not as an AGC, but as a very accurate programmable

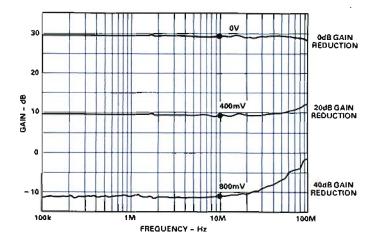

gain amplifier with 55.5 dB of VGA and buffer gain with 0 V on the gain control pin, and a gain-reduction rate of 1 dB for each 20-mV decrease in the control voltage. Performance is trimmed and temperature-compensated.

The variable-gain amplifier has an equivalent input noise figure of only 5 nV/ $\sqrt{\text{Hz}}$ , while the "gain of 4" buffers have a noise figure of 7 nV/ $\sqrt{\text{Hz}}$ . The AGC control is linear to within  $\pm 0.5$  dB over a 26-dB AGC range for the full bandwidth, and has excellent performance to 40 dB of range, Figure 5. Its fast and clean response to an input step can be seen in Figure 4.

Another critical feature is the input clamp, operated during data writes to the disk. When the clamp is activated (via the mode control lines), the input impedance of the amplifier falls to about 8 ohms, greatly reducing the input resistance/coupling capacitance time constant. Also, with 200  $\Omega \parallel 0.1 \mu F$  source impedance driving the input (a typical source value), differential input signals are attenuated by more than 34 dB. This greatly assists in producing a rapid recovery after read/write switching.

### **DESIGN AND PERFORMANCE OF THE AD891**

The AD891 is basically a very fast, single-bit a/d converter, which provides output pulses corresponding to zero-crossing events of sufficient magnitude to exceed a threshold value. It is fabricated in temperature-compensated reduced-swing ECL, which exhibits typical propagation delays of 0.6 ns per gate. The output's ECL data pulse has standard 10KH ECL logic levels. It can drive a 75-ohm transmission line, if properly terminated.

The signal from the AD890 arrives through a second-order discrete-delay-line and differentiator, which is made of passive components and provides identical time delays through both the undifferentiated and differentiated data paths. This scheme permits the signal amplitude to be qualified at the zero-crossing time. The second-order design also provides uniform magnitude and phase-delay/group-delay characteristics, up to about 60% of the resonant frequency. This minimizes dispersion of the processed readback data coming from the AD890 and prevents degradation in error rates. The 2nd-order section also provides a high-frequency rolloff, useful in rejecting high-frequency noise.

This design qualifies the pulse by both level and time. Level qualification is performed on alternating half cycles of the data waveform via a user-defined threshold level, applied to a pair of ultra-fast comparators with 3-ns propagation delays (only one

AGC RESPONSE

INPUT STEP

Figure 4. Response of AGC to step input.

Figure 5. VGA gain versus frequency as a function of control voltage – showing linear 20 dB/400-mV gain sensitivity.

shown in Figure 1—the upper one), matched to better than 300 ps. A third comparator (the lower one in Figure 1), for derivative zero-crossing detection, provides the time qualification.

Since a comparator with significant offset will produce a double pulse ("pulse pairing") in real waveforms with non-infinite slew rates, the offsets of the comparators in the AD891 are trimmed to less than 250µV to minimize this error source. The offset and delay characteristics of the comparators are carefully controlled to remain constant over temperature; a bandgap reference provides temperature stability. The timing error contributed by the AD891 from offset, gain, and drift is less than 1 nanosecond.

The outputs from the amplitude qualification comparators are applied to the "D" inputs of two master-slave flip-flops (one shown in Figure 1), clocked by the outputs from the zero crossing detector/comparator. Each valid zero-crossing event causes a one-shot—with a user-definable period—to be triggered. This delays resetting of the flip-flops, preventing detection of additional zero-crossing events until the one-shot period ends. Simultaneously, an output one-shot is activated; its leading edge is synchronous with the change in D-flop outputs.

The user-definable period of this one shot is intended to insure adequate output-pulse duration for transmission to the users' data decoder. The period of each one-shot, ranging from 5.4 ns to 180 ns, is set by a single resistor; all the one-shots are trimmed to ensure predictable settling of the pulse periods. The final output of the IC is a 10KH ECL-compatible pulse, which corresponds to the detected zero-crossing, with a 7-ns delay.

Both units require  $\pm 5$ -volt power and dissipate less than 500 mW. For operation on  $\pm 5$ - and  $\pm 12$ -volt power, only five resistors and one diode are needed: four resistors for level-shifting the TTL mode control lines, and one resistor and a diode to reduce internal power dissipation under maximum operating voltage conditions. The AD890 is housed in a 24-pin Cerdip package or 28-pin plastic leadless chip carrier (PLCC), while the AD891 is available in either 14-pin Cerdip or a 20-pin PLCC. Price of each drops to well below \$10 in quantities of 10,000.

## PRECISION BIPOLAR OP AMP HAS LOWEST OFFSET, DRIFT

AD707 Series Has max Offsets & Drifts as Low as 15  $\mu$ V, 0.1  $\mu$ V/°C Open-Loop Gain is typically 13 V/ $\mu$ V with CMR of 140 dB

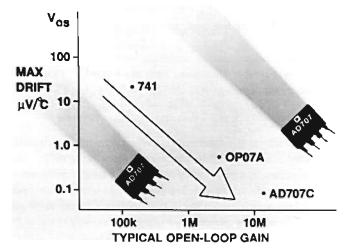

The AD707 op-amp\* sets a new standard among high-deprecision devices for designers who require low input offset voltage and drift, low noise, high open-loop gain, and high common-mode rejection. The highest performance grade, AD707C, with less than 15-μV offset, is the first bipolar monolithic op amp specified to have offset voltage drift below 0.1 μV/°C. Its deaccuracy specifications are comparable to those of chopper-stabilized amplifiers, but with less noise and far lower cost.

Higher accuracy and precision benefit the designer by tighter error budgets at lower cost through the elimination of offset trim components and the associated time required for trimming. Even the lower-cost, relaxed-spec grades, AD707J and AD707K, provide significant performance improvements over industry-standard op amps: the AD707J has typical input offset voltage of  $30~\mu\text{V}$  with drift of  $0.3~\mu\text{V}/^{\circ}\text{C}$ ; for the AD707K (best price/performance choice), offset is  $10~\mu\text{V}$ , with  $0.1~\mu\text{V}/^{\circ}\text{C}$  drift.

The high open-loop gain (8 V/ $\mu$ V min and typically 13 V/ $\mu$ V) and 140-dB typical common-mode rejection (CMR) of the AD707C make it ideal for applications such as precision instrumentation amplifiers. This open-loop gain is maintained over the full 10-V output range when driving a 1,000-ohm load. As shown in Figure 1, the gain and gain linearity are better over the output range than for comparable industry-standard op amps.

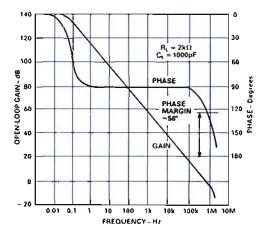

Open-loop gain and phase shift as a function of frequency are shown in Figure 2. Unity gain occurs at 0.9 MHz, with a phase margin—the difference between the measured phase shift and 180° at the unity-gain frequency—of 58°.

Offset current for most grades drifts less than 1 pA/°C, while the input bias current has a maximum value of 1 nA for the C-grade device. Power supply rejection (PSR) is at least 120 dB—and is typically 10 dB greater than that minimum figure.

Noise is a critical parameter for de precision op amps; both low-frequency and wideband noise are specified. Input voltage noise in the 0.1 to 10 Hz band is 0.35  $\mu V$  peak-to-peak (max-

Figure 1. Linearity error of the AD707 and other precision do op amps (ADI test results).

imum), guaranteed by test; at 1 kHz, the noise spectral density is less than 11 nV/ $\sqrt{\text{Hz}}$ . Input current-noise spectral density is typically 0.12 pA/ $\sqrt{\text{Hz}}$  (0.17 nA/ $\sqrt{\text{Hz}}$ , max) at 1 kHz.

Output impedance of the AD707 series is low: for closed-loop gain of  $\pm 1$ , it is essentially a 5  $\mu$ H inductance (1 m $\Omega$  at 33 Hz, 1  $\Omega$  at 33 kHz) and, for gain of 1,000, it is essentially 5 mH in parallel with 30 ohms (1  $\Omega$  at 33 Hz). With a 10-k $\Omega$  load, the output can swing to within 1 volt of positive and negative rail for power supplies from  $\pm 3$  V to  $\pm 22$  V.

For a de-optimized op amp, the AD707 is surprisingly fast. The closed-loop bandwidth of the AD707 (unity gain) is at minimum 0.5 MHz, and typically 0.9 MHz. It can settle to 18 bits within 100 µs, with a typical slew rate greater than 0.3 V/µs.

The AD707 family is available in 7 performance grades and several packages: 8-pin plastic mini-DIP, small outline, hermetic Cerdip, and hermetic TO-99 metal cans, for temperature ranges of 0 to +70°C, -40 to +85°C, and -55 to +125°C. S- and T-grade devices are available processed to MIL-STD-883B, Rev. C. Prices (100s) begin at \$1.25/\$3.25/\$16 (AD707JN/KR/CQ).

The AD707 family was designed by Moshe Gerstenhaber, at Analog Devices Semiconductor, Wilmington, MA.

Figure 2. Open-loop gain and phase versus frequency

<sup>\*</sup>For technical data, use the reply card.

## LOW-COST TRUE-RMS CHIPS ALSO COMPUTE AC AVERAGE

## Measure 200-mV-RMS LF & Audio Signals with 100-µV Resolution AD736 Has Buffered Voltage Output; AD737 Saves Battery Power

by Chuck Kitchin, Will Drachler, and Wyn Palmer

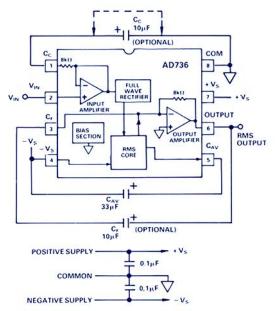

The AD736\* and AD737\* are flexible new monolithic rms-to-dc converters combining low cost, small size, and low power drain. They replace discrete designs, saving board space and assembly cost in multimeter, audio, automatic-gain-control, and many portable-equipment applications. They are housed in a choice of 8-pin plastic small-outline and minidip packages, for 0°C to 70°C grades—and in Cerdip for -40 to +85°C grades. Prices start at \$3.58 in 100s for both the AD736JN and the AD737JN.

They are members of a family of monolithic rms-to-dc converters that started with the AD536 (Analog Dialogue 11-2, 1977). The AD736 is a complete low-impedance-voltage-output device, while the AD737—designed for very low power-drain applications—has a power-down control input for standby currents as low as 40 µA

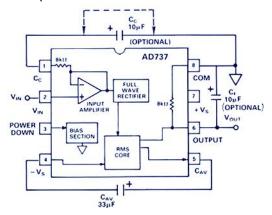

The AD736, shown here connected for true rms, has a buffered output.

b. The AD737 omits the output buffer, has power-down control to minimize drain on power supply.

Figure 1. RMS-to-dc converter block diagrams.

maximum, and it omits the output buffer amplifier. Even without this feature, both devices require little quiescent power, 200 and 160  $\mu$ A (AD736 and AD737) with  $\pm$ 5-volt supplies.

Depending on how they are connected, these devices will compute either mean absolute-value, root mean-square, or instantaneous absolute-value measures of an ac or de input voltage:

$$\frac{1}{T} \int_{-T/2}^{+T/2} |y(t)| dt \qquad \text{or} \qquad \sqrt{\frac{1}{T} \int_{-T/2}^{+T/2} y(t)^2 dt} \qquad \text{or} \qquad |y(t)|$$

### HOW THEY WORK

RMS is a direct measure of the power or heating value of an ac voltage: if an ac (or ac + dc) signal of any peak value and shape has an rms value of 1 volt, it will produce the same amount of heat in an R-ohm resistive load as will 1 volt of steady dc voltage. In this sense, rms is a universal measure of a signal. Some excellent wideband rms measuring units have been built that use the heating effect; however, it does not stack up as a good general-purpose approach for practical low-power, low-cost, wide-dynamic-range IC measuring devices.

Analog Devices rms-to-dc converters† solve the rms equation by analog computing; that is, they continuously produce the absolute value of the signal to be measured, square its magnitude, then take the average and square-root it. Since the measurement is performed continuously, an averaging (low-pass) filter is used to approximate continuous averaging instead of computing the definite integral indicated above. The time constant of of the filter is established by the user—with externally connected capacitance—to serve the needs of the application.

Figure 1a illustrates the process. An input buffer amplifier provides a choice between a high-impedance (FET) buffered input

<sup>\*</sup>Use the reply card for technical data

<sup>†</sup>For further information on root-mean-square advantages, concepts and devices, see RMS-to-DC Conversion Application Guide, 2nd edition (1986) available from Analog Devices FREE upon request—and ADI's classic: Nonlinear Circuits Hundbook (1974), \$5.95.]

and a lower-impedance (8-k $\Omega$ ) input having wider dynamic range and bandwidth. The signal is full-wave rectified and applied to an "rms core," which consists of a set of logarithmic diodes in a temperature-compensated configuration; they perform the squaring and square-rooting. Terminals are furnished for connection to the averaging capacitor,  $C_{AV}$ . Output (AD736) is via a buffer op amp, with provision for an optional external feedback capacitor,  $C_{F}$ , which can provide additional filtering in the rms mode and basic filtering in the full-wave-rectifier mode.

If  $C_{AV}$  is not connected, the computation is in effect the square root of the square of the absolute value of the input—which in the ideal case is simply equal to the absolute value of the input. With no capacitors, the output is the unfiltered instant-by instant absolute value; but with feedback capacitor,  $C_F$ , connected, the device measures the *mean* absolute value (average rectified value).

If the measurement is a purely "ac" measurement, i.e., if it must ignore the average (or dc) level of the input waveform, the input may be capacitively coupled. When the high-impedance "+" input is used, connect an optional ac-coupling capacitance,  $C_{\rm C}$ , from pin 1 to ground to eliminate errors due to input offset and drift, insuring a resolution of 100  $\mu V$  or better.

Figure 1b shows the basic circuitry of the AD737 connected for true-rms computation. It is similar to the AD736, except that its output is brought out at low level across an 8-k $\Omega$  source resistance (in parallel with the optional external filter capacitance,  $C_{\rm F}$ ).

### HOW WELL DO THEY WORK?

The general-purpose AD736 is internally laser trimmed to an accuracy of  $\pm 0.5$  mV  $\pm 0.5\%$  of reading max in the low cost J/A grades ( $\pm 0.3$  mV  $\pm 0.3\%$  rdg max K/B grades) including its output buffer amplifier. The AD737, optimized for portable meters, omits the buffer amplifier, reducing these errors to  $\pm 0.4$  mV  $\pm 0.5\%$  of rdg ( $\pm 0.2$  mV  $\pm 0.3\%$  rdg). These sets of specs are for 1-kHz sine waves. Both chips will operate over a wide range of supply voltage: from  $\pm 3$  volts up to  $\pm 16.5$  volts.

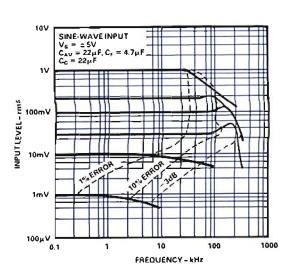

Figure 2. Frequency response, driving high-impedance input (pin 2). Flat response (to beyond 100 kHz at higher amplitudes) is available when low-impedance pin 1 is used.

Sine-wave response at a given frequency depends on amplitude and on which terminal is used for the input. Figure 2 shows the response when the high-impedance input is used. As crest factor\* (CF) increases from 1 to 3, up to 0.7% of additional error is produced; with CF of 5 (1-V peak), the additional error is 2.5%, with  $C_{AV} = C_F = 100 \ \mu F$ . In general, the higher CF, the larger  $C_{AV}$  must be to maintain a given level of accuracy.

The table below shows settling times with typical combinations of practical values of  $C_{\rm AV}$  and  $C_{\rm F}$  for various input levels and low-frequency cutoffs—and crest-factor ranges—found in a variety of applications.

### **APPLICATIONS**

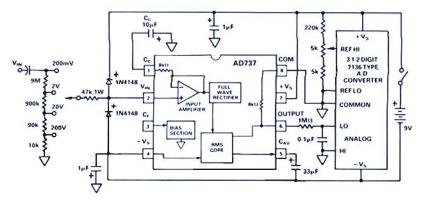

Figure 3 shows how the AD737 would be applied in a portable 9-volt battery-powered 3 1/2-digit voltmeter, using a 7136-type DPM chip as the a/d converter, which drives an LCD display. High input impedance permits an attenuator to be used for the higher-voltage ranges. The AD737's input is protected by a 47-ks? series resistor and a pair of 1N4148 diodes, which serve to clamp the input to either end of the supply. Operating on less than 4 milliwatts of power, this circuit will run even if the battery voltage drops to as little as 6 volts.

Input ranging is provided by the standard 10-M(1 input attenuator. AC input coupling is provided by capacitors C and C<sub>1</sub>. Because of the a/d converter's high input impedance, the post-filter doesn't require a high value of capacitance; a 1-megohm-0.1-µF R-C filter provides adequate smoothing without loading the 7136's input significantly, while saving board space.

Other applications include wide-range dB-measuring circuits and rms ratio circuits. However, because of the versatility and low cost of these devices, their most popular use will be as a one-chip replacement for average-responding ac measurement circuits, with the bonus of a free upgrade to the kind of ac measurement accuracy only an rms circuit can provide.

The originator of the AD736/AD737 was Letvis Counts, AD1 Fellow; the chip was designed by Wyn Palmer; test and trim design twee by Andrew Wheeler. All are of Analog Devices Semiconductor, Wilmington MA.

Figure 3. Applying the AD737 in a 3 1/2-digit voltmeter.

<sup>\*</sup>Crest factor for a given input signal is the ratio of peak to rms, a property of the input waveform. Typical crest factors are 1 for square waves,  $\sqrt{2}$  for sine waves, and 10 for a square pulse having a 1% duty cycle.

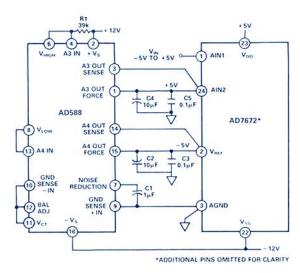

## TRUE 18-BIT DAC IN HYBRID PACKAGE HAS SMALL SIZE, LOW COST

## AD1139 Is Complete With Latches, Reference, Output Amplifier

Includes Range Resistors and Kelvin Connections

by Jeffrey Greenwald and Bill Sheppard

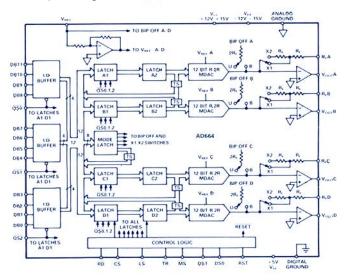

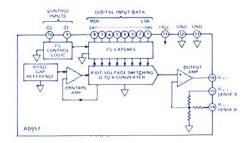

The AD1139 d/a converter (DAC)\* provides true 18-bit performance in a hybrid package, smaller and less costly than earlier modular designs. It is complete (Figure 1), with all functions—input data latches, precision reference, output amplifier and ranging resistors, and Kelvin connections—needed to translate digital data to voltage that drives a load accurately.

Applications for a DAC of this caliber include automatic test (including equipment for testing ADCs and lesser DACs) and scientific instrumentation (chromatographs, spectrographs), and electron beam positioners. High accuracy and stability mean that calibration of systems using such devices may in many cases not be needed over the product life, a major benefit in the field.

No user adjustments are needed to achieve the specified 18-bit (0.00019%) accuracy, with  $\pm 1/2$  LSB ( $\pm 2$  ppm) maximum differential and integral nonlinearity (DNL and INL). For a full-scale step (10 V) the DAC's output settles to within 1/2 LSB in 40  $\mu$ s, and a single-bit change settles in 6  $\mu$ s; glitch impulse at major carries is 400 mV  $\times$  500 ns. INL and DNL temperature coefficients are  $\pm 0.5$  ppm/°C and  $\pm 1$  ppm/°C of full-scale range (FSR), and gain drift is a maximum of  $\pm 4$  ppm/°C, including the reference. The maximum offset tempco is  $\pm 1$  ppm/°C FSR.

Digital Input Structure: Input to the AD1139 is latched as a single 18-bit 5-V-CMOS-compatible parallel rank. Inputs are binary coded for unipolar output and offset binary for bipolar. A 200-ns write pulse latches the data bits; if the write line is held active, the latches are transparent to data changes. To interface the DAC input to an 8-bit bus requires only five ICs: two for I/O space address decoding and enabling, and three for latching the data from the 8-bit data bus. Wider buses require fewer ICs.

Analog Output: Pin-programmable internal resistors set the output voltage range to one of four voltage spans: 0 to  $\pm 5$ , 0 to  $\pm 10$ ,  $\pm 5$ , and  $\pm 10$  V. A current output is available from another pin of the DAC; normally 0 to  $\pm 10$  mA, it can be offset by 0.5 mA via pin strapping to provide a bipolar  $\pm 0.5$  mA output range.

Figure 1. AD1139 block diagram.

### **GETTING BEST RESULTS**

Offset- and gain-trim pins are provided to reduce initial offset and gain errors. The procedure steps are straightforward—adjust for zero offset, then adjust gain at full-scale output—but at the 18-bit level, great care is necessary. The voltmeter used must resolve to 10 µV for end-point calibration.

Remote Sensing Voltage drops due to line resistance between the output and load can be a major source of gain error and gain temperature coefficients when using a high-resolution DAC. On the  $\pm 10$  V range, a single bit corresponds to only 76.3  $\mu$ V (and correspondingly less on the smaller span ranges). A 0.02"-wide copper track, with 50 milliohm/inch track resistance, that connects the output of a DAC to a load just 3 inches away will have a resistance of 0.15  $\Omega$  in each direction, a 0.3  $\Omega$  total. A 10-mA output current will cause a 3-mV voltage drop, or a 0.03 % gain error (79 LSBs at 18 bits). Variations of the track-resistance effect with temperature cannot be trimmed out (unlike the initial gain error) and can contribute as much as 1.2 ppm/°C to the gain drift.

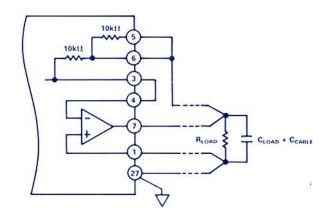

The AD1139 can be configured to sense the actual output value at the load and feed back a correction; the DAC adjusts its output voltage so as to deliver accurate voltage to the load. When configured as shown in Figure 2, all the load current will flow through the force line connected to the internal output amplifier on the high side—and power ground on the low side—of the load, but not through the sense lines. The input of the output amplifier senses the load voltage through the DAC feedback resistor; the low side of the load is sensed by the AD1139's measurement ground—where only bias currents flow.

Figure 2. Remote Sensing compensates for lead resistance.

<sup>\*</sup>Use the reply card for technical data.

When remote sensing is used, the track-resistance contribution at the remote load is reduced to 0.0015%, with a tempco of less than 0.1 ppm/°C. Although the AD1139's output amplifier can typically drive up to  $\pm 20$  mA, the load should not exceed  $\pm 10$  mA or 2,000 pF for rated accuracy and amplifier stability.

Grounding and Ground Currents Because a small amount of current flows through a DAC's signal ground, a length of ground wire or equivalent circuit-board track will cause errors due to voltage drop through the ground lead. Milliohms are critical when one LSB is less than  $100 \ \mu V$ , even on the highest range.

This error cannot be calibrated out in most DAC architectures, since the ground current varies with the actual DAC code; this variation produces system nonlinearity and gain errors. A typical range of ground currents is 0 to -2 mA, or  $\pm 1$  mA. In the AD1139, a combination of techniques makes the ground current independent of the DAC code. The two internal DACs and the voltage reference were initially identified as sources of potential code-dependent ground-current; their design was improved to keep the AD1139 ground current constant, regardless of code.

There are two grounds on the AD1139, the measurement ground and the power ground. The measurement ground is intended to be used for remote sensing to the point considered as the user's high-quality "star" ground. Small bias currents (less than 1  $\mu$ A) flow from this terminal. The power ground carries analog and CMOS digital supply current from the AD1139, to be returned to the power supply—about 1.5 mA, independent of code.

With separate grounds available, the user can define the system measurement ground instead of having to use the DAC's power ground as a measurement point. This works to advantage in systems with multiple DACS, since the signal grounds can all be connected to a single star point, which in turn can be connected to the digital ground at one point only. For the AD1139 to operate properly, the measurement ground must be connected to power ground somewhere in the system, because the two grounds are not directly connected to each other within the DAC. Clamp diodes are used to restrict the open-terminal voltage (sense loop open) to a single diode drop from power ground.

The 18 bits of resolution are divided between two DACs within the AD1139. The six most-significant bits are developed by a novel switched-voltage DAC, while the 12 lower-order bits, DB0 through DB11, are converted by 12 bits of a 14-bit current-steering DAC. Its output is converted to a voltage and then back

Figure 3. Ratiometric testing of 14- and 16-bit DACs with the AD1139.

to a current to be properly summed along with the MSBs in the output stage of the AD1139. Typically, R-2R current-steering DACs have nonlinear code-dependent ground current. To eliminate this error source, the DAC ground is driven with a "voltage-follower ground buffer," which provides a convenient sense point to be connected to measurement ground.

Reference: A highly accurate DAC requires a precise, stable reference. The AD1139's -10-volt reference circuit is based on the Analog Devices AD588 IC reference. Initial maximum error of the reference is  $\pm 0.1\%$ ; temperature compensation results in a maximum tempco of  $\pm 3$  ppm/°C over the 0 to 70° range. The performance specifications of the AD1139 include reference error. The reference has narrowband noise (0.1 to 10 Hz) of 10  $\mu$ V peak to peak (p-p) and wideband (100 kHz) noise <50  $\mu$ V rms.

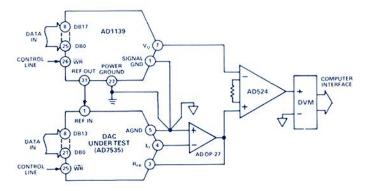

A buffered version of the reference is available for external applications, such as ratiometric device testing. When the AD1139's REF OUT is used as the reference for a DAC under test, Figure 3, the gain of the DUT will track the AD1139 gain; the reference's contribution to gain error is thus eliminated.

As a reference DAC for testing linearity, the AD1139 measures to 1/32 LSB of uncertainty for 14-bit DACs, 1/8 LSB for 16-bit devices. The integral-linearity error is the difference between the outputs of a reference AD1139 and the DAC under test. For differential linearity error, the DAC digital input is stepped and the new output is compared with the previous output—any difference from the ideal is a differential linearity error.

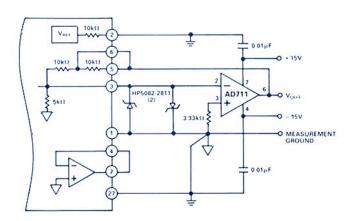

External Output Amplifier: The AD1139's output amplifier is optimized for very low noise, dc-stable applications and moderate settling time. For higher speed or more output current, an external op amp is used instead of the internal amplifier (Figure 4). The AD711 is a good choice for higher-speed applications; it will settle to within 16 bits in only 6  $\mu$ s for a unipolar full-scale step. Other amplifiers may be chosen for differing tradeoffs. The noise gain, as seen by the output amplifier, depends on the output voltage range selected: it is 2 for 0 to +5 V range, 3 for 0 to +10 V, and 7 for the  $\pm$ 10 V range. The amplifier selected must be stable at the noise gain corresponding to the output range.

Two grades of the AD1139 are available; the  $\pm 1$ -LSB J and the  $\pm 1/2$ -LSB K are both packaged in a hermetic 32-lead triple-width DIP package. Prices (100s) are \$195 and \$295.

Figure 4. External amplifier for augmented DAC-output performance.

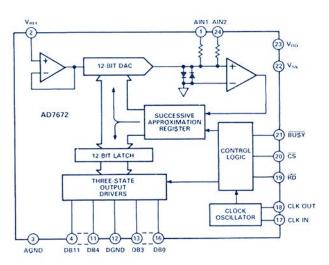

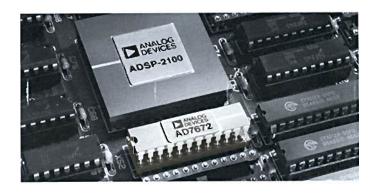

## 12-BIT ADCs FOR DSP PROVIDE COMPLETE INTERFACE

## Single-Channel AD1332 Has S/H, Filter, FIFO, Digital Interface Multichannel AD1334 Can Do Simultaneous Sampling

by Bob Malone and Rene Sierra

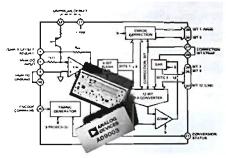

The AD1332 and AD1334 sampling a/d converters,\* with 12-bit resolution and accuracy, provide the functions necessary for a complete interface between audio-bandwidth signals and digital signal-processing systems. The 40-pin-DIP-packaged hybrid devices provide a space-saving, system-level means of data acquisition for DSP applications, replacing a board-full of ICs.

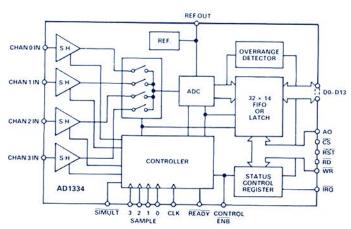

The single channel AD1332 combines a sample/hold amplifier with an anti-aliasing filter and 12-bit A/D converter; the AD1334 converter provides 4 input channels which can used independently or sampled simultaneously. The digital side of these converters is fully asynchronous, with extremely fast (15-ns) bus-access time; included is a 32-word first-in first out (FIFO) memory to make the interface between the converter and the processor transparent and efficient. Because the AD1332 and AD1334 convert asynchronously; there is no need to synchronize the sampling clock and the system clock.

This digital interface design greatly simplifies the circuitry and software needed to transfer digitized signals to the processor. High-speed DSP processors, such as the ADSP-2100/2100A (see page 20), TMS320C25, and DSP56000, can access data directly without an inefficient "wait state." The 32-word FIFO decouples the data sampling and conversion cycle from the needs of the processor and its software timing; conversion results can be transferred as a group to the processor memory, rather than singly.

### AD1332 SINGLE-CHANNEL FRONT END

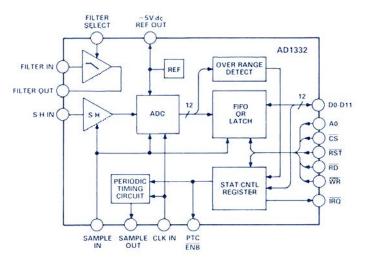

A block diagram of the AD1332 is shown in Figure 1. The converter is scaled for a  $\pm 5$  V input signal range, using an internal precision reference. The sample/hold operates on a band-limited input signal prior to conversion by the ADC. S/H and conversion timing are set by an externally applied  $20 \times \text{clock}$ ; a clock frequency of 2.5 MHz will achieve the maximum sampling rate of 125 kHz. The clock must be stable, since clock jitter affects the precision of the sampling period.

Figure 1. AD1332 block diagram.

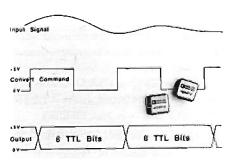

Two conversion modes are available. In the *periodic* timing mode, sampling and conversion proceed continuously, at the rate determined by the clock—useful where data will be processed continuously, as in digital filters or FFTs. The other mode is *externally miggered* conversion, where sampling and conversion take place only after the *Convert Start* control line goes active. This mode's maximum conversion rate is 110 kHz unless the trigger is synchronized to the clock.

The AD1332's internal anti-aliasing filter is intended to limit bandwidth. Sampling theory states that a signal can be fully represented and reconstructed from 2N samples per second for a signal that is bandwidth-limited to N Hz. Sampling at <2N, or sampling signals with bandwidths >N, results in aliasing, which makes it impossible to reconstruct the original analog signal. That's why the input-signal bandwidth must be limited.

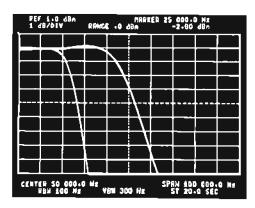

The AD1332's filter is an active 4-pole Butterworth low-pass. The user can set the cutoff frequency, f<sub>c</sub>, at up to 50 kHz with four identical capacitances. The Butterworth filter was chosen because it provides maximally flat magnitude response in the passband. Attenuation at the cutoff frequency is 3 dB, and rolloff beyond f<sub>c</sub>, 20 dB/decade per pole, totals 80 dB/decade. Figure 2 shows passband and stop band responses for f<sub>c</sub> of 25 kHz and 50 kHz. Guaranteed minimum attenuation is 45 dB at 4<sub>c</sub> and 76 dB at 10f<sub>c</sub>.

The filter uses low-noise, high-speed op amps for low distortion and consistent frequency response over the entire range. Precisely trimmed thin-film resistors give consistent and accurate filter setting with user-supplied capacitors. Unlike switched-capacitor filters (which are sampled-data systems), the filter in the AD1332 does not require a clock, pre-filtering, or post-filtering. Although present, the filter is optional. *External* filters allow connection of the input signal directly to the S/H input, or a programmable-gain amplifier between the filter and the ADC.

To meet the needs of DSP applications, the device is specified for both static (dc) and dynamic (ac) performance. Integral nonlinearity over temperature is  $\pm 1/2$  LSB typical,  $\pm 1$  LSB maximum. The full-scale error is  $\pm 2$  LSB at 25° C, for both + and - FS.

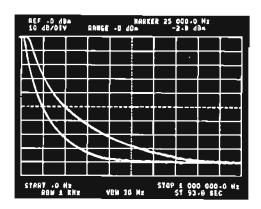

<sup>\*</sup>Use the reply card for technical data.

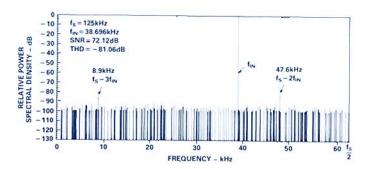

Dynamic specifications: with the anti-aliasing filter set to f<sub>c</sub> of 50 kHz and an input sine wave of 38.7 kHz, signal-to-noise ratio (SNR) is 70 dB, corresponding to 11.3 effective bits. Total harmonic distortion (THD)—same input conditions—is at least 72 dB below the fundamental (Figure 3). Intermodulation distortion (IMD) with inputs of 32.8 kHz and 34.3 kHz is also at least 72 dB down. Results are similar without a filter and 60-kHz input.

#### AD1334 FOUR-CHANNEL FRONT END

Each input channel of the AD1334 has its own S/H, which provides signals to the high-speed 12-bit ADC via the multiplexer (Figure 4). Anti-alias filtering is user-provided externally. The channels can be digitally programmed to operate either independently or in concert. All four channels can be sampled simultaneously (and converted sequentially) at rates up to 28 kHz; the maximum one-channel-only sampling rate is 65 kHz. The four channels can be sampled at differing rates.

The low effective S/H aperture-delay-time mismatch and aperture uncertainty from channel to channel and device to device are essential where the signal phase information and relationships are as important as amplitude, e.g., in phased-array sonar, medical ultrasound, and multiple-axis position control.

Integral and differential nonlinearity are typically less than  $\pm 1/2$  LSB ( $\pm 1$  LSB over temperature). Full scale error is  $\pm 2$  LSB maximum at 25° C and typically half as much. Total harmonic distortion and intermodulation distortion are 72 dB below the fundamental; the 70-dB SNR corresponds to 11.3 effective bits, very close to the theoretical maximum of 12 bits.

a. Passband response. Scale: 10 dB/div, 10 kHz/div.

b. Stopband attenuation. Scale: 10 dB/div, 100 kHz/div.

Figure 2. AD1332 filter responses at 25 and 50 kHz.

Figure 3. AD1332 spectral response, with filter; note low level of aliased harmonics.

#### DIGITAL INTERFACE

Both devices have 32-word FIFO memories. The FIFO in the single-channel AD1332 is 12 bits wide, but the AD1334's FIFO is 14 bits wide, to store both the 12 bit conversion data and a 2-bit channel identification code. Interrupts indicate to the processor that data is available.

Interaction between the converters and the processor is managed by a control byte and a status byte. The control byte sets FIFO operating mode and sampling conversion mode (periodic or triggered). The status byte indicates FIFO conditions; it can either be polled by the processor or read after an interrupt.

The control word sets the interrupt to occur when the FIFO is full, half-full, or indicating analog overrange (beyond the ±5 V range). This last setting allows the analog range to be changed immediately to prevent useless conversions from continuing. There is also a mansparent mode, effectively bypassing the FIFO, where the result of each conversion is available immediately without waiting for it to propagate through the FIFO. Upon the interrupt, the processor can quickly access all results in the FIFO in a single burst, even while another conversion is occurring.

The interface between a DSP processor and the AD1332 or AD1334 usually requires only a simple address decoder. The fast data access—15 ns—results in zero wait states; no special wait state circuitry or handshake lines are needed for DSP ICs available today and known members of the next generation. Internal three-state buffers connect directly to the processor bus.

Both the AD1332 and the AD1334 operate from ±12 to ±15 V supplies. Total power consumption is <2 W, maximum, and operation is specified for the −40° to +85° C temperature range. Devices will be available screened to MIL-STD-883B. Prices begin at \$140 (100s) for the AD1332 and \$180 for the AD1334. ▶

Figure 4. AD1334 block diagram.

## MONOLITHIC DIGITALLY PROGRAMMABLE DELAY GENERATOR

AD9500 Converts an 8-Bit Digital Input to an Output Time Interval FS Range Is from 2.5 ns (with 10-ps Resolution) to 100 µs And More

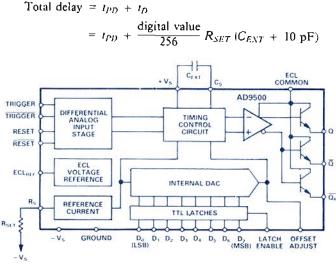

The AD9500 Programmable Delay Generator\* receives a digital trigger pulse and outputs a signal after a specified delay period, as programmed by an 8-bit digital input. The full-scale delay range is flexible, ranging from a few nanoseconds to more than 100 µs; it is set by an externally connected R-C combination. Compact, low-cost single-chip digitally programmable delays have immediate practical applications in test systems: eliminating signal skews in high-speed systems, measuring unknown delays, and constructing programmable ring oscillators.

Figure 1 shows the various functions within the AD9500. The key functions are the reference and the timing-control circuit—which form an analog integrator; an 8-bit d/a converter, set by the 8-bit digital control input; and a high-speed precision comparator with complementary ECL outputs. Inputs are differential trigger and reset signals, which may also be used with single-ended inputs. The maximum triggering rate is 100 MHz.

#### **HOW IT WORKS**

The trigger and reset inputs are designed primarily for ECL signal levels, but they can function with analog and TTL input levels. An on-board reference midpoint allows both of the inputs to be driven by either single-ended or differential ECL circuits.

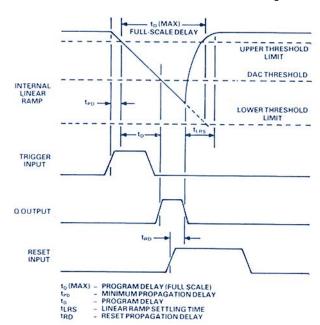

As the timing diagram in Figure 2 shows, the delay is initiated when the trigger input goes high. The integrator generates a downgoing ramp; when it crosses a level established by the 8-bit DAC, the comparator output changes state, producing the delayed outputs, Q and  $\overline{Q}$ . A parallel  $\overline{Q}_R$  output circuit is available for uses where the AD9500 drives its own reset.

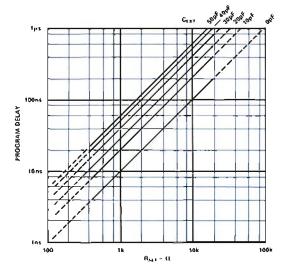

Its delay is equal to the programmed delay,  $t_D$ —a function of the selectable RC time constant (Figure 3) and the precision threshold set by the DAC—plus a propagation delay ( $t_{PD} = 7.4$  ns max with a 5-ns full-scale input).

Figure 1. Block diagram of the AD9500.

Reset: A pulse of appropriate width applied at the Reset input resets the integrator and the Q outputs to prepare the device for the next trigger. At the end of the reset propagation delay  $(t_{RD})$ , approximately equal to  $t_{PD}$ ), Q returns to its original state; 0.2 ns after the Reset input goes low, the device is ready for the next trigger. A reset interval,  $t_{LRS}$ , should be allowed for the linear ramp to return and settle to its original level.

When  $C_{ENT} = 0$ , and  $R_{SET} = 250 \Omega$ , the full-scale programmed delay time is 2.5 ns, and the LSB (one increment of delay) is 2,500 ps/256  $\approx 10$  ps, which is also the typical jitter level; this establishes the basic delay-time resolution.

The digital control data is passed to the AD9500 via a transparent latch, controlled by the *latch enable* signal. In the transparent mode, the DAC follows changes at the inputs; the *latch enable* signal is used to strobe the digital data into the AD9500's latches.

Because the DAC has fast response, the programmed delay may in principle be updated in the same time frame as the signals being

Figure 2. Timing diagram.

<sup>\*</sup>Use the reply card for technical data.

Figure 3. Typical values of programmed delay ranges as a function of resistance and capacitance.

delayed. However, the next trigger should wait for the DAC to settle, typically 29 ns after latching in a new value.

The AD9500's programmed time delay is linear to within 1 LSB maximum integral nonlinearity with >100-ns full-scale input, with 1/2-LSB max differential nonlinearity; monotonicity is guaranteed over the full specified operating temperature range. 312mW of power is drawn from the +5-V and -5.2-V supplies.

Devices are graded to operate from -25 to +85°C (B grades) and -55 to +125°C (T grades). Except for operating temperature range, all grades have identical electrical spees. Available packages include 28-pin PLCC (P) and LCC (E) packages and 24-pin ceramic "skinny" DIPs (Q). Prices in 100s start at \$16.00.

#### APPLICATIONS

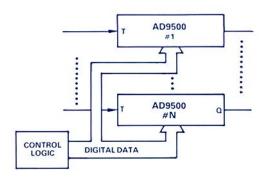

Multichannel Deskewing: A highly effective use of the AD9500 is in multiple delay-matching applications. For example, in a high-speed, high-pin-count logic tester, slight differences in impedance and cable length can create large timing skews. The high speed of modern test systems makes timing accuracy particularly important, and the large number of driver lines (e.g., 128 driver lines with switching capabilities in excess of 100 MHz) requires the use of compensating circuitry. In practice, each signal line would drive an AD9500; its output would drive a logic test-head line (Figure 4). With one line as a standard, the programmed delays of the others are adjusted to eliminate the timing skews.

With the very fine timing adjustments possible from the AD9500 (as small as 10 ps), nearly any high-speed system should be able to

Figure 4. Multiple delay matching.

adjust itself automatically to within very tight tolerances.

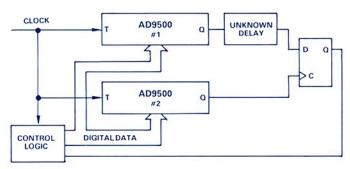

Measuring Unknown Delays: Two AD9500s can measure delays precisely (Figure 5). One is set with little or no programmed delay; its output drives the unknown-delay circuit, which in turn drives the input of the "D"-type flip-flop. The second AD9500 drives the clock input of the flip-flop. With both triggered together repetitively, the programmed delay of the second unit is varied to detect the output edge from the unknown delay.

Detecting the output edge is straightforward. If the programmed delay through the second AD9500 is too long, the flip-flop output will be at logic high—if too short, at logic low. When the unknown is very closely matched, the flip-flop's output will bounce between high and low. The digital code value used to create the second programmed delay is a direct indication of the delay though the unknown circuit. Best results are achieved by calibrating the system with the unknown delay removed.

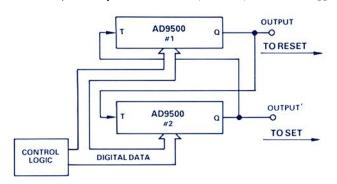

Programmable Oscillator: A digitally programmed oscillator for frequencies up to 67 MHz is an interesting use of the AD9500. The high-precision delays it generates can be exploited to create a ring oscillator with variable duty cycle (Figure 6). The delayed output of the first AD9500 is used to drive the trigger input of the second unit; the output of the second, in turn, drives the trigger

Figure 5. Programmable oscillator.

input of the first. Together, the devices will alternately trigger one another, creating two pulse chains on their outputs.

The total delay through both AD9500s determines the period of the oscillation. The duty cycle can be controlled by using the outputs to drive the set and reset inputs of a flip-flop. The delay through the first AD9500 controls the flip-flop logic low output pulsewidth; the second controls the logic high pulsewidth.

The AD9500 was designed by Jeff Barrow at ADI's Computer Labs Division, in Greensboro NC. Critical portions of this circuit are covered by U.S. Patents 4,742,331 (Jeff Barrow and A. Paul Brokaw) and 4,349,811 (A. Paul Brokaw).

Figure 6. Measuring unknown delays.

## 15 NEW CMOS SWITCHES AND MUXES IN CONVENIENT VARIETY

ADG Series Is Spec'd for 44-V max Supply, Wide Temperature Range, Single-Supply Superior 2nd Sources Include ADG-201HS: 50-ns  $\,t_{\text{DN}}$

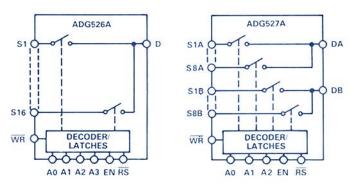

Fifteen additions to Analog Devices' line of CMOS switches and multiplexers (muxes) give designers a choice of components optimized for the application. The ADG201A/202A\* (utility), ADG201HS (high-speed)\*, ADG211A/212A\* (lowest cost), and ADG221/222 (latched) quad switches—and the multiplexers in the ADG506A/507A & 526A/527A (16/dual-8-channel),\* and the ADG508/509A & 528A/529A\* (8/dual-4-channel) families—are specified for dual- and single supplies and for applications with higher supply voltages and wider temperature ranges than many of the industry-standard namesakes that they replace.

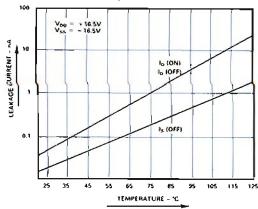

Avoiding dielectric isolation, these components are fabricated at low cost in a high-performance, linear-compatible CMOS process (LC<sup>2</sup>MOS) with a breakdown voltage of 44 V. The normal operating voltage range is  $\pm 10.8$  to  $\pm 16.5$  V, but the devices can operate with supply voltages up to the breakdown voltage. Low leakage currents ( $\leq 1$  nA at 25° C) minimize offsets.

The self-aligned high-voltage switch process results in much lower parasitic capacitances than dielectric isolation, with correspondingly higher switching speeds. The basic switch is latchup-free over the full operating range; advanced design and process techniques eliminate latchup-prone parasitic transistors.

#### ANALOG SWITCHES

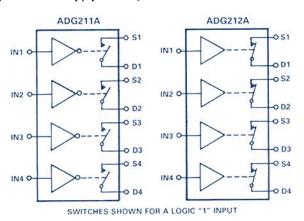

The ADG201A & 201HS, ADG202A, 211A, 212A, 221, and 222 are quad SPST switches; each switch is independent of the other three in the package (Figure 1). The xx1's and xx2's differ only in the sense of their control logic, as shown in the table. The digital control signal can be either TTL or 5-V CMOS compatible. The latches in ADG221/222 permit switch-state storage.

A low charge-injection design minimizes transients that occur during switching. All switches are "break before make," an advantage in multiplexer applications, since the outputs of the switches can be safely tied together. The analog signal range that can be handled is  $\pm 15$  V. The switches can be operated from a single + 15-volt supply for unipolar (0 to + 15-V) analog signals.

Figure 1. Block diagram of complementary quad switches.

### COMPARING ADG QUAD SWITCHES

| 201A/<br>202A | 201HS                                                                                 | 211A/<br>212A                                                                                                                                                                                                                                                                | 221/<br>222                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/0           | 1                                                                                     | 1/0                                                                                                                                                                                                                                                                          | 1/0                                                                                                                                                                                                                                                                                                                                                                                             |

| No            | No                                                                                    | No                                                                                                                                                                                                                                                                           | Yes                                                                                                                                                                                                                                                                                                                                                                                             |

| 9011          | 50Ω                                                                                   | 115                                                                                                                                                                                                                                                                          | 90Ω                                                                                                                                                                                                                                                                                                                                                                                             |

| 145Ω          | 7511                                                                                  | 1751)                                                                                                                                                                                                                                                                        | 1450                                                                                                                                                                                                                                                                                                                                                                                            |

| 300 ns        | 75 ns/50 ns                                                                           | 600 ns                                                                                                                                                                                                                                                                       | 300 ns                                                                                                                                                                                                                                                                                                                                                                                          |

| 250 ns        | 75 ns/50 ns                                                                           | 450 ns                                                                                                                                                                                                                                                                       | 250 ns                                                                                                                                                                                                                                                                                                                                                                                          |

| K,B,T'        | $J,A,S/K,B,T^2$                                                                       | к'                                                                                                                                                                                                                                                                           | K, B, T'                                                                                                                                                                                                                                                                                                                                                                                        |

| N, Q, E       | N, Q, E, P                                                                            | N, P                                                                                                                                                                                                                                                                         | N,Q                                                                                                                                                                                                                                                                                                                                                                                             |

| \$3.15/\$2.95 | \$3.10/\$4.80                                                                         | \$1.60                                                                                                                                                                                                                                                                       | \$2.56                                                                                                                                                                                                                                                                                                                                                                                          |

|               | 202A<br>1/0<br>No<br>90Ω<br>145Ω<br>300 ns<br>250 ns<br>K,B,T <sup>1</sup><br>N, Q, E | 202A         201HS           1/0         1           No         No           90Ω         50Ω           145Ω         75Ω           300 ns         75 ns/50 ns           250 ns         75 ns/50 ns           K,B,T¹         J,A,S/K,B,T²           N, Q, E         N, Q, E, P | 202A         201HS         212A           1/0         1         1/0           No         No         No           90Ω         50Ω         115           145Ω         75Ω         175Ω           300 ns         75 ns/50 ns         600 ns           250 ns         75 ns/50 ns         450 ns           K,B,T¹         J,A,S/K,B,T²         K¹           N, Q, E         N, Q, E, P         N, P |

<sup>1</sup>Temp. Ranges: J, K = 0°C to 70°C, A, B = −25°C to +85°C, S,T − −55°C to +125°C.

<sup>2</sup>Temp. Ranges: J. K =  $-40^{\circ}$ C to  $+85^{\circ}$ C, A, B =  $-40^{\circ}$ C to  $+85^{\circ}$ C, S, T =  $-55^{\circ}$ C to  $+125^{\circ}$ C.

'Packages: N=Plastic DIP, Q=Cerdip, E=LCC, P=PLCC.

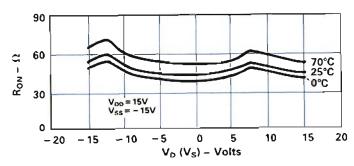

Figure 2. Ron versus temperature for ± 15 V supplies.

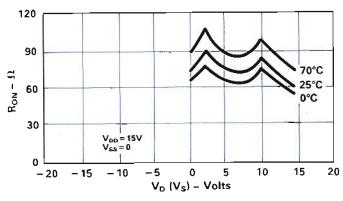

Figure 3. Ron versus temperature for single + 15 V supply.

<sup>\*</sup>Use the reply card for complete data sheets on any of these product pairs and to request the short-form guide: Analog Switches and Multiplexers.

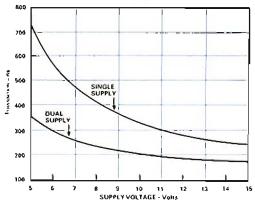

An important specification that affects accuracy of the final system design is the on resistance, R<sub>ON</sub>; its maximum values at both +25°C and T<sub>II</sub> are shown in the table. Note that, for both single and dual supplies (Figures 2 and 3), the on resistance does not vary by more than 2:1 over temperature. Switch turn-on and turn-off times are also critical; they too are shown in the table. Data sheets\* show characteristics for both dual- and single-supply operation. Power consumption of these switches is less than 33 mW, except for the ADG201HS (240 mW max).

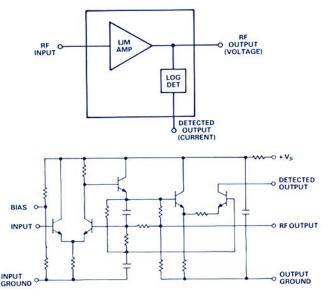

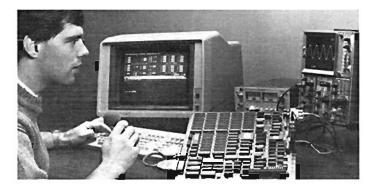

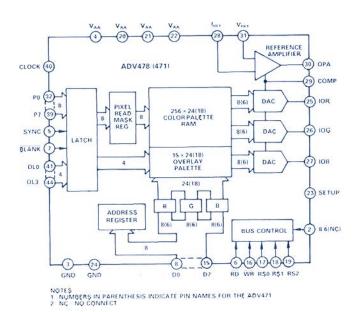

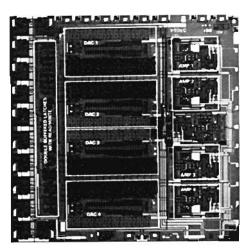

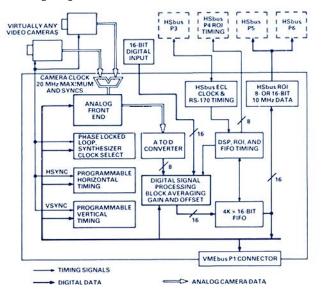

### ANALOG MULTIPLEXERS