## analog dialogue

A forum for the exchange of circuits, systems, and software for real-world signal processing

FAST, FLEXIBLE, MONOLITHIC CMOS MICROPROCESSOR FOR DSP (page 3)

Monolithic 16-Bit DAC is 16-Bit Monotonic (page 7)

5B Series of Compact Low-Cost Plug-in Signal Conditioners (page 8)

μMAC-6000: Expandable Modular I/O Processor for Industrial Automation (page 10)

#### **Editor's Notes**

#### **ANALOG & DIGITAL**

"Microprocessor?" we hear you ask. "Isn't it a bit unseemly for a nice 'Analog' IC company to be designing a microprocessor? (What could be more digital?)"

Good question.

Our objective has always been to design and manufacture cost-effective components that are key elements of the signal path for

processing real-world (i.e., analog) data and for which performance is maximized and errors minimized.

The signal path? Real-world data almost always starts out as analog (i.e., parallel, non-numeric) variables, which are measured by sensors that provide analog electrical signals—voltage and current. The signals must be accurately and speedily amplified, conditioned, (almost always in parallel) and converted to digital for processing. Once in digital form, they must be processed rapidly. Often, they again wind up as analog signals.

Key elements of the signal path include preamplifiers, analog signal processors, data converters to and from digital, and—when the signal is in digital form—a digital processor. Inadequacy in any one of the key elements—amplifier, analog processor, data converter, or microprocessor—can cause poor performance of the overall system.

Obstacles in the signal path include noise, drift, nonlinearity, and measurement lag at the analog stages, similar obstacles in conversion—and throughput delays in digital processing, often because of the lack of parallelism in von Neumann architectures.

Throughout our history, our role in the signal path has been to initiate new products (or product lines) when dissatisfied with the cost-effectiveness of what's available (which is often limited to user-assembled kludges, when nothing else is available). At this point in time, we (and our competitors) have virtually eliminated the user-assembled amplifier, signal-conditioner, and data converter by designing and marketing families of cost-effective products.

We have always been dissatisfied with the cost, power dissipation, and slow throughput in the digital domain; this concern led to our pioneering development of CMOS multipliers and other digital signal-processing ICs (note that because we were already familiar with analog multipliers, digital multipliers became just another analog signal-processing tool; note also our commitment to signal processing—not payroll, desktop publishing, or order-handling products). Our dissatisfaction with the complexity of systems using Bit-Slice parts led to the powerful and compact Word-Slice TM microcoded system parts.

And finally our dissatisfaction with insufficient throughput in DSP processors led to design of the ADSP-2100, which stresses the use of that analog characteristic, parallelism, to minimize instruction cycles, whether in processing, data transfer, or interrupt handling. It's neat! We invite you to read about it.

Dan Sheingold

#### **THE AUTHORS**

James Conant (page 14) is a Senior Marketing Engineer in the Interface Products Division of Analog Devices. A biographical sketch and his photo appear in the last issue (20-1, 1986).

Daniel Denaro (page 19) is a Senior Design Engineer for ADI's Memory Device Division, in East Molesey, England. He received a BEE with honors from the University of Queensland (Brisbane, Australia) in 1979. Before joining ADI, he was working on radar detection systems at EMI Electronics; he has been working on hybrid converters since 1983.

Bob Fine (page 3) is the Applications Engineering Manager for ADI's Digital Signal Processing Division. He has been with the DSP division for four years, mostly in applications. Earlier, Bob worked for the Systems Division of ADI, designing both analog and digital circuits. Bob has a BSEE from Northeastern University and has

specialized in data-acquisition circuits, analog and digital signal processing.

Amer Iqbal (page 18) is a Marketing Engineer at ADI's Interface Products Division. Before joining Analog Devices, he worked at Qualogy (San Jose, CA), designing DEC-compatible disk- and tape controllers. Amer holds a BSEE degree from MIT and an MBA from Wharton. He enjoys camping, sailing and squash.

Kathryn Kasper (page 8), a Marketing Engineer with ADI's Interface Products Division, has an SM in Management from M.I.T. and a BES in Chemical Engineering from the Johns Hopkins University; she is now working towards an MSEE at Northeastern University. Kathryn joined Analog Devices in 1984 as a Marketing Analyst in

Corporate Strategic Information and moved to IPD in 1985.

(Continued on page 26)

## analog dialogue

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106

Published by Analog Devices, Inc., and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and display circuits and systems. Correspondence is welcome and should be addressed to Editor, Analog Dialogue, at the above address. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577, Telex 174059, or cable ANALOG NORWOODMASS.

## FAST, FLEXIBLE CMOS SINGLE-CHIP LP FOR DIGITAL SIGNAL PROCESSING

High-Performance ADSP-2100 Has Multiple-Bus Architecture, Parallel Operations Available Development System Speeds Program Development and Verification

by Mike Nell and Bob Fine

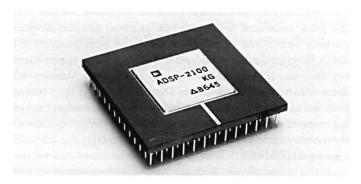

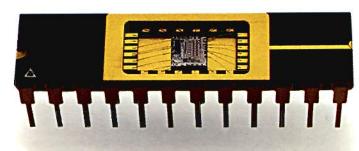

The ADSP-2100\* is a single-chip CMOS microprocessor designed specifically for DSP applications and high-performance number crunching. Combined to utilize its 125-ns cycle time efficiently, its multiple-bus structure, substantial external program- and datamemory capacity, powerful instruction set, and independent on-chip computational units—including a multiplier-accumulator/subtractor (MAC), arithmetic-logic unit (ALU), and full-function barrel shifter (for floating-point computations)—deliver performance far exceeding that of earlier single-chip DSP microcomputers. In fact, its performance approaches that of multi-chip (multiwatt!) bit-slice systems, but with power consumption less than 0.6 W. It can perform a 1K-point complex fast Fourier transformation (FFT) in 7.2 ms, or a 64-tap FIR filter operation in 8 µs per output sample. Table 1 lists these and a selection of other key benchmarks.

#### TABLE 1. Benchmark Performance of the ADSP-2100.

| ROUTINE                             | EXECUTION TIME           |

|-------------------------------------|--------------------------|

| 64-tap FIR filter (pipelined rate)  | 8 µs/sample(125 ns/tap)  |

| 64-tap complex FIR filter           | 32 µs/sample(500 ns/tap) |

| Biquad filter section               | 0.88 μs/section          |

| Normalized lattice filter section   | 0.63 µs/section          |

| Two-dimensional convolution (3 × 3) | output sample/عبر 1.25   |

| Matrix multiply (10 × 10 matrices)  | 0.22 ms total            |

| 1,024-point complex FFT             | 7.2 ms                   |

| 4,096-point complex FFT             | 33.3 ms                  |

| 256-tap LMS adaptive filter update  | 64.9µs                   |

| Tenth-order LPC analysis            |                          |

| (240-pt. rectangular window)        | 0.56 ms                  |

|                                     |                          |

Because of its speed and flexibility, it has become the DSP microprocessor of choice for such real-time and near-real-time applications as adaptive filtering, image processing, speech recognition and synthesis using linear predictive coding (LPC), and modem systems.<sup>†</sup> It can also be used in multiple-processor systems or as an accelerator to offload computations under control of a host computer.

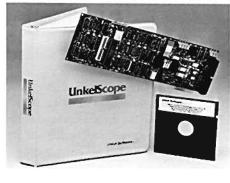

To facilitate applications, Analog Devices makes available—in addition to an experienced applications staff and the usual support publications—a development system to speed program development and verification. Software tools include: a System Builder, Assembler, Linker, Simulator, and PROM Splitter; in addition, an Emulator provides the necessary hardware to debug user-developed programs in the "target system." In these pages, you will find a brief overview of the ADSP-2100 and its development system. For more information, use the reply card or get in touch with our DSP Division in Norwood, Mass.

#### WHY THE DSP MICROPROCESSOR?

The spectrum of DSP systems ranges from large, flexible micro-

‡For a description of a typical chip set for such arrays, see Analog Dialogue 20-1, pp. 7-9, "Fast 64-Bit IEEE-754 Floating-Point Multiplier and ALU," and pp. 10-11, "Fast, Flexible Word-Slice<sup>TM</sup> CMOS ICs Simplify Design of Microcoded DSP Systems."

programmed arrays assembled with such chips as multiplier-accumulators, address generators, sequencers, etc.<sup>‡</sup>—and a potentially large complement of modular memory—to self-contained compact devices, such as dedicated function chips (FIR filters, etc.) and monolithic DSP microcomputers (µPs with a substantial complement of memory). When designing general-purpose DSP chips, there is a tradeoff between memory and computing power—both compete for chip area. If sufficient memory is on-chip to handle significant problems without off-chip memory transfers, processing capability is usually far from optimum.

Since memory requirements for different applications vary widely, and external memory is cheap, the designers of the ADSP-2100 concluded that (a) memory should remain off-chip and (b) the bulk of design effort on a general-purpose chip should be invested in maximizing computing power and optimizing the memory inter-

#### IN THIS ISSUE

| Volume: | 20, I | Number | r 2, 1 | 986 – | 281 | Pages |

|---------|-------|--------|--------|-------|-----|-------|

|---------|-------|--------|--------|-------|-----|-------|

| Editor's Notes, Authors                                                      | 2 |

|------------------------------------------------------------------------------|---|

| Fast, Flexible CMOS Single-Chip uP for Digital Signal Processing (ADSP-2100) | 3 |

| Monolithic 16-Bit DAC is 16-Bit Monotonic - All Grades and                   |   |

| Temp Ranges (ADS69)                                                          | 7 |

| The SB Series: Compact Low-Cost Plug-In Signal Conditioning Modules          | 8 |

| µMAC-6000: An Expandable Modular I/O Processor for Industrial Automation 1   | 0 |

| Precision Wideband 3-Port Hybrid Isolation Amplifier (AD210)                 |   |

| Monolithic Synchronous V/F Converter: 0.005% Max Nonlinearity (AD651) 1      | 5 |

| High-Linearity 16-Bit DAC Is Digitally Trimmable (AD1147/AD1148)             |   |

| Small, Fast, Low-Cost, High-Resolution Integrating A/D Converter (AD1170) 1  |   |

| Low-Cost Hybrid Strain-Gage Signal Conditioner (1B31)                        |   |

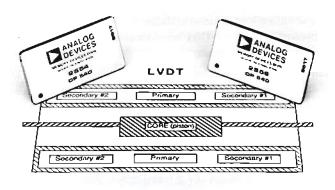

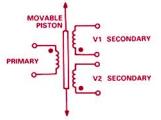

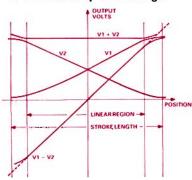

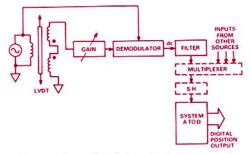

| The Easy Way to Interface an LVDT to Digital (2856 converter family) 1       | 9 |

| New-Product Briefs:                                                          |   |

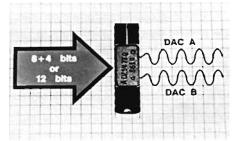

| Dual 12-Bir DACs in 0.3" DIPs for 8/16-Bir Data Buses (AD7537/AD7547) 2      | 2 |

| Highest-Performing Low-Cost BiFET Op Amps (AD548/AD648/AD711/AD712) . 2      | 2 |

| AD202/AD204 Isolator Family Enhanced (K versions and low-profile DIPs) 2     | 2 |

| High-Resolution Programmable-Gain DAS (AD367)                                | 3 |

| Data Acquisition and Processing for PCs - RTI-800s & Commercial Software 2   | 3 |

| LCCs, PLCCs, and SOICs: ICs Available in Surface-Mount Packages              | 3 |

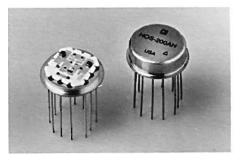

| Unity-Gain Buffer Amplifier with 200-MHz Bandwidth (HOS-200) 2               | 4 |

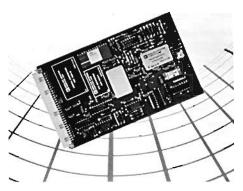

| Complete 12-Bit, 5-MHz A/D Converter (with T/H) on Eurocard                  | 4 |

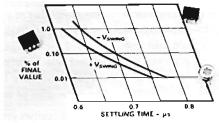

| 12-Bit Multiplying DAC with 110-ns Settling Time                             | 4 |

| Fast, User-Reprogrammable OCR Reader, SPEED READER                           | 5 |

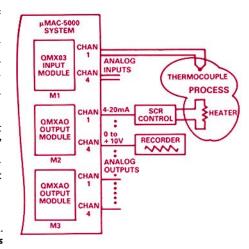

| Analog Output Module for µMAC-5000 (QMXAO)                                   | 5 |

| μMAC-5000 Runs C - Software Tools for New Programming Option 2               | 5 |

| New Literature and More Authors                                              | 6 |

| Porpourri                                                                    |   |

| Advertisement                                                                |   |

|                                                                              |   |

<sup>\*</sup>Use the reply card to obtain technical data.

<sup>†</sup>A few typical applications are described in some detail in a series of articles that appeared in Electronic Design magazine early in 1986. The series has been collected and is available as a reprint "Advanced Chips Launch a New Age of Digital Signal Processing." Use the reply card to obtain a copy.

face to minimize delays in communication with external memory. Thus, with the exception of stacks, a small program cache, and a generous assortment of registers associated with on-chip functions, it has no memory on chip.

#### MEMORY

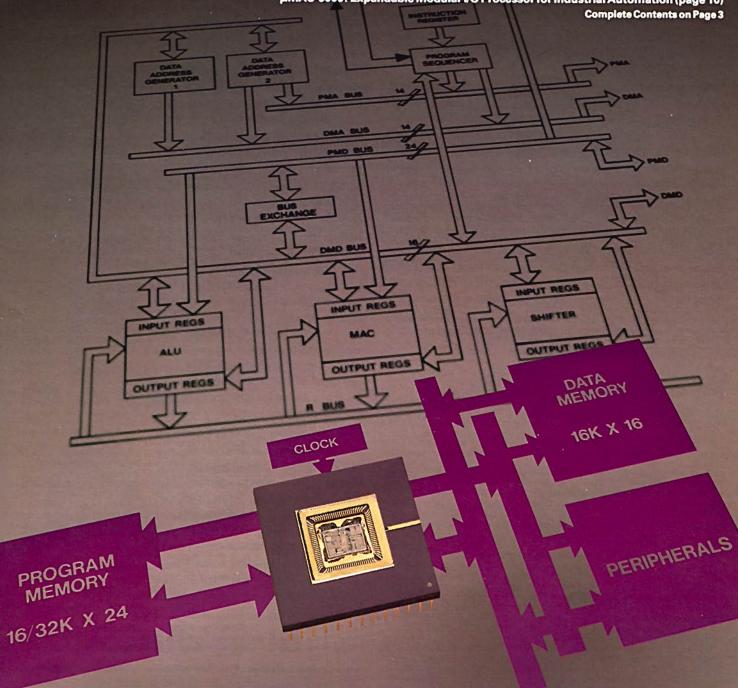

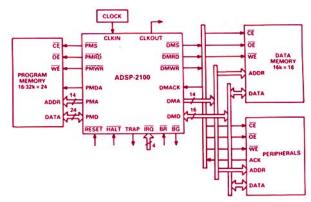

Figure 1 shows how the ADSP-2100 communicates with the outside world. Program memory holds the application program, data memory stores the system data. There are two buses, and their control lines, associated with up to 32K of 24-bit external program memory (which can be used for storage of both program and data): Program-Memory Address bus (PMA) and Program-Memory Data bus (PMD). Another pair of buses, Data-Memory Address (DMA) and Data-Memory Data (DMD), and their control lines, are associated with up to 16K of 16-bit data memory (including memory-mapped I/O peripherals—slower devices can stretch the memory cycle by inserting WAIT cycles to delay the acknowledge signal (DMACK)). Both memories can be accessed simultaneously and independently. Both can be read from or written to, with single-cycle direct access. Access time is 55ns for DM and and 50ns for PM if the processor is running at maximum speed.

Linked to two external memories in this way, the chip can access instructions and data simultaneously. However, both memories can store data if a computation uses two operands. In digital filtering, for example, a user can keep the chip's multiplier-accumulator running at full throttle by storing samples in one memory and coefficients in the other, and retrieving them simultaneously; a Data Access signal (PMDA) indicates that data, not an instruction, is being retrieved from program memory.

When the program memory is used to furnish data, it is important that extra memory cycles not be used for the data fetch, since that would negate the advantage of storing the data in program memory. Fortunately, most time-critical computations are repetitive in nature; thanks to the DSP chip's cache memory, those operations can be written in the form of program loops. The cache memory maintains a short history of previously executed instructions. When the program enters a loop, the cache stores the loop instruc-

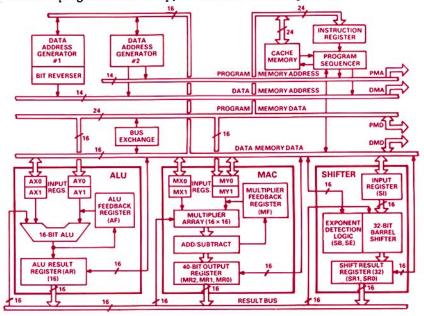

Figure 2. Basic chip architecture of the ADSP-2100. The independent MAC, ALU, and barrel shifter sections—plus the dual bus and addressing structure, the internal R-bus, and microcoded instruction cache—are central to its processing power.

Figure 1. The ADSP-2100 in a basic system environment, with program and data memories and I/O peripherals.

tions on the first pass, then feeds the instruction register on all subsequent passes. While the cache is providing instructions, the program memory bus is free to supply data without incurring overhead cycles; thus, the processor's performance is equivalent to that of a three-memory system.

Bus request and grant signals allow the ADSP-2100 to run under the control of a host processor. When another processor requests access to one of the system memories, the chip responds by halting program execution and releasing the address, data, and control lines. The chip's four interrupt-request lines can be individually programmed to respond to a signal's logic level or its edge.

#### **COMPUTING POWER**

Figure 2 shows the internal structure of the ADSP-2100. Five major buses speed the internal transfer of information. In addition to the internal extensions of the four data and program buses, a fifth, the R (results) bus, handles intermediate computational results within the chip. By providing the necessary signal paths, these buses make possible complex, multifunction instructions that can be executed in one machine cycle.

The chip's computational capabilities revolve around three functional units: an ALU, a multiplier-accumulator/subtractor (MAC),

and a barrel shifter. They sit side-by-side, function independently of one another, and operate on 16-bit input data with provision for multiprecision operations. While they rely for fast interconnection on the flexible use of the R bus, each also has a feedback register to permit it to make use of its own result in its next computation while leaving the R bus free for other uses. Thus, a sequence of arithmetic operations can be performed smoothly without excessive juggling of intermediate results.

Two independent address generators keep data flowing freely to the computational units, and the program sequencer has provisions for executing looped code without incurring overhead cycles. A set of background "shadow" data registers that duplicates the on-chip registers makes possible rapid context switching (i.e., new tasks, such as interrupt service routines, can be executed without taking time to transfer current states to storage).

ALU The 16-bit-wide ALU performs addition, subtraction, division, and logical functions. It can provide both double-precision and saturation (to eliminate rollover-type overflows) arithmetic. As a useful

option, the ALU—and the other math units—can be programmed to perform an operation conditionally (i.e., if a specified test is met).

MAC The MAC's repertoire includes multiply, multiply-accumulate, and multiply-subtract. Its  $16 \times 16$  array feeds a 32-bit product into a 40-bit adder-subtractor. The final 40-bit result leaves plenty of room for overflow. The multiplier will accept any combination of signed or unsigned input formats, thus making double-precision possible. Users can also choose options for unbiased rounding and saturation of the final result.

Shifter The barrel shifter efficiently implements the numerical scaling operations needed for floating-point and block floating-point (BFP) arithmetic. It also supports double-precision shifting, normalization, denormalization, shifting by a constant, and the derivation of an exponent for an individual number or block of numbers (BFP). The shifter's array accepts a 16-bit input and produces a 32-bit output. Unfilled high-order positions in the result can be padded with zeros or extensions of the sign bit.

Registers Each functional unit contains a set of input and output registers that act as stopover points for data traveling between the external memory and the computational circuitry. In effect, the registers introduce a single level of pipelining into the data flow. Consequently, the processor's instruction set overlaps computations and register-memory transfers. Computational operations, which take their operands either from a local input register or from an output register via the R bus, load their results into a local output register.

Addressing Fast number-crunching hardware is wasted if it must frequently sit idle, waiting for data. To make this situation unlikely, especially for operations that require two operands (like addition or multiplication), a powerful memory-addressing scheme is used; the chip's two independent data address generators compute memory-reference locations at the processing rate. One of the address generators has a bit-reversing capability for scrambling or unscrambling fast-Fourier-transform data. While both can supply data-memory addresses, one of them also addresses program memory, allowing access to data stored in program memory.

Each address generator has four Index registers (for the memory pointers), four Modify registers (for the offset values, which move the pointers by a specified amount each time they are used), and four Length registers, which define the size of the data structures being addressed and allow circular—or modulo—addressing (for example, if an index register is pointing to the last location in a circular data structure of length 5, moving the pointer ahead by 1 will actually move it back by 4, to the first location in the structure—and vice versa). Circular addressing helps to efficiently implement digital filters, FFTs, matrix manipulations, and many other DSP routines.

A large portion of the ADSP-2100 chip is devoted to the program sequencer, which streamlines the program flow and reduces overhead when looping, branching, and responding to interrupts. It has four stacks, full interrupt capabilities, single-cycle conditional branch, and zero-overhead looping. "Do-until" loops can be any length, and the loop stack allows them to be nested four deep.

#### **INSTRUCTION SET**

Every instruction is coded into a single 24-bit word, using high-level algebraic notation, and operates in one cycle. There are four

basic categories of processor instructions (Table 2): Move instructions encompass register-to-register and register-to-memory transfers, as well as immediate loading of registers and data memory. Memory addresses are supplied either by the data address generators or from a field in the instruction word. Computational instructions exercise the ALU, multiplier-accumulator, and shifter. The instructions can be executed conditionally based on the contents of the status register. They can also be combined with register-to-register and register-to-memory Move operations, including a simultaneous Read of program and data memories.

Table 2. Summary of ADSP-2100 Instruction Set.

Move Instructions

Register ← Register

Register ← Data Memory

Register ← Program Memory

Immediate Value → Register

Immediate Value → Data Memory

Computational Instructions

ALU Operations: Add, Subtract, Divide, Negate, Increment,

Decrement, Absolute Value, Logical Operations, Clear to 0.

MAC Operations: Multiply, Multiply and Add, Multiply and Subtract

Clear to 0; formats: signed, unsigned, or mixed.

SHIFT Operations: Arithmetic Shift, Logical Shift, Normalize,

Derive Exponent, Block-Exponent Adjust, Immediate Shifts,

Denormalization and Normalization, Derive Block Exponent.

Conditional ALU/MAC/SHIFT Operation

ALU/MAC/SHIFT Operation with Register ← Register

ALU/MAC/SHIFT Operation with Register ← Data Memory

ALU/MAC/SHIFT Operation with Register ← Program Memory

ALU/MAC Operation with Data Memory → Register

and Program Memory → Register

Program Flow Control

Conditional Jump

Conditional Subroutine Call

Conditional Return

Conditional Trap

Conditional Do. . . . Until

Miscellaneous

Saturate Accumulator

Modify Index Register

Push Status Stack

Pop Status/Loop/Counter/Program Stack

Mode Control

No Operation

The program-flow instructions direct the activities of the program sequencer. Their execution can be either unconditional or dependent on count expiration or current status-register contents. Miscellaneous instructions include saturation of the MAC output register, manual modification of address-generator index registers, and manual pushing and popping of the various internal stacks.

#### AIDS TO SYSTEM DEVELOPMENT

Hardware and software development tools for the ADSP-2100 shorten the system design cycle. The software tools consist of five modules: an assembler, a linker, a simulator, a PROM splitter, and a system builder (that defines the target hardware). In addition, an ADSP-2100 Emulator provides the necessary hardware to debug user-developed programs in the target system.

Modular design eases software development by permitting a complicated program to be divided into easier-to-handle modules. Programmers develop code for the ADSP-2100 by writing assembly-language modules with the ADSP-2100's assembly instructions. Modules can be assembled separately, then connected together with the Linker, which generates a complete executable program by linking together program modules that were assem-

bled separately. The linker uses the hardware environment model specified by the user with the system builder. The system builder specifies important details of the target hardware, like the address range of program memory, data, and I/O ports.

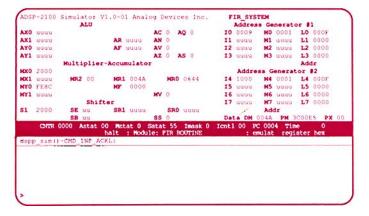

Before committing to final hardware, the designer can test the system's software by calling up the simulator. The simulator has a friendly, interactive user interface, to permit the user to monitor the simulated status of all internal and external hardware as well as the current program instruction. Programmers can display the contents of all on-chip registers (Figure 3), cache memory, and external program and data memories. In addition, the simulator permits programmers to step through code on a line-by-line basis to track all internal and external conditions.

Figure 3. Basic simulator screen, showing the state of the ADSP-2100's registers at a given instant; data is in hexadecimal notation. Note the registers associated with each section of the processor. The values labeled "uuuu" are undefined.

The software tools are available for VAX computers running under the VMS operating system and for IBM PC personal computers running under MS-DOS.

When the target system reaches the hardware stage and is ready for debugging, the stand-alone in-circuit emulator provides full-speed (8-MHz) execution, monitoring, and control. The emulator can run executable code from its own 32K words of program RAM or from the target system's memory. Its user interface is identical to that of the simulator. The emulator also allows multiple-processor configurations and can supply trigger signals to external instruments.

#### EXAMPLE—FIR FILTER

The FIR filter, perhaps the simplest subsystem one might use the ADSP-2100 for, demonstrates the chip's power by implementing a discrete convolution between a series of input samples and a set of coefficients in fewer than 10 instructions. In this example (Figure 4), written in assembler syntax, the availability of a new data point from an a/d converter creates an interrupt; the service routine, when called, fetches the data point, performs an FIR calculation—using coefficients stored in program memory and the requisite number of recent data points (equal to "taps\_less\_one") stored in data memory, outputs the new data point through a d/a converter, and returns from the interrupt.

```

FIR FILTER EQUATION: y(n) = \sum_{k=1}^{L-1} h(k) \cdot x(n-k)

.MODULE/ROM

fir_routine; (relocatable fir_routine interrupt)

. INCLUDE

<const.h>;

[include constant declaration file]

ad_sample;

da_data;

. PORT

. PORT

.ENTRY

fir_start;

.CONST

taps_less_one = taps-1

FIR START:

[subroutine code section]

CNTR = taps_less-one;

SI = DM(ad_sample);

DM(I0,M0) = SI;

(read from port)

MR=0, MY0=PM(I4,M4), MX0=DM(I0,M0);

DO convolution UNTIL CE;

MR=MR+MX0*MY0(SS), MY

convolution:

MY0=PM(I4,M4), MX0=DM(I0,M0);

MR=MR+MX0*MY0(RND);

IF MV SAT MR;

DM(da data) = MR1;

(write to port)

(return from interrupt)

. ENDMOD:

```

Figure 4. Summary of FIR filter interrupt service routine, showing program steps. The actual convolution occurs during successive repetitions of the one-line DO...UNTIL loop.

In the assembler description of the module, "FIR\_ROUTINE", the file, "CONST", contains "taps\_less\_one", equal to the number of taps\* minus 1. Memory-mapped locations for I/O ports are referenced as AD\_SAMPLE (input port) and DA\_DATA (output port). This interrupt service routine is entered at the point FIR\_START. (Elsewhere, in the main\_routine, the interrupt vector address is loaded; data buffers, coefficient addresses, and the counter are initialized; the address generator Modifier registers (M0 and M4) are set at 1, so that during loops the addresses are incremented by 1 on each pass, and the data buffer is cleared.)

When "FIR\_START is called, the counter is set to the constant, taps\_less\_one; in the next cycle, the value of ad\_sample is read from its memory-mapped port to register SI; then that data is moved from SI to the data memory address stored in register 10, modified by the contents of M0; then, the multiplier output register, MR, is cleared (i.e., set to zero), and—at the same time—the data (i.e., filter coefficient) stored in program memory at address (14) is written to multiplier input register MY0, and the input data at (10) is written to multiplier input register MX0.

The next instruction, DO convolution UNTIL CE (count expires), initiates the loop (indented) in which the contents of register MR are added to the signed product of MX0 and MY0, while—during the same cycle—the next values of data and coefficients are fetched to MX0 and MY0 from memory locations determined by the incremented address generators, as the counter counts down. When the counter reaches zero, the next instruction (multiply and add, with rounding) is executed. Then the overflow flag is checked; if an overflow has occurred, the output is saturated (viz., set to full-scale). Finally, the value stored in register MR1 (the most-significant word) is written to the d/a converter, and the program returns from the interrupt.

Portions of this article are drawn from an earlier article by John Roesgen and Sayuri Tung, "Moving Memory Off Chip, DSP  $\mu$ P Squeezes in More Computational Power," ELECTRONIC DESIGN, February 20, 1986.

<sup>&</sup>quot;Note that the powerful use of symbolic references, such as "taps" and "taps\_ less\_one" makes it easy to change the number of taps without changing the program.

## 16-BIT DAC IS 16-BIT MONOTONIC—ALL GRADES & TEMP RANGES

Low-Noise, Voltage-Output, Single-Chip AD569 Is  $\mu$ P-Compatible, Double-Buffered High DC Stability with 100-kHz Analog Bandwidth, 3  $\mu$ s 16-Bit Settling Time

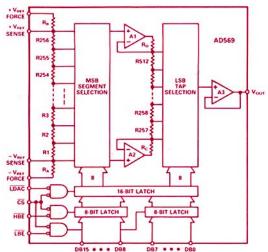

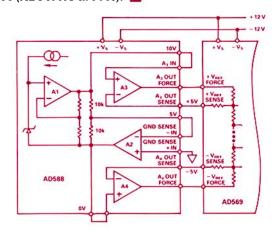

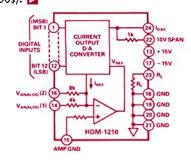

The AD569\* is a monolithic voltage-output 16-bit multiplying d/a converter with true 16-bit resolution: all grades are monotonic over temperature. Its double-buffered digital input is compatible with 8- or 16-bit microprocessor buses. The analog output, via a buffer follower (Figure 1), delivers ± 5 volts at up to 5 mA and can stably drive up to 1000 pF of capacitive load. Its analog (reference) input terminals are in force-sense pairs to preserve gain and offset accuracy in the presence of wiring and ground resistance.

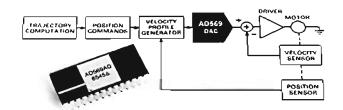

The AD569 is useful for the many instances where one of 64K possible words of digital data must be converted to an analog output, with unique and monotonically increasing analog values corresponding to binary data. Typical applications include closed-loop process control, position servo applications, building block for 16-bit-resolution a/d converters, and high-precision waveform generation<sup>†</sup>. Its multiplying capability permits digitally controlled scaling to be applied to analog input signals, analog inputs to control the gain of digitally generated waveforms, and—in conjunction with the AD588 monolithic precision voltage reference <sup>‡</sup>—the implementation of a high-stability fixed-reference DAC (Figure 2).

Figure 1 shows the unique two-stage voltage-segmented architecture of the AD569. There are two cascaded tapped strings of 256 (=  $2^8$ ) equal resistors in series, buffered by unity-gain followers. The reference voltage,  $V_{REF} = +V_{REF} - (-V_{REF})$ , is divided into a series of (ideally) equally spaced voltages appearing at the taps of the first string.

When a 16-bit digital word, of value 256 M+L, is latched in, the (M)ore-significant 8-bit byte is decoded, and the difference voltage,  $V_{REF}/256$ , across the (M+1)th resistor, is buffered and applied to the second voltage divider. The (L)ess-significant 8-bit

Figure 1. The AD569 is a pair of cascaded 8-bit tapped voltage dividers, buffered by unity-gain followers.

byte is decoded and the output voltage at the Lth tap, referred to  $-V_{REF}$ , is equal to the voltage at the lower tap of the first string,  $V_{REF}$  (M/256), plus the product of the output difference of the first string ( $V_{REF}$ /256) and the divider ratio of the second string,  $V_{REF}$ (L/256), i.e.,

$$V_{OUT} = V_{REF} \left[ \frac{M}{256} + \frac{L}{256^2} \right] = \frac{256M + L}{65,536}$$

The dividers are inherently monotonic; and monotonicity at segment boundaries is preserved, despite offsets in the difference amplifiers, by a leapfrogging switching scheme that lets each amplifier work on both sides of alternate taps. In order to obtain the advantages of cool (200 mW dissipation), compact, fast CMOS logic and nonloading switches, and at the same time retain the low drift and noise of fast-settling (3 µs to 0.001% FS) bipolar amplifiers, the Analog Devices BiMOS II process is used.

The result is a maximum differential nonlinearity specification of  $\pm 1$  LSB over temperature for all grades. Integral nonlinearity is  $\pm 0.024\%$  max over temperature for the K/B grades; however, it is stable over both time and temperature (typically  $< \pm 0.25$  LSB per 1,000 hours), owing to the untrimmed architecture of the DAC. This permits 16-bit linearity over temperature to be achieved and maintained with software error correction alone.

Packaging is in ceramic (plastic available soon). Prices start from \$28.00 (AD569AD in 100s).

Figure 2. Kelvin connections (complementary use of forcesense terminals) with ultra-low drift tracking reference puts the reference voltage precisely at the active ends of the first resistor string, in the same way the buffer followers' feedback puts the tap difference voltage across the second string.

<sup>\*</sup>Use the reply card for technical data.

For a typical user application, see "Plug-in Card Generates Arbitrary Waveforms," Electronic Design, Oct. 2, 1986 (pp. 49-50).

<sup>&</sup>lt;sup>‡</sup>The recently announced AD588 will be covered in some detail in the next issue of this Journal.

### COMPACT LOW-COST SIGNAL-CONDITIONING MODULES

The 5B Series Features Direct Sensor Interface, 1,500-V rms Isolation, High Noise-Rejection,  $-25^{\circ}$ C to  $+85^{\circ}$ C Operation, No Adjustments

by Kathryn Kasper

The 5B Series modules\* are a family of plug-in single-channel signal conditioners for sensors. Readers familiar with the 3B Series subsystem (Analog Dialogue 16-3, 1982, pp. 7-9) will recognize the 5B Series modules as a new generation characterized by even higher performance, smaller size, and lower price; we expect that users will take to them as enthusiastically as they adopted the 3B Series for monitoring analog signals such as pressure, temperature, and flow in industrial data-acquisition applications.

A new circuit design using transformer-based isolation combines with automated surface-mount manufacturing technology to provide compactness and high performance at low cost. Joining these features with operation on a single +5-V supply, 1,500-V rms isolation and  $\pm 0.05\%$  calibration accuracy, the 5B Series is an attractive alternative to expensive commercial signal conditioners and in-house designs for industrial applications. Substantial discounts in quantity encourage OEM use in systems; the 5B Series modules are priced at less than \$80 in quantity.

In addition to the 5B Series modules, physically and electrically compatible backplanes are available to make it easy to assemble the modules into complete signal-conditioning subsystems. As many as 16 modules can be placed in a 19" rack-mountable backplane that requires only 3 ½" of panel space.

#### RUGGED, COMPLETE, HIGH-PERFORMANCE

All modules are identical in pinout and size (2.25" × 2.25" × 0.60"). Users can mix and match them to meet the specific needs of the application, and they can be changed without disturbing field wiring. Each module provides complete signal conditioning, optimized for the nature of its input. Signal-conditioning functions include input protection, filtering, chopper-stabilized low-drift amplification, isolation, linearization for RTD inputs, and excitation for sensors when required. Table 1 is a summary of module types available at this printing.

The specifications and packaging of the SB Series were designed for industrial applications. Each module has factory-calibrated

\*Use the reply card for technical data.

TABLE 1. 5B Series Modules and Backplanes Available in Late 1986.

| INPUT MODULES                                     |                    |           |

|---------------------------------------------------|--------------------|-----------|

| Input Type/Span                                   | Output             | Model     |

| DC, $\pm 5 \text{ mV to } \pm 500 \text{ mV}$     | 0-5 V or ±5 V      | SB30,5B40 |

| DC, $\pm 500 \text{mV}$ to $\pm 10 \text{V}$      | $0-SV$ or $\pm 5V$ | 5B31,5B41 |

| Process Current, 4-20 mA or 0-20 mA               | 0-5 V              | 5832      |

| Thermocouple types J,K,T,E,R,S,B                  | 0-5 V              | SB37      |

| 2,3,4-wire RTDs:                                  |                    |           |

| 100-Ω Pt, 10-Ω Cu, 120-Ω Ni                       | 0-5 V              | SB34      |

| OUTPUT MODULES                                    |                    |           |

| $0 \text{ to } + 5 \text{ V or } \pm 5 \text{ V}$ | 4-20 mA/0-20 mA    | SB39      |

| BACKPLANES (WITH COLD-JUNCTION SENSORS)                |      |

|--------------------------------------------------------|------|

| 16 channels, pin-compatible with 3B Series             | 5B01 |

| 16 channels, with "analog 3-state" output multiplexing | SB02 |

| 1 channel, DIN rail companible                         | 5B03 |

$\pm 0.05\%$  accuracy and features 1,500-V rms isolation,  $\pm 1 \mu V/PC$  input drift, and 240-V protection for all field terminations. All modules feature excellent common-mode rejection, meet IEEE 472-1974 surge-withstand specs, and operate over the  $-25^{\circ}C$  to  $+85^{\circ}C$  temperature range. Physically, the 5B Series is rugged: The modules are hard-potted and have sturdy 0.04-inch pins; there are no adjustment potentiometers. The inaccuracies that could be introduced by these mechanically sensitive devices are avoided, and system integrity is improved since there are no exposed field adjustments.

#### ISOLATED INPUT MODULES

The modules listed in Table 1 are available in standard ranges that address most input requirements. However, the flexible laser-trim process that ensures calibration accuracy to within 0.05% can be used for calibration of other input spans. This custom ranging capability allows you to map any input range into the full output span, thereby improving system resolution within that narrow range. The 5B Series input modules require only a single +5-volt supply; they consume about 0.15 W typically.

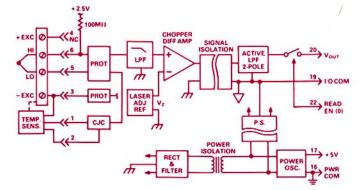

Example: 5B37 Thermocouple input module Figure 1 is a diagram of the 5B37 transformer-isolated thermocouple input module. The

Figure 1. Block diagram of 5B37 thermocouple module.

1,500-V isolation provides both protection and 160 dB of common-mode rejection and assures compliance with IEEE 472-1974:SWC. As is the case with all modules, 240-V normal-mode input protection prevents damage if line voltage is accidentally connected to its input terminals. Cold-junction compensation circuitry corrects for ambient temperature and its variations.

Like all the input modules, the 5B37 includes a self-multiplexed output—a low-resistance series output switch (much like digital 3-state), controlled by a TTL-compatible Enable input. If the switch is not used (single channel or conventionally multiplexed applications), the Enable input can be grounded.

#### **OUTPUT MODULE**

The 5B39 Output Module (Figure 2), provides an isolated 0-20-mA or 4-20-mA process-current output. It provides the same level of protection as the input modules, 1,500-V rms isolation and 240-V rms continuous output protection. Maximum load resistance is  $750\Omega$  and power consumption is 0.85 W.

Figure 2. 5B39 output module.

The voltage input to this module is latched—if need be—in a track-hold circuit. When each module is updated by its track-hold under logic control, one d/a converter can serve numerous output channels. With the Enable lines grounded, the modules can be used with one DAC per channel.

Figure 3 shows a general application of input and output modules in a system.

#### SYSTEM DESIGN

The functionally complete 5B Series modules are easily applied in the designer's own circuit board or backplane. The modules have a simple pinout; they plug into widely available sockets; and they are secured with self-contained mounting screws. The output

Figure 3. General measurement-and-control application.

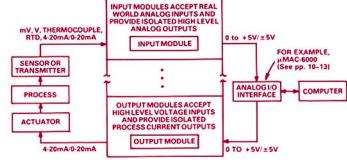

switch eliminates the need for an external multiplexer with input modules and the track-hold in each output module allows a single DAC to serve numerous output channels. For thermocouple applications, cold-junction-compensation sensors are available as one-piece pre-calibrated units. An example of an *integrated system* is shown in the following pages, where the modules are used with the  $\mu$ MAC-6000 backplane.

#### **5B SERIES SUBSYSTEMS**

Complete 5B Series subsystems reduce user design effort. A family of backplanes, precalibrated plug-in modules, direct sensor interface via screw-terminal connections, standardized high-level outputs, and ribbon-cable system interface result in easy integration into any system. For thermocouple applications, high-accuracy cold-junction compensation sensing is inherent on each channel.

To address diverse applications, the 5B Series includes a growing family of backplanes (Table 1). The 5B01, a 16-channel backplane that can be mounted in a  $19'' \times 3.5''$  panel space, provides 16 single-ended input/output plugs on the system connector; it is pin-compatible with the 3B Series (note, however, that the 5B Series has a  $\pm 5$ -V output swing, while the 3B Series has a  $\pm 10$ -V output swing). The 5B02 (Figure 4) has input and output buses, which take advantage of the built-in switching in the modules. With the 5B02, external input multiplexers are not needed for inputs, and only a single output DAC is needed. For single-channel applications, the 5B03 DIN-rail-compatible socket is available.

The 5B Series delivers, for the first time, a low-cost solution to industrial signal conditioning. The family will continue to evolve, as backplanes and modules are added to meet user demand.

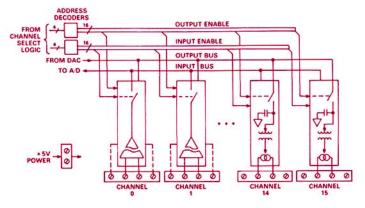

Figure 4. Diagram of the 5802 backplane.

## EXPANDABLE MODULAR I/O PROCESSOR FOR INDUSTRIAL AUTOMATION

μMAC-6000 Handles Real-World Analog and Digital Signals

Provides Isolation, Signal Conditioning, Conversion, Processing, Communications

By Bill Schweber

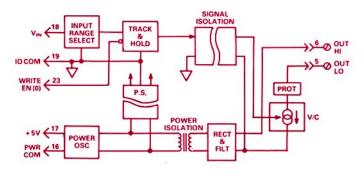

The µMAC-6000\* is a modular multiple-input/output processor system for analog signals and digital decisions. It combines computing, communications, and sophisticated software. Alone, or with a host computer, it monitors and controls processes and machinery. Designed for OEM use, it finds applications in equipment monitoring, continuous control, test-stand automation, and energy management. Each plug-in signal-conditioning module addresses one channel; thus users can custom-configure inputs and outputs. Expansion with extra processing power makes it possible to increase the number of channels with little effect on performance.

This newest member of the  $\mu$ MAC family of programmable systems for real-world measurement and control evolved from the technical and product experience gained by Analog Devices and its customers with the earlier  $\mu$ MAC-4000 and  $\mu$ MAC-5000 systems [Analog Dialogue 15-1 (1981) and 17-3 (1983)]. The  $\mu$ MAC-6000 is manifestly similar to, yet better—faster, more modular, and more configurable—than either of its predecessors.

####

In the fall of 1980, Analog Devices introduced the µMAC-4000 system. This "Micro Measurement-And-Control" system endows virtually any computer with real world input and output capability (thermocouples, currents, voltages, on/off signals). Connected to the RS-232 or 20-mA current-loop serial ASCII port of any computer, and operating in a command/response mode, the µMAC-4000 uses ASCII characters to pass data. The host computer generates an ASCII string with a request (for the temperature of the signal on Channel 1, for example), and the µMAC-4000 returns the value, e.g., 47 degrees.

Besides the serial interface and the analog-to-digital converter, the main circuit board of the µMAC-4000 contains all the electronics needed for high-quality, isolated signal conditioning of the analog inputs. This single board (which could be expanded with additional boards)—and such computers as the HP-85, Apple II, IBM PC, and PDP-11—form data-acquisition, measurement, and control systems for such applications as laboratory automation, temperature monitoring, and water treatment. All of the µMAC-4000's acquired data is processed at the host, which also makes the decisions and requests the necessary outputs.

User needs and requests, along with technology advances, led to the announcement of the  $\mu$ MAC-5000 in late 1983. While the  $\mu$ MAC-5000 resembles the  $\mu$ MAC-4000 (and uses many of the same expansion cards) there is a major difference: the  $\mu$ MAC-5000 is user-programmable in  $\mu$ MACBASIC, a real-world-I/O version of BASIC (see below). The advantages of user programmability are vital:

The user application program can reside on and execute from the  $\mu$ MAC-5000 board, allowing it to perform data acquisition & processing and to make decisions, functioning independently of the communications link between the  $\mu$ MAC-5000 and the host.

\*Use the reply card for technical data.

Also, the overall integrity of the system is increased. The link to the host is used mainly for transmitting overall application parameters (such as loop constants) to the  $\mu$ MAC-5000 system on startup or summary data back to the host. If the communications link to the host is down, the  $\mu$ MAC-5000 can continue to function and perform the application.

The entire applications program can be burned into programmable read-only memory (PROM), which is then installed on the board, fully resident and ready to execute as soon as power is applied, making the  $\mu$ MAC-5000 ideal as a stand-alone, dedicated controller for machinery (such as extruders and testing) or for dedicated data logging and fixed-function control applications. No host computer is needed in these applications; the  $\mu$ MAC-5000 can drive a local operator terminal or annunciator screen.

#### μMACBASIC: THE LANGUAGE OF THE μMAC-5000

A key feature of the µMAC-5000 (and µMAC-6000) is the µMACBASIC language, developed by Analog Devices for the system's real-world, real-time applications. Standard BASIC, though easy to use and familiar to both programmers and non-programmers, lacks several features that are necessary for good, effective real-world applications programs. µMACBASIC adds them:

With integral I/O statements, an analog or digital input or output can be incorporated into the applications program. Keywords were added to BASIC; for example, to input an analog signal simply requires using the keyword AIN, along with parameters that define the analog signal's physical input (connection location and type). Once the system executes this keyword, all of the internal details needed to find the input channel, connect the a/d converter to the appropriate input channel through the multiplexer, make the conversion, and translate the converted value to engineering units are done automatically and transparently to the user.

Procedures and Functions were added for a more structured BASIC. Traditionally, BASIC programs result in intertwined "spaghetti" code because programmers, using GOTO statements, have difficulty efficiently structuring the flow chart and corresponding program. In addition, the requirement to use a single set of line numbers and unique variable names makes it hard for more than one programmer at a time to work on a single application,

without causing conflicts. µMACBASIC's Procedures and Functions allow programmers to develop independent modules of code; they can be called from the main program by name.

Real-time operation is a necessity for most applications where real-world signals must be measured and controlled, since timing is critical to the process. It is important to update the control loop at exact intervals, e.g., 100 ms, rather than approximate intervals variable from 50 to several hundred ms, depending on program flow. With \(\mu\)MACBASIC's real-time interrupt capability, the user application program can specify that certain activities occur at a desired rate; unplanned events (such as characters arriving via a communications port) are handled efficiently but do not delay time-sensitive events.

#### μMAC-6000—THE NEW GENERATION

The  $\mu$ MAC-6000 was designed to incorporate preferred features of the previous  $\mu$ MAC models and maintain the high level of system integration, which makes the  $\mu$ MAC attractive in so many applications. Key goals included improved performance, attractive pricing, and an architecture that was:

- more modular, in hardware and I/O, with rugged, removable major assemblies

- more configurable, so that the end user could tailor the final configuration to fit system needs

- · more flexible, to meet the needs of a wide range of applications

- more expandable, to grow as users' needs grow, yet maintain the required level of overall performance

- · more powerful, using today's highly integrated ICs.

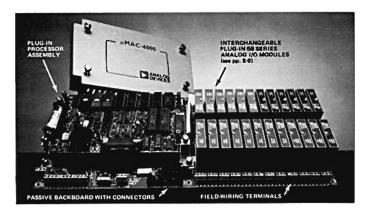

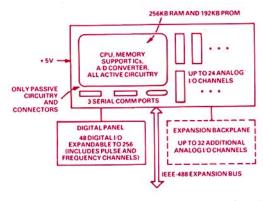

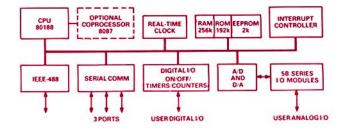

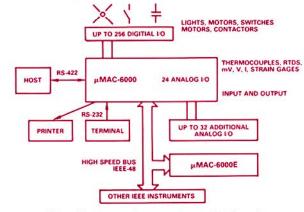

Figure 1. Basic configuration of the µMAC-6000.

Figure 1 shows the functional block diagram of the  $\mu$ MAC-6000. A single backplane supports the major building blocks:

- a 16-bit 80188 CPU with support chips, memory(256K bytes RAM, 192K ROM, and 2K EEPROM), a/d and d/a converters, and communications-support ICs

- interchangeable low-cost analog I/O modules, all electrically isolated. They are the new 5B series (see pp. 8-9), which provide 1,500-volt isolation, excellent performance, and a wide choice of analog input and output conditioning for thermocouples, valves, current loops, voltage signals at various levels, and other transducers. Each channel's unique requirements are met by an appropriate module—the ultimate in flexibility and modularity.

- connectors for the digital I/O. They can connect directly to low-level (TTL) digital points, or via solid state relays to higher-voltage, higher-power points. Examples of digital I/O include switch closures, relays, counters, frequency inputs, and time-proportional outputs with varying duty cycles.

- communications ports, both serial-type (two RS-232 and one isolated RS-422) and IEEE-488 (GPIB).

- screw terminals for the +5 Vdc power supply, which is the only power needed to run the entire μMAC-6000 and VO modules.

As with the  $\mu$ MAC-5000, the heart of the system is the CPU. But in the  $\mu$ MAC-6000, the backplane plays a critical role in meeting the design objectives; it is the physical support for the CPU, I/O field-wiring connectors, communications connections, and power. It is entirely passive, containing no active components.

The active blocks of the system—the CPU module—in its protective metal enclosure—and the I/O modules—are all easily removable from the backplane, without disturbing the field wiring; and they can be installed after the rack- or panel-mounted backplane has been wired completely and the field wiring checked out. Any 5B-series analog I/O module can be changed easily by loosening a single screw. Should a CPU unit require changing, it can be removed by loosening 4 screws.

Interchangeability means that any one of the 24 analog I/O locations on the backplane can be used for any 5B module—input or output. Users can change input sources at any channel or turn it into an output channel simply by putting the appropriate 5B module into a socket and identifying the module in software. As I/O needs vary, the I/O can be quickly changed.

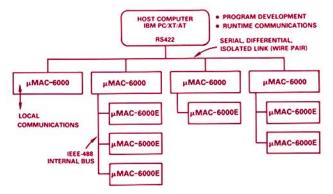

The µMAC-6000 system supports three serial-communications ports and one high-performance IEEE-488 port. The serial ports are used for connection to host computer, local terminal, and printer—and multidrop configurations with other µMAC-6000s.

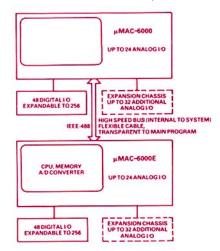

The IEEE-488 port has two purposes. First, it can be used as the internal bus to connect dedicated intelligent expansion units (called µMAC-6000E) to the main unit (Figure 2). It can also be

Figure 2. Expanded  $\mu$ MAC-6000 systems using expansion chassis and  $\mu$ MAC-6000E.

used to connect a  $\mu$ MAC-6000 to a host (using the IEEE-488 interface standard) or a specialized electronic instrument, such as a gas analyzer or high-resolution voltmeter (Figure 3).

a. Host and µMAC-6000. b. µMAC-6000 and instrument. Figure 3. IEEE-488 communications.

#### **EXPANSION**

In many application the number of channels is large but the rate at which these channels have to be sampled is relatively low. A good example of this is a large temperature-monitoring installation, which has many thermocouples attached to critical points on an engine. The  $\mu$ MAC-6000 is designed for the number of channels of analog I/O to be increased beyond the basic 24; each  $\mu$ MAC-6000 backplane has an analog expansion connection for two additional 16-channel backplanes, which can hold up to 32 5B Series modules of any type. Effectively a physical extension of the main backplane, it doesn't have a CPU, ADC, memory, or any other processor components; it brings the total number of channels that a single  $\mu$ MAC-6000 can support by itself to (24+32=)56.

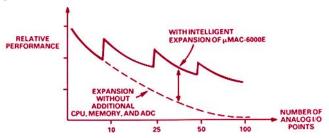

The overall throughput and performance decrease as the CPU and A/D converter must service the increasing number of channels (dashed curve in Figure 4). For applications where this is intolerable, intelligent expansion is available using the  $\mu MAC$ -6000E. Each  $\mu MAC$ -6000E brings another CPU and ADC into the system, so that more I/O channels can be handled without severe degradation in performance (solid curve).

Figure 4. Avoiding performance deterioration in expanded systems by *intelligent* expansion. Performance vs. number of I/O points.

Up to three such units, acting as IEEE-488 talker/listener devices, can be connected via the IEEE-488 bus to the main, master µMAC-6000, acting as the IEEE-488 controller.

The user's ability to add modular CPU and A/D units to the system as the number of I/O channels increases makes the µMAC-6000 unique. Unlike most data acquisition and control systems, the µMAC-6000 architecture allows the channel expansion—when necessary—to include an additional CPU and a/d converter via the µMAC-6000E, so overall performance degrades much more slowly.

Each  $\mu$ MAC-6000E is physically and electrically very similar to the basic  $\mu$ MAC-6000; it can handle the same amount of realworld analog and digital I/O as the basic  $\mu$ MAC-6000, including "dumb" expansion. The result of this design is that a user can start with a standard 24-analog-channel  $\mu$ MAC-6000, add up to 32 more analog channels, and/or use additional  $\mu$ MAC-6000E units to increase channel capacity and processor power as needed.

The digital VO has not been neglected either; both analog and digital VO can grow with the needs of the application (a typical installation has 1 or 2 digital points per analog point). Each  $\mu$ MAC-6000(/E) can directly interface with up to 48 digital VO points. In addition, a multiplexed digital VO panel is available; it allows the same physical connector of the  $\mu$ MAC system to handle up to 256 channels. The user can upgrade capacity in this way at any time, even in the field, by simply changing digital VO panels; no changes are made to the basic  $\mu$ MAC-6000 system.

#### SYSTEM SOFTWARE

When the system is programmed in µMACBASIC, the statements for real-world I/O and real-time operation tie together all the hardware pieces of the system—I/O, CPU, memory, timers, etc., so that the user sees a fully integrated system, despite its building-block nature. One or more µMAC-6000E units can be added without affecting the level of integration; the µMACBASIC statements have a simple argument list which allows the user to identify whether the I/O channel is on the main µMAC-6000 board or an IEEE-488-linked µMAC-6000E. Handshaking and operating details for passing data over the bus are automatic; they are made transparent to the user by the µMAC-6000's operating-system software and programming language. The real-time clock keeps time accurately, even when power is off.

The user's program can be stored in the on-board RAM (256K bytes), fully backed up by a socket-mounted lithium battery, which can be replaced at the end of its 6+-month life without turning off the power. For greater non-volatility, the program can be burned into PROM.

While the µMACBASIC language is convenient and flexible, many programmers want the benefits of more-powerful, standardized languages; accordingly, the µMAC-6000 is available with the C language instead of µMACBASIC. C is a transportable language that improves memory usage, speed, and efficiency with the existing hardware. Figure 5 compares a µMACBASIC program fragment with the same fragment written in C.

```

μΜΑCBASIC

100 Value = (Ain(1) + Ain(2)) / 2

110 If Value > Hi_Val Then Print "ALARM"

Else Print Value

ret1 = ain(1, &val1);

ret2 = ain(2, &val2);

value = (val1 + val2) / 2.0

if (value > hi_val)

printf ("ALARM")

else

printf ("%f", value);

```

Figure 5. Comparison of syntax in µMACBASIC and C: Sampling two input values, averaging them, and printing if in range or sounding alarm if not.

An IBM PC is used as the development tool for µMACBASIC-6000 C. In the C version of µMAC-6000, the compiled C object code is linked to its Clibraries; the linked code is downloaded from the PC to the µMAC-6000, where a special C operating-system PROM allows this object code to execute properly and perform real world I/O, as called for by the user program. The C PROM on the µMAC-6000 requires less memory than the µMACBASIC PROM, leaving more PROM space for user programs.

The processor board of the  $\mu$ MAC-6000 is designed to accommodate an optional 8087 numeric co-processor IC, which increases the speed of numeric computations by factors from 20 to 100. The 80188-8087  $\mu$ MAC-6000 system with C gives highest performance.

#### COMMUNICATIONS AND SOFTWARE TOOLS

The ability to effectively develop programs for a system like the  $\mu$ MAC-6000 depends on the right development tools. The usefulness of the  $\mu$ MAC-6000 when actually running the application is

related to the communications topologies and run-time software available.

The  $\mu$ MAC-6000 system can be connected to a host via RS-232 or RS-422 serial interface ports. The RS-422 port on the system backplane is specifically designed for noisy environments and *multidrop communications*; two twisted pairs of wires can link up to 10  $\mu$ MAC-6000 systems, at distances of several thousand feet, to a host (Figure 6).

Figure 6. μMAC-6000s in various systems using multidrop topology.

The µMAC-6000 has two software tools available:

For developing the program, program-development software (PDS) is used. With PDS, the user types program lines of code on a terminal or IBM PC (acting as a workstation) connected to the  $\mu$ MAC-6000; they are edited and stored on floppy disks. Programs can be recalled and downloaded to the  $\mu$ MAC-6000. Any  $\mu$ MAC-6000 connected via the multidrop line can be addressed uniquely; new lines of code can be sent to it while other units continue to run.

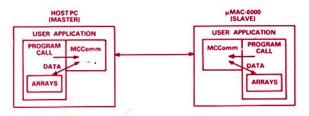

For communications between the host and the  $\mu$ MAC-6000(s) while running the application program, a software package called *MCComm* is available. MCComm\* is a master/slave protocol which allows a host computer program to transfer arrays of data or strings to the  $\mu$ MAC-6000, or request that a specified array or string be returned from the  $\mu$ MAC-6000 to the host. Through this mechanism, data transfer in both directions is achieved (Figure 7).

Figure 7. Master-slave operation using MCComm link.

#### SALIENT POINTS OF SYSTEM DESIGN

Figure 8 is a simplified block diagram of the CPU assembly. The analog inputs from the 5B-series modules can be read directly by the ADC or first passed through a 10-kHz filter to minimize high-frequency noise. The choice of filter-in or -out is made by a parameter in the argument list for analog input-conversions and can be changed as input noise conditions require. The a/d converter has software-selectable resolutions of 12 or 14 bits, using a 12-bit a/d converter, a 14-bit DAC, and subranging; the additional time for conversion to 14 bits is 1 conversion cycle. Either resolution can be called for at any time as needed.

Figure 8. Block diagram of  $\mu$ MAC-6000's CPU and system architecture.

Among µMAC-6000's protective features, a simple software command permits the analog input subsystem to read the temperature of the CPU module, under its protective metal housing, in order to detect a potential heat problem and alert an operator. Similarly, the exact value of the +5 V dc supply at the CPU can be read by the program as part of a periodic self-check on the system status, especially if intermittent operation is suspected.

RAM is battery-backed. Special power-detection circuitry monitors the +5-V dc line. If system power should start to fail and supply voltage drops below a threshold, the processor is interrupted and critical register-saving routines are initiated. The user program is also interrupted to let the program know that there are milliseconds left in which to implement a special power-failing application routine, if present.

The CPU circuitry also has a "watchdog timer" function, calling for a periodic reset by the operating system. If a problem in the circuitry or software causes the reset to be missed, the watchdog output produces a state change of an open collector connected to a screw terminal on the system backplane. An alarm or indicator, if wired to it, can alert the operator to the problem.

#### CONNECTABILITY

A key factor in the µMAC-6000's usefulness is that it is designed to interconnect with a wide range of entities, from the broad repertoire of analog inputs and outputs available via the 5B modules, to communications with host processors and peripherals, to easy system expansion via the expansion chassis and the µMAC-6000E, to other instruments via the IEEE-488 bus (Figure 9). In this sense, µMAC-6000 is a universal input/output subsystem.

The μMAC-6000 includes the CPU enclosure—with μMAC-BASIC software in PROM—and the backplane. With discounts available for quantity, the μMAC-6000/6000E are priced at \$3,395/\$2,295.

Figure 9. The diverse universe that  $\mu MAC$ -6000 connects with.

<sup>\*</sup>For information on MCComm use the reply card.

## PRECISION WIDEBAND THREE-PORT ISOLATION AMPLIFIER

## AD210 Has 2,500-V Continuous RMS CMV rating, 0.012% Nonlinearity, 20-kHz BW Design Expertise, Surface-Mount Combine for Highest Performance & Low Cost

by James Conant

The AD210\* is a complete high-performance three-port isolation amplifier in a  $1.00'' \times 2.10'' \times 0.35''$  (25.4 × 53.3 × 8.9-mm) package. Its input, output, and power sections are isolated from one another for continuously applied common-mode voltages up to 2,500 volts rms at 60 Hz ( $\pm 3,500$  volts peak).

Salient features include: maximum nonlinearity specification of  $\pm 0.012\%$  (AD210BN), 20-kHz full-power -3-dB bandwidth, and 2- $\mu$ A-rms maximum leakage current at 240 V rms, 60 Hz. The input amplifier is an uncommitted op amp; the output stage is buffered by a unity-gain amplifier that can drive a 2-k $\Omega$  load to  $\pm 10$  V.

Typical applications for isolators include multi-channel data acquisition, high-voltage instrumentation amplifiers, current-shunt measurements, and process-signal isolation. With its 120-dB common-mode rejection (60 Hz, gain of 100, 500-ohm resistive imbalance) the AD210's isolation performance allows it to maintain signal integrity when making safe measurements of low-level signals in harsh industrial environments, where signal interference, ground faults, and transients are commonplace.

The AD210 owes its unequalled performance and user-oriented features to surface-mounted components and state-of-the-art automated assembly technology, backed by Analog Devices' 15 years of experience in the design and manufacture of isolators. The high performance, small size, and low cost of the AD210 make it ideal for application in process controllers, data loggers, welders, power monitors, motor controls, and test equipment.

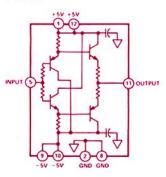

#### **HOW IT WORKS**

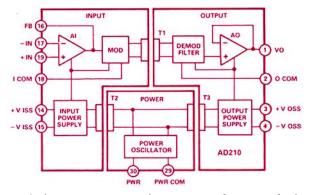

The AD210 (Figure 1) requires  $\pm$  15-volt dc ( $\pm$  10%) excitation, applied to the power section. A 50-kHz oscillator couples power to the input and output sections via isolation transformers T2 and T3. In both sections, the coupled power is rectified and filtered;  $\pm$  15 V dc is made available to operate all of the AD210's internal circuitry—and to provide up to 5 mA at  $\pm$  15 V dc at the power-output pins in both sections.

Figure 1. Input, output, and power sections are isolated from one another with 2,500-volt rms (3,500-V peak) common-moderatings.

The 50 kHz also serves as a carrier, modulated by the output of AI, coupled across the isolation barrier by transformer T1, synchronously demodulated and three-pole filtered (20-kHz cutoff) in the output section, and buffered by follower AO, which can drive low-impedance loads.

The three-port design permits the AD210 to be configured as an input or output isolator, in single- or multi-channel configurations. Besides eliminating the need for a separate dc-to-dc converter, the AD210 in fact serves as a pair of isolated power supplies (within its ratings) for circuitry sharing common ground returns with the input and output signals, for example, front-end preamps, remote transducers, etc.

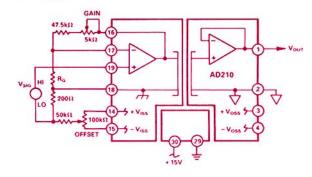

The uncommitted input op amp can be configured by the user for buffering and gain, filtering, summing, voltage ranging, and current inputs. In the example of Figure 2, amplifier AI is used as a non-inverting gain-of-100 amplifier; the isolated input power supply serves the input offset adjustment circuit.

Two performance grades are offered for operation over the  $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  temperature range, AD210AN and AD210BN. Specifications include: maximum gain drift  $\pm 50$  ppm/°C (and  $\pm 25$  ppm/°C, 0°C to  $+70^{\circ}\text{C}$ ); offset drift  $\pm 10 \pm 50$ /G  $\mu$ V/°C (and  $\pm 10 \pm 30$ /G  $\mu$ V/°C, 0°C to  $+70^{\circ}\text{C}$ ). Other maximum guaranteed specifications include (A/B): nonlinearity  $\pm 0.025\%$ / 0.012%; offset ( $\pm 15 \pm 45$ /G)/( $\pm 5 \pm 15$ /G) mV; gain error  $\pm 2\%$ /1%. Price in 100s is \$47 for AD210AN and \$56 for AD210BN.

Figure 2. Noninverting gain is set in the same way as for an operational amplifier. Floating power is used for offset trim.

<sup>\*</sup>Use the reply card for technical data.

### MONOLITHIC SYNCHRONOUS V/F CONVERTER: 0.005% MAX NONLINEARITY

Full-Scale Frequency (up to 2 MHz) Set by External System Clock No Critical Components Required; 25 ppm/°C max Drift; Dual or Single Supply

by Paul Klonowski

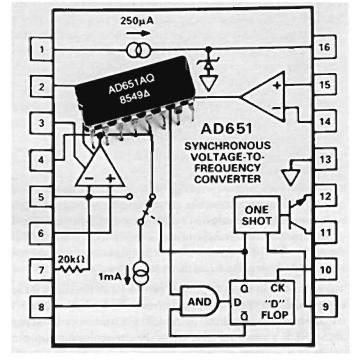

The AD651\* is a fast, high-precision single-chip charge-balance analog (voltage or current) to frequency converter. It is a synchronous VFC, in that its full-scale output frequency depends on an external clock frequency instead of the usual external capacitor in a one-shot oscillator circuit. The result is a stable, linear transfer function, with significant application benefits in both single- and multi-channel systems. Applications include a/d conversion, process control, analytical and medical instrumentation, isolated data acquisition, and frequency-to-voltage conversion.

The AD651 works with either single or dual power supplies and requires only a single non-critical integrating capacitor. Maximum nonlinearity is  $\pm 0.005\%$ , for full-scale output frequency up to 1 MHz (B grade), increasing to only  $\pm 0.02\%$  at 2 MHz, while maximum gain drift, over the temperature range, is only  $\pm 25$  ppm/°C for frequencies up to 500 kHz, increasing to  $\pm 50$  ppm/°C at 2 MHz. Corresponding figures for the A & S grades are 0.02% and  $\pm 50$  ppm/°C, increasing to 0.05% and  $\pm 75$  ppm/°C over their respective temperature ranges. It is available in a 16-pin Cerdip package; prices start at \$7.95 (AD651AQ, 100s).

#### **ABOUT VFCs**

A typical charge-balance V/F converter<sup>1</sup> is based on an integrator that has two modes, integration and reset. The input signal (I<sub>IN</sub>) is continuously integrated with respect to time, building up charge proportional to its average value; during the fixed reset period, —I<sub>REF</sub>, an opposing fixed current (hence a fixed charge) is integrated and subtracted from the accumulated input charge, giving the characteristic triangular waveform. Whenever the integrated input exceeds a threshold, a reset interval starts; its duration is determined by an external capacitor, which establishes the period of a

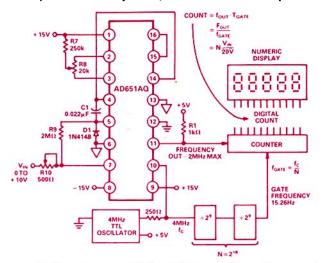

Figure 1. Synchronous VFC as high-precision a/d converter.

one-shot  $(T_{os})$ . Thus, the greater the input, the more often the reset phase occurs. The output pulse begins at the same time as the reset interval; therefore, the output frequency is equal to the number of Resets per second. The output relationship is:

$$f = \frac{I_{\rm IN}(avg)}{I_{\rm REF}T_{\rm os}} \tag{1}$$

Since  $T_{os}$  depends critically on a capacitance, output frequency is subject to the external capacitor's temperature coefficient and dielectric properties.

The synchronous VFC differs in that the length of the reset interval is precisely equal to the clock period. Thus,

$$f = f_c \frac{I_{\rm IN}(avg)}{I_{\rm REF}} \tag{2}$$

Since clock frequencies can be crystal-controlled,  $f_c$  may be eliminated as a source of error; thus, the major source of error has been removed. The remaining sources of error (which are present in both types)—reference, threshold, integrator, and switching errors—limit the performance, but are less significant than the one-shot's capacitor.

Besides accuracy, the synchronous VFC has other advantages: When used with a multi-phase clock, it can be multiplexed with similar VFCs to transmit several outputs over a single channel. In a/d conversion, where the digital output is determined by counting output pulses for a preset period, if the same clock drives the VFC and (through a suitable divider) sets the counting period, conversion accuracy is maintained independent of variations in clock frequency. Figure 1 shows how this is done in the design of a stable, low-noise a/d system with 16-bit resolution.<sup>2</sup>

<sup>\*</sup>Use the reply card for technical data.

For more information on VFCs, see Chapter 15 of the Analog-Digital Conversion Handbook (1986), D. H. Sheingold, ed., published by Prentice-Hall and available from Analog Devices (\$32.95).

<sup>&</sup>lt;sup>2</sup>For full details, see the Analog Devices Application Note: "Analog-Digital Conversion Using Voltage-to-Frequency Converters, by Paul Klonowski.

## HIGHEST-LINEARITY 16-BIT DAC IS DIGITALLY TRIMMABLE

## AD1147 & AD1148 Are The Most Accurate Hybrid DACs You Can Buy Internal 8-Bit Correction DACs Eliminate Offset- and Gain-Trim Pots

by Bill Sheppard

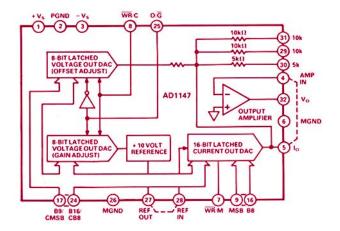

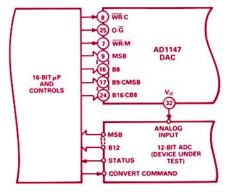

The AD1147 and AD1148\* are hybrid 16-bit voltage-output d/a converters in a 32-pin package. Both have a pair of latched 8-bit internal DACs for adjustment of reference and offset voltage under digital control (Figure 1). The AD1147 has true 16-bit integral and differential linearity, to within  $\pm \frac{1}{2}$  LSB (0.00076%), while the AD1148's linearity tolerances are  $\pm 1$  LSB.

Typical applications include adjustable precision reference voltage for equipment and laboratory applications, automatic test equipment, scientific instrumentation, beam positioners, and robotics.

Why correction DACs? Although the AD1147/48 have low initial offset and reference errors, the user's system often has initial offset and span errors, and they change with time and temperature. In a fixed-calibration system, the errors must be measured and the correction values computed in a calibration cycle; they must modify all subsequent data values on each conversion instruction. With the AD1147/48, the correction can be simply latched in to the correction DACs once; the actual data need not be changed.

The AD1147 and AD1148 provide two useful architectures for accomplishing this. Both accept data from a 16-bit bus and latch it into the main d/a converter. In the AD1148, the entire 16 bits are latched into a single register, while the correction bits are connected to a separate set of 8 terminals and multiplexed into the individual latched DACs for reference and offset. This allows for a separate 8-bit calibration interface, common in applications such as automatic test equipment.

In the AD1147, the correction inputs are multiplexed with the 8 least-significant bits of the 16-bit bus; Once the nominal input word is latched into the main DAC register, the 8 lesser bits can be used by the correction DACs for offset and reference adjustment.

Figure 1. The AD1147 multiplexes a precision 16-bit DAC with a pair of 8-bit gain- and offset-correction DACs on a 16-bit bus.

The AD1147 has a choice of four analog output ranges: 0 to  $\pm$  5 V, 0 to  $\pm$  10 V,  $\pm$  5 V, and  $\pm$  10 V—and two current ranges: 0 to  $\pm$  2 mA and  $\pm$  1 mA ( $\pm$  0.5-V compliance). When it is not used as a fixed-calibratable-reference DAC, its reference input is available for use in four-quadrant multiplying DAC applications with digitally adjustable offset.

Since the AD1148's calibration bus uses up all the available pins, its analog gain options are somewhat less flexible: fixed-reference only, with fixed (digitally adjustable)  $\pm 10$ -volt output range. However, it does have a price advantage over the AD1147. Prices in 100s are \$152 for the AD1147, \$138 for the AD1148.

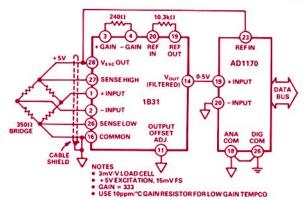

A typical application of the AD1147/AD1148 is in converter testing. For example, when the AD1147 is used as the source of analog voltage to test 12-bit converters, its error is less than 1/16 that of the device under test—essentially negligible. Figure 2 shows how an AD1147 would be used as a calibrated incremental voltage source in testing a 12-bit ADC under  $\mu$ P control. The AD1147's least-significant bits would be used as a "dither DAC" in finding transitions of the ADC, while the correction DACs compensate for the ADC's initial offset and gain errors.

Figure 2. ADC testing.

<sup>\*</sup>Use the reply card for technical data.

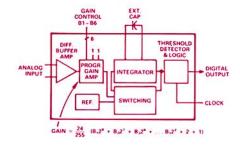

## SMALL, FAST, LOW-COST, HIGH-RESOLUTION INTEGRATING ADC

18-Bit  $\mu$ P-Based AD1170: Low Nonlinearity,10-ppm Integral/4-ppm Differential Automatic Calibration, No Trims, Programmable Resolution and Integrate Time

by Bill Sheppard

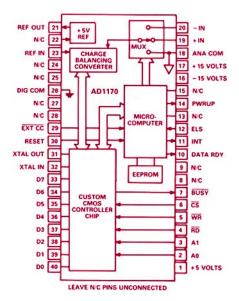

The AD1170\* is a microprocessor-compatible and programmable high-resolution (to18 bits) integrating a/d converter. Its small  $(1.24" \times 2.5" \times 0.55"$  max) modular package contains a complete microcomputer-based measurement subsystem comprising a high-linearity charge-balancing (V/F) converter, a single-chip microcomputer, and a custom CMOS controller chip (Figure 1). It requires  $\pm 15$ V and  $\pm 5$ -volt power supplies, and an external 12-MHz crystal or system clock; no trim potentiometers, external references, or timing capacitors. Price in 100s is \$98.

It periodically calibrates itself by reading a zero-input signal and a full-scale signal provided by an internal reference; using this data to compensate the converted data produces gain stability comparable to that of the reference—and negligible offset drift. Integral linearity error, which depends on the linearity of the charge-balancing converter, is a low  $\pm 0.001\%$  at all resolutions.

Both resolution (7 to 22 bits) and speed (integrating time from 1 ms to 350 ms) are programmable. However, differential non-linearity—which limits the effective resolution—is introduced by the uncertainty due to noise; hence there is a tradeoff between resolution and speed. The longer the integration time, the lower the uncertainty and the better the resolution; but also the lower the throughput. Here are some examples of effective resolution and throughput that can be achieved with the AD1170:

| INTEGRATION       | RESOLUTION     | THROUGHPUT      | LINEARITY ERROR |              |

|-------------------|----------------|-----------------|-----------------|--------------|

| TIME              |                | RATE            | INTEGRAL        | DIFFERENTIAL |

| (programmable)    | (programmable) | (conversions/s) | (% c            | (span)       |

| 1 ms              | 12 bits        | 250             | ± 0.001%        | ± 0.01%      |

| 16.667 ms (60 Hz) | 16 bits        | 50              | ±0.001%         | ±0.008%      |

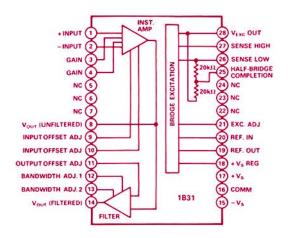

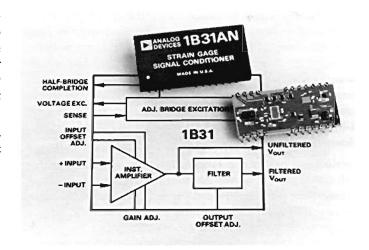

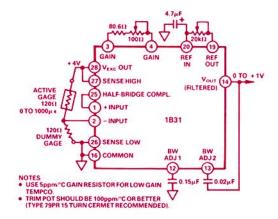

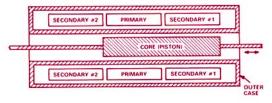

| 300 ms            | 18 bits        | 3               | ±0.001%         | ±0.00035%    |