#### Editor's Notes PRODUCTIVITY & LEARNING

"There is no limit to learning, there is only what we settle for."

With these words, President and Chairman Ray Stata concluded his 1984 address to Analog Devices shareholders. The gist of his message was that: the organization learning curve is a universal means of measuring learning perform-

ance (and thus productivity) among organizations of all sizes, from product lines to national economies; its slope is a measure of competitiveness, and increasing the slope by improving organizational learning is not only possible but should be a major objective of progressive organizations. The objective of Analog Devices is to evolve from its present flatness to 7.5% to 12.5% annual growth in real productivity for 25% growth in real sales.

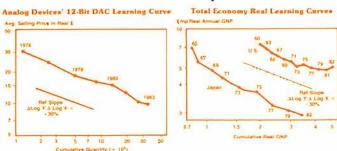

The product-cost learning curve, developed through empirical observations by the Boston Consulting Group, has shown that real value-added costs—for a wide range of products—decline by 20% to 30% every time cumulative product volume doubles. Plotted on a log-log scale, this function approximates a straight line with a slope of about -0.2 to -0.3. The left- hand figure shows the learning curve for 12-bit d/a converters at ADI, with selling price (real dollars) used as a proxy for value added.

At ADI, we have extended this concept to embrace organizational learning. The "output" of the organization is the value added to the costs of things bought, transformed, and sold to customers. The "cost" of the organization is the human effort to produce the value-added, viz., "cost in employee-years per \$million of valueadded." Since employment grows, negative slope of the "organizational learning curve" means that value-added grows even faster. The counterpart of the decline in the cost curve is an increase in its reciprocal, productivity, i.e., "\$million of value added per employee-year"; a falling learning curve implies increasing productivity, and we are more concerned with the rate of increase than the actual datum at any time. As the organization learns, value-added increases with cumulative value-added experience.

Applying the concept to total economies, the right-hand figure compares organizational learning curves for Japan and the U.S.A., measured by (employment)/(real annual GNP) vs. cumulative real GNP - with GNP as a proxy for value added. It is evident that the learning curve for Japan's economy is both steeper and more consistent than that of the U.S., which currently shows a "bottoming" tendency (productivity "topping-out.")

Use the reply card to request a copy of the complete message, containing many charts and equations (by ADI Vice President A. Graham Sterling) and presenting economic information in a light that is both unusual and eye-opening.

Improving the slope of the learning curve, using a measure of value added meaningful to the organization, is a worthwhile objective that will improve the ability of a growth-oriented organization to compete and produce real benefits for its employees. ADI believes that this can be done and is committed to it for the future.

The elements of ADI's program to increase organizational learning are: Vision (top management must not impede employee self-motivation); Participation (in the ideal case, each worker should be his or her own manager); Alignment (every employee should understand the purpose of his or her job in terms of the final results to be achieved); Quality improvement (the causes of defects and process variations should be understood and eliminated—"do it right the first time"); Long tenure (knowledge is carried in people's heads, turnover is detrimental to organizational learning); Assimilation and training (education and training programs for employees must be effective); and Investments in capital and technology (ability of workers to produce must be enhanced by the availability of up-to-date tools). Dan Sheingold

#### THE AUTHORS

John Gasking (page 22) is the Marketing Manager of ADI's Memory Devices Division, Surrey, England. He received the HNC (Higher National Certificate) in Applied Physics and M. Phil. in Electrical Engineering at the Polytechnic of Central London; his thesis was on electronic bloodflow measurement, while working

as a Research Assistant at St. Bartholomew's Hospital. Early in his career, he worked with large analog computers, as a Design Engineer, at Vickers Armstrong Aircraft Company; he joined Analog Devices 10 years ago as a Sales Engineer.

Doug Grant (page 7) is New Product Marketing Manager for Analog Devices Semiconductor. A more-complete biographical sketch and a photograph appear in Analog Dialogue 18-1, page 2.

Walter Jung (page 16) is a freelance electronics experimenter and a prolific writer, living in Forest Hill, Maryland. His published works include eight books on IC applications, including the IC Op-Amp Cookbook, the IC Timer Cookbook, and the IC Converter Cookbook, all published by Howard Sams, Inc. Walt is a member of

the IEEE and a Fellow of the Audio Engineering Society. His leisure interests include music, audio, and amplifiers.

(Continued on page 26)

2 Technology Way, P.O. Box 280, Norwood, Mass. 02062

Published by Analog Devices, Inc., and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and display circuits and systems. Correspondence is welcome and should be addressed to Editor, Analog Dialogue, P.O. Box 280, Norwood, Massachusetts, U.S.A. 02062. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577 or 710-336-0562, Telex 924 491, or cable ANALOG NORWOODMASS.

© Analog Devices, Inc. 1984

2

### ADSP-1110: SINGLE-PORT 16 X 16 MULTIPLIER-ACCUMULATOR

Save Hardware Costs and Real Estate in Digital Signal Processing 28-Pin DIP with Unusual Arithmetic Capabilities for Compact DSP Designs

by John Oxaal

Although prices of integrated circuits for digital signal processing (particularly digital multipliers) have been coming down, high price and large circuit-board footprint have tended to restrict their use to applications where performance is required without regard to the costs. The introduction of CMOS for DSP components by Analog Devices and others has brought a welcome reduction of dissipation, but there are still problems. A standard three-port  $16 \times 16$ -bit multiplier-accumulator (MAC), for example, costs well over one hundred dollars; and the 64-pin package required for connecting to its three 16-bit data ports (two inputs and one output), plus power and controls, consumes considerable real estate. In addition, conventional 16-bit MACs suffer from restricted arithmetic capability, making them cumbersome to use.

The new ADSP-1110\* eliminates these problems of three-port MACs. All data is handled via a single 16-bit bus, in response to a sophisticated 6-bit instruction set. The single-port structure allows it to fit into a 28-pin DIP, which makes DSP substantially more cost-effective with little sacrifice of throughput. The smaller package costs less to manufacture and reduces board-space requirements by nearly a factor of four, compared to 64-pin packages. Its cost is less than half that of conventional 16-bit MACs, \$75 in 100s.

#### ABOUT MULTIPLIER/ACCUMULATORS

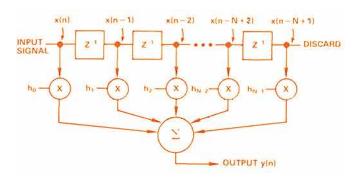

Digital multiplier/accumulators (MACs) play a fundamental role in what has come to be known as digital signal processing. The core DSP tasks—filtering, spectral estimation via fast Fourier transforms (FFT), correlation, and matrix multiplication are characterized by chains of multiplications, the results of which are accumulated. A good example is the well-known FIR (finite impulse-response, or non-recursive) filter equation (Figure 1, see also page 8):

$$y(n) = \sum_{m=0}^{N-1} h(m) \cdot x(n-m)$$

(1)

Each output point, y(n), is obtained by accumulating the results of N multiplications between coefficients, h(m), and data, x(n-m). Three-port MACs have been employed for years to per-

Figure 1. Finite impulse-response filter architecture.

form these functions. But, as mentioned, three-port MACs are expensive, make inefficient use of board space and require external logic chips to make up for their arithmetic deficiencies.

### IN THIS ISSUE

| Volume 18, Number 2, 1984 – 28 Pages                                    |

|-------------------------------------------------------------------------|

| Editor's Notes, Authors (more authors on page 26)                       |

| Single-Port Multiplier-Accumulator Saves Hardware and Real Estate       |

| (ADSP-1110)                                                             |

| The Compleat General-Purpose 12-Bit D/A Converter (AD667) 7             |

| Speed Up FIR Filters                                                    |

| Flash Converters Work Better with Track/Holds                           |

| First 12-Bit, 1-MHz Hybrid A/D Converter with Track/Hold (HAS-1201). 15 |

| Generate Precision Square and Triangular Waves with AD630 Balanced      |

| Modulator/Demodulator                                                   |

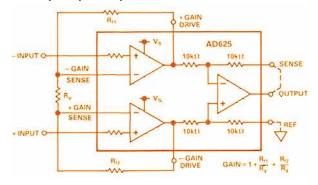

| Flexible Monolithic Instrumentation Amplifier (AD625)                   |

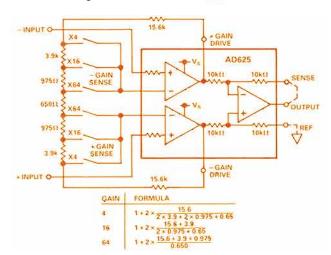

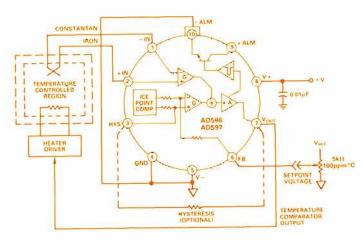

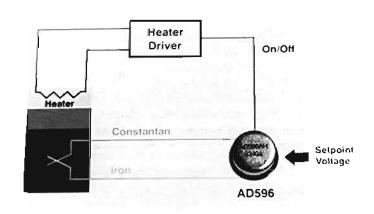

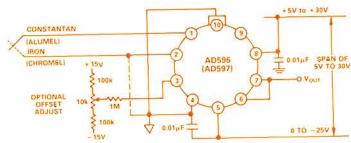

| Thermocouple-Based Setpoint Controllers (AD596 and AD597) 20            |

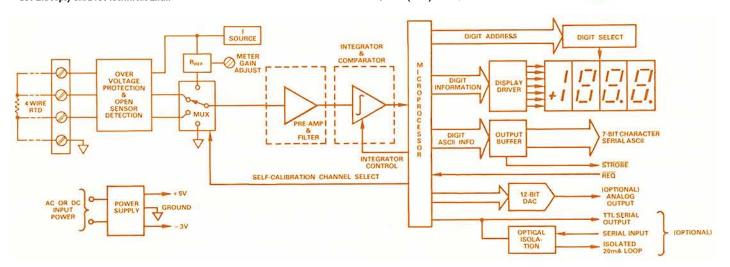

| Autoranging Microprocessor-Based RTD/Thermistor Meters (AD2060/61). 21  |

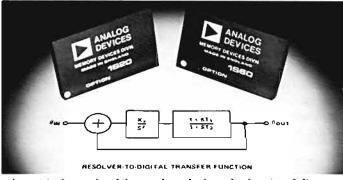

| New Hybrid Resolver-to-Digital Converter Family (1S20/40/60/61) 22      |

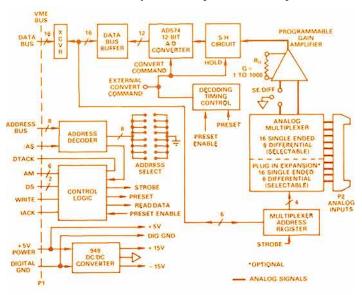

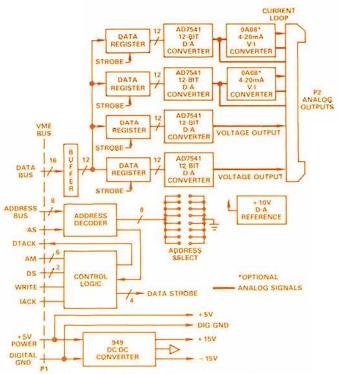

| Low-Cost 12-Bit Analog Interface Boards for VMEbus (RTI-600) 23         |

| New-Product Briefs:                                                     |

| 16-Bit Hybrid A/D Converter (AD ADC71/72)                               |

| 8×8 Monolithic CMOS Multiplier with Unsigned Format (ADSP-1081) . 24    |

| Low-Cost Precision FET Op Amp (AD611)                                   |

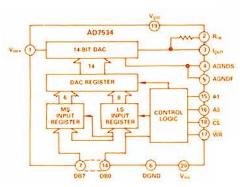

| Double-Buffered 14-Bit CMOS Multiplying DAC (AD7534) 25                 |

| Analog Devices "Eye" Intelligent Vision System (IVS-100) 25             |

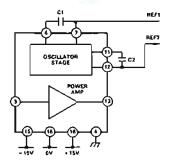

| Power Oscillator for Resolvers (OSC1758)                                |

| Worth Reading - New Publications from Analog Devices, ADI in            |

| Trade Press                                                             |

| Porpourri                                                               |

| Advertisement                                                           |

<sup>\*</sup>Use the reply card for technical data.

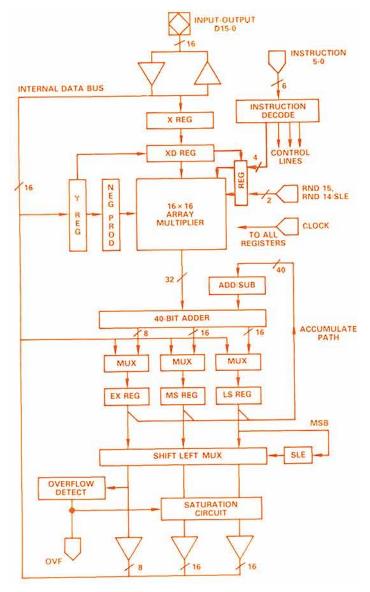

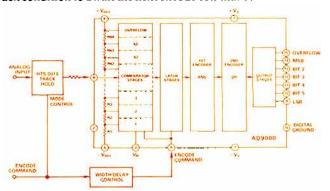

Figure 2. Block diagram of the ADSP-1110.

Figure 2 shows the architecture of the ADSP-1110. The single 16-bit I/O port handles the 16-bit X and Y inputs, 16-bit more-significant product (MSP), 16-bit less-significant product (LSP), and the 8-bit extension—which allows up to 256 full-scale products to be summed without danger of losing information.

The time required to perform the multiply-accumulate operation is 200 ns (over the entire -55°C to +125°C ambient temperature range), and 100 nanoseconds is required for 1/O. In two 100-nanosecond cycles, the device can load new X and Y inputs, while concurrently performing a multiply/accumulate on previous input data. For DSP calculations, which typically require only infrequent outputs, this scheme results in an average time of only slightly more than 200 ns per operation. Furthermore, as will be discussed, many on-board "hooks" save both external hardware and 1/O cycles.

To understand why throughput is not sacrificed in DSP applications, consider the case of a 90-tap FIR filter. As illustrated in equation 1, each output sample would require 90 separate multiply/accumulate operations. A typical three-port CMOS MAC, such as the ADSP-1010, features a multiply time of 200ns over temperature, so a 90-tap FIR filter calculation requires (90)-(200ns), or 18µs per output sample. The ADSP-1110 single-port MAC, in the same application, requires 100ns to load the first x value, (90)-(200ns) for the multiply-accumulates (multiplication occurs simultaneously with the y input), and 100ns to output the 16 most-significant-product bits. The total time to output the result is thus 18.2µs, only 1% slower than a three-port device.

Other interesting benchmark operations that will be discussed in the applications section are:  $1.1\mu s$  per IIR biquad (infinite impulse-response—or recursive—filter section); 10ms per complete 1024-point complex FFT; and,  $4\mu s$  for multiplying a  $4\times 4$  matrix by a  $4\times 1$  matrix.

While offering all the arithmetic functions of the three-port device, the single-port MAC boasts several unique (among MACs) features that simplify numerical calculations. These include:

- A 40-bit accumulator with overflow detection and overflow flag. This feature is especially useful for many-tap FIR filters.

- The option of conditional (on the overflow flag) saturation on output, i.e., permitting the output to saturate instead of rolling over on a carry. Saturation on overflow minimizes the deleterious effects of wraparound (e.g., when trying to go from +FS to +FS + 1, the output actually goes from +FS to -FS in twos-complement arithmetic). Among the problems associated with it, wraparound can cause full-scale oscillations in an IIR filter.

- Shift left on output allows the redundant sign bit to be removed and a digit of precision to be gained in twos-complement multiply-accumulate operations.

- Independent controls for rounding in either the 14th or 15th product bit allow rounding consistent with either a shifted or unshifted output. The combination of shift left and rounding on the 14th bit allows one to obtain a properly rounded 15-bit plus sign twos-complement output.

- The ADSP-1110 provides negative product logic, which allows the designer to obtain  $\pm$  product  $\pm$  accumulator. This feature is quite useful to obtain multiplication by +1, i.e.,  $(-1)\cdot(-\text{product})$ , which can't be done in twos complement with standard MACs.

- A single-bit shift-left-extend register increases the precision obtainable in double precision operations.

- The ability to transfer the MS (more-significant) register to the LS (less significant) register and the EX (extension) register to the MS register is useful for table look-up operations and rotate and merge functions.

While not all these features will be useful for every application, they will in general (as shown in the following applications section) reduce the external logic elements and attendant power and board-space costs associated with the standard three-port designs.

#### **APPLICATIONS**

The following examples describe applications of the single-port MAC in traditional DSP benchmark calculations. They will show that the ADSP-1110 provides, on a single chip in a 28-pin package, the characteristics needed in an arithmetic processor—without significant performance penalties. We will first describe IIR filters, then FFTs and matrix multiplications.

#### IIR Filter

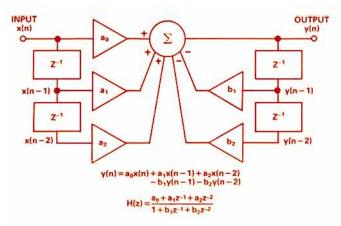

Recall that, in the equation for a biquad section of an IIR filter, for the 0th (i.e., present) point,

$$y(0) = a_0x(0) + a_1x(-1) + a_2x(-2) - b_1y(-1) - b_2y(-2)$$

(2)

where y(0) and x(0) are the present output and input, y(-1) and x(-1) are the last values of y and x, and y(-2) and x(-2) are the next previous values, as shown in the block diagram of Figure 3.

While most of the coefficients can be scaled to be equal to or less than unity,  $b_1$  often ranges in value from 1 to 2. The most convenient way to represent the coefficients and data is in fractional twos-complement notation. Since this numbering system only ranges from -1 to +0.999..., all the coefficients and data for the IIR filter have to be divided by 2, in order to handle the larger values of  $b_1$  when using a conventional MAC. Then, at the output, external shifters are needed to shift the result up 1 bit (or re-multiply by 2).

Figure 3. Infinite impulse-response filter biquad section.

With the single-port MAC, however, a coefficient in the +2 to -2 range is available by means of a mixed-mode multiplication (unavailable with standard MACs) which has an output with twice the magnitude of a twos-complement multiply. A multiply-and-add—or a multiply-and-subtract—provides the correct choice of sign as the product enters the accumulator, an option unavailable with other MACs; the result is multiplication by a constant from -2 to +1.99...

A problem with IIR filters (as with any system that has feedback) is that, because of "wraparound" in twos-complement arithmetic, certain combinations of data and coefficients (even though the filter is theoretically stable) can induce full scale oscillations in the filter. The hard limiting provided by the ADSP-1110's saturation arithmetic prevents oscillations due to overflow.

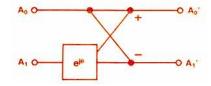

#### Simplifies FFT Butterflies

Single-port MACs are of great use in implementing "butterflies"—the key arithmetic operation in computing fast Fourier transforms. The FFT is a powerful algorithm used to greatly reduce the number of complex multiplications in performing a digital Fourier transform (i.e., from N<sup>2</sup> to (N/2) log<sub>2</sub> (N)—for example, from more than one million (1,024<sup>2</sup>) to 5,120, for a 1024-point transform—a factor-of-200 reduction.

Figure 4. Fast-Fourier-transform "butterfly".

The characteristic flow diagram of a basic FFT computational unit, or "butterfly," is shown in Figure 4, for a decimation-in-time computation. In the general case, all variables and coefficients are complex, leading to a typical pair of equations of the form,

$$\begin{aligned} A_0' &= A_0 + A_1 \varepsilon^{j\theta} \\ A_1' &= A_0 - A_1 \varepsilon^{j\theta} \end{aligned} \tag{3}$$

the complex number  $A_1$ , multiplied by a rotation,  $R = e^{i\theta}$ , is added to the complex number,  $A_0$ , to produce  $A_0'$ , and subtracted from  $A_0$ , to produce  $A_1'$ . By properly sequencing the butterflies, you obtain an FFT. A 1024 point FFT, for example, contains about 5000 butterflies. The rotation, R, can be written

$$e^{i\theta} = \cos\theta + i\sin\theta$$

= C + iS (4)

If Ao and A1 are complex numbers,

$$A_0 = X_0 + j Y_0$$

$A_1 = X_1 + j Y_1$  (5)

then,

$$A_1 e^{j\theta} = [X_1 + jY_1] [C + jS]$$

$$= [X_1 C - Y_1 S] + j[X_1 S + Y_1 C]$$

(6)

The outputs, Ao' and A1', are also complex, i.e.,

$$A_0' = X_0' + jY_0' A_1' = X_1' + jY_1'$$

(7)

From (3) and (6), their real and imaginary parts are computed as follows:

$$X_{0}' = X_{0} + (X_{1}C - Y_{1}S)$$

$$Y_{0}' = Y_{0} + (X_{1}S + Y_{1}C)$$

$$X_{1}' = X_{0} - (X_{1}C - Y_{1}S)$$

$$Y_{1}' = Y_{0} - (X_{1}S + Y_{1}C)$$

(8)

To complete the butterfly, a number of multiplications, additions and subtractions must be performed.

When using a single-port MAC to perform butterflies, begin by placing  $X_0$  into the accumulator; simply multiply by positive full scale, or 0111111111111111111. Compute  $X_0$ '

$$X_0' = KX_0 + X_1C - Y_1S (9)$$

$$X_1' = 2 K X_0 - X_0' \tag{10}$$

where  $X_0'$  is the accumulator's contents, and 2 K  $X_0$  results from a mixed-mode multiplication of 2K and  $X_0$ . This operation represents a multiply-and-subtraction which (unlike other available MACs) the single-port MAC readily handles. The imaginary terms,  $Y_0'$  and  $Y_1'$  are computed in the same way.

Table 1 provides the details of the process for computing an FFT butterfly with a single-port MAC. For each point, ten cycles are required to compute the real component, plus ten more cycles for the imaginary part. At 100ns per cycle, the total time required is 2.0 microseconds. A 1,024-point FFT, requiring about 5000 butterflies, takes 10 milliseconds.

An FFT calculation contains a series of multiply/accumulates and multiply/subtracts. This presents a challenge in rounding the result, because rounded inputs from earlier cycles become inputs for later cycles. The rounding on cycles 4, 6, 14, and 16 ensures that the outputs (on lines 7, 10, 17 and 20) are rounded correctly.

Lines 4 and 14 round on bit 14 to prepare for a left-shift during

Table 1. Computing Sequence for Single-Port MAC Butterfly

| Cycle# | Operations                                | Acc Reg Contents                                                              |

|--------|-------------------------------------------|-------------------------------------------------------------------------------|

| •      | •                                         | The red comme                                                                 |

| 18'    | LoadK                                     |                                                                               |

| 19'    | Load X <sub>0</sub> & Mult                | Previous<br>KY <sub>0</sub> – X <sub>1</sub> S + Y <sub>1</sub> C)<br>+ RND14 |

| 20'    | Output MS Reg left-shifted (previous Y1') |                                                                               |

| 1      | Load C                                    |                                                                               |

| 2<br>3 | Load X <sub>1</sub> & MAC                 | $KX_0$                                                                        |

| 3      | Load S                                    |                                                                               |

| 4      | Load y 1 & Neg Mult                       |                                                                               |

|        | & ACC+RND14                               | $K_0X_0 + X_1C$                                                               |

| 5      | Load 2K                                   |                                                                               |

| 6      | Load X <sub>0</sub> & Mult & Neg          |                                                                               |

|        | ACC+RND15                                 | $K_0X + (X_1C - Y_1S)$<br>+ RND14                                             |

| 7      | Output MS Reg (X1') left-shifted          |                                                                               |

| 8      | Load K                                    |                                                                               |

| 9      | Load Yo & Mult                            | $K_0X - (X_1C - Y_1S)$<br>+ RND14                                             |

| 10     | Output MS Reg (Xo')                       |                                                                               |

| 11     | LoadS                                     |                                                                               |

| 12     | Load X <sub>1</sub> & MAC                 | KY <sub>0</sub>                                                               |

| 13     | Load C                                    | •                                                                             |

| 14     | Load Y <sub>1</sub> & MAC + RND14         | $KY_0 + X_1S$                                                                 |

| 15     | Load 2K                                   |                                                                               |

| 16     | Load Yo & Mult & Neg Acc                  |                                                                               |

|        | + RND15                                   | $KY_0 + (X_1S + Y_1C) + RND14$                                                |

| 17     | Output MS Reg (Y1') left-shifted          |                                                                               |

| 18     | Load K                                    |                                                                               |

| 19     | Load X <sub>0</sub> (new) & Mult          | $KY_0 - (X_1S + Y_1C) + RND14$                                                |

| 20     | Output MS Reg (Y0') left-shifted          |                                                                               |

output. However, lines 6 and 16 round on bit 15. This is necessary because, in performing the multiply and subtract on these lines, the original round on lines 4 and 14 becomes inverted—it becomes a subtraction of one, rather than an addition of one. For compensation, 2 must be added to the 14th bit: 1 to compensate for the previous round, and then 1 to round the current result. This can be easily accomplished in one step by adding a 1 to bit 15 rather than to bit 14. Thus, the result in MS continues to maintain the correct rounded result after further accumulations.

To prevent overflow during FFT calculations, the overflow flag can be used. The overflow flag is set when a bit in the EX register differs from the sign bit in the MS register. The combination of the overflow flag and the MAC's saturation arithmetic ameliorates the disastrous consequences of overflow in the FFT calculation.

#### Use Single-Port MAC To Upgrade Graphics Systems

Matrix multiplications are used in numerous applications; examples include modern motion controllers and graphics systems. In a bit-mapped graphics system, matrix multiplications are used to implement a variety of image manipulations such as translation, rotation, and zoom. The ADSP-1110 Single-Port MAC makes an ideal accelerator for speeding up the performance of matrix multiplications for a microprocessor-based graphics system.

Here's an example: Points on an object are rotated abut the Z-coordinate axis to new positions by setting the new x,y coordinates  $-X',Y'-to: X'=x \cos\theta+y \sin\theta$  and  $Y'=-x \sin\theta+y \cos\theta$ . For the homogenous three-dimensional transformation

$$P(x,y,z) \longrightarrow P(X',Y',Z')$$

where P(x,y,z) is the original point, whose coordinates are x,y, and z, and P(X',Y',Z') is the transformed point, the following matrix is computed.

$$[X,Y,Z,1] \begin{bmatrix} \cos\theta & -\sin\theta & 0 & 0\\ \sin\theta & \cos\theta & 0 & 0\\ 0 & 0 & 1 & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

The transformed point is equal to the row, [x, y, z, 1], multiplied by the transformation matrix, and:

$$X',Y',Z' = [x\cos\theta + y\sin\theta, -x\sin\theta + y\cos\theta, z]$$

In general, a translation matrix, a scaling matrix, and a rotation matrix are concatenated to yield an overall transformation matrix, (for which some—or most—of the zero elements above would become non-zero). In any case, the ADSP-1110 can multiply a  $4\times4$  matrix and  $4\times1$  vector (requiring 16 MACs) in less than  $4\mu$ s.

#### Conclusion

We have shown here that the single-port MAC has the hooks necessary to perform the varied tasks of the number-crunching section of a DSP system with reasonable performance. Filtering, FFT's, matrices for graphics, and other operations are all done at a fast clip on a single chip. The savings in parts count, parts cost, board space and power dissipation—with acceptable speed for many cases—make the ADSP-1110 an ideal choice as an arithmetic processor in compact systems.

#### **Interpreting Digital Multiplication Results**

When performing digital multiplications with devices such as the single-port MAC, the results you get will depend on whether the inputs, X and Y, are unsigned or signed (twos-complement) numbers.

There are four possible input combinations:

|    | X               | Y               |

|----|-----------------|-----------------|

| 1. | Unsigned        | Unsigned        |

| 2. | Unsigned        | Twos complement |

| 3. | Twos complement | Unsigned        |

| 4. | Twos complement | Twos complement |

The figure below illustrates the results of the multiplication for each of the above four cases. Note how the two most-significant bits of the MS register differ, depending on the case. The results of cases 2 and 3 have only a single sign bit. As a result of twos-complement arithmetic, on the other hand, case 4 has two sign bits, and the "decimal" point is shifted down by one position. However, this is not a problem; because the single-port MAC has left-shift capability at its output, the result of case 4 can be reformatted to have only 1 sign bit and 30 magnitude bits.

The left-shift capability can also serve to upscale both signed and mixed-mode numbers.

|                                      | BIT 31                | 8IT BIT           | BI |

|--------------------------------------|-----------------------|-------------------|----|

| 1. X <sub>US</sub> , Y <sub>UN</sub> | MS                    |                   |    |

| 2. X <sub>U</sub> , Y <sub>TC</sub>  | S MS                  | s   L             | s  |

|                                      | ♦ DEC PT              |                   |    |

| 3. X <sub>TC</sub> , Yus             | Is Ms                 | s L               | S  |

|                                      | DEC PT                |                   |    |

| 4. X <sub>1C</sub> , Y <sub>TC</sub> | ISIS N                | vis L:            | S  |

|                                      | DEC                   | PT                |    |

| *THIS IS A SIGN                      | BIT IF NEGATIVE PRODU | CT LOGIC IS USED. |    |

### THE COMPLEAT GENERAL-PURPOSE 12-BIT D/A CONVERTER

Monolithic AD667 Has Voltage Output, Linearity to ½-LSB over Temperature Internal Reference, 3-μs max Settling, Double-Buffered μP-Compatible Input

by Doug Grant and Steve Lewis

The evolution of high-linearity 12-bit digital-to-analog converters in integrated-circuit form has constituted a long, arduous climb. Significant landmarks on the bipolar-technology route were the AD550 quad switches (1970), the AD562 two-chip current-output DAC (1974), the AD565 internal-reference monolithic DAC (1978), the AD567 double-buffered current-output DAC (1982), and —now—the summit has been reached, in the form of the AD667\*, a completely self-contained monolithic device which does not require a single support component to perform its function.

#### UNIVERSAL MONOLITHIC DAC

The AD667 (Figure 1) complete, voltage-output d/a converter has its own on-chip high-stability buried-Zener voltage reference, double-buffered digital latches that are compatible with 4-, 8-, 12-, and 16-bit data buses, and a fast output amplifier with five user-configurable output ranges. It will operate at voltages from  $\pm 11.4$  to 16.5 V dc and typically dissipates less than 300 mW when operated from  $\pm 12$ -volt supplies.

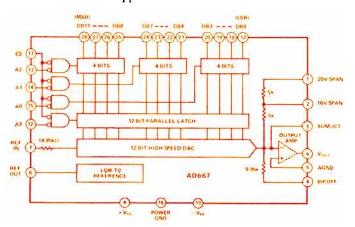

Figure 1. AD667 block diagram.

Its completeness, versatility, speed, accuracy, choice of packaging options, and low price make it a first choice for any application calling for a fixed-reference "no-problem" bus-compatible 12-bit d/a converter.

Versatility: The AD667's positive-true digital data inputs are compatible with both TTL and 5-volt CMOS logic. Divided into 3 4-bit quads, they accept input data in a sequence of 4-bit nybbles from 4-bit buses, 8 + 4 or 4 + 8-bit bytes (left- or right-justified – see Figure 2) from 8-bit buses, and 12 bits in parallel from 12-or 16-bit buses. The inputs are double-buffered—this means that the converter may be updated when all 12 bits have been loaded, avoiding spurious analog output values. The control signals may be arranged for automatic updating when the full 12-bit word has been loaded. In addition, a group of DACs may be updated simultaneously or in any desired sequence after having been loaded asynchronously by any of the above schemes. Since the latches are level-triggered, they may be hard-wired in a transparent mode.

\*Use the reply card for technical data.

The AD667's 10-volt ( $\pm 1\%$ ) reference, which is externally jumpered to the device input, with typically 1 mA to spare, may also serve other devices or as a system reference. The AD667's output voltage may be pin-programmed for bipolar outputs of  $\pm 2.5$  V,  $\pm 5$  V, or  $\pm 10$  V, and unipolar outputs of + 5 V or + 10 V, at up to 5 milliamperes. The AD667's connection scheme permits a current booster to be connected inside the output op-amp's loop for high-current applications (e.g., line driving).

Speed: The use of precision high-speed bipolar current-steering switches and an on-chip high-speed output amplifier results in a 10 V/ $\mu$ s slew rate and settling time of 3  $\mu$ s maximum to within  $\pm \frac{1}{2}$  LSB for a 10-volt output change; for 1-bit changes, typical settling time is 1  $\mu$ s. The digital latch responds to strobe pulses as short as 100 nanoseconds, allowing the device to be used with fast microprocessors.

Accuracy: All versions of the AD667 have guaranteed monotonic behavior over the specified temperature range. The AD667K and AD667B guarantee maximum linearity error of  $\pm \frac{1}{4}$  LSB at  $\pm 25^{\circ}$ C and maximum differential and integral linearity errors of  $\pm \frac{1}{4}$  LSB over temperature. Initial gain error is 0.2% of full scale (max) and offset is 2 LSB (max), while maximum temperature coefficients are  $\pm 15$  ppm of full-scale range per °C for gain,  $\pm 3$  ppm/°C for offset, and  $\pm 10$  ppm/°C for bipolar offset.

Packaging Options: The AD667 is offered in five grades, J/K for 0°C to +70°C, A/B for −25°C to +85°C, and \$ for −55°C to +125°C. J/K versions are provided in 28-pin proven plastic DIPs, and the other grades are available in a choice of hermetically sealed ceramic DIPs or 28-terminal ceramic leadless chip-carriers (LCCs). Prices, the lowest in the industry, start at \$9.90 in 1000s (\$11.95 in 100s) for the AD667JN.

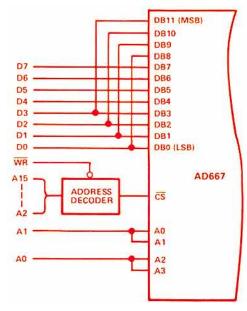

Figure 2. Connections for right-justified 8-bit bus interface.

### SPEEDING UP FIR FILTERS (MAKING THE FIR FLY)

### When Coefficients Exist in Symmetric or Antisymmetric Pairs Symmetry Can Be Used to Speed up Computation by Factors of 2

by Per E. Pedersen and Bill Windsor

Editor's Note: In Analog Dialogue 17-2 (1983), we published an article<sup>1</sup> discussing a simplified design method for digital finite impulse-response (FIR, or non-recursive) filters. In response to the article, and to our invitation to readers to join in the Dialogue, Per E. Pedersen, of Hellerup, Denmark, sent us a note suggesting a way of speeding up implementation of the design discussed in the article. In these pages, the earlier article is recapitulated and Mr. Pedersen's valuable suggestion is explained.

#### FIR FILTER-DESIGN BASICS

Both analog and digital filters pass signals in a specified frequency range and attenuate signals outside that range. But digital filters operate on discrete data—that is, sampled data in digital form, obtained either from stored data of any kind retrieved in the form of a time series or from conversions of electrical signals to digital by an a/d converter.

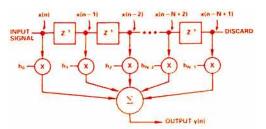

Figure 1. Block diagram of direct-form FIR filter (N-tap filter).

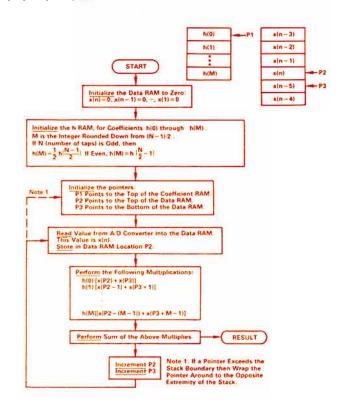

The digital filter can operate on the data in the time domain by performing numerical calculations to implement the filter's equation. As Figure 1 shows, the output of an FIR filter is the sum of a series of multiplications of filter coefficients, h(m), and the corresponding sampled input-data points, x(n-m). If the filter has N coefficients, or taps, N multiplications will be required on the N most-recent signal samples. The coefficients, which constitute the indicial time response, or the discrete Fourier transform of the desired frequency response, are usually generated by a computer program<sup>2</sup>. The equation for an FIR filter output at the nth sample point (instant of discrete time) is:

$$y(n) = h(0)\cdot x(n) + h(1)\cdot x(n-1) + ... + h(N-1)\cdot x(n-N+1)$$

$$y(n) = \sum_{m=0}^{N-1} h(m) \cdot x(n-m)$$

(1)

For example, if the filter has 27 taps and we are computing the value of y(100), the first term of the sum will be h(0)-x(100) and the last term will be h(26)-x(74). This series of multiplications and additions performs the convolution of the input signal with the filter coefficients. The output values are available for storage, further processing, or conversion to analog with a d/a converter.

In the direct form of Figure 1, there are N multipliers, and each data point can be computed as rapidly as data can be shifted, the multiplications performed in parallel, and the sum taken in real time. Generally, such rapid computation (and high expense) is not warranted; a single multiplier will still compute each point several orders of magnitude faster than multiplication in software.

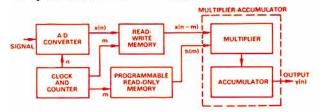

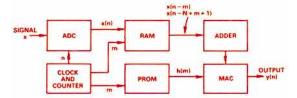

In one implementation (Figure 2), the input signal is sampled using the a/d converter, and the discrete data are stored in the RAM. The coefficients are stored in PROM. The counter addresses values of coefficients and corresponding input data, and feeds these values to the multiplier. The pointers step sequentially through memory to access the coefficients and data. The multiplier computes the products, which update the sum in the accumulator. After all multiplications have been performed, the output value for the point then computed is read from the accumulator.

Figure 2. FIR filter employing a hardware multiplier.

#### Linear Phase and Symmetric Coefficients

Besides being simpler in concept and easier to design than digital filters in other forms, FIR filters can be made to have a linear phase response, resulting in a constant time delay for all frequency components. Besides being useful in many applications requiring preservation of waveshapes, linear phase response is accompanied by symmetric coefficients. Symmetric coefficients have mirror symmetry about the ordinate at the midpoint of the range of N coefficients; corresponding antisymmetric coefficients have odd-value symmetry (equal magnitudes but opposite polarity).

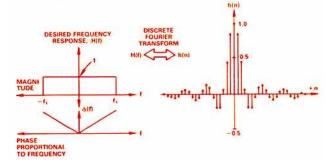

The set of coefficients h(n) is determined from the desired frequency characteristic of the filter; for example, for an ideal low-pass filter (Figure 3), with rectangular magnitude transfer function, H(f), and linear phase, the inverse Fourier transform, h(n), will be of the form,  $\sin x/x$ , comprising real coefficients having mirror symmetry about the central term. Although the  $\sin x/x$  function

Figure 3. Filter coefficients, h(n), derived from the frequency response, H(f).

<sup>1&</sup>quot;Digital FIR Filters Without Tears," by Bill Windsor and Paul Toldalagi, Analog Dialogue 17-2 (1983), pp. 12-19.

<sup>&</sup>lt;sup>2</sup>A FORTRAN program to generate FIR filter coefficients is available free of charge. Write to Analog Devices, DSP Marketing, One Technology Way, Norwood MA 02062. Request the "Remez Exchange Application Note."

has are infinite number of terms, the filter as designed will have a finite number of terms, N, arbitrarily truncated via a windowing function, but still symmetrical.

Although h is time-shifted, to establish its leftmost element as h(0), at m=0, such a time shift is simply equivalent to a linearly increasing phase shift in the frequency domain, leading to a fixed delay in the response.

#### Design Improvement

Symmetrical coefficients lead to a substantial improvement in design of a digital filter, because

$$h(0) = h(N-1), h(1) = h(N-2), \text{ etc.}$$

(4)

Since addition is distributive, we can take pairs of terms of (1), starting with the outermost terms, and compute them by adding the x's in pairs and multiplying them by the common factor—thus saving one multiplication per pair of terms. This is done by inserting an adder ahead of the multiplier/accumulator (MAC), shifting about half of the computational burden to the adder.

$$y(n) = h(0)[x(n) + x(n - N + 1)] + h(1)[x(n - 1) + x(n - N + 2)] + ... + final term$$

(5)

For an even number of coefficients, the final term is the (N/2)th term, equal to (since the first term is h(0)):

$$h(N/2-1)\{x(n-N/2+1)+x(n-N/2)\}$$

(6)

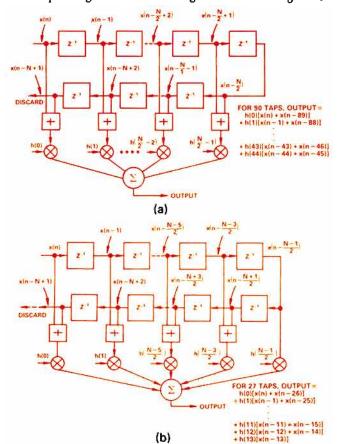

The block diagram is shown in Figure 4a. If there are an odd number of coefficients, the final term is the ((N+1)/2)th term, equal to

$$h((N-1)/2))[x(n-(N-1)/2)]$$

(7)

The corresponding FIR filter block diagram is shown in Figure 4b.

Figure 4. FIR filter block diagrams for symmetric coefficients. (a) Even number of taps. (b) Odd number of taps.

Figure 5. Hardware architecture of the filter.

If the filter coefficients are anti-symmetric, the pairs of magnitudes of x are subtracted instead of being added. A hardware configuration to implement this add-then-multiply scheme is shown in Figure 5. Figure 6 outlines the pointer scheme, similar to Figure 9 of Reference 1, to implement the add-then-multiply FIR filter.

The speed increase for the FIR calculation is significant. In a benchmark test, using a PDP11/03 system and software multiplication, computation time was reduced from 28.6 to 13.6 milliseconds per computed value of the output, y(n), for a 27-tap FIR-filter subroutine—and to 11.9 ms with direct addressing.

With hardware multipliers, the high speed they make available is also approximately doubled. An N-multiplication FIR design, using a 16 × 16-bit ADSP-1010 multiplier/accumulator (165ns per multiply/accumulate) yields an execution time—for a 32-tap FIR—of 5.28 microseconds. The add-then-multiply approach, using an ADSP-1010 for the MAC and four Fairchild 74F283's for the adder (36ns per 16-bit add), yields an execution time for a 32-tap FIR of 2.68µs. Part of the speed improvement in the add-then-multiply approach results because the clocked input registers of the MAC act as a pipeline register between the adder and the MAC stages of the hardware. Thus, at the cost of minimal additional hardware, the add-then-multiply approach attains an almost twofold improvement in speed over the direct-form implementation of the FIR.

Figure 6. Pointer scheme to implement add-then-multiply FIR filter.

Analog Dialogue 18-2 1984

### FLASH CONVERTERS WORK BETTER WITH TRACK/HOLDS

# There Is Less Distortion of High-Frequency Signals Conversion Is Performed with Better Linearity and Few (If Any) Missed Codes

by Jerry Neal and Jim Surber

High-speed analog-to-digital "flash" converters (ADCs) are coming into widespread use. Although they provide the promise of "instantaneous" conversion, and their latching systems would appear to make track-holds unnecessary, it has long been our opinion that they would perform closer to their full dynamic potential when used with fast track-holds. Until now, users have had few options because of the rarity of really fast T/H's, but with the recent introduction of the HTS-0010" (Analog Dialogue 18-1, 1984), it is now feasible to enjoy the benefits of track/hold with flash converters.

In this article, we report on the results of a Computer Labs study of the possibility of improving flash-ADC performance by employing a fast track-hold amplifier. Not to leave you in suspense, the magnitude of the improvement, at both fast and slow encode rates, is remarkable. Even low-resolution (6-bit) flash-converter circuits can benefit.

Read on if you wish to learn: why flash ADC circuits benefit from track/hold signal conditioning; about two test methods for verifying performance improvement; how to select and implement track-and-hold amplifiers for use with flash converters.

#### WHY FLASH CONVERTERS NEED TRACK/HOLDS

Traditionally, flash converters have been used without a track/hold amplifier, because the internal latches of the converter perform a track/hold function. However, there are distinct advantages in using a T/H for signal conditioning ahead of the converter, because the analog comparison may not yet be valid at the time the decisions are latched.

Figure 1 shows a typical converter subsystem. The function of a track/hold amplifier at the input of a sampled-data system is to follow all changes in the analog input as they occur ("track" mode) and periodically capture an instantaneous sample of that input ("hold" mode) for additional signal processing. The change from track to hold is accomplished with an encode command by the user; the trailing edge of that command returns the unit to the track condition to await the next encode command.

Figure 1. Typical flash ADC-track/hold subsystem.

\*Use the reply card for technical data.

Portions of this article are reprinted with permission from ELECTRONIC DESIGN, Vol. 32, No. 9; copyright Hayden Publishing Co., Inc., 1984.

Track and hold alternate during each strobe period; the hold interval is established by the time allotted for conversion, and the track interval is the remaining portion of the strobe period. The sampling rate (1/strobe period) is limited at the high end by the time required for the track/hold to acquire the analog signal and settle to a sufficient degree of accuracy.

The ability of the track/hold amplifier to freeze a fast-changing analog signal, i.e., to transform it into a set of successive dc voltages, is the characteristic which permits the T/H to enhance the performance of flash converters.

Flash ADC's use  $2^{(n-1)}$  comparator cells to perform the parallel flash conversion. Certain inherent characteristics of these cells tend to degrade the performance of the flash converter as the analog input frequency and/or the encode rate are increased.

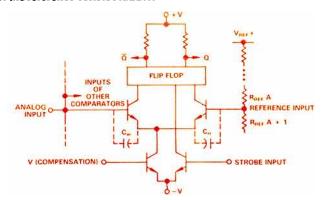

As Figure 2 shows, each comparator has a differential input—with the analog input signal on one side and a reference voltage on the other. The reference voltage, or switching threshold, at a different level for each comparator, is established by the voltage divisions of the reference-resistor ladder.

Figure 2. Typical flash-converter comparator cell.

All flash converters have inherent capacitance characteristics that affect their ability to operate on high-frequency analog signals. There are sets of problems that are specific to each of the inputs.

The analog input capacitance ( $C_{ai}$ ) of each comparator is determined primarily by the base-emitter junction capacitance of the transistor on the analog-input side. The value of this capacitance is affected by junction bias; forward-bias capacitance is higher than reverse-bias capacitance. Since the inputs of all comparators are in parallel, the total capacitance at the flash converter's analog input is the sum of the individual comparators' base capacitances.

Unfortunately, the total capacitance is essentially random, because it depends on the amplitude of the analog signal: the signal amplitude and the on-off state of each individual comparator dictate its base-emitter voltage, hence its contribution to the total capacitance. The total capacitance can vary from 30 to 120 pF.

Since the comparator can be driven by an analog buffer, this is not a serious problem. However, the buffer doesn't solve capacitance problems associated with the reference input.

Figure 3. Equivalent circuit of the reference-resistor ladder.

Since the comparator has a differential input, the reference input is similarly subject to capacitance variations introduced by its base-emitter capacitance, C<sub>ri</sub>. But the problems they raise are not as easily dealt with; see Figure 3.

The charging path for each individual  $C_{\rm ri}$  is through the reference ladder. This charging path constitutes an R-C time constant at the reference input; and the time required to charge the capacitances through the resistors tends to cause the reference voltages to lag fast changes in the current flowing through the reference ladder, dynamically distorting the voltage division of the reference ladder.

This capacitive reactance effect depends on the differential input voltage to the comparator, the speed at which it varies (frequency), and the comparator's position within the ladder. When signals having high slew rates are applied, the a-c integral-linearity error of the comparator array will increase because of the reactance variations among the many comparators.

In addition, errors also occur due to noise introduced by parasitic coupling from the strobe circuit to the reference ladder via C<sub>ri</sub>. Although the strobe is equally coupled to both sides, the lower source impedance at the analog side tends to reduce its amplitude, resulting in an imbalance between the comparator inputs.

One of the most effective ways to equalize the differential input impedances of the comparators is to use an external resistor in series with the analog input of the converter, as Figure 1 shows, to produce better common-mode rejection of unwanted noise voltages and improve the integral linearity of the comparator array. The resistance value should be about one-fourth of the total resistance of the reference ladder (i.e., the parallel resistance of the upper and lower halves of the ladder resistance).

Another potential source of dynamic conversion error in flash ADC designs is the variation of effective sample delays. Individual comparators within an array can be visualized as having variable delay lines in series with their latch inputs. The magnitude of delay for each comparator is determined by comparator inconsistencies, chip layout, and the strobe frequency.

For low-frequency analog inputs, these sample-delay variations among adjacent comparators are not a significant problem. But as the input frequency is increased, latch-time disparities among comparators can result in missing codes and excessive differential nonlinearities. The errors differ with slew-rate magnitude and direction.

Many manufacturers and users of flash converters loosely define this variable-slew-vs.-latch error as "aperture-time uncertainty" or "jitter." That terminology can be misleading if a "jitter" specification does not include the total sample delay variations among the comparators. The misconception becomes readily apparent when the relationship of the maximum bandwidth (slew rate) of a flash converter to its specified aperture jitter is considered.

For a  $\frac{1}{2}$ -LSB error tolerance in the design of a flash converter, the maximum rate of change is  $(\tau_a = \max \text{ aperture jitter})$

$$dV/dt_{max} = \frac{1}{2}LSB \text{ voltage/}\tau_a$$

(1)

An undistorted sine wave's rate of change is

$$dV/dt = 2\pi f V_p \cos(2\pi f t)$$

(2)

where  $V_p$  is the peak amplitude of the sine wave. The maximum rate of change, occurring at the zero crossing, is

$$dV/dt_{max} = 2\pi f_{max} V_{p}$$

(3)

Substituting (3) in (1), and recognizing that  $\frac{1}{2}$  LSB =  $2^{-(n+1)} \cdot 2V_p$ , where n is the converter resolution,

$$f_{\text{max}} = 2^{-(n+1)}/\pi \tau_a$$

(4)

Thus, for an 8-bit converter with a specified aperture jitter of 30 picoseconds, one would expect a maximum large-signal bandwidth of 20.7 MHz. It is interesting to note that, for a commercially available 8-bit device with this specified aperture jitter, the maximum bandwidth is specified at only 7 MHz.

This disparity between the calculated bandwidth—using the aperture-jitter specification—and the bandwidth the vendor is willing to guarantee indicates that "aperture jitter" is not the crucial factor in the sample-delay variation of a flash converter. Performance evaluations of several models of flash converters have led to the practical conclusion that it would be more realistic to expect sample-delay variations as large as 200 to 300 picoseconds rather than to calculate them based on published aperture-jitter specifications.

They also suggest that there is room for improvement, if we can replace the sample-delay variations of a flash converter by the much faster performance characteristics of a sample-hold. For example, the Analog Devices HTS-0010 track/hold amplifier is specified to have an aperture uncertainty of 5 ps, in contrast to the 50-or-more picosecond sample-delay variation of a typical flash converter.

Since the track/hold ahead of the flash converter freezes the input signal, it maintains a constant input while the comparators are latching, and it can also be timed to allow the comparator input capacitances to charge and settle before the conversion takes place.

It is important to remember that a track/hold amplifier used ahead of a flash converter has no effect on the conversion time; it simply allows the converter to digitize higher-frequency (faster slew rate) analog signals. The total time required for conversion, taking into account the delays of both the track/hold amplifier and the flash converter, can be calculated and compensated for by the system timing.

#### TESTING COMPARATIVE PERFORMANCE

AC linearity tests concretely demonstrated the improvement of performance gained by teaming a flash converter with a track/hold amplifier. The parameters tested were harmonic distortion and differential linearity. Both test series demonstrated excellent performance improvement for converters of all resolutions—at all encoding rates.

A real-time spectrum analyzer provided a basis for judging the improvement in harmonic distortion. An input waveform was con-

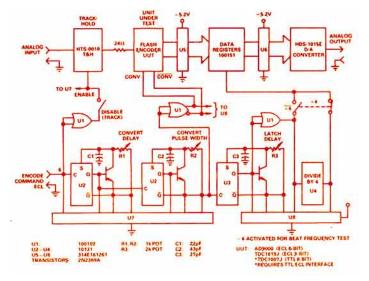

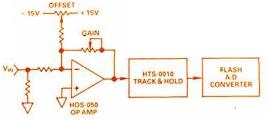

Figure 4. Test fixture for converting and reconstructing analog waveforms at high speed.

verted to digital, then reconstructed, using the test fixture of Figure 4. The measurement instrumentation consisted of a Hewlett-Packard model 8553B RF-section/8552B IF-section spectrum analyzer, for displaying the frequency spectrum of interest.

The sampling bandwidth of the spectrum analyzer was limited to 3 kHz, to maximize the dynamic range of the analyzer and make the test results easier to interpret. If the sample bandwidth is too high, the quantizing noise level can mask the harmonics and make it more difficult to determine their precise amplitudes.

The encode command, buffered through U1—wired as shown—generates the track/hold command; its duty cycle determines the hold time. Strobes for the flash-encoder and the data-registers are generated by one-shot multivibrators; they are used to control the timing and width of the flash converter's strobe—and the timing of output data being applied to the register.

Elements U5 and U8 are resistor strips, which supply Thévenin equivalent terminations for the high-speed ECL signals being used. They were selected because they are easy to use, and their characteristics are compatible with good high-speed-design practice. At the output of the test fixture, a high-performance, 10-bit ECL-compatible d/a converter minimizes the amount of DAC-contributed error at the frequencies of interest.

Harmonic-Distortion Test. In the harmonic-distortion test, the flash ADC encodes a full-scale sine-wave input at various selected

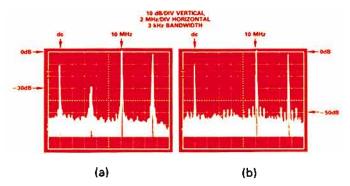

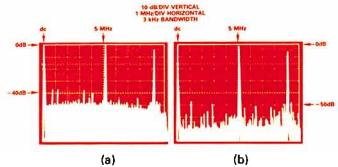

Figure 5. 6-bit flash converter output-spectrum display, 25-MHz encode rate, 10-MHz analog input. (a) Track/hold inactive. (b) Track/hold active

frequencies. The d/a converter in the test fixture reconstructs the digital output of the ADC into an analog representation of the input. The reconstruction is then measured for harmonic content on the analog spectrum analyzer. Although the harmonics themselves are out-of-band, they produce beat frequencies that appear in-band.

In the first test, a 6-bit flash converter (AD9000) was encoded at 25 MHz, with a 10-MHz sine-wave input. With a word rate of 25 MHz, the frequency band of interest is from dc to 12.5 MHz, for Nyquist conversion. It is desirable for all frequencies in this band to be well below the amplitude of the input signal. As Figure 5a shows,\* with the T/H inactive (i.e., in the track mode), or even completely bypassed, the highest component in this band is 29 dB below full scale.

Figure 6. 9-bit flash converter output-spectrum display, 14-MHz encode rate, 5-MHz analog input. (a) Track/hold inactive. (b) Track/hold active.

When the T/H is activated (i.e., switched between track and hold, with a 25 ns strobe, the highest harmonic component in the band measures 45 dB below full scale (Figure 5b). The AD9000 used in this test was selected for excellent linearity (within ±1/4 LSB), which resulted in low harmonic content. The test demonstrates than an input track/hold amplifier is beneficial, even for a 6-bit flash operating at relatively slow word rates.

Another harmonic distortion test was performed with a 9-bit flash converter (TDC1019J), encoded at 14 MHz with a 5-MHz full-scale sine-wave analog input. For this test, the frequency band of interest is from dc to 7 MHz. With the T/H inactive (Figure 6a), the in-band harmonics measure 39 dB below the fundamental. Figure 6b shows that activating the track/hold amplifier results in a 9-dB improvement of in-band harmonics—a significant improvement. Tests performed with an 8-bit flash (TDC1007J) indicated performance improvement commensurate with that of the 9-bit flash.

Beat-Frequency Test. This test demonstrates the converter's highspeed differential-linearity characteristics. The method used is to encode the converter's full-scale sinewave analog input at a frequency differing from the input frequency by precisely 2 kHz. Successive samples of the encode command step slowly through the

\*A bit of guidance may be desirable in interpreting these spectral plots: First, note that dB scales are logarithmic; there is no "zero." Hence, all that frightening-looking stuff at the bottom of the figure is pretty far down; the highest error peaks are the only ones to be concerned about. In Figure 5a, the peak at de is a marker to indicate the location of de; the peak at 15 MHz represents a beat between the 10 MHz signal and the 25 MHz sampling frequency - it is out of hand; and the one at 5 MHz is the result of a beat between the 15 MHz beat and the 10 MHz signal. Note that, on the logarithmic scale, each bit of resolution corresponds to 6.02 dB. However, these results are not intended to imply absolute harmonic-distortion performance of the various flashes, just comparative performance with and without T/H.

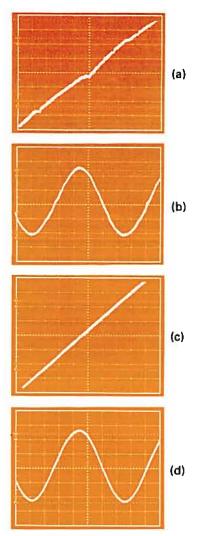

Figure 7. 8-bit converter linearity with 9.998-MHz input, 10-MHz encoding rate. (a) Major-carry linearity, T/H inactive. (b) Output waveshape, T/H inactive. (c) Major-carry linearity, T/H active. (d) Output waveshape, T/H active.

sinewave input at the 2 kHz beat rate, and the ADC yields an output sinewave at the beat frequency. In effect, we are purposely creating a 2-kHz alias which, nevertheless, shows the errors of the conversion, such as missing codes and differential nonlinearities which are occurring at a much higher frequency and would be much harder to capture in a high-speed reconstruction.

A modulo-4 counter is incorporated in the test setup to look at every fourth sample, an arbitrary measure to make it easier to synchronize the oscilloscope waveform. The relatively slow beat code is reconstructed with a slow, accurate d/a converter and displayed on an oscilloscope.

The first test was of an 8-bit TDC-1007J flash converter. The ADC strobe width was 20 nanoseconds, applied to the converter 15 ns after the leading edge of the *encode* command. The track/hold amplifier was activated with a 23-ns hold pulse. In all tests, the analog input was a crystal-controlled full-scale sinewave of the appropriate frequency; the encode command, crystal-controlled but asynchronous, was set at a frequency 2 kHz higher than the analog input.

Figure 7 shows the test output with an encoding rate of 10 MHz and a 9.998-MHz sine wave applied. Without the T/H, the sinewave is visibly distorted (b), and the actual linearity errors and

Figure 8. 8-bit converter linearity with 19.998-MHz input, 10-MHz encoding rate. (a) Major-carry linearity, T/H inactive. Note multiple missed codes. (b) Output waveshape, T/H inactive. (c) Major-carry linearity, T/H active. (d) Output waveshape, T/H active.

missing codes are quite apparent (a). When the T/H is activated, the clean waveforms of (c) and (d) result. The code-spacing now seems almost perfect, with greatly improved overall linearity.

Figure 8 shows the test output for the same ADC with an encoding rate of 20 MHz and a 19.998 MHz sine-wave input. Here, the display (a) and (b) shows even greater anomalies in the flash output because of the higher slewing rate of the analog input. But again, with the T/H activated (c) and (d), the errors disappear and the integrity of the reconstructed signal is materially improved.

The above tests were repeated with a 9-bit flash converter (TDC1019J) and displayed the same kind of degradation/improvement results in high-speed differential linearity.

#### SELECTING AND USING A TRACK/HOLD AMPLIFIER

Careful selection of the correct track/hold amplifier and a few design precautions will help the designer ensure successful operation of a flash converter-track/hold combination. The encoding rate limitation for the units working together can be calculated:

$$f_{\text{max}} = 1/(T_A + T_S + T_b) \tag{5}$$

where  $f_{max}$  is the maximum encoding frequency, and  $T_A$  and  $T_S$  are the acquisition and settling times to the desired resolution

(track/hold specification), and  $T_h$  is the hold-time necessary for the flash converter to set up (flash converter specification).

The large-signal bandwidth of the track/hold amplifier must also be high enough to accommodate the analog input signal without attenuation. For example, the 40-MHz analog bandwidth of the HTS-0010 is commensurate with Nyquist operation of most available flash converters.

For best performance, the track/hold amplifier and the flash converter should be mounted on a massive ground plane, as close to one another as possible. All ground pins must be connected together and to the ground plane, close to the case. Decouple the track/hold amplifier power-supply leads from ground with a 0.01-µF ceramic capacitor and a 10-µF electrolytic capacitor. These connections should be made right at the supply pins of each device. It is also mandatory to isolate the analog and digital inputs physically for proper high-speed performance.

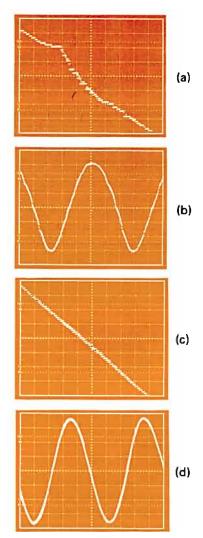

Figure 9. Input signal conditioning with HOS-050 op amp.

Some flash converters work best with a unipolar input range such as 0 to +2 V, or 0 to -2V. Since many applications use bipolar sources, some sort of signal conditioning is often necessary to scale and offset the input signal. This can be combined with buffering through the use of a high-performance op amp, such as the HOS-050\*, as shown in Figure 9.

Adhere to the guidelines outlined here to obtain better initial performance and reduce the time needed for "cleaning up" the circuit layout. Applications assistance from manufacturers is readily available, and designers should make use of this help, whether they are planning to implement a high-speed track/hold amplifier, a flash converter, or some combination of these and other devices.

#### CONCLUSION

When maximum ac performance is required from a flash ADC, a fast track/hold amplifier at the input is a must. The T/H performs the signal-acquisition function and allows the flash ADC to operate in essentially a dc mode. As the test results shown here illustrate, flash converters of all resolutions benefit from an input track/hold amplifier, even at relatively low conversion frequencies.

One final caveat: Since all systems are unique, the engineer is strongly encouraged to evaluate the track/hold amplifier in the actual final design application. This technique is the only true guarantor of performance and guardian against surprises.

#### UNDERSTANDING TRACK/HOLD AMPLIFIER TERMINOLOGY

Acquisition Time An indication of how fast the track/hold can be updated, it is the total time required for the charge on the storage capacitor (and, in most cases, the output voltage) of the track/hold amplifier to reach a specified error band about its final value, after the control input is switched from hold to track. Included are the times required for switching, slewing, and capacitor charging to within a specified tolerance.

Aperture (delay) time The mean time required for the switch in the track/hold amplifier to become fully open after the hold command is applied. The actual sample of the analog voltage being held is delayed by this amount; the timing of the hold command can be advanced to take the aperture delay time into account. This interval does not vary from one sample to the next within a given T/H; since it can be compensated for, it does not contribute to errors in the held value of a regularly sampled voltage.

Aperture Uncertainty (jitter) The sample-to-sample variation in the track/hold's aperture time. Caused by noise, phase shifts, and other unpredictable factors, it is augmented by the jitter of any time marker affecting the system aperture time. A random phenomenon, aperture jitter cannot be compensated for by timing adjustments. It can cause errors in the held value of voltage from one sample to the next. The contribution to aperture jitter is a critical specification for a T/H amplifier.

Bandwidth The maximum frequency which can be transmitted by the track/hold amplifier with less than (or equal to) 3 dB of attenuation. It is expressed in MHz for high-speed devices.

Charge Transfer See Pedestal.

Droop Rate The rate at which the held value at the output of the T/H amplifier changes during the time the unit is in the hold condition, as a result of leakage or bias currents flowing in either direction through the hold capacitor; its polarity depends on the sources of droop. In devices requiring external capacitors, it is often specified as a maximum current (I = C dV/dt).

Feedthrough The fraction of the ac input waveform or fast signal variations that appears in the held output value of the track/hold amplifier in the hold mode; it is caused by stray capacitive coupling from the input to the storage capacitor, principally across the open switch. This value is generally expressed in terms of dB below full scale.

Pedestal (also known as charge transfer, offset step, or sample-to-hold error) A measure of charge transferred to the hold capacitor via stray capacitance when switching to the hold mode. The charge causes a shift in the level of the sample voltage which is being held. Pedestal voltage is reduced by lightly coupling a version of the hold command signal in opposite polarity for cancellation. In devices with fixed internal capacitors, it is expressed in millivolts; otherwise in picocoulombs.

Settling time The time required for the output of the T/H amplifier to reach its final value, within some error band (usually expressed as per cent of full-scale), when the unit makes a change from track to hold.

<sup>\*</sup>Use the reply card for technical data.

### FIRST 12-BIT, 1-MHz HYBRID A/D CONVERTER WITH TRACK-HOLD

HAS-1201 Is Complete in 46-Pin Hermetically Sealed DIP

Two-Step Flash Unit is Ready to Go, Needs only Power and Encode Commands

#### WHY COMBINE A TRACK/HOLD WITH AN ADC?

As the preceding article (page 10) has noted, track/hold is essential to accurate conversion at high sampling rates, even with "flash" converters, because of the converter's sample-delay variations. A good track/hold stage, with low aperture jitter, freezes the rapidly varying input signal, converting it momentarily to a "dc" signal, long enough for a fast converter to deal with it.

To demonstrate the necessity of track/hold in high-speed conversion (as well as at surprisingly low speeds), consider this: the highest sine-wave frequency, f<sub>H</sub>, that can be digitized with predictable ½-LSB resolution, with a given aperture uncertainty, T<sub>a</sub>, is

$$f_{H} = 2^{-(n+1)}/\pi \tau_{a}$$

(1)

For n = 12 bits and  $\tau_a = 100$  ns,  $f_H$  is about 389Hz. In order to digitize a 389 kHz sine wave (about the highest frequency you'd want to digitize at a 1-MHz sampling rate) to this degree of resolution, the aperture uncertainty would have to be less than 100 ps. A track/hold can be used to achieve this; in the HAS-1201\*, the aperture delay time is 30 ns, and the uncertainty is 80ps.

The strong rationale for the HAS-1201, the coming standard 1-MHz 12-bit converter, is: since the track/hold is necessary, why not have it on-board? For this to happen with specified performance, all sorts of parts-procurement, noise, timing, layout, and interconnection problems are resolved by the converter manufacturer (instead of the user). This allows the manufacturer to optimize the components as a subsystem, providing a synergism that is otherwise unavailable to the end user.

#### **THE HAS-1201**

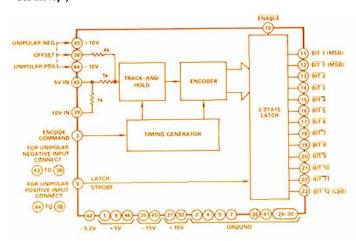

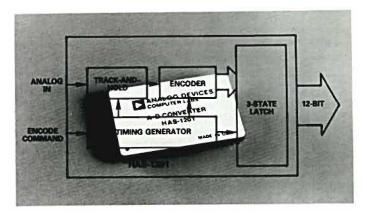

The HAS-1201 is the first complete commercially available 12-bit, 1-MHz converter with track/hold in a hybrid package; it requires only power and an encode command. After receiving an encode command, the HAS-1201 generates the necessary internal timing commands to hold the signal, control the two-step flash conversion process, and load the data into the output three-state latches.

\*Use the reply card for technical data.

Figure 1. Functional block diagram of the HAS-1201

Designed for applications in radar, digital signal processing, medical instrumentation, and test systems, it eliminates the need for either a board-level product or a separate ADC and T/H.

Available in a 46-pin hermetically sealed metal package, the HAS-1201 linearity is typically within ½ LSB; monotonicity is guaranteed over temperature. The converter accepts bipolar or unipolar 5- or 10-volt signals, presenting respective input impedances of 1000 or 2000 ohms. Other dc specifications include 2-mV maximum input offset and 200 µV/°C max input offset drift.

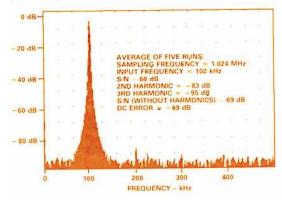

In high-speed conversion applications, dynamic specifications are as important as dc performance. For the combined converter and T/H, the HAS-1201 offers typical 80-dB in-band harmonics and 67-dB signal-to-noise ratio (100-kHz input). The typical 3-dB signal bandwidth is 3 MHz for small signals and 500 kHz for large signals.

Outputs are coded in complementary: binary, offset binary, or twos complement; all outputs are TTL-compatible, and the output is interfaced to a 12- or 16-bit bus by a set of 12 parallel 3-state latches.

Standard supply voltages required are: +15 V, -15 V, +5 V, and -5.2 V, and power dissipation is 3.5 W max. Available in a  $2.4'' \times 1.6'' \times 2''$  (60 mm  $\times$  40 mm  $\times$  6 mm) hermetic metal package, the HAS-1201SM is specified over a  $-55^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  case-temperature range. The HAS-1201KM and HAS-1201SM are priced at \$365 and \$457 (100s).

Figure 2. 512-point FFT spectrum of ADC output shows excellent harmonic and broad-band noise performance.

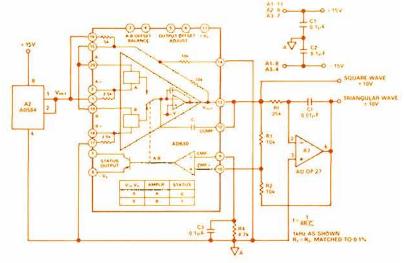

### USE THE MONOLITHIC AD630 FOR PRECISION WAVEFORMS

# Generate Square and Triangular Waves with Balanced Modulator/Demodulator Control Amplitude and Frequency Independently and Flexibly

by Walter G. Jung

A great many free-running relaxation oscillator circuits, employing R-C circuits for timing, have been published in recent years—including many that offer high precision. <sup>1,2</sup> Generally the precision of these circuits is restricted to their frequency predictability and stability; seldom do we see circuits that, in addition, offer accurate, easily adjustable output amplitudes.

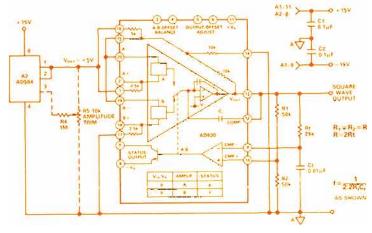

The AD630\* Balanced Modulator/Demodulator, described recently in these pages,<sup>3</sup> is uniquely suited for such applications, since it contains all the active circuitry needed to self-generate a square wave, with well-defined frequency and amplitude. To illustrate the device's versatility, we will describe here a precision astable circuit which has the flexibility to be modulated for transmitting data. We will also describe a function generator, which follows from the basic timing & control principles.

#### PRECISION ASTABLE OSCILLATOR

A square wave with predictable output amplitude can be built using a straightforward precision balanced modulator design, with a well-defined reference voltage as an input. The square-wave output can then be made to be equal to  $\pm$  M times the reference voltage. We can generate the required timing signals for commutating the balanced modulator with a precision comparator—a function that is inherently available in the AD630.

In Figure 1, the AD630 is configured as a switched-gain amplifier, with alternate gains of +2 and -2, set by appropriate external pin-strapping of the device's internal precision feedback circuitry.

For gain of +2, when input A is active, the input ( $V_{REF}$ ) is applied to A +, the non-inverting terminal of input A; and the gain is provided by feedback of ½ the output, via the two 10-kilohm resistors (there is no contribution by the 5-kilohm resistor, because both ends are at voltages equal to  $V_{REF}$ ). When input B is active, the 5-kilohm resistor serves as an inverter input resistor, and feedback

is via a 10-kilohm resistor, for a gain of -2 (the other 10-kilohm resistor is inactive because both ends are at 0 V). For best phase margin, the internal compensating capacitor (pin 12) is connected to the output terminal.

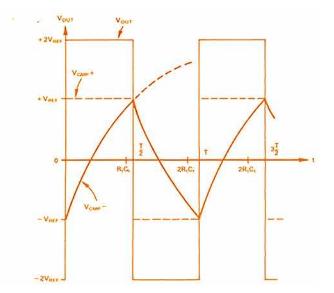

The timing characteristics of the circuit are defined by the feedback to the comparator, which switches the device inputs between A and B. There are two networks connected to the comparator inputs. To observe their function, let us suppose that the comparator has just switched to input A and the output is at  $+2 \times V_{REF}$ . R1 and R2 provide a fixed positive feedback of ½ the output level (i.e.,  $+V_{REF}$ ), keeping the comparator positive and A in the circuit. At the same time, Rt & Ct develop an exponentially increasing voltage on Ct, at the negative input to the comparator, changing from its previous state ( $-V_{REF}$ ) positively towards  $+2 \times V_{REF}$ . When it reaches  $+V_{REF}$ , the comparator switches,  $V_{OUT}$  jumps to  $-2 V_{REF}$ , and the exponential is now swinging back towards  $-2 V_{REF}$ , with the next change of state occurring as it crosses  $-V_{REF}$ .

Referring to Figure 2, at the switching point,

$$+ V_{REF} = -V_{REF} + 3 V_{REF} (1 - \epsilon^{-t/R_t C_t})$$

(1)

$$1 = 3\epsilon^{-t/R_t C_t} \tag{2}$$

Since the circuit switches symmetrically, t is the half-period point

$$T/2 = t = R_t C_t \ln(3) = 1.1 R_t C_t$$

(3)

$$f = 1/(2.2 R_t C_t)$$

(4)

As with all oscillators with timing dependent on an R-C time constant, the predictability and stability will depend critically on that of the components used. Both should have low temperature coefficients; the resistor should be a metal-film type, and the capacitor should be a low-dielectric-absorption polystyrene or polypropylene film type. The most-predictable and accurate performance occurs below 10 kHz, but the oscillator is generally useful at

Figure 1. Precision astable oscillator.

<sup>\*</sup>For technical data, use the reply card.

<sup>&</sup>lt;sup>1</sup>Jung, W. G. IC Op-Amp Cookbook Second Edition. Indianapolis: Howard W. Sams & Co., Inc., 1980.

<sup>2——</sup> IC Timer Cookbook Second Edition. Indianapolis: Howard W. Sams & Co., Inc., 1983.

<sup>&</sup>lt;sup>3</sup>Brokaw, P., Gerstenhaber, M., Miller, S. "Fast, Flexible Switched Dual-Input Op Amp and Comparator." *Analog Dialogue* 17-1 (1983): 14-15.

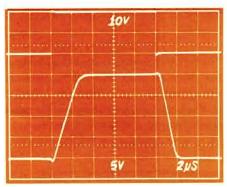

Figure 2. Waveforms illustrating operation of the circuit of Figure 1.

frequencies up to 100 kHz. In the example shown here, the frequency is approximately 1.8 kHz.

While the comparator's small switching window ( $\pm 2$  mV max over temperature) and fast action (200 ns step response time) enhance the predictability of the circuit's timing, the amplitude depends on the applied reference voltage,  $V_{REF}$ , and the gain-setting programmed into the AD630 (with gain error and mismatch less than 0.05%, when the internal resistors of the AD630BD or AD630KN are used). As it is set here, the peak output will be 2  $V_{REF}$ , since the application resistors are strapped for gains of 2. The peak-to-peak output is, of course, 4  $V_{REF}$ .

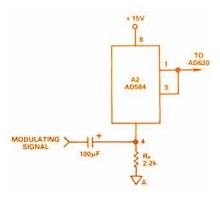

For V<sub>REF</sub>, an AD584\* precision reference-voltage source is used, with pins 1 and 2 strapped together for +5-volt output. Any alternative references used should have low output impedance, to minimize possible side effects which can arise from the dynamic load presented by the AD630's input when it is switched. This should not be surprising, since the AD630 responds to the comparator by essentially making two different op amp circuits available. The input impedance is characteristically high for the non-inverting mode and typically equal to R<sub>A</sub> in the inverting mode.

With  $V_{REF}=5$  volts and the gains equal to +2 and -2, an AD630AD (or JN) has a typical gain error of 0.1%. When it is used with an AD584K reference, the overall combined (untrimmed) amplitude tolerance will generally be less than 0.25%. For closer tolerances, the amplitude error can be reduced by the use of a trim network, shown in dotted lines in the figure.

Perhaps the principal virtue of the timing scheme employed can be seen in the step between equations (1) and (2): Since both the fraction of the output voltage and the amplitude of the exponential timing waveform are proportional to V<sub>REF</sub>, the actual switching time, hence frequency, has a first-order independence of output amplitude. This basic scheme, made popular with the ubiquitous 555 timer<sup>2</sup>, has an output frequency characterized by high immunity to output amplitude changes.

The practical advantage of this relationship is that the reference voltage can be programmed for different (coarse) amplitudes without disturbing the nominal operating frequency. Therefore you can strap the AD630, in this circuit, for different gains and output

amplitudes, as well as different levels of  $V_{REF}$ , and the basic frequency relationship will remain the same.

While the main square-wave output of the AD630 is at an accurate  $\pm 10$  volts, the STATUS output of the AD630's comparator—also a square wave—is available at pin 7. This output can be used for external synchronization and interfacing to logic operations. It is an NPN open collector, capable of swinging between  $\pm 15$  volts.

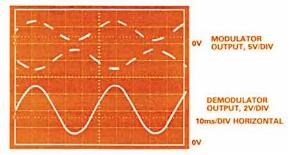

#### MODULATED OSCILLATOR