## analog dialogue

A forum for the exchange of circuits, systems, and software for real-world signal processing

AMPLIFIER NOISE BASICS REVISITED – AUTOMATIC NOISE TESTING (page 3)

"ADCPORT": Complete µP-Compatible Monolithic 8-Bit, 10-µs A/D Converter (page 24)

Monolithic CMOS Triple-Output DC-DC Converter (page 22)

Complete Contents on Page 3

### Editor's Notes

#### A SALUTE TO IEEE

In 1984, IEEE is celebrating its Centennial, as the successor organization formed by a merger in 1963 between the AIEE (American Institute of Electrical Engineers, founded in 1884) and the IRE (Institute of Radio Engineers, 1912).

sponsored conferences and in IEEE publications. Most of the illustrious contributors to the recent history of electrotechnology, whose names are household words, were members of IEEE.

During the coming year, you will hear much of the history and statistics of IEEE and about its Centennial—in any medium you happen to be tuned in to. Indeed, it will be impossible to avoid.

So it is not necessary for us to recite endless historical details or reams of facts and statistics about the numbers of members (approaching a quarter-million), the number and magnitudes of Societies and Councils housed under IEEE's copious roof, the number of conferences held under its aegis, the truly back-breaking number of publications at all levels—in both serial and book form—the sweep of its grassroots technical and educational activities (in Sections around the world), its vital standards activity, and its decade-old (and steadily evolving) "professional" activities, under the banner of its U. S. Activities Board. Congratulations to IEEE on its 100th anniversary!

#### CONTRIBUTE BEFORE YOU COMPLAIN

In the electronics trade press, we see criticisms of IEEE, particularly in relation to its purported neglect of the "working engineer." We believe that criticism is beneficial; either because of it or in spite of it, IEEE is growing rapidly, is embracing change, and, in many ways, is as healthy as we have ever seen it.

Our (your Editor's) involvement with IEEE has included major elective Society office and appointive activity on headquarters committees and boards. However, our most treasured activity has centred on the ongoing grassroots program activities of an IEEE technical-Society chapter in the Boston Section. We have contributed to its technical program via down-to-earth technical talks at local meetings, organized a Lecture Series, and perenially served on the program committee, contributing and evaluating subject matter, and taking responsibility for organizing meetings.

As a working local volunteer, in contact with members and other volunteers on a practical technical organizational level, we have gotten tremendous pleasure from our IEEE connection—and an appreciation that without such activity IEEE would be of far less value to its members. True also of those other grassroots volunteers who organize and participate in conferences, and those who write—and review—papers. IEEE is its volunteers. We suggest that people not criticize or complain about what IEEE has or hasn't done for the "working engineer" until they've tried contributing (of) themselves through IEEE in some modest way for their fellow working engineers' benefit.

Dan Sheingold

#### **THE AUTHORS**

Donald W. Brockman (page 18) is Technical Communications Manager at ADI's Computer Labs Division (formerly Computer Labs Incorporated), which he joined in 1968 from Bell Telephone Laboratories. His formal education includes a B. A. degree and he has worked in engineering, writing, recruiting, and sales functions before his present job in Marketing.

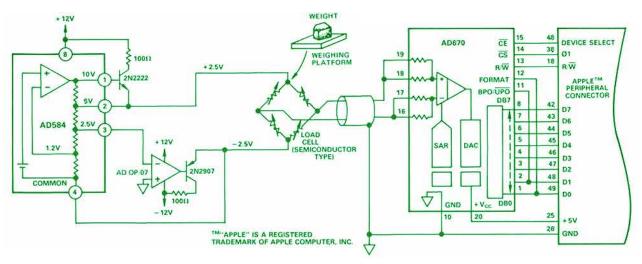

Doug Grant (page 24), New-Product Marketing Manager for data converters at Analog Devices Semiconductor, gained substantial recognition as a Microcircuits Applications Engineer at ADS and has published numerous papers and articles. He has a BSEE from Lowell Technological Institute and extensive experience in de-

veloping converters, µP-based data-acquisition systems, and analytical instruments. He is also active in Amateur Radio.

Diane Heerema (page 24), a Marketing Engineer for converter products at Analog Devices Semiconductor Division, was graduated from Rutgers in 1979 with B.S. degrees in E.E. and Physiology. After a brief period at Exxon Enterprises (Battery Division) as an Applications Engineer, she became an Applications En

gineer at ADI's System Components Division. She joined ADS in 1981.

Matt Johnson (page 14) is an applications engineer at the Analog Devices Digital Signal Processing Division (Norwood MA). He earned the BSEE degree at the Worcester Polytechnic Institute. Before joining ADI within the last two years, he worked at Teradyne, Inc., as a test engineer. Matt's leisure-time interests include

speech synthesis, home computers, and music (jazz, bluegrass, and classical).

(continued on page 29)

## analog dialogue

2 Technology Way, P.O. Box 280, Norwood, Mass. 02062

Published by Analog Devices, Inc., and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and display circuits and systems. Correspondence is welcome and should be addressed to Editor, *Analog Dialogue*, P.O. Box 280, Norwood, Massachusetts, U.S.A. 02062. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577 or 710-336-0562, Telex 924491, or cable ANALOG NORWOODMASS.

### D-C AMPLIFIER NOISE REVISITED

## Understanding, Measuring, and Testing for Random Noise A New Op-Amp Noise Fixture for Automatic Benchtop Tests with LTS-2010

by Al Ryan and Tim Scranton

"Like diseases, noise is never eliminated, just prevented, cured, or endured, depending on its nature, seriousness, and the costs/difficulty of treating it."

In Analog Dialogue 3-1 (1969)—now out of print—we published an article entitled "Noise and Operational Amplifier Circuits," intended to be a readable and easily applicable essay on noise principles, with primary emphasis on random noise, in a treatment distinguished more by vigor than by rigor. On this, its 15th anniversary, it seems appropriate to review the salient tutorial, proffer data on modern IC op amps, and discuss the test means embodied in a new test socket assembly for automatic noise testing, employing the LTS-2000 family of benchtop device testers.

#### WHY BE CONCERNED ABOUT NOISE?

An understanding of noise is needed to know what the real resolution of your system is. A knowledge of noise characterization and testing is needed to evaluate an amplifier or other purchased device with a given set of noise specifications.

As conversion systems employ increased digital resolution, the value of the least-significant bit decreases. For example, the LSB of a 10-bit system with 10V full scale is about 10 millivolts, the LSB of a 12-bit system is about 2.5 millivolts, and the LSB of 16 bits is 153 microvolts. This, by itself, poses significant problems in converter design.

However, the real-world measurement situation is worse, because most signals derived from real-world sources have full-scale amplitudes considerably less than 10 volts and must be amplified. If, for example, the original signal has a full-scale level of 10 mV (not unusual in transducer applications) and thus requires amplification of 1000 ×, the 12-bit LSB would become about 2.5  $\mu$ V. If the preamplifier and its associated active and passive circuit elements generate only 1  $\mu$ V of noise—or 100 pA in 10,000 ohms—(referred to the input) when the signal is sampled, they will significantly affect the accuracy, perhaps neutralizing the resolution.

Noise in data-acquisition systems takes three basic forms, transmitted noise—inherent in the received signal, device noise—generated within the devices used in data acquisition (preamps, resistors, etc.), and induced noise—picked up from the outside world, power supplies, logic, or other analog channels by magnetic, electrostatic, or galvanic coupling.

Transmitted noise must be dealt with, to the degree possible, by reducing noise at the source or in the transmission medium, and

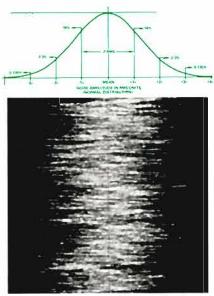

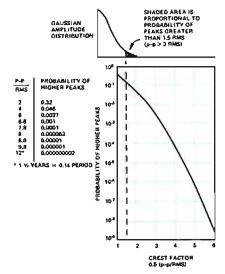

Figure 1. Gaussian amplitude distribution, juxtaposed against random-noise waveform.

otherwise by making use of statistical analysis and filtering to distinguish between properties of the signal and of the noise, often employing techniques of digital signal processing (DSP).<sup>4</sup>

Induced noise is affected by both electrical design choices and physical layout. Purposeful use of design techniques to predict and

### IN THIS ISSUE

| Volume 18, Number 1, 1984 – 32 Pages                                          |

|-------------------------------------------------------------------------------|

| Editor's Notes, Authors (more authors on pages 29 and 30) 2                   |

| Amplifier Noise Revisited - and a New Fixture for Automatic Noise Testing . 3 |

| Second-Generation Monolithic RMS-to-DC Converter (AD637) 11                   |

| Approximating Functions with Digital Signal-Processing ICs 14                 |

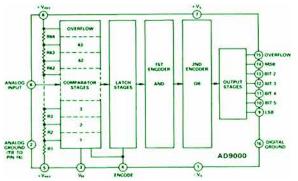

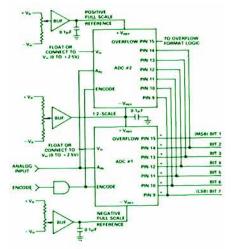

| 75-MHz Conversions with 6-bit Monolithic Flash ADC (AD9000) 18                |

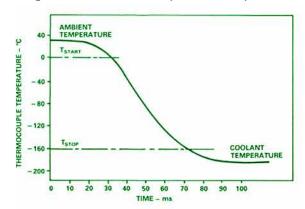

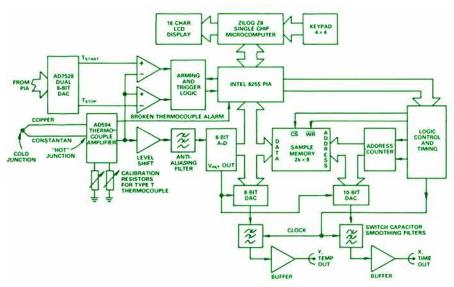

| Rate-of-Cooling Meter for Cryogenic Applications (featuring ADS95) 19         |

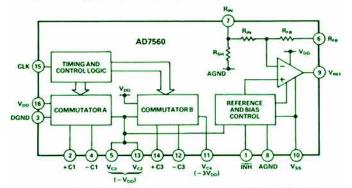

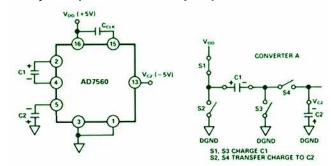

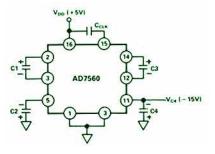

| Monolithic CMOS Triple-Output DC-DC Converter (AD7560) 22                     |

| Complete Monolithic 8-Bit, 10-us A/D/Converter (AD670) 24                     |

| New Products:                                                                 |

| Low-Noise Op Amp: 0.18µV p-p max (AD OP-27) 26                                |

| Monolithic Temperature Sensor in Plastic (ADS92)                              |

| Monolithic 12-Bit DAC Family (AD DAC80, DAC85, DAC87) 26                      |

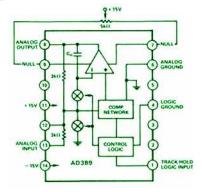

| Highest-Resolution, -Speed, Track-Holds:                                      |

| First Hybrid 14-Bit Track-Hold (AD389)                                        |

| Fastest Acquisition Time: 14 ns typ, 19 max, to 0.1% (HTS-0010) 27            |

| CMOS Multipliers and Multiplier-Accumulators (ADSP-1012, -1009) . 27          |

| Test Boards for Fast MCT-Handler-Based Tests of Digital ICs 28                |

| 12-Bit Hybrid Inductosyn/Resolver-Digital Converter (IRDC1732) 28             |

| p.P-Controlled 12-bit 3-Axis Resolver/Inductosyn Conversion                   |

| (MCI-1794)                                                                    |

| New Analog Devices Division Fellow Named: Lew Counts                          |

| Worth Reading: Noise Bibliography, RMS Application Guide, Short-Form          |

| Catalogs on High-Speed Conversion Products and Component Testers . 30         |

| Porpourri                                                                     |

| Advertisement 32                                                              |

<sup>&</sup>lt;sup>1</sup>Analog-Digital Conversion Notes, ed. by D. H. Sheingold, Analog Devices, Inc., \$5.95.

<sup>&</sup>lt;sup>2</sup>Based on work done by LR. Smith at Analog Devices.

<sup>&</sup>lt;sup>3</sup>A bibliography on random noise will be found on page 30.

<sup>\*</sup>Good information and bibliographies on DSP can be found in articles recently published in \*Analog Dialogue: "CMOS ICs for Digital Signal Processing," (17-1, 1983) and "Digital FIR Filters without Tears" (17-2, 1983). Also available free from Analog Devices: "A Cookbook to Digital Filtering and Other DSP Applications," a collection of reprints of papers that originally appeared in EDN magazine during 1983.

reduce induced noise was discussed in Analog Dialogue in a twopart series by Alan Rich.<sup>5</sup>

This article is about the irreducible minimum—device noise—its properties, how it affects circuit performance, and how it is measured. Later in the article, we will describe a test fixture that can be used for noise tests employing the Analog Devices LTS-2000 family of automatic benchtop testers.

#### **RANDOM NOISE**

Resistors and semiconductor junctions generate random noise: the output amplitude at a given instant is uncorrelated with the output amplitude at some other instant, and any value of output is possible at any instant—but it cannot be predicted. When a large number of samples are taken, many stationary random processes have amplitude distributions that appear Gaussian, i.e., characterized by the familiar bell-shaped curve (Figure 1). If the distribution is of voltages, and if care has been taken to eliminate dc offsets, then the rms voltage will be equal to the standard deviation of the distribution. Since random noise tends to be a stationary process,\* the rms value tends to be constant for a given bandwidth and/or (sufficiently long) averaging interval.

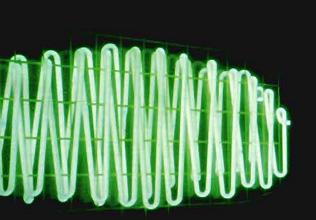

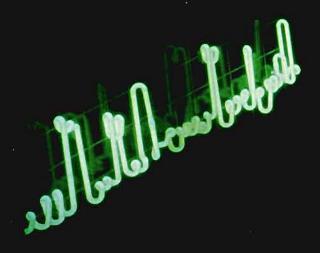

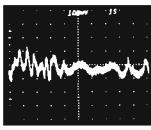

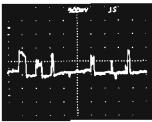

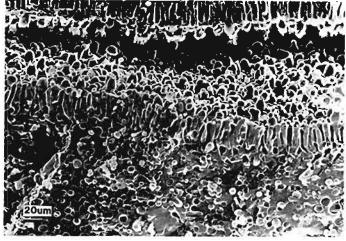

Device-produced random noise, when plotted on an oscilloscope screen, can be identified in terms of several characteristic signatures. The noise output of a single device may combine all three types. Figure 2 (a) shows broad-spectrum "white" noise, which may be thermal (Johnson), or shot (Schottky); it has a constant distribution across the frequency spectrum but looks as if it is heavily oriented to the higher frequencies. Figure 2 (b) shows "pink", or "1/f", or "flicker" noise, dominated by low frequencies, and (c) illustrates "popcorn" noise (so-called because of its sound when presented audibly), characterized by random jumping between two or more levels.

(a) White noise.

(b) 1/fnoise.

(c) Popcorn noise.

Figure 2. Noise signatures.

Since popcorn noise consists of jumps having approximately equal amplitudes, devices that have popcorn noise tend to have anomalous sharp peaks in the amplitude distribution, indicating that the number of such amplitudes greatly exceeds their probability in a purely random distribution.

White noise is present in all resistors and in semiconductor junctions. Resistor noise is thermal noise; its average power in a given bandwidth depends on temperature. Semiconductor junction noise is known as shot noise; its rms current variation in a given bandwidth is a function of the dc current through the junction.

"Excess noise" comprises all device noise that exceeds theoretical white-noise levels; it may be found when current flows through resistors, especially carbon composition types; it contains both shot noise and flicker components that are due to contact between carbon granules in resistors. For this reason, good practice mandates metal-film or wirewound resistors whenever low noise is required in the presence of significant dc current flow.

Flicker noise in semiconductors is due to random fluctuations in the number of surface recombinations; and "popcorn noise," a negative indicator of semiconductor process quality, is due to random on/off recombination action in the semiconductor material, leading to erratic switching of an affected device's current gain.

#### QUANTITATIVE MEASURES

The average Johnson noise power, generated by thermal agitation of the electrons in a resistor, and dissipated in a circuit containing a matched resistive load of equal magnitude is given by (1):

$$P_0 = k T B$$

watts (1) where

$k = Boltzmann's Constant = 1.381 \times 10^{-23} joules/kelvin$

T = Absolute temperature, kelvins (°C + 273.2°)

B = Bandwidth,  $f_2 - f_1$ , ("brick wall") in hertz.

In a series circuit with a resistor, R, containing a noise generator,  $E_n$ , and a matched resistor, of value R, the power dissipated in the load resistor is  $(E_n/2)^2/R$ , therefore

$$E_n = \sqrt{4 k T R B} \text{ volts}$$

(2)

where  $E_n$  is the rms value of voltage generated in source resistance R. Near room temperature, and with more-convenient units (i.e., T = 300 K, and  $R \times B$  in meg(ohm-Hz)

$$E_{\rm p} = 0.129\sqrt{\rm R} \times \rm B \, microvolts \, rms \tag{3}$$

Example: if  $R = 1k\Omega$  and B = (5 kHz - 4 kHz) = 1 kHz,  $E_n$  is equal to  $0.129 \,\mu\text{V}$ . If  $R = 100\Omega$  and  $B = 1 \,\text{kHz}$ ,  $E_n = 41 \,\text{nV}$ .

Johnson noise is quite often expressed in terms of an equivalent current source, In in parallel with the resistor,

$$I_n = E_n / R = 0.129 \sqrt{\frac{B}{R}}$$

(4)

where B is in hertz and R is in megohms.

Shot noise, caused by current flowing through a junction, is normally expressed as an ac current component, added to the dc value of I; it will produce voltage drops in series impedances, such as transistor emitter resistance or op-amp computing resistors:

$$I_n = \sqrt{2 e I B} = 5.66 \times 10^{-10} \sqrt{I B} \text{ amperes rms}$$

(5) where

<sup>5&</sup>quot;Understanding Interference-Type Noise," Analog Dialogue 16-3; and "Shielding and Guarding," Analog Dialogue 17-1

<sup>\*</sup>The statistical properties of a stationary process are invariant under a shift of the time origin.

<sup>\*</sup>Perfect sharp-cutoff filtering.

e = Unit charge,  $1.602 \times 10^{-19}$  coulombs

= DC current flowing through the junction, amperes

B = Bandwidth,  $f_2 - f_1$  hertz ("brick wall")

Expressed in more convenient units, if I is in microamperes,

$$I_{\rm p} = 0.566\sqrt{\rm IB} \, \rm picoamperes \tag{6}$$

#### NOISE DENSITY SPECTRUM

Noise exists in all parts of the frequency spectrum; the noise contribution of a resistor or amplifier varies with the bandwidth over which the observation is made. Characterization of noise in terms of its spectral density, i.e., as a function of frequency, makes calculation of noise in differing bandwidths in active circuits easier. A useful way of presenting noise characteristics graphically is via a plot of noise spectral density vs. frequency.

The power spectral density is defined as the derivative of noise power with respect to frequency (watts per hertz), i.e.,

$$p_n = \frac{dP_n}{df} \tag{7}$$

Since power is proportional to the square of rms voltage or current, the respective expressions for voltage and current noise spectral density are:

$$e_n = \sqrt{\frac{dE_n^2}{df}}$$

and  $i_n = \sqrt{\frac{dI_n^2}{df}}$  (8)

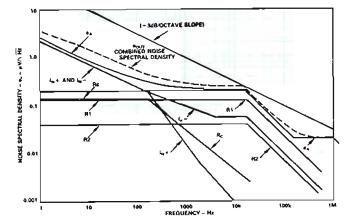

with units of V/ $\sqrt{\text{Hz}}$  and A/ $\sqrt{\text{Hz}}$ . Figure 3 shows typical spectral density plots of AD741 voltage and current noise, (a) and (b), compared with the low-noise bipolar AD OP-27's  $e_n$  and  $i_n$  (c) and the the low-drift FET-input AD547's  $e_n$  (d). Voltage noise tends to have a lower "corner" frequency (see 1/f noise, next page) than current noise in bipolar amplifiers. Illustrating different ways of presenting the data, the scales of (a) and (b) show mean-square voltage and current spectral density per hertz, while (c) and (d) show rms voltage and current spectral density per  $\sqrt{\text{Hz}}$ ; (d) is a semilog plot with a linear voltage scale for greater sensitivity to small noise voltage changes in the vicinity of the corner frequency.

The rms voltage or current in a given frequency band is determined by integrating the expressions in (8), i.e.,

$$E_{n}[f_{1} \text{ to } f_{2}] = \sqrt{\int_{f_{1}}^{f_{2}} e_{n}^{2} df}$$

$$\tag{9}$$

Spot Noise. If  $f_2 - f_1$  is quite small, we can assume that  $e_n$  is essentially constant (or "white") in that band (or "spot"), and  $E_n = e_n \sqrt{f_2 - f_1}$ . Using this, we can derive noise spectral density from a series of narrow-band measurements; the individual values of  $e_n$  are  $E_n / \sqrt{f_2 - f_1}$ . Enough points are observed to define a curve. These measurements are not easy to make, especially at low frequencies. By the same token, we can integrate a spectral-density curve of any shape by dividing the spectrum into small enough increments and taking the root sum-of-squares of the individual rms spot-noise contributions.

Graphical integration can be used to good effect, because plotted data based on measurements is seldom describable by easy formulas, and bandwidths aren't "brick-wall." However, approximations are often available that make it unnecessary to perform actual integrations over wide ranges of the noise characteristic.

#### **EXAMPLES OF SPECTRAL DENSITY**

Some simple rules for calculating noise over any bandwidth can

Figure 3. Noise spectral density plots. (a) Voltage-squared/Hz vs. frequency for AD741. (b) Amperes-squared/Hz vs. frequency for AD741, log-log plot. (c) Voltage and current per root hertz for AD OP-27, log-log plot. (d) Voltage per root hertz for AD547, semi-log plot.

be ascertained by the examination of two common forms of noise, white noise and 1/f noise.

White noise. As equations (1) and (5) show, white-noise power is of the form, (constant)  $\times$  ( $f_2 - f_1$ ), which can be recognized as the definite integral of (constant) with respect to frequency between the limits of  $f_2$  and  $f_1$ . For white noise, the spectral density is thus a theoretical or measured constant. Similarly, the voltage and current spectral densities,  $e_n$  and  $i_n$ , are equal to the square-roots of the respective constants (0.129 $\sqrt{R}$  microvolts for Johnson voltage,  $0.129/\sqrt{R}$  picoamperes for Johnson current (R in megohms), and  $0.566\sqrt{l}$  picoamperes for shot current (I in  $\mu$ A). The right-hand portions of the graphs in Figure 3 illustrate the approximately constant level of white noise at the higher frequencies.

From the curves in the white noise regions, wideband noise for any bandwidth is easily calculated as the product of voltage or current spectral density and the square root of the bandwidth  $(f_2 - f_1)$ . For voltage noise, if  $e_n$  is given:

$$E_n = e_n \times \sqrt{f_2 - f_1} \tag{10a}$$

If (e<sub>n</sub>)<sup>2</sup> is given,

$$E_{n} = \sqrt{(e_{n})^{2} \times (f_{2} - f_{1})}$$

(10b)

If  $f_1 < 0.1 f_2$ , the error in assuming  $f_2 - f_1 = f_2$  is less than 5%.

Example: Calculate the noise in the band, 100 Hz to 10 kHz, for each curve in Figure 3. The results are shown in the table:

| Curve    |          |                   | Value                                         | Calc.           |

|----------|----------|-------------------|-----------------------------------------------|-----------------|

| (Fig. 3) | Device   | Quantity          | from cueve                                    | rms noise       |

| (a)      | AD741    | $(e_n)^2$         | $3.5 \times 10^{-16} \text{V}^2/\text{Hz}$    | 1.86µV rms      |

| (b)      | AD741    | $(i_n)^2$         | $3 \times 10^{-25} \text{A}^2/\text{Hz}$      | 54 pA rms       |

| (c)      | AD OP-27 | (e <sub>n</sub> ) | $3 \times 10^{-9} \text{ V/}\sqrt{\text{Hz}}$ | $0.3~\mu V~rms$ |

| (c)      | AD OP-27 | $(i_n)$           | $0.4 \times 10^{-12}$ A/ $\sqrt{\text{Hz}}$   | 40 pA rms       |

| (d)      | AD547    | (e <sub>0</sub> ) | $23 \times 10^{-9} \text{ V/VHz}$             | 2.3 μV rms      |

5

Although the values of e<sub>n</sub> and i<sub>n</sub> are not strictly constant over the band, the value of wideband noise is always dominated by the higher frequency; if f<sub>2</sub> is well into the white-noise region, the shape of the curve at the lower frequencies will have negligible effect on wideband noise measurements.

Flicker noise, or "1/f" noise, has a noise power spectral density varying inversely with frequency. It is of the form (constant)/f";  $\gamma$  may be any value from 0 to 2, but it is usually close to 1. The shape of the left-hand portion of the noise curves in Figure 3 is due to 1/f noise, and the asymptotic slope—on a log-log plot—at the lowest frequencies is determined by  $\gamma$ . The point at which the projected 1/f asymptote crosses the average white-noise spectral density is the "corner frequency;" it is a measure of the quality of the device process—better devices have lower corner frequencies.

For voltage (and correspondingly for current),

$$e_n = K\sqrt{\frac{1}{f}}$$

(11)

K is the actual or extrapolated value of  $e_n$  at f = 1 Hz.

To compute  $E_n$  for the band,  $f_1$  to  $f_2$ , using (9),

$$E_{n}(f_{1} to f_{2}) = K \sqrt{\int_{1}^{f_{2}} \frac{df}{f}}$$

$$= K \sqrt{\ln(\frac{f_{2}}{f_{1}})}$$

(12)

The important result here is that equal amounts of 1/f noise will be generated in frequency bands having equal ratios. Every octave  $(f_2 = 2 f_1)$  or decade  $(f_2 = 10 f_1)$  in the 1/f-noise region will generate as much noise as every other octave or decade (i.e.,  $0.83 \times K$  per octave and  $1.52 \times K$  per decade); and the noise generated over m octaves or decades will be  $\sqrt{m}$  times as great as that generated in a single octave or decade.

Consider, for example, the rms value of noise in the 9-decade realm below 1 Hz (down to about 1 cycle per 32 years). If the rms value of noise in the decade, 0.1 Hz to 1.0 Hz, is 1 microvolt, then the noise over 9 decades will be  $\sqrt{9} \times 1 = 3.0 \,\mu\text{V}$ ! Over such long periods,—unless K increases—flicker noise can be expected to be less significant than drift caused by environmental factors, component aging, and perhaps even component life (however, there is evidence that increased 1/f noise—i.e., increased K—is often part of the end-of-life syndrome).

Example: What rms noise can be expected in the band, 0.1 to 10 Hz, for the devices plotted in Figure 3 (a), (b), and (c), extrapolating the curves to be asymptotic to a 1/f slope? The results are shown in the table.

| Curve              | K (Extrapolated)                     | Calculated E <sub>n</sub> | Corner<br>Frequency |

|--------------------|--------------------------------------|---------------------------|---------------------|

| (a)                | 0.22 μV/√ <del>Hz</del>              | 0.47 µV rms               | 100 Hz              |

| (b)                | 22 pA/√ <del>Hz</del>                | 47 pA rms                 | 2 kHz               |

| (c) e <sub>n</sub> | $4.9 \mathrm{nV}/\sqrt{\mathrm{Hz}}$ | 12 nV rms (white)         | 2.7 Hz              |

| i                  | 4.7 pA/√Hz                           | 10 pA rms                 | 140 Hz              |

Noise amplitude and Crest Factor. The rms value of noise is a consistent measure and is especially useful when dealing with signal phenomena having stationary properties, such as ac waveforms. However, in many cases, the accuracy or resolution of data is affected by the *instantaneous* value of noise, for example, sampled

dc measurements and one-shot responses. For these, we must know the expected peak or peak-to-peak values of noise.

Although all values of noise amplitude are theoretically possible, there is a rapid decrease in the likelihood of large values, corresponding to the residual area under the distribution curve (Figure 4) beyond a given value. For example, the probability of a *crest factor* (peak/rms) exceeding 3.3 is 0.1%; for a c.f. exceeding 6, it is  $2 \times 10^{-9}$ . Figure 4 is a table and plot of the percentage of time that noise can be expected to exceed a given nominal peak-to-peak value ( $2 \times c.f.$ ), for a Gaussian distribution.

Figure 4. Crest factor of gaussian noise. For a measurement period of 0.1 seconds, a crest factor of 6 can be expected to occur once in 1 ½ years.

Combining noise. Noise from uncorrelated sources adds as the square-root of the sum of the squares of the individual rms values,

$$E_{n} = \sqrt{(E_{n1})^{2} + (E_{n2})^{2} + \dots + (I_{n1} R_{1})^{2} + \dots}$$

(13)

Examples of uncorrelated sources are different resistors, transistors, diodes, amplifiers, etc. However, the magnitudes of the noise voltage and the current that it causes to flow through a resistor (or any impedance) are correlated.

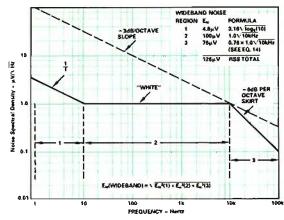

Since noise values are random with time, they are also random with frequency; thus, it is reasonable to consider that rms noise in different "brick-wall" frequency bands is uncorrelated and may be combined in root-square fashion. In fact, the integral performs just that function, using infinitesimal bands and the "spot" value of spectral density at each. This suggests that, in the example of Figure 5, we can treat the total noise given by integrating the spectral distribution characteristic over the broad frequency range as the noise obtained by separately integrating over the numbered regions and vector-summing (root sum-of-squares) the results.

#### **NOISE AND AMPLIFIERS**

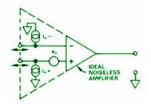

The model of a differential operational amplifier for noise, lumping the effects of all the internal sources, and referring noise to the input, is very similar to that for offsets and drift. As Figure 6 shows, it consists of an ideal noiseless amplifier, a noise-voltage generator in series with either of the inputs, and two uncorrelated noise-current generators, one in parallel with each input. Basic noise-test circuits resemble those for offset voltage and bias current.

Figure 5. Wideband noise is equal to the root-square sum of components in (1), (2), and (3). For any upper-frequency limit, total noise can be well-approximated by summing just those components in the vicinity of a-3 dB/octave line lowered tangent to the curve. In this example, (1) can be ignored for the wideband case, but not for a cutoff at 20 Hz.

Figure 6. Operational amplifier noise model.

In instrumentation amplifiers, in addition to the input noise sources (especially relevant at high gains), there is also a noise source associated with the output stage; its effect, referred to the input, is seen principally when the amplifier is set for low gains.

Like offsets and drifts, voltage noise is amplified by the "noise gain," (the closed-loop gain of the amplifier with its feedback circuit). Current noise, flowing through impedances, produces noise voltage, just as bias current produces offset voltage.

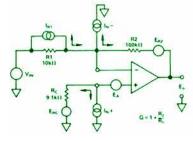

In addition to the effects lumped within the amplifier, each external resistor's noise contributes to the overall noise total, as though it were in series with a voltage noise generator or in parallel with a current noise generator (the choice depends on which makes the analysis easiet). The output noise, in a given bandwidth, depends on the contributions (to the output) of all independent noise sources. Since we assume the amplifier—and all the associated components—to be operating in the linear region, we may calculate the effects separately and combine them by superposition, but in root-square fashion, (they are uncorrelated random signals). In the example of Figure 7, the individual contributions are:

| E <sub>A</sub><br>I <sub>N</sub> _<br>I <sub>N+</sub> | Amplifier voltage noise Current noise at — input Current noise at + input | Multiplied by G = 1 + R <sub>2</sub> /R <sub>4</sub> Multiplied by R <sub>2</sub> Multiplied by R <sub>c</sub> × G |

|-------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| E <sub>Rc</sub>                                       | Voltage noise due to R <sub>c</sub>                                       | From eq. (2), multiplied by G                                                                                      |

| I <sub>RI</sub>                                       | Current noise due to R <sub>1</sub>                                       | From eq. (3), multiplied by R <sub>2</sub>                                                                         |

| E <sub>R2</sub>                                       | Voltage noise due to R <sub>2</sub>                                       | From eq. (2), direct                                                                                               |

When performing root-square summation, it is worthwhile to remember that any noise source less than  $\frac{1}{4}$  of the largest noise source contributes less than  $\frac{3}{6}$  to the total and can probably be ignored ( $\sqrt{1+0.25^2}=1.03$ ). Table 1 illustrates a typical calculation for the bandwidth, 100 Hz to 10 kHz, using values previously determined from the 741 curves in Figure 3 (a) and (b), the AD OP-27 curves in (c), and the AD 547 voltage noise curve in (d).

Figure 7. Noise sources in a gain-of-10 op-amp circuit.

Anticipating the reader's question, curves for current noise in FET-input op amps are not often published, because the noise is so low. In junction FETs, current noise is basically equal to the shot noise produced by the leakage current. For the AD547K, the maximum bias current is 25 pA at room temperature. Using (6),  $i_n = 0.566\sqrt{0.000025 \,\mu\text{A}} \, \text{pA}/\sqrt{\text{Hz}} = 2.8 \, \text{fA}/\sqrt{\text{Hz}}$ .

Table 1. Op Amp Noise Calculations in 100 Hz to 10 kHz BW ( $\Delta f = 9900 \text{ Hz}$ )

|          |                            |                       |                                        | Output            |

|----------|----------------------------|-----------------------|----------------------------------------|-------------------|

| Type     | Source                     | RMS Noise             | Factor                                 | Contribution (µV) |

| AD741    | EA                         | 1.86 μV               | ×11                                    | 20                |

|          | 1 <sub>N-</sub>            | 54 pÅ                 | ×0.1 M                                 | 5.5               |

|          | l <sub>N+</sub>            | S4 pA                 | $\times 0.009 \mathrm{M} \mathrm{X}11$ | 5.5               |

|          | ERC                        | 1.22 μV               | ×11                                    | 13.5              |

|          | l <sub>R1</sub>            | 128 pA                | $\times$ 0.1 M                         | 12.8              |

|          | E <sub>R2</sub>            | 4.1 µ V               | ×1                                     | 4.1               |

|          | Total                      | (root sum-of-squares) |                                        | 29                |

| AD OP-27 | E <sub>A</sub>             | 0.3 µV                | ×11                                    | 3.3               |

|          | I <sub>N</sub> _           | 40 pA                 | $\times 0.1 M$                         | 4                 |

|          | l <sub>N</sub> .           | 40 pA                 | $\times 0.009 \mathrm{M} \mathrm{X}11$ | 4                 |

|          | Enc                        | 1,22 μV               | × f 1                                  | 13.5              |

|          | J <sub>RI</sub>            | 128 pA                | × 0.1 M                                | 12.8              |

|          | E <sub>R2</sub>            | 4.1 µV                | ×1                                     | 4.1               |

|          | Total                      | (root sum-of-squares) |                                        | 20                |

| ADS47K   | EA                         | 2.3 μV                | ×11                                    | 25.3              |

|          | I <sub>N</sub> _           | 0.28 pA               | $\times 0.1 M$                         | 0.03              |

|          | I <sub>N</sub>             | 0.28 pA               | $\times$ 0.009M X 11                   | 0.03              |

|          | $\mathbf{E}_{\mathbf{Rc}}$ | 1.22 μV               | ×11                                    | 13.5              |

|          | J <sub>R1</sub>            | 128 pA                | × 0.1 M                                | 12.8              |

|          | ) <sub>R2</sub>            | 4.1 μ̈V               | ×1                                     | 4.1               |

|          | Total                      | (root sum-of-squares) |                                        | 31.6              |

In this example, it can be readily seen that, with an inverting gain of 10, the effective overall noise—referred to the input signal—is dominated by the AD741 and AD547's voltage noise—with significant contributions from the resistors—and amounts to about 3  $\mu$ V in both cases. On the other hand, with the much quieter AD OP-27, the resistors are the principal source of noise—with about 2  $\mu$ V, referred to the input signal.

Noise Figure. Even if there were no other sources of noise, the Johnson noise due to the input signal's source resistance would constitute a minimum. The noise contributed by the amplifier circuit, in relation to the noise generated by the source resistance, provides a means of characterizing the noise referred to the signal input. The circuit's noise figure is the logarithmic expression of the ratio of the total noise to that contributed by the source resistance. If no additional noise were produced, the total noise would be identical with the source noise and the ratio would be unity, thus the noise figure would be 0 dB. In this particular example, if we were to let the input resistance ( $R_1$ ) represent the source resistance, the noise figure would become 7.1 (=  $20 \log_{10} (29/12.8)$ ), 3.9, and 7.8 dB for the three cases.

Equivalent noise resistance. The amplifier circuit's noise may be characterized in terms of the Johnson noise, generated by the addi-

tional resistance that would be required to generate an equivalent amount of noise in the presence of an otherwise noise-free circuit; for the above examples, 41, 14, and 51 kilohms.

#### DYNAMICS

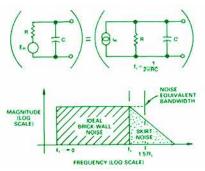

The noise, in the calculations above, is considered to be broadband white noise, with brick-wall filtering and no frequency-shaping elements (e.g., capacitors) in the circuits. Real filters, though, tend to have reduced response near the extremities of the pass band and graduated responses ("skirts") beyond the cutoff frequency; they are likely to pass more noise than a filter having the same cutoff frequency and perfectly sharp cutoff characteristics.

A simple circuit that can introduce us to both real-world considerations is shown in Figure 8. It consists of a resistor, R, considered as a current source, in parallel with a capacitor, C. The noise voltage generated by this circuit will be identical to that obtained using R as a noise voltage generator and a first-order low-pass filter with time constant RC, and cutoff frequency,  $1/(2\pi RC)$ .

Figure 8. White noise voltage with first-order lag filtering is similar to noise produced by a resistor with a capacitor in parallel and the same RC.

To determine the output voltage in accordance with (9), multiply the resistor's noise current spectral density,  $i_n$ , which is flat with frequency, by the magnitude of the impedance of the parallel R-C to determine  $e_n$ , then square it, integrate from  $f_1$  to  $f_2$ , and take the square-root. Assuming that  $f_1$  is much smaller than  $f_c$ , and desiring to determine all the noise within the passband of the filter, we integrate over all  $f_1$ , 0 to  $\infty$ . Since the impedance magnitude is

$$|Z| = \frac{R}{\sqrt{1 + \left(\frac{f}{f_c}\right)^2}}$$

$$E_n = i_n R \sqrt{\int_{f_1}^{f_2} \frac{df}{1 + \left(\frac{f}{f_c}\right)^2}}$$

$$E_n = i_n R \sqrt{f_c} \sqrt{\tan^{-1}\left(\frac{f}{f_c}\right)} \Big|_{0}^{\infty}$$

$$E_n = i_n R \sqrt{f_c} \sqrt{\frac{\pi}{2}}$$

$$= 1.25 i_n R \sqrt{f_c}$$

(14)

Thus, the first-order filter's 6-dB-per-octave skirt causes a 25% increase over the noise measured with an ideal sharp-cutoff filter.

We can think of this in two ways. First, the first-order lag filter adds an amount of rms noise equal to  $0.76 \, e_n \sqrt{f_c}$ , i.e.,  $\sqrt{1.25^2 - 1}$ , root-sum-square, to the brick-wall value of  $e_n \sqrt{f_c}$ . Second, we can think of the filter as being equivalent to a brick-wall filter having

an increased bandwidth, or noise equivalent bandwidth (N.E.B.) of  $(\pi/2)f_c = 1.57 f_c$ . Noise equivalent bandwidth, a useful concept, differs for various filters, depending on order (1st, 2nd, 3rd, etc.), type (high-pass, low-pass, Butterworth, Chebyshef, etc.), and spectral density characteristics of the noise being filtered, e.g., white, pink, shaped.

In similar fashion, overall frequency content of output noise is determined by the shaping effect of the circuit's dynamic elements on the spectral density of the noise from each source. The noise spectral density at the output of the amplifier due to the amplifier's voltage noise (in the absence of current noise) is the product of the closed-loop gain transfer function and the noise spectrum. The output noise produced by noise current in an inverting op amp is determined by multiplying the noise-current spectrum by the impedance spectrum of the feedback element. The overall output noise spectrum is determined by adding the noise spectral densities of output voltage due to all sources, taken independently, at each frequency, in root-square fashion.

This is easier than it sounds, because in practice very little error is incurred by allowing the largest value of noise at any frequency to represent the r.s.s. sum at that frequency. In the few exceptional cases, the largest values can be r.s.s.-added; for this kind of calculation, a calculator that performs vector addition is useful. A graphical technique is helpful in visualization.

#### ANOTHER EXAMPLE

Consider the example of Figure 9, a dynamic version of one of the examples given previously, employing the 741-type op amp and assuming a feedback capacitance, in parallel with  $R_2$ , of 100 pF. The AD741 has a -6 dB/octave rolloff and unity-gain bandwidth of 1 MHz; assume an input capacitance (amplifier and wiring) of 10 pF from the inverting input to common, and that  $R_c$  is bypassed by a 0.1  $\mu$ F capacitor. We wish to determine the overall noise spectral density and the wideband rms noise.

Figure 9. Dynamic version of Figure 7.

Table 2 describes the noise sources, the spectral density of the noise generated by each source, and its gain-bandwidth-output function. For the circuit shown, the noise gain is 11 V/V at dc, breaking at 15.9 kHz, dropping at 6 dB/octave to unity at frequencies above 159 kHz, and rolling off with the amplifier's gain at 1 MHz.

Figure 10 is a plot of the individual contributions of all six sources to the output, plus a plot of the combined noise spectral density, obtained by r.s.s. summation at various critical frequencies (e.g., 1 Hz, 100 Hz, 175 Hz, 300 Hz, 1 kHz, 2 kHz, 16 kHz, 160 kHz). Note that, at low frequencies, the amplifier's voltage and current 1/f noises are the most-significant contributors, while at high frequencies, e<sub>A</sub> and R<sub>1</sub> are the most-significant contributors. R<sub>2</sub>'s contribution is insignificant, and R<sub>c</sub> is a minor contributor, principally in the 100-200 Hz range.

Table 2. Calculations for spectral density plots of Figure 10.

|                  | _                                    |                                               | Output Spectral Density, µV√Hz |                        |                              |                                     |                                      |                          |                           |

|------------------|--------------------------------------|-----------------------------------------------|--------------------------------|------------------------|------------------------------|-------------------------------------|--------------------------------------|--------------------------|---------------------------|

| Noise<br>Source  | Frequency<br>or<br>Band<br>Hz        | Generated<br>Spectral<br>Density              | OHE                            | (c <sub>A</sub> comer) | 175 Hx<br>(0.1 µF<br>corner) | 2 kHz<br>(l <sub>N</sub><br>corner) | 15.9kHz<br>(C <sub>i</sub><br>comer) | 139 kHz<br>(C,<br>comer) | I MHz<br>(AD241<br>comer) |

| c <sub>A</sub>   | 1<br>10<br>100<br>175<br>2 k +       | 220 nV/VIII<br>71<br>.32<br>.26<br>.20        | 2.4                            | 0.33                   | 0.29                         | 0.21                                | 0.2                                  | 0.02                     | 0.01                      |

| i <sub>N-</sub>  | 1<br>10<br>100<br>175<br>2k<br>10k + | 22 pAVR2<br>7,1<br>2.3<br>1.8<br>0.71<br>0.55 | 2.2                            | 0.23                   | 0.19                         | 0.071                               | 0.033                                | 0.0033                   | 0.0009                    |

| i <sub>N</sub> , | Same as for i <sub>N</sub> _         |                                               | 2.2                            | 0.23                   | 0,19                         | 0.006                               | -                                    | -                        | -                         |

| R,               | Broadband                            | (2.2 nV/√)1x                                  | 0,134                          | 0.134                  | 0.134                        | 0.012                               | -                                    | -                        | -                         |

| R,               | Broadband                            | 1.19 pA√Hz                                    | 0.129                          | 0.119                  | 0.129                        | 0.129                               | 0,129                                | 0.013                    | 0.002                     |

| R,               | Breadband                            | 41 nV/√Hz                                     | 0.041                          | 0.041                  | 0.041                        | 0,041                               | 0.041                                | 0.004                    | -                         |

Figure 10. Output voltage contributions of noise sources in the circuit of Figure 9 and combined noise spectral-density.

The rms noise can be approximated in 3 "brick-wall" regions: 1/f, from below 1 Hz to about 400 Hz (extrapolated corner), with K =  $3.9~\mu\text{V}/\sqrt{\text{Hz}}$ , white noise with  $e_n = 250~\text{nV}/\sqrt{\text{Hz}}$ , from that point to the 15.9 kHz rolloff, and white noise at  $20~\text{nV}/\sqrt{\text{Hz}}$ , from about 159 kHz to the 1-MHz amplifier rolloff. The contributions and sum, referred to output and signal input, are:

|                                                          |   | R.T.O.       | R.T.I.     |

|----------------------------------------------------------|---|--------------|------------|

| 1/1 noise (400Hz down to 0.1 Hz):3.9\(\sqrt{\ln(4000)}\) | = | 11 μV rms    | 1.1 µV cms |

| Wideband noise (to 15.9 kHz and including the            |   |              |            |

| skirt from (5.9 kHz)):0.25 $\sqrt{15.9}$ kHz × 1.25      | = | 39 μV rms    | 3.9 μV ems |

| Total noise in passband:                                 |   | 41 µV rms    | 4.1 μV cms |

| H-Four-of-band noise from 159 kHz to 1 MHz and           |   |              |            |

| including the NEB of the 1-MHz skirt:                    |   |              |            |

| $0.02\sqrt{(1.57 \times 1 - 0.159)MHz}$                  | = | 24 μV cms    | 2.4 μV rms |

| Total rms noise:                                         |   | 78 µV rms بر | 4.8 μV rms |

#### **NOISE TESTING**

In order for users to predict that an amplifier will be sufficiently quiet for a given application, with a guarantee that goes beyond the "typical" curves given in the data sheet, the manufacturer must guarantee a set of maximum noise specifications. Here is an example, the specifications of noise for the AD OP-07:

| Band                   | Typical | Maximum | Units  | Remarks                                                                |

|------------------------|---------|---------|--------|------------------------------------------------------------------------|

| 0.1 Hz-10 Hz           | 0.35    | 0.6     | μ∨ p-p | Voltage noise V spectral density V spectral density V spectral density |

| $f_0 = 10$ Hz          | 10.3    | 18.0    | n∨/√Hz |                                                                        |

| $f_0 = 100$ Hz         | 10.0    | 13.0    | n∨/√Hz |                                                                        |

| $f_0 = 1$ kHz          | 9.6     | 11.0    | n∨/√Hz |                                                                        |

| 0.1 Hz-10 Hz           | 14      | 30      | pΑ ρ·p | Current noise I spectral density I spectral density I spectral density |

| $f_0 = 10 \text{ Hz}$  | 0.32    | 0.80    | pΑ/√Hz |                                                                        |

| $f_0 = 100 \text{ Hz}$ | 0.14    | 0.23    | pΑ/√Hz |                                                                        |

| $f_0 = 1 \text{ kHz}$  | 0.12    | 0.17    | pΑ/√Hz |                                                                        |

Noise is usually specified in this way, peak-to-peak at low frequency and either spectral density or band-limited rms noise at higher frequencies. The manufacturer further specifies whether these specs have been 100% tested in production or on a sampling basis. Whether the noise is tested in characterization, in production, or by the user to verify noise performance of an incoming lot of devices, the test definition and circuitry should be standardized.

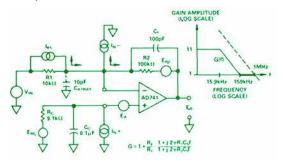

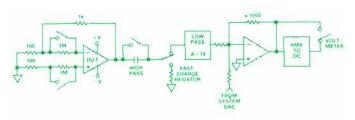

Figure 11 shows a typical test scheme, and the measurement circuitry employed. The device under test (DUT) is connected for a noise gain of (say) 10. A pair of 1-megohm resistors in series with the input terminals permit current noise to be measured, and a pair of shorting switches permit voltage noise and the current noise at either input to be measured individually. The output of the DUT is applied to a bandpass filter with a further gain of 10; the high-pass makes the noise measurement independent of the DUT's de offset. The low-pass filter is a two-pole Butterworth. With the high-pass, the filter is programmable for 7 different frequency bands. Measurements are performed by either the rms-to-de converter or the system voltmeter (for discrete sampling).

Figure 11. Noise-test circuit for op amps.

The bandpass filter has a noise effective bandwidth (N.E.B.) comparable to the band in question, e.g., 10 to 1000 Hz. The test system must take into account the DUT's reduction of bandwidth with increased gain, if it is a factor in the measurement. A wideband true-rms voltmeter measures the output of the filter and either interprets it directly as rms noise in the band, or calculates noise spectral density. At lower frequencies, the output is sampled, and calculations are performed to determine the rms, the peak-to-peak amplitude, and the presence of popcorn noise.

Both white noise and 1/f noise are random and have benign statistics. However, popcorn noise with sufficient amplitude to be readily detectable is of concern because it is an indicator of defective processing. Also, its "burst" nature (over periods from microseconds to seconds) is particularly annoying in many applications. When looked at with an oscilloscope, it is readily visible as a shift between levels (Figure 2c). How does a computer determine within a short time if substantial popcorn noise is present?

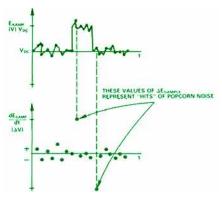

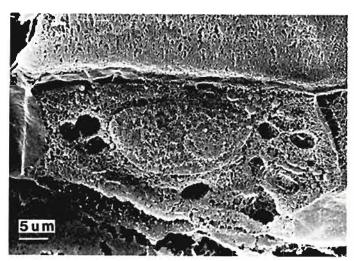

In one easy-to-automate approach, the criterion used to identify popcorn noise is: for successively sampled values of the output of the DUT and filter, are there any differences (jumps) that exceed  $4 \times \text{rms}$  (4  $\sigma$ )? If so, these jumps, which have a probability of less than 0.01%, are taken to be "hits" of popcorn-noise (Figure 12).

#### NOISE TESTING WITH THE LTS-2000 FAMILY

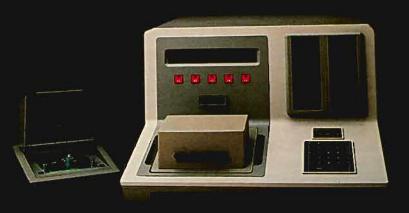

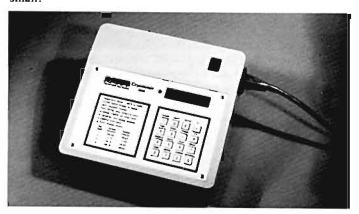

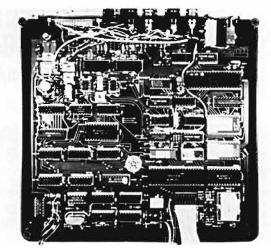

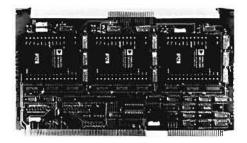

The LTS-2000 family of device testers are powerful low-cost computer-based self-contained benchtop test systems that can test a wide gamut of linear, digital, active, and passive devices, including amplifiers, d/a and a/d converters, digital logic ICs, discrete semiconductors, and passive components. Calibration is automatic and tests are performed quickly and automatically in accordance with either menu-driven or BASIC-programmed software pro-

Figure 12. Examining the sampled signal for popcorn noise by differencing.

grams. Documentation is available as pass/fail, quantitative, and statistical information.

Flexible hardware, as well as software, programs the system for testing specific devices. Plug-in family boards provide the rapid-change circuitry essential to testing such families as DACs, ADCs, amplifiers, etc. Circuitry for performing general- or special-purpose tests (such as noise) is wired to a device-test socket assembly, which plugs into the family board. Devices under test are plugged into test-socket cards, which are wired for specific devices and plugged into the socket assembly.

The LTS-0613 Noise-Test Socket Assembly (soon to be announced\*), in conjunction with the op-amp family board, enables users of the LTS-2000 family to perform noise testing on op amps—a capability available for the first time in benchtop ATE.

When used in conjunction with the LTS-2100 Op-Amp Family Board, the LTS-0613 tests noise, as well as the full range of parameter tests that the LTS-0600 Op-Amp Socket Assembly has been providing, for single, dual, and quad packages. It permits measurement of noise spectral density and peak-to-peak values for both voltage and current noise over a range of seven different bandwidths; the associated software also provides a routine for detecting popcorn noise.

The LTS-0613's circuit is quite similar to the block diagram of Figure 12, and—in fact—performance of the tests is similar to the technique described above. Automatic switching is available to choose among the four op amps in a quad. The high-pass filter, which serves the function of blocking any DUT offsets, can be initially switched—prior to testing—to have low values of resistance so that the blocking capacitor can be rapidly charged; without it, the wait for the circuit to settle before performing tests at the low end (0.1 to 10 Hz) would greatly reduce the speed of testing.

The DUT is wired for a gain of 10, a compromise that allows its noise to be amplified to a level significantly higher than that of the filter and gain stages, while retaining as large a bandwidth as possible for measurement of noise in the higher-frequency bands. Gain is also taken in the filter, which employs low-noise amplifiers, and in a pair of post-filter amplifiers. The overall gain from the DUT input is 100,000 V/V.

Relay-switchable filter time constants permit tests over the following bands: 0.1 to 10 Hz; 0.1 to 100 Hz; 1 to 100 Hz; 1 Hz to 1 kHz; 10 Hz to 1 kHz; 10 Hz to 10 kHz; and 100 Hz to 10 kHz. Output to the system is software-switchable between an analog true-tms circuit, for wideband measurements, and individual sam-\*For technical data, use the reply card.

ples, for the low frequencies. Sampling permits both accurate low-frequency rms computations and examination for popcorn hits.

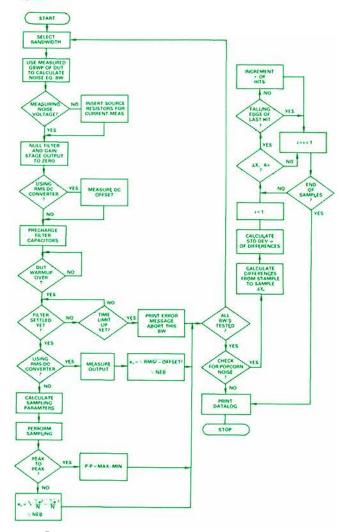

The software is set up as a subroutine to be called from the user's BASIC test program. All variables (such as test limits, bandwidths, choice of voltage noise, current noise, or both) are listed in documentation that accompanies the socket assembly. The user simply establishes the appropriate variables in the test program and then calls the subroutine. The flow chart in Figure 13 is a diagram of the subroutine's procedure.

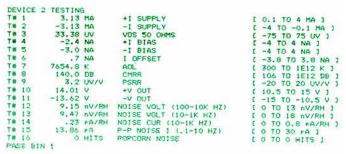

When the testing has been completed, the system prints the results in a form similar to the datalog shown in Figure 14, which depicts the test results (vs. limits) of 16 critical parameters for an AD OP-07E.

Figure 13. The LTS-0613 noise-test subroutine.

Figure 14. Data-log of test results on OP-07E, employing the LTS-0613. Columns are test number, actual measurement, description, and pass limits.

## SECOND-GENERATION MONOLITHIC RMS-TO-DC CONVERTER

AD637 Combines High Accuracy, Wide Bandwidth, and Versatility Twice the Bandwidth and Less than Half the Nonlinearity of the AD536A

by Lew Counts and Charles Kitchin

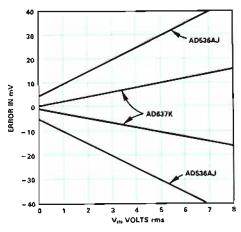

In 1977, the industry's first monolithic rms-to-dc converter, the Analog Devices AD536, was introduced in this Journal (11-2). It was one of the earliest IC products to have its performance enhanced by laser trimming at the wafer level. Since then, an improved version, the AD536A, and a low-level version, the AD636 (both based on the same design) have been introduced. In these pages, we introduce a second-generation descendant of the AD536, a device with greatly improved accuracy and much higher bandwidth at low levels as well as some interesting features that permit it to be used as a multifunction component.

The AD637\* is a monolithic rms-to-dc converter in a 14-pin DIP. It accepts waveforms of any shape, including dc, and produces an output which is proportional to the input's rms value. Its improved performance includes both high accuracy at all input levels, with nonlinearity less than 0.02% of full scale over its entire 0 to 7-volt input range, and wide bandwidths—up to 8 MHz for 2-volt-rms input signals. A logarithmic output is also available for applications that require a decibel interpretation of the output signal.

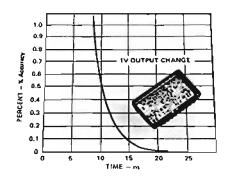

Figure 1 is a plot of worst-case error vs. rms voltage level for input levels from 0 to 8 V rms. Besides showing how low the errors can be with no external trim of the AD637, it also illustrates the extent of optional accuracies available following the introduction of the AD637, from the lowest-error AD637K to the lowest-cost AD536AJH. Errors can be reduced even further by external trimming of the AD637's scale factor and offset.

Figure 1. Error of rms devices as a function of rms amplitude.

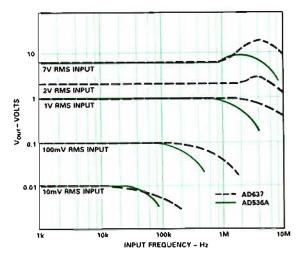

Figure 2 shows frequency responses typical of the AD637 (dashes) compared with those of the AD536A (solid) at various rms input levels. It should be apparent that the AD637's bandwidth is about twice that of the AD536A at all levels and is greater than 100 kHz at low levels (e.g., 10 mV rms).

In addition to performance improvements, the denominator feed-back—which was connected internally in the AD536A—has been

Figure 2. Bandwidth of the AD637 compared with the AD536A.

"unbundled" in the AD637 for greater versatility and increased design freedom in applications. The AD637 can be readily connected to compute:

•The square and mean-square of the input signal

•The vector sum or the sum of the squares of two or more independent time-varying voltages using two or more AD637s connected together.

•The root-mean-square of very slowly varying (less than 1 Hz) input signals.

#### A BRIEF REVIEW OF RMS

RMS, or root mean-square, is a fundamental way of summarizing and measuring an ac signal's magnitude. It has meanings that are relevant from both the mathematical and the practical physical point of view.

In the physical sense, the rms voltage or current value assigned to an ac signal is the same as the dc voltage or current that would be required to generate an equivalent amount of heat in the same resistive load. For example, an ac signal of 1 volt rms—irrespective of waveshape—will produce the same amount of heat in a resistor as a 1-volt dc signal. It doesn't matter whether the ac voltage is a pure sine wave with a peak amplitude of  $\sqrt{2}$  volts, a symmetrical square wave of  $\pm$  1-volt amplitude, or a zero-average noise voltage with undefinable peak amplitude. The rms voltage is defined as

$$V_{RMS} = \sqrt{average(V^2)}$$

(1)

where V is the set of all consecutive discernible "instantaneous" values of voltage in the averaging interval.

The rms value of an ac-coupled waveform is of especial value when random noise and vibrations are measured. The reason is that the rms value of a waveform is identical to the standard deviation of that signal. The relationship is independent of signal type; for

<sup>\*</sup>For technical data, use the reply card.

noise, rms equals the standard deviation, whether the noise is gaussian or has some other type of distribution.

For an analog device that computes rms, the bandwidth must be sufficient to deal with the input signal's "instantaneous" values; in addition, the averaging time must be sufficiently long to allow adequate filtering at the lowest frequencies of operation desired. Since the averaging time-constant in effect sets the time during which the device "holds" the input signal during computation, its value directly affects the low-frequency accuracy of an rms measurement.

#### A WORD ON RMS CONVERTER DESIGN

There are two popular approaches to designing analog true-rms circuits, thermal and computational. The most typical thermal approach is to allow the input signal to heat a resistor, then cause a feedback loop to adjust the temperature of a similar resistor by sensing the temperature difference while continuously adjusting the dc voltage across the second resistor to keep the temperatures equal; at equilibrium, the dc voltage across the second resistor is equal to the rms voltage across the first resistor. While this approach can result in very accurate, wideband designs, the resulting circuitry tends to be both expensive and power-hungry.

Computational rms-to-dc converters perform rms computations directly by squaring the input signal, averaging it, and computing the square root. This can, of course, be done digitally, either online or off-line. However, digital computation of rms requires considerable commitment of equipment, software, and computing time, especially if the rms is required continuously in real time for wideband signals. On the other hand, the rms can be computed in real time while the signal is in analog form, with predictable accuracy, using a single monolithic chip and minimal external circuitry.

It is tempting to consider explicit computation, in which circuits that perform the squaring, averaging, and rooting operations are cascaded in sequence. But this is not the best method, because the squaring operation doubles the number of decibels of dynamic range during the computation; for example, if the signal range is from 2 volts to 100 millivolts (26 dB), the voltage after the squaring circuit would range from 4 volts to 10 millivolts (52 dB). For this reason, the AD637, like most modern rms converters, uses an implicit computational approach combining logarithmic computation and feedback circuitry; signals with extra-wide dynamic range do not appear explicitly in the computation. The result is an rms device with about 60 dB of dynamic range (7V rms to 7 mV rms).

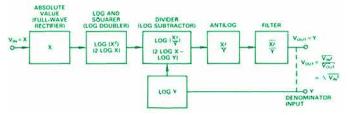

Figure 3 demonstrates the principle employed in the AD637 and other rms devices manufactured by Analog Devices. First, the signal is accurately full-wave rectified (without filtering) in the absolute-value section. Next, the device computes the logarithm of the resulting absolute-value signal and doubles it, producing, in effect, the square of the input signal (i.e.,  $2 \log X = \log (X^2)$ ); from it, the log of the output signal is then subtracted, performing a divi-

Figure 3. Implicit logarithmic rms computation.

sion (i.e.,  $\log (X^2) - \log Y = \log (X^2/Y)$ ). The inverse of the logarithm (i.e.,  $X^2/Y$ ) is computed by an exponential operation; and the result, after averaging by a low-pass filter, becomes the output signal (i.e.,  $Y = \text{average}(X^2/Y)$ ). The output is fed back; its logarithm is computed and fed to the subtraction stage, resulting in division by the output. If X is equal to  $V_{\text{in}}$  and Y is equal to  $V_{\text{out}}$  then, since the loop enforces the condition,

$$V_{out} = average \left( \frac{V_{in}^2}{V_{out}} \right)$$

(2)

and assuming that  $V_{out}$  is essentially constant in relation to  $(V_{in})^2$  due to adequate low-pass filtering:

$$V_{out} = \sqrt{average(V_{in})^2}$$

(3)

Thus, the relationship is enforced by feedback; division by the output results in the computation of the square root.

In the actual implementation, voltages are converted to currents, with all of the logarithmic operations taking place in a tightly knit central core (more like that depicted in Figure 4, rather than in the neatly delineated separate sections of Figure 3). While the AD637's core is similar to that of the AD536 (Dialogue 11-2), a much-improved crest-factor compensation scheme is employed to permit operation at significantly higher current densities while achieving smaller errors than those of the AD536A. An 11% duty cycle (or crest factor of 3) adds only 0.1% to the sine-wave error, and for a crest factor of 10 (1% duty cycle), the error is increased by only 1%. The reduced crest-factor error is of particular importance when complex waveforms, such as those occurring in switching-type power supplies, are being processed.

#### FEATURES OF THE AD637

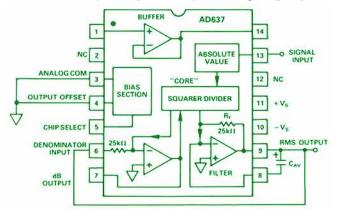

Figure 4 is a combined block diagram and connection diagram of the AD637. The signal, via pin 13, is seen going through the absolute-value, squarer/divider, and current-to-voltage output-amplifier stages, finally arriving at the output (pin 9). The filter amplifier (key to the improved linearity) converts the core's output current to a buffered output voltage which can drive load currents of up to 5 mA directly. An external capacitor,  $C_{AV}$ , is connected across the amplifier's 25 k $\Omega$  (nominal) internal feedback resistor,  $R_F$ . The averaging time constant,  $C_{AV}$   $R_F$ , is independent of signal level, an improvement over the AD536A. In the standard rms connection, the feedback path is completed via the denominator input voltage-to-current converter at pin 6.

Apart from the basic rms-to-dc function, there are several other features of interest. Although the device is laser-trimmed on the wafer to an offset of less than 0.5 mV, it has a provision for external offset trim for user fine-tuning. A chip-select terminal (pin 5) provides for powering down the chip, reducing the power-supply drain from 3 mA max (about twice that of the AD536A) to 450 µA max when invoked; it is a useful feature for energy conservation in battery operation and for multiplexing a number of measurement channels performing rms-to-dc conversion.

Another useful feature is the internal buffer, an uncommitted unity-gain non-inverting amplifier, accessible via pins 1 and 14. It is helpful in various ways—for example, providing additional filtering or buffering the dB output (pin 7).

Device bandwidth has been raised by increasing the signal current in the absolute-value stage and by the use of a high-speed process in manufacture; the result is a useful bandwidth of up to 8 MHz (at 2-V rms input)—a substantial improvement over the AD536A, as Figure 2 shows.

#### APPLICATIONS

Standard RMS Connection. Only one external component, C<sub>AV</sub>, is needed for complete high-accuracy rms computing (Figure 4).

Figure 4. Block diagram and pin connections of the AD637.

The maximum error for input voltages from 0 to 7 V rms will be 0.5 mV  $\pm$  0.2% of reading, at mid-band audio frequencies. The internal buffer amplifier, not used here, is freed for other tasks. For a range of low frequencies, the finite averaging time of the converter will produce an additional error, principally ripple, varying inversely with signal frequency and averaging time-constant:

% peak ripple =

$$\frac{50}{\sqrt{1+40\tau^2f^2}}$$

(4)

in % of the rms level;  $\tau = R_i C_{AV}$  and f is signal frequency in hertz.

If  $C_{AV}=1~\mu F$ , peak ripple with a 380-Hz sine wave will be about 1% of reading. The error will be reduced in proportion to increased  $C_{AV}$ , but response time to signal amplitude changes increases proportionally. A better solution is to reduce the ripple by following the AD637 with a low-pass filter; suitable filters (which can use the on-chip buffer) are described on the AD637 data sheet.

The AD637 will compute the root sum-of-squares of an ac input signal that has a dc component. To measure the ac component only, the signal may be coupled to the AD637 by insertion of a capacitor in series with the input terminal. A 1-µF capacitor will produce a -3-dB frequency of about 20 Hz; for lower frequencies, use tantalum capacitors with 20-V ratings connected back-to-back in series.

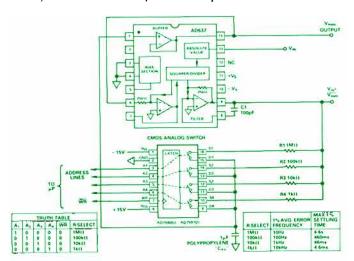

μP-Controlled Averaging/Settling Time-Constant. Figure 5 shows one example of the benefits realizable from a denominator input that can be connected externally. In this circuit, a digitally controllable switch permits a choice among 4 averaging/settling time constants.

For low frequencies, such as 10 Hz, an external filter with a 1-second time constant—for settling to within 1% of final value in 4.6 seconds—should have a sufficiently long time constant for low error. However, at higher frequencies, e.g., 10 kHz—or for inputs which have most of their energy at higher frequencies—it would be useful to switch the time constant quickly and automatically to a much smaller value, such as 1 ms, with settling time of 4.6 ms.

<sup>1</sup> A more-thorough discussion of averaging errors—and a wealth of additional useful information—can be found in the 56-page RMS-to-DC Application Guide, available free upon request (see page 30).

This would permit readings in that frequency range with a minimum of delay.

In the circuit of Figure 5, one of 4 time constants—1 ms, 10 ms, 100 ms, and 1 s—is established by switching an appropriate resistor between the AD637's output and a 1-µF filtering capacitor, to form an external single-pole filter buffered by the on-chip follower, inside the AD637's feedback loop.

Figure 5. RMS converter with digitally controlled averaging/ settling time, independent of signal amplitude.

The time constant, controlled by digital logic, can be switched by a microprocessor. The  $\mu P$  must have a means of determining the frequency content of the signal, and it must be programmed to decide which time constant to use.

The values shown here, and the 10:1 relationships between them, were chosen just as an example. Different values of time constants, and different incremental relationships between them (for example, linear or logarithmic) may be selected to fit your application. The upper limit on resistance is established by the 1-nA bias current of the AD637's internal buffer follower; in this example, resistance was limited to 1 megohm to keep the offset below 1 mV. For longer time constants, use more capacitance; for shorter time constants use less resistance.

One caution: this circuit may saturate (without damage) on transient spikes as a consequence of the very low value of feedback capacitance ( $C_1 = 100 \text{ pF}$ ) around the internal amplifier. In this case, the effective  $C_{AV}$  is the capacitor in the filter; the 100-pF capacitor is there solely for stability. Since  $C_1$  entails minimal filtering, the output voltage, at pin 9, responds to the instantaneous square of the input rather than the mean square. The resulting higher crest factors can be handled by increasing  $C_1$  by a factor of 100 or more, as long as the feedback circuit's time constant is kept substantially less than that of the switched time constants to minimize additional time delays.

There are many other possible applications that can profitably use the fast, precise, versatile AD637, for example, controlled squaring and mean-square measurements. While the above example shows  $\mu$ P-controlled switching of filter time constants, the clever designer may wish to consider auto-adaptive possibilities employing all-analog circuitry. With the accessible denominator input, the internal voltage buffer, the log output, and the power-down feature, many exciting new configurations—as yet unknown—await the creative designer's imagination.

## FAST, SIMPLE APPROXIMATION OF FUNCTIONS

## Use A Lookup Table And a Digital Multiplier To Implement Newton-Raphson Approximations

by Matt Johnson

Now that low-cost, low-power digital multipliers and multiplier/ accumulators are readily available (for example, ADI's ADSP-1000 device-family\*) it has become possible to implement many digital signal-processing (DSP) applications with high speed. The most common applications are in performing fast Fourier transforms (FFT) or filtering incoming data from either a real-time source or from stored data off-line. However, their utility is not limited to such conventional applications. DSP components can be used, along with applied mathematical convergence theory, to embody algorithms for evaluating scientific functions at high speed.

When exact solutions are not required, approximation techniques—employing parallel computation using hard-wired components—allow us to bypass the long calculation times normally required by CPUs in evaluating scientific functions. Depending on the specific function and the accuracy of the desired solution, the execution time required by a CPU to effect solutions—using its built-in algorithms—can be bettered by as much as two orders of magnitude. For example, a 16-bit 8086 divide takes some 30 microseconds, compared to about 300 ns for the implementation to be described here, using an 8-bit lookup table and a hardware multiplier. Such increased performance can mean the difference between a successful design and a merely interesting one that never gets off the ground.

As an example of the technique, we show how one might implement an approximation of a common function occurring frequently in signal processing systems, the reciprocal (y = 1/x). A fast reciprocal is just one multiplication away from a full-blown fast divider, but redundant architectures do exist for implementing the complete division without the extra multiply cycle. We will examine both the theoretical implications and hardware realizations of the technique.

#### **NEWTON-RAPHSON**

We will apply the Newton-Raphson recursion algorithm, which is well known to users of mathematical approximation techniques. It is a very powerful algorithm because it produces quadratic convergence (i.e., each iteration provides a doubling of precision). To begin, a guess is made as to the root of the function (solution for

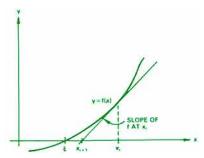

Figure 1. Well-behaved convergence using Newton-Raphson. The first guess is  $x_i$ , the second is  $x_{i+1}$ .

an unknown value) in the vicinity of the desired root. The derivative (slope) of the function is evaluated at the guessed value, leading in turn to new, successively closer iterations (Figure 1). The method may be applied to approximate any "well-behaved" function, i.e., a function not exhibiting zero derivatives within the region where the function is expected to converge.

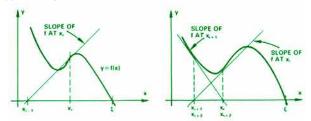

The significance of "well-behaved" is apparent in the following cases. Figure 1 traces the algorithm as it converges through two iterations towards a root,  $\xi$ , of a monotonic function. As the plot shows, the guess for the *i*th iteration was  $x_i$ ; the slope is determined at  $x_i$ , and the point where it intersects the x-axis is the new guess,  $x_{i+1}$ . Notice how successive solutions converge quickly. Figure 2, on the other hand, illustrates two examples in which a naughty function (having zero derivatives) prevents convergence. Fortunately, the reciprocal is well-behaved for all values of  $x \neq 0$ .

Figure 2. No convergence with zero-derivative functions.

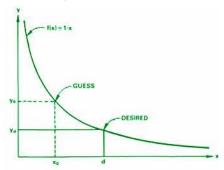

Figure 3. Functional relationship, f(x) = 1/x.

The Newton-Raphson recursion is derived using a first-order Taylor series expansion in the following manner (figure 3). Assume we wish to find the reciprocal of a value of x we will call d (thus,  $y_d = 1/d$ ), knowing only the functional dependence, f(x) = 1/x, and the value of y at an arbitrary point,  $x_0$ :  $f(x_0) = y_0$ . We define an error function, F(y) = 1/y - d, whose root occurs at  $F(y_d)$ , i.e.,

$$F(y_d) = 1/y_d - d \ (= 0)$$

(1)

When it is solved for y, we will have the desired value of the reciprocal at d,  $y_d$ .

We write a first-order Taylor series expansion of this error function about the point,  $y_d$ , giving us a linear approximation to the desired solution. Hence we have, for the *n*th iteration,  $y_n$ ,

<sup>\*</sup>Use the reply card for technical data.

$$F(y_d) \simeq F(y_n) + (y_d - y_n)F'(y_n)$$

(2)

Equating this expansion to zero (to minimize the error) and generalizing  $y_d$  as  $y_{n+1}$  (the improved guess), equation 2 becomes:

$$0 = F(y_n) + (y_{n+1} - y_n)F'(y_n)$$

(3)

Solving (3) for the value of  $y_{n+1}$  (which we are seeking),

$$y_{n+1} = y_n - F(y_n)/F'(y_n)$$

(4)

This is the general form of the Newton-Raphson recursion. For the specific case of the reciprocal, we substitute the error function (from equation (1)) and its derivative  $(F'(y_n) = -1/(y_n)^2)$ :

$$y_{n+1} = y_n + y_n^2 (1/y_n - d)$$

=  $y_n (2 - d * y_n)$  (5)

#### **PREPARATIONS**

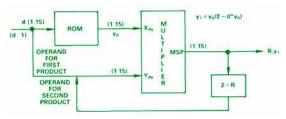

How do we make our first guess,  $y_0$ , to start the Newton-Raphson iteration? The most effective way is to address a lookup table (ROM), having a relatively small number of fixed points, with a nearby value of x. Although the hardware could be simplified (eliminating ROM and associated circuitry) by always starting at a fixed arbitrary value, we would find that it is a somewhat inefficient approach, because the resulting higher initial error leads to more iterations than we want (albeit still faster than an exact solution executed by a CPU).

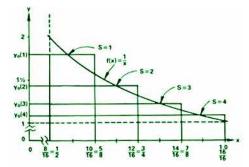

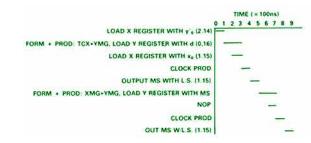

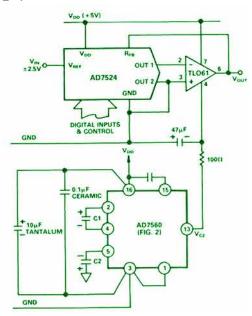

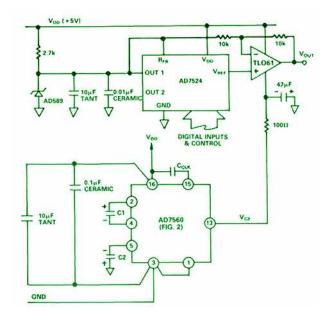

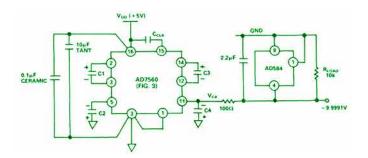

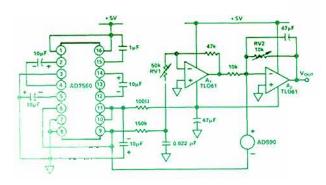

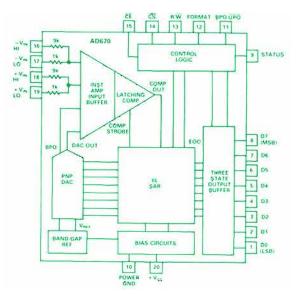

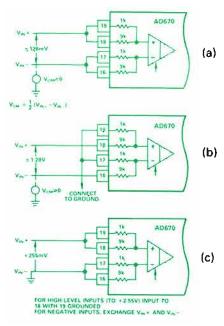

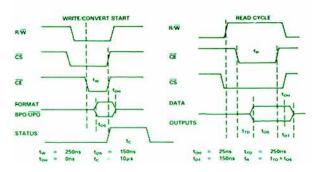

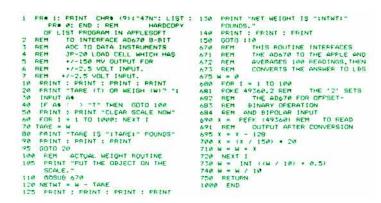

When lookup tables and finite-precision hardware are used, an important aspect of approximation techniques is data normalization. We would like to match the full operating range of a device to the full range of the function. In the interest of restricting the range of the function's argument to fully utilize the limited precision of hardware multipliers (or conversely, to maximize the dynamic range of the result), it is common practice to shift the argument (viz., successively multiply or divide by 2) until it is in the range within which a sufficiently correct answer can be obtained most efficiently. After the approximation technique has been applied, the result is denormalized (i.e., restored to its appropriate range).