## analog dialogue

A forum for the exchange of circuit technology: Analog and Digital, Monolithic and Discrete

13-BIT MONOLITHIC CMOS A/D CONVERTER (page 3)

Also in this issue:

Monolithic Sample-Hold Amplifiers

FET-Input IC Electrometers

Full contents on page 3

### Editor's Notes

#### **DECENNIAL**

Our first ten years in business having been weathered, it is perhaps appropriate to assess the late decade, one in which Analog Devices has appeared on the scene, survived, and prospered. As is our wont, as well as our charter, we shall hew here to

technical matters; readers seeking further enlightenment on our business as a whole – present, prospective, and retrospective – are invited to request copies of the 1975 Annual Report, the President's message at our Annual Meeting, and the not-unpleasant tidings in the 1976 first-quarter Report.

For this ith recital of our history, we hope for the indulgence of our faithful readers on the ground — established by our recent survey — that perhaps one-half of our present readers have been with us for two years or less.

For the first third of the decade, our activities were fully consonant with our corporate name — we developed and produced high-performance modular operational amplifiers of all descriptions: FET-input, chopper, high-speed, parametric — and taught users how to apply them to best advantage. Despite the parallel growth of commodity IC's, our amplifier activities succeeded, because our amplifiers, backed in depth by applications information, helped solve user problems, aided and abetted by other Analog modules: multipliers, logarithmic devices, instrumentation amplifiers, and (the necessary) power supplies.

In the late sixties — the second third of our decade — we recognized that the destination of the information processed by our modules would increasingly be an interface with digital processing equipment. We also recognized that the cost and size advantages of IC's and hybrids would inevitably result in their encroachment upon (to begin with) the simple functions then available in modular form and would make possible more-complex modules, which would themselves be challenged, in an endless cycle reminiscent of the familiar picture of large fish cating smaller fish eating smaller fish, etc. — but in a reversed progression.

For A/D and D/A converters, the manifestation of progress was the replacement of breadbox-sized converters by modules of ever-increasing speed and accuracy and ever-decreasing size and cost. For analog functions, we established an integrated-circuit facility that initially concentrated on high-performance op amps, multipliers, and converter quad-switches.

In the final third of the decade, we articulated the mission of Analog Devices, the unifying underpinning of our technical activities — the key to both past and future. Succinctly stated, it is: to design and produce immovative electronic products that acquire, convert, condition, or display data for precision measurement and control.

In an explosion of progress, there appeared: digital panel meters, SERDEX (SERial Data-EXchange) products, and denier sensors and systems for the textile industry; low-cost modular converters, including V/f's; rms modules; high-performance multiplier-dividers and functional modules; microprocessor-

compatible IC A/D and D/A converters; precision resistor networks; and a host of other precision IC's: voltage references, instrumentation amplifiers, multiplier-dividers, and op amps.

The keys to our future lie in the statement of our mission and in a disposition and a competence to seek out and understand the user's problems and to provide him with helpful solutions.

In the first decade, the technologies we used resulted principally in products of small size that performed simple unit functions. While efforts in that product area will continue and intensify, the second decade will — almost from the outset — see the introduction of more-complex products of greater size and scope. A salient feature of the new system-oriented products will be their advanced software. Provided as an inherent necessity, it will make life easier for the user, in much the same way that ADI's traditional diversity and abundance of publications helped (and will continue to help) component users.

The first ten years were fun - but as nothing compared to the next ten!

Dan Sheingold

#### THE AUTHORS

Will Ritmanich (page 3), Applications Engineer at Analog Devices Microsystems, obtained his basic engineering background at Foothill College. Prior to joining ADI, he spent time in the U.S. Navy, then at National Semiconductor, Fairchild Semiconductor, and American Microsystems,

where he was responsible for product engineering and test engineering for various linear and MOS integrated-circuit products.

Dennis Langley (page 3) is Project Engineer at Analog Devices Microsystems and was responsible for development of the AD7550. Before joining ADI, Dennis designed modular conversion products for Cycon and Zeltex and was Product Engineer at Fairchild Semiconductor. He

has a B.S. from the University of Illinois and has completed course work for the M.S. degree at U.C. Berkeley.

(more Authors on page 18)

### analog dialogue

Route 1 Industrial Park, P.O. Box 280, Norwood, Mass. 02062

Published by Analog Devices, Inc., and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and display circuits. Correspondence is welcome and should be addressed to Editor, Analog Dialogue, P.O. Box 280, Norwood, Massachusetts, U.S.A. 02062. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577, Telex 924 491, or cable ANALOG NORWOOD MASS.

### 13-BIT MONOLITHIC CMOS A/D CONVERTER

## AD7550 Has 1ppm/°C Gain and Offset Sensitivities, 3-State Logic, Two's-Complement Output

by Will Ritmanich, Dennis Langley, and Ivar Wold

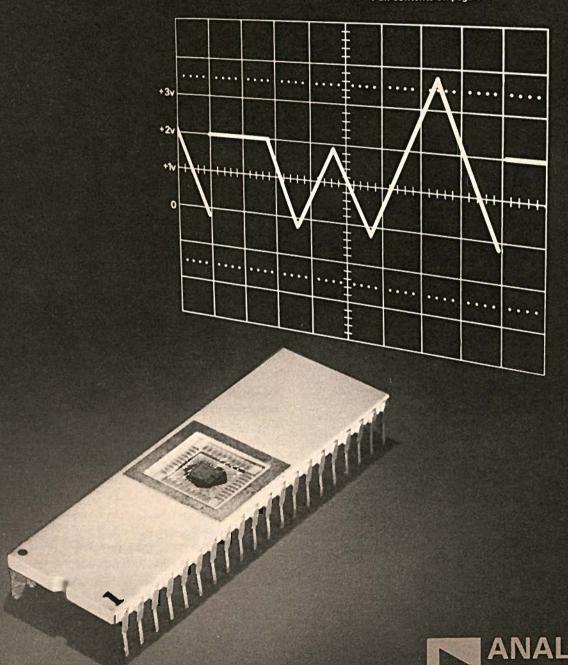

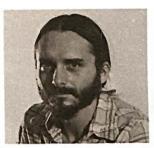

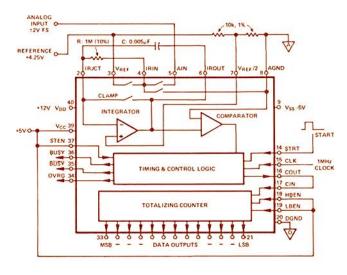

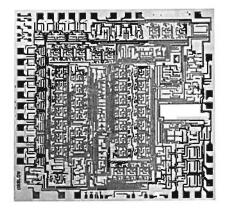

The AD7550\* is a 13-Bit A/D Converter on a single 3 x 3.2mm (118 x 125 mil) chip, enclosed in a 40-pin dual in-line package (Figure 1). It utilizes a totally-new "Quad-Slope" integration techniquet, which provides both autozeroing and low sensitivity to component error, supply variations, and temperature changes. It accepts analog inputs of either polarity; the output is available as either a train of pulses for external counting, or as a parallel 2's-complement word, divided into 5- and 8-bit bytes, and buffered by 3-state logic especially suited for microprocessor-controlled bus-oriented systems. The AD7550 interfaces directly with either TTL or CMOS logic.

Figure 1. Block diagram of the AD7550 A/D converter.

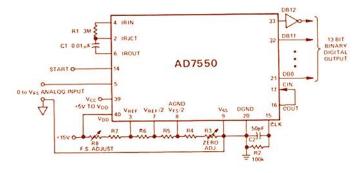

Requiring typically only 8mW total power ( $V_{DD} = 12V$ ,  $V_{SS} = 0$  to -5V, and  $V_{CC} = 5V$  up to  $V_{DD}$ ), and a single external positive reference, the AD7550 contains its own comparator, integrating amplifier, clock, control-, counting-, and buffer logic, and analog switches. Since the reference is applied externally, the AD7550 may be used for ratiometric conversion. The internal clock may be overriden by an external clock for applications in which an external clock is desirable. The only passive external components normally required are a resistive divider-pair for the reference and a resistor-capacitor pair for the integrator (Figure 2).

Because of the integrating technique used (see page 5), the digital output is monotonic, with no missing codes. The AD7550 will accurately digitize signals from up to slightly less than one-half the maximum reference down to levels limited only by the internal FET-input amplifier's ability to accurately integrate small microvolt-level signals without errors due to noise. Because the Quad-Slope integration technique accurately adjusts for offsets over the temperature range, the zero-drift and gain-temperature coefficients are less than 1ppm/°C maximum process.

\*Use the reply card to request complete information on the AD7550. IU.S. Patent 3,872,466

Figure 2. AD7550 connections for basic operation.

mum, at typical conversion speeds of 40Hz, with  $\pm \%$ LSB differential nonlinearity. The AD7550BD is priced at \$35 (1-49), \$25 in hundreds.

#### MICROPROCESSOR COMPATIBILITY

The AD7550 was specifically designed to be easy to use in data-bus systems, where its 3-state outputs are under external

IN THIS ISSUE

(continued on the next page)

| E SANUAL SERVICE DE LA COMPANION DE LA COMPANI |  |    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----|--|

| Volume 10, Number 1, 1976, 20 pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |    |  |

| Editor's Notes, Authors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  | 2  |  |

| 13-Bit Monolithic CMOS A/D Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | 3  |  |

| Monolithic Sample-Hold Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | 6  |  |

| Inductosyn-to-Digital Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | 8  |  |

| 10 Volt (±1mV) References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  | 10 |  |

| FET-Input IC Electrometers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | 11 |  |

| New Products:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |    |  |

| Low-Cost Chopper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | 12 |  |

| 6-Decade Log-Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |    |  |

| 100kHz V/f Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | 12 |  |

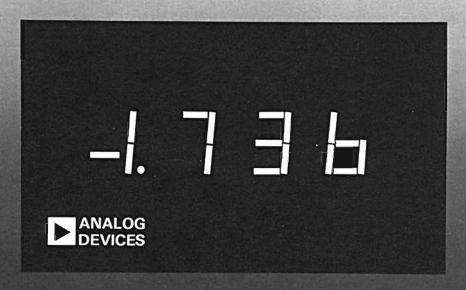

| Three More "2nd-Generation" DPM's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | 13 |  |

| Application Briefs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |    |  |

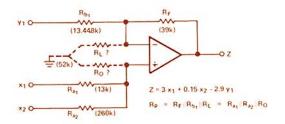

| Simple Rules for Choosing Resistor Values in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |    |  |

| Adder-Subtractor Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  | 14 |  |

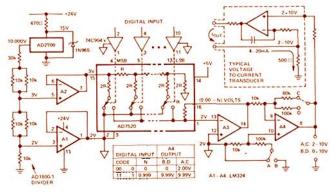

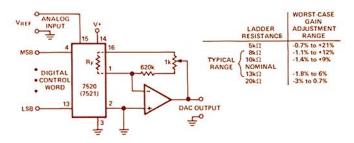

| DIA Conversion with Single-Supply Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  | 15 |  |

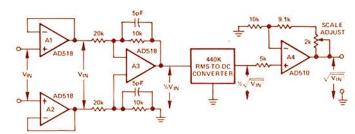

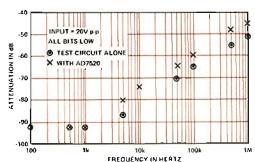

| Differential High-Impedance rms-to-dc Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | 15 |  |

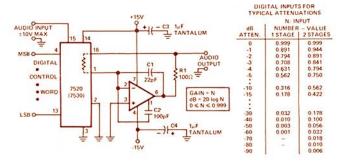

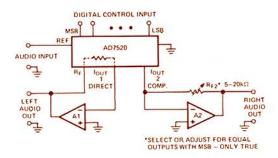

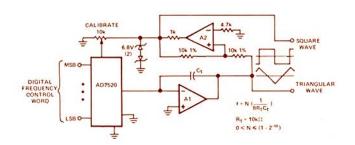

| Audio Application Ideas for CMOS DAC's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | 16 |  |

Potpourri: More Authors, HP-25 Resistance-Computation

Worth Reading: Book Review (Operational Amplifiers -Roberge), Last Issue of Analog Dialogue, Erratum . . . 19

Program for Adder-Subtractor Circuits, etc. . . . . . 18

Advertisement: Digital Panel Meters. . . . . Back Cover

control. In this respect, the timing-sequencing and data-bus connections are compatible with those of the earlier AD7570\* 10-bit successive-approximation A/D converter and the AD7522\* multiplying D/A converter.

- The positive-true parallel data outputs (bits 0-12), the overrange indication, and the conversion status lines (BUSY, BUSY) are 3-state and are isolated from the common data bus until appropriate interrogation signals are received (Data ready? High byte? Low byte?)

- The five most-significant bits (including the sign bit), the 8 least-significant bits, and the three status bits can be interrogated in separate bytes; all 13 bits can be furnished on an 8-bit common data-bus in 2 bytes.

- The serial-output pulse stream is brought out on a separate pin with regular (TTL or CMOS) logic levels; this permits the data to be manipulated before being clocked into the output buffers. The pulse train, COUT, is activated after the completion of the measurement cycle and has:

$$C_{OUT} = \left[\frac{2.125V_{IN}}{V_{REF}} +_1\right] (4096) counts$$

• If the control inputs are connected to the appropriate logic levels, the AD7550 will work as a conventional 13-bit parallel-binary A/D converter.

#### APPLICATIONS

The AD7550's forte lies in applications for which accuracy and lack of discontinuities (such as missed codes), especially over wide temperature ranges, are vastly more important than speed of conversion. The self-contained nature of the AD7550, its low power consumption, and its insensitivity to temperature and supply voltage make it ideal for use in compact, remote, battery-powered precision instrumentation, for example, in seismic or geological exploration. On the other hand, its special control features allow it to be readily employed in microprocessor-controlled data-acquisition systems where 13-bit accuracy, flexible polarity, and a noise-averaging capability are necessary and high speed isn't.

Panel-meter and digital-voltmeter applications, especially in conjunction with a requirement for binary data for system use, and where high accuracy at elevated temperatures is necessary, are also pregnant possibilities. The count-out/count-in feature permits the pulse count to be manipulated separately (for auxiliary BCD displays), or prior to being counted in the tristate-buffered counter (for example, by the use of binary rate-multipliers).

Figure 2 shows the basic circuit connection for binary operation. With all the data-output command inputs held high, as shown, parallel data will be present at the outputs. By selectively exercising the various command inputs, HBEN (High Byte ENable: 5 most-significant bits), LBEN (Low Byte ENable: 8 least-significant bits), and STEN (ST atus ENable: OVer Ran Ge, BUSY, BUSY), the desired data can be made available on an 8-bit data bus. The internal clock can be employed simply by replacing the 1MHz clock-input lead by a capacitor from the CL oc K terminal to ground. Similarly, repetitive auto-start can be gained by connecting a capacitor from the STaRT terminal to ground.

\*For information on these devices, use the reply card.

#### SINGLE-SUPPLY OPERATION

Figure 3 illustrates operation from a single +15V power supply. The AGND (A nalog G rou N D) terminal is biased to a positive voltage (relative to the converter power supply), which offsets the AD7550 transfer function. If the voltage at AGND is exactly one-half full-scale input (unipolar positive) and the reference is at 1.5625 the full-scale input, the negative full-scale input voltage is shifted to occur precisely at OV.

Figure 3. AD7550 single-supply operation (13-bit binary).

The adjustable resistors permit the zero and full-scale points to be fine-trimmed. Since drifts in the resistance ladder or the power-supply voltage directly affect the reference, they will directly affect the scale factor and the offset, but not the midscale point. Since the circuit provides unipolar 13-bit conversion, the normal 2's-complement code (used for bipolar conversion) is easily changed to straight binary by complementing DB12. The digital inputs and outputs are CMOS-compatible; although not shown, the control inputs should be ried to VCC. If the AD7550, used in this configuration with sensing transducers, shares their power supply, the ratiometric transfer characteristics of the AD7550 will tend to reject supply-voltage variations.

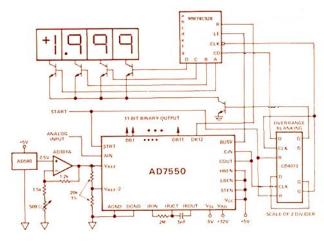

#### 3½-DIGIT DPM (0 TO +2V FULL SCALE)

Figure 4 shows a simple circuit to provide 3½-digit readout for positive input voltages. The number of output pulses is divided by 2, and the reference is scaled so that 1999 of the 2047 output pulses clock a National MM74C928 counterlatch-display through a 0 to +1.999V range.

An AD580\* 2.5V reference and an AD301AL\* op amp provide the reference voltage, adjustable by the  $500\Omega$  resistor.

Figure 4. 31/2-digit display application.

<sup>\*</sup>For information on these products, use the reply card.

Conversion begins when the STaRT command is initiated. When DB12 goes low, indicating a positive input, the MM74C928 starts its count, corresponding to the analog input voltage. After the last C<sub>OUT</sub> pulse, BUSY goes high and latches the display. The Carry output of the MM74C928 indicates overrange by toggling the CD4013 to blank the display for inputs ≥ 2.000V.

#### HOW THE QUAD-SLOPE CONVERTER WORKS

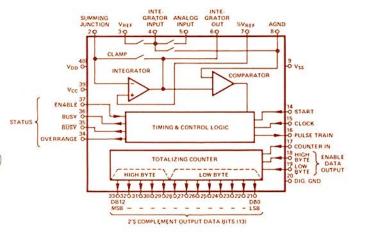

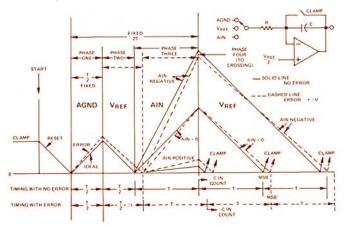

The quad-slope converter is an integrator-counter converter, related to the conventional dual-slope converter. However, it includes two additional integration phases for virtual cancellation of offset- and scale-factor errors. Its operation can be seen in Figure 5.

Figure 5. Illustration of quad-slope principle: integrator output waveforms for positive, negative, and zero input — with and without error.

The integrator has four modes of connection, determined by internally-controlled CMOS switch settings: Clamped (when no conversion is in process), Grounded input, Reference input, and Analog (signal) input. The positive input of the integrating amplifier is continuously connected to  $V_{REF}/2$ . When a conversion is initiated (phase "0"),  $V_{REF}$  is applied to the integrator input, providing a net positive voltage,  $V_{REF} - V_{REF}/2$ , across the integrator's input resistor, resulting in a negative-going ramp at the output. When the output is equal to the comparator trip-voltage, phase 1 is initiated.

Phase 1. The integrator input is connected to Analog Ground. Since the integrating resistor has a net negative voltage across it, equal to -V<sub>REF</sub>/2, plus any error, the output increases positively at a proportional rate. At the beginning of Phase 1, a counter starts counting clock pulses. When it has counted a number of pulses representing an interval, T/2, Phase 2 is initiated; the counter continues to count.

Phase 2. The integrator input is connected to the Reference. Since the voltage across the integrating resistor is  $+V_{REF}/2$ , plus any error, the output ramps down at a proportional rate. When the output reaches the comparator trip voltage, Phase 3 is initiated. If there were no error, the time for Phase 2 would be equal to T/2, the same as for Phase 1. Any error will increase or decrease the time to the trip point by an amount  $\Delta t$ . Note that the trip point is approached with the same slope and from the same direction as at the end of Phase 0 (and also the end of Phase 4), hence any comparator hysteresis errors and differential propagation delays are avoided.

Phase 3. The integrator input is connected to the Analog signal, which is positive or negative, and less than V<sub>REF</sub>/2 in magnitude. The net input to the integrator will always be negative and equal to A<sub>IN</sub> -V<sub>REF</sub>/2, plus any error. The output of the integrator will ramp upwards with a proportional slope. For large positive inputs, the output slope will be small; for large negative inputs, the output slope will be steep; and for zero input, the slope will be the same as in Phase 1. Phase 3 is terminated when the counter that started at the beginning of Phase 1 reaches a count corresponding to 2T.

Because Phases 1, 2, and 3 occupy a total period 2T, Phase 3 is lengthened or shortened by  $\Delta t$ , the same amount by which Phase 2 was shortened or lengthened. At the beginning of Phase 3, a second counter is started, counting down from zero\*; note that, with zero error, it starts at T exactly; but with an error, it starts at  $T \pm \Delta t$ .

Phase 4. The integrator input is again connected to the Reference, and it ramps down at the rate V<sub>REF</sub>/2, plus any error. Phase 4 ends when the integrator output reaches the trip point, after which the integrator is clamped and the second counter is stopped. Conversion is now complete, and the counter output is a 2's complement representation of the analog input.

Discussion. The data sheet describes the actual workings of the circuit in some detail and includes a derivation of the error equation. Here we will rely somewhat more on graphics and intuition to show that it actually works. In Figure 5, it can be seen that the time from the MSB crossing, corresponding to zero input, to the time of occurrence of the crossing corresponding to a positive or a negative input, is proportional to that input. The effect of an error is simply to shift all crossings by an equal amount of time,  $\Delta t$ .

If the counter's capacity is 2T, and if it counts down from all zero's at the beginning of Phase 3, then at the largest positive number, it will read 0 1111 1111 1111 (and will stop there if a crossing occurs), at zero it will read 0 0000 0000 0000, and at the largest negative number, it will read 1 0000 0000 0001, a range which will be recognized as belonging to a 2's-complement code.

In actual practice, in order to avoid negative integration and allow sufficient time after Phase 4 begins for offset correction and overrange indication, a somewhat different counting scheme is used, in association with an input full-scale range of  $V_{REF}/2.125$ , instead of  $V_{REF}/2$ .

\*The implementation discussed here is simplified for clarity.

### MONOLITHIC SAMPLE-HOLD AMPLIFIERS

### 2 New Devices Achieve 12-Bit Performance, Low Cost of AD582KH May End "Do-It-Yourself" Lashups

by Dave Kress and Dick Wagner

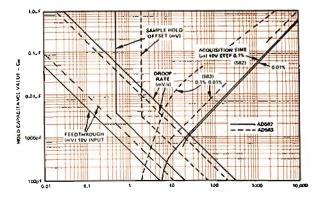

The AD582\* and AD583\* are two new monolithic integrated-circuit sample-hold amplifiers. Both are self-contained, except for the externally-connected hold capacitor, CH, which is chosen by the user for the best compromise between speed of acquisition-and-tracking, and error magnitudes in hold.

The AD583 provides extremely-fast acquisition (2 $\mu$ s to 0.1% with C<sub>H</sub> = 100pF, 10 $\mu$ s to 0.01% with 1000pF), low aperture time (50ns), and a fast 5V/ $\mu$ s slowing rate (C<sub>H</sub> = 1000pF). The AD582, while somewhat slower (6 $\mu$ s to 0.1% with 100pF, 25 $\mu$ s to 0.01% with 1000pF), is far less costly, \$5.95 in 100's, \$8.90 (1–24) for AD582KH, vs. \$14.85 in 100's, \$20.25 (1–24) for AD583KD.

Besides having lower cost, the AD582 is also capable of greater accuracy, with a maximum charge transfer of SpC (5mV at 1000pF), compared to 20pC (20mV at 1000pF) for the AD583, when switched from sample to hold. Minimum error with the optimum value of  $C_H$  is also considerably less:  $500\mu V$  at  $C_H = 3000pF$ , vs. 2mV with  $C_H = 5000pF$ .

Sample-holds are conventionally used in data-acquisition systems, either to "freeze" fast-moving signals during conversion, or to store multiplexer outputs while the signal is being converted and the multiplexer is seeking the next signal to be converted. In analog data-reduction, sample-holds may be used to determine peaks or valleys and to facilitate analog computations involving signals obtained at different instants of time. Other uses include automatic zero-correction systems and spike-noise eliminators ("deglitchers").†

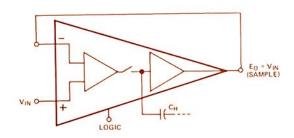

The AD582 and AD583 both have differential inputs: they both utilize high gain in a feedback loop for rapid tracking.

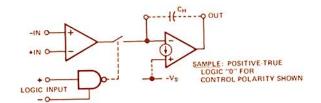

(a) AD582 has differential logic inputs, current switching, output integrator.

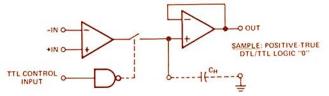

(b) AD583 has single-polarity logic, output follower.

Figure 1. Block diagrams of the AD582 and AD583.

However, there are several differences, as shown in Figure 1. The AD582's hold capacitor is connected as the feedback element of an integrator; the AD583's hold capacitor is unloaded by a unity-gain follower. While the AD583's control input accepts only positive-true 5V TTL, the differential control input of the AD582 permits easy interfacing to any standard logic family – TTL, DTL, 3-, 5-, or 15-volt CMOS, 15V HTL, with either positive- or negative-true sense. The AD583 has a lower output impedance in hold, for applications in which the load on the sample-hold amplifier is variable.

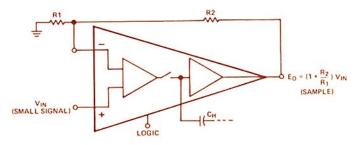

Both devices perform essentially as differential operational amplifiers with open-loop de gain of 25,000 in the sample (or track) mode; their dynamics depend on the value of C<sub>H</sub>. They can therefore be used either as high-impedance gain-of-one followers with normalized input signals, or to obtain single-ended or differential gain for low-level inputs (Figure 2). In

(a) Conventional unity-gain follower application.

(b) Follower with gain.

Figure 2. Basic sample-hold follower circuits.

<sup>\*</sup>For technical data on these devices, use the reply card. tConsiderable information on the nature and uses of sample-holds can be found in the Analog-Digital Conversion Handbook, available from Analog Devices @ \$3.95.

cither case, when a hold signal is applied to the control input, the output is ideally held at the last value until the device is returned to sample.

Sample-holds are by no means ideal devices, but they are sufficiently ideal for many applications. They can be best applied if the essential sources of error are commonly understood and are adequately characterized (and/or specified) by manufacturers. Since there is no industry approach, it may be useful to provide a brief review of terminology used in relation to Analog Devices integrated-circuit sample-hold amplifiers.

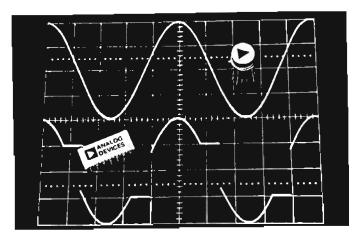

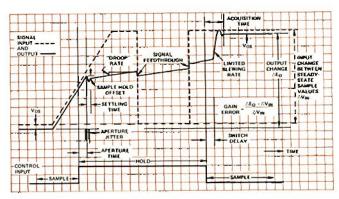

Figure 3 shows the common sources of error that occur during the four phases of operation, and Figure 4 shows how some of them are affected by the magnitude of C<sub>H</sub>. In the adjacent column will be found a discussion of sample-hold parameters. The four phases of operation are:

- Sample: The output is seeking to track the input, with the relationship determined by the external feedback connections, as an operational amplifier. Error sources include bandwidth and slewing rate limitations (a function of CH), low-frequency gain errors, and do offset.

- Sample-to-Hold: When the control signal switches, the S-H output should simply stop changing, and hold the last value. In fact, there will be aperture-time and settling-time errors, during which delays, spikes, and lags occur, and a sample-hold offset, caused by coupled charge from the control signal.

- Hold: The output should stay put. Actually, it will "droop" up or down as a function of CH and the leakage current through it, and ac input signals will "feed through" to the output.

Figure 3. Principal sample/hold dynamic parameters. Errors are exaggerated for clarity.

Figure 4. Circuit parameters as a function of hold capacitance.

• Hold-to-Sample: When the control signal switches, the output should immediately jump to the existing input value and follow it accurately thereafter. In real devices, there will be switching-delay, acquisition-time, and settling-time errors.

#### PARAMETERS OF SAMPLE-HOLD AMPLIFIERS

#### Sample Mode

Gain errors may be expressed in terms of scale factor, non-linearity, or both. In the case of differential-input devices, such as the AD582 and AD583, the limiting factor in the unity-gain follower is the input common-mode error and its non-linearity (0.01% max for AD582, 0.02% typ for AD583), rather than the dc open-loop gain of 25,000. When feasible, the unity gain inverter configuration will provide the best linearity and gain accuracy.

"Op-amp errors" are those errors that generally apply to op amps, whether or not they are gated; they include offset voltage, bias current, their sensitivities to temperature and supply voltage, etc. Dynamic op-amp errors which involve slewing and/or gain-bandwidth, will depend on the value of CH.

#### Sample-to-Hold Transition

Aperture time is the time from the hold command until the hold capacitor is actually disconnected. If the time were fixed, the command could be advanced sufficiently to obtain a switch opening (and subsequent "freezing" of the data) at exactly the right time. However, it can differ by 20% or more from unit to unit and is subject to "jitter" which is the ultimate determinant of uncertainty of the time of measurement.

From the opening of the switch, the settling time is the interval required for the output to settle to its final value, within a given percentage of full scale. In data acquisition, it is a critical parameter, because an A-D converter should not begin conversion until this interval is complete.

Sample-to-hold offset is a step produced by charge coupled from the logic signal to the hold capacitor via stray capacitance and internal operating-point changes. This step can be reduced up to a point by increasing the magnitude of CH. It can be further reduced by "charge cancellation" circuitry, which is most-successfully employed if the S-H offset is small to begin with, as in the AD582.

#### **Hold Mode**

Droop is simply the integration of net positive or negative leakage current in the hold capacitor and is inversely proportional to C<sub>H</sub>: dV/dt = 1/C<sub>H</sub>. For example, a droop specification of 50mV/s with C<sub>H</sub> = 1000pF at +25°C indicates a leakage current of 50pA.

Feedthrough is the residue of an ac input signal that is coupled into the hold capacitor by stray capacitance or leakage across the switch. It is inversely proportional to CH.

#### Hold-to-Sample Transition

Acquisition time is the shortest time after a sample command has been given that a hold command can be given and result in retaining a voltage acquired with the necessary accuracy. For devices of the nature of the AD582 and AD583, involving the kind of causality found in high-gain feedback loops, it is equal to the time interval for the switch to close and the output to slew and settle to within the prescribed limits.

### INDUCTOSYN-TO-DIGITAL CONVERTERS

### For the Accurate Measurement of Displacement; Their Use in Linear Measurements for Control Systems

by D. McDonnell

With the coming of computer control of machine tools and drafting systems, the need arose for a linear measurement system that could work with digital data that was fed from the computer-controller. Optically-encoded discs at the end of leadscrews, Moiré-fringe techniques using optical gratings along the machine bed, and other such devices have been used, including lasers, in applications for which they were suitable. However, none of these devices has the combination of ruggedness and low cost of the Farrand Linear Inductosyn.

Until recently, the use of the Inductosyn with digital-control systems has been limited by the lack of high-speed methods of accurately interpolating within one period of the scale. The high-speed tracking Inductosyn-to-Digital converter provides an elegant solution to this problem. The Analog Devices IDC1701 and IDC1703 are converters\* specifically designed for this purpose.

#### THE INDUCTOSYN

For machine-tool and other control systems, the use of the Farrand Linear Inductosynt has been recognized for many years as an accurate method for performing linear measurements. Inductosyns are manufactured in forms suitable for measuring either straight-line distances or angles. Here we consider the use of linear Inductosyn measurements, though nearly all aspects of the discussion can be easily applied for rotary measurements.

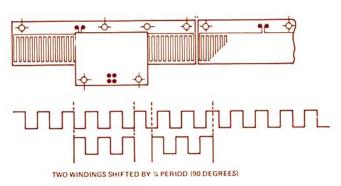

The linear Inductosyn is an especially-useful tool in the high-resolution measurement and control of linear motion over relatively-large distances (many meters). It consists of two magnetically-coupled parts, one usually fixed to the bed of a machine, the other movable with the tools or work. The fixed portion consists of joined lengths of material with a printed rectangular "square-wave" pattern; the movable portion has two short lengths of the same pattern, displaced by one-quarter period ("90°"). The two parts which form the Inductosyn are shown in principle in Figure 1. The fixed "ruler" is typically

Figure 1. The Inductosyn track and slider system.

\*Use the reply card to request information on these devices. †Farrand, Inc. trademark

available in either 10'' or 250mm lengths, depending on whether the metric or the English scale is to be used. (The fixed scales are also available as continuous strip in lengths up to 30 feet -9.144m.)

Like the two-phase synchro resolver, the Inductosyn utilizes the inductive coupling between a reference winding and two mutually-orthogonal windings to provide an output that is a function of position. In the Inductosyn, the electromagnetic circuits are rearranged in two parallel flat plates, with an intervening electrostatic shield to minimize capacitive coupling. The Inductosyn is a bilateral device; that is, either (1) the fixed winding can be driven by an ac reference, with the slider position manifested in the relative amplitudes of the voltages induced in the two orthogonal windings, or (2) the two windings could be driven by orthogonal resolver outputs, with the fixed winding providing a measure of the difference between the resolver angle and the corresponding positional displacement of the slider.

The second mode of operation is used in conventional Inductosyn feedback-control systems, with the slider driven to maintain nil error between the "set point", applied by the resolver, and the incremental slider position (within a given modulus (cycle) of the printed stator). Although effective in analog servo systems, (2) is not as useful as (1) in digitally-controlled systems. Our discussion in these pages will deal with applications of the first alternative.

### INDUCTOSYN-TO-DIGITAL CONVERSION SYSTEMS

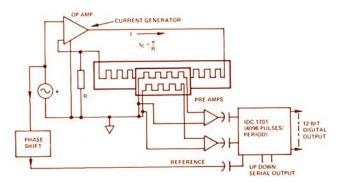

The reference input to the fixed scale is an accurrent generator at a frequency typically greater than 2.5kHz. The ac outputs at the slider windings, with amplitudes respectively proportional to the sine and cosine of the incremental angle, are preamplified and applied to the input of an Inductosyn-to-Digital Converter (IDC). A reference ac signal, in a phase relationship with the current input to the stator, is also fed into the converter, as shown in Figure 2. As the slider of the Inductosyn is moved through one cycle of the pattern, the

Figure 2. The Inductosyn as a resolver control transformer with digital output.

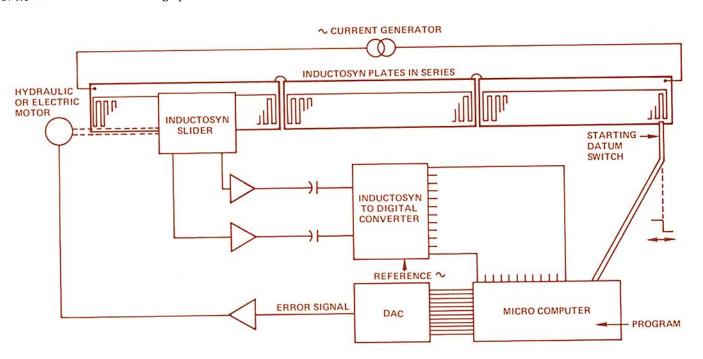

digital output of the IDC will change through 360°. For absolute positioning, relative to a datum, a counter counts half cycles, providing the most-significant bits of information, and the IDC provides the fractional information, at resolutions up to 12 bits. The outstanding degree of resolution available is quite apparent. A typical system is shown in Figure 3.

#### PERFORMANCE REQUIREMENT FOR THE IDC

For modern milling and drafting machines, the speed of operation is very important. A standard minimum top speed of 10 meters/minute is now accepted as being necessary in machinetool control. The standard pitch of the Inductosyns being used is 2.0mm. Since one revolution corresponds to 2.0mm along the track, the top speed is equivalent to 83.3 revolutions per second.

For some standard European machines, a reading rate of 40 commands (or readings) per second has been adopted – providing an interval of 25ms between readings. This means that at the maximum speed, the machine will have moved by 2.08 periods between samples. This means, further, that the IDC must have two extra up-down counting stages beyond the normal MSB of 180°, or else lost periods will occur at high speed.

In addition, the IDC should be capable of following accelerations of up to 1500 revolutions/second/second more or less accurately but without saturating the error detector. This acceleration rate implies that the machine can get up to its maximum velocity of 10 meters/minute in approximately 5mm displacement; similarly, it can be brought to rest from its maximum speed in 5mm.

The choice of carrier frequency for use in the converter is a compromise, taking into account: (1) at low frequencies, the signals out of the Inductosyn are too small, in comparison to the amplifier input noise and system interference: (2) at high frequencies, the capacitances across the precision resistors and switches establish the limiting speed. From the point-of-view

of acceleration performance, the higher the frequency, the better, since less smoothing is needed in the shaping circuits following the phase-sensitive detector.

Two factors influence the useful maximum resolution: (1) the precision with which the induced voltages in the two windings follow the sine and cosine laws with angle and (2) the degree of smoothness of control required. The higher the resolution required, the more difficult it becomes to meet the maximum velocity and acceleration requirements. The maximum resolution that seems justified by the overall accuracy of the system is 12 bits for a 2mm period (1 bit corresponds to 0.5µm, or 19µin, with 1-bit smoothness.

The IDC1701 and IDC1703 are tracking Inductosyn-to-digital converters which have been specifically designed to meet the needs of Inductosyn systems. They differ from other tracking resolver-to-digital converters principally in having the ability to track at 150 pitches/second and accelerate at 250/second/second with only 1LSB error. They are designed to work with carrier frequencies from 2kHz to 10kHz, and are tested at 5kHz. They accept input signals of ¼V rms, and provide digital outputs at TTL levels. Because of the low levels and high-resolution capability, the input signal amplifiers should be well-shielded and located as close to the slider as possible — preferably on the slider.

The stator is driven by current in order to obtain complete control over the flux generated in the stator, irrespective of differing track resistances in a series chain or tendencies by stray fields linking the track to induce parasitic currents.

The IDC1701 has parallel and serial (4096 pulses/pitch) sigital outputs; the IDC1703 outputs are up-down pulses at 4000/pitch, together with carry-borrow pulses for each complete pitch. The latter is necessary to obtain a precision datum point. The price of either unit is \$350 by the 1's.

Figure 3. The use of an Inductosyn-to-digital converter in an Inductosyn control loop.

### 10-VOLT (±1mV) REFERENCES

### Low-Cost Hybrids Have 5ppm/°C Stability Choice Among +,-, or Both Polarities

by Jerry Gunn

In precision analog circuits, there is a recutring need for precisely-set, dependable reference voltages that can be used as a basis for introducing constant voltages or currents for bridge excitation, analog computation, predictable offsets and references, and A/D and D/A conversion. Some desirable properties of such references include:

- Accurate initial values (to within ±0.01%) to permit the use of fixed, predictable resistors, without tweaking

- Good stability over wide temperature ranges, comparable with that of typical precision resistors

- Ability to operate over a wide range of inputs for example, ±20% of nominal - with regulation of only a few ppm/% of input variation

- · Good load regulation. Although the loading on precision references is fixed in many circuits, load regulation still affects the initial value.

- Availability in a choice of polarities, including dual. Murphy's Law tells us that a single available reference is always of the wrong polarity, or may be insufficient, in any event, if several reference voltages are needed.

To meet these needs, 3 related references\* are now available, for the popular 10.000V output level, all housed in hermetically-sealed 14-pin dual in-line packages: the AD2700 for +10V, the AD2701 for -10V, and the AD2702 for both polarities.

#### WHAT TYPICAL ALTERNATIVES EXIST?

- If the system power supply is sufficiently accurate, it can itself serve as a rather expensive reference.

- Operate a low-cost Zener diode at constant temperature; unload it with an op amp. This may prove bulky and unfeasible for very wide-temperature-range operation.

- Use a temperature-compensated band-gap reference, such as the 2.5V monolithic AD580† with appropriate opamp circuitry (Dialogue 9-2). The result is not very compact, it requires a user tweak, and its best standard tempco is 10ppm/°C.

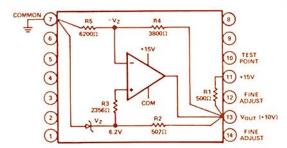

- Use a temperature-compensated Zener diode in a circuit like that of Figure 1 (which is the basic circuit of the AD2700 series). T-C Zeners are proven, have low noise and high stability. However, since the diode voltage is current-sensitive, the buffer must be used to unload the diode and reduce the influence of power-supply variations, as well as permit precise amplification from 6.2V (±5%) to 10.000V. In the AD2700 series, the circuitdesign, assembly, test, and hermetic scaling in its DIP package are all provided, along with guaranteed performance, at a reasonably low cost (\$10 in 100's for the AD2700L and AD2701L, \$12 in 100's for the AD2702L dual reference).

#### †Use the reply card to request data on the AD580.

#### HOW IT WORKS

The high-gain operational amplifier serves to balance the bridge formed by R2 and the Zener diode, and R4 and R5. Since, at balance,  $V_{\rm Z} \cong (6.2/10) V_{\rm OUT}, \, V_{\rm OUT} \cong 10 V.$  The bridge ratio is laser-trimmed for VOUT = 10.000V. Since (VOUT - VZ) is nearly constant, irrespective of supply voltage, the variation of current through the diode is affected only to a second order by supply-voltage variations.

Resistor R1 facilitates startup and reduces the load current furnished by the amplifier, by supplying the 7.5mA diode current and part of the external load current, for VS = 15V.

Because the circuit is a high-gain feedback loop, IR drops in the internal output leads and wirebonds can be compensated for by directly connecting the ends of measuring divider R4-R5 to the output pins. The resulting output resistance is  $0.02\Omega$ .

The AD2700/01/02 use the Analog Devices Ni-Cr-Au thin-film system (Analog Dialogue, 8-1, 8-2) for resistors and conductors, with a high-quality temperature-compensated reference diode and low-drift op-amp chip. To make best use of the stability of the reference diode, R4 and R5 - which determine the gain-track to better than 0.5ppm/°C, with low absolute temperature coefficients and excellent long-term stability.

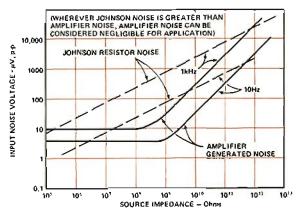

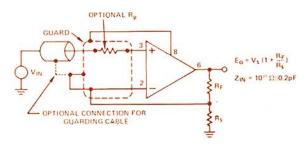

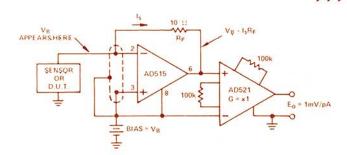

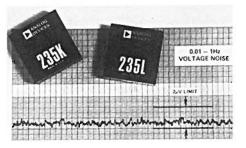

#### PERFORMANCE